Design Automation Conference (DAC) - главная выставка софтверных компаний, которые создают средства проектирования чипов. Именно на ней появляются стартапы, которые определяют проектирование через 10-15 лет (например появление Synopsys на рубеже 1980-1990-х привело к появлению iPhone в середине 2000-х).

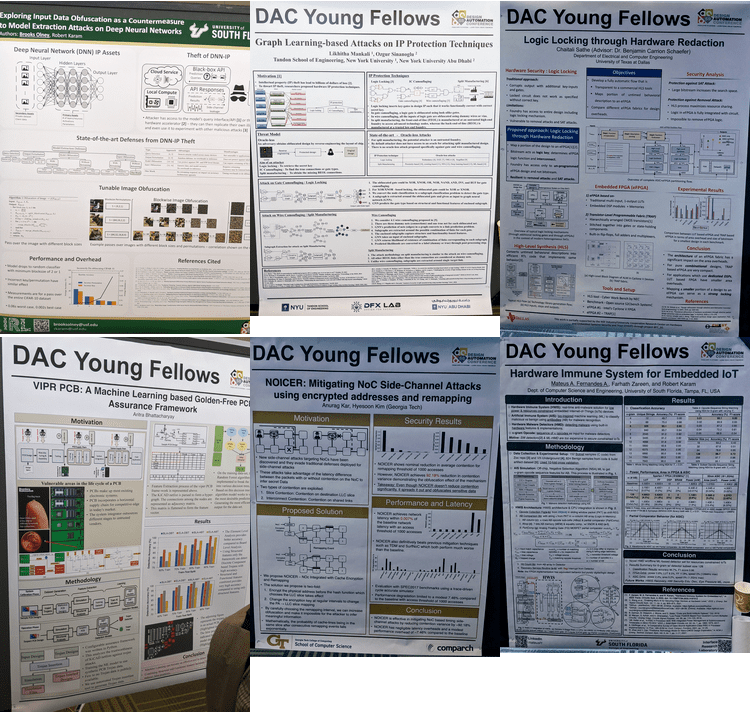

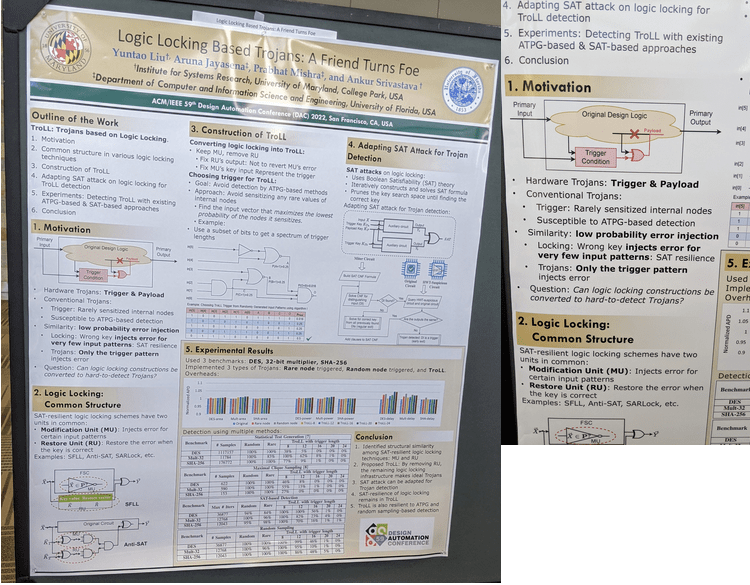

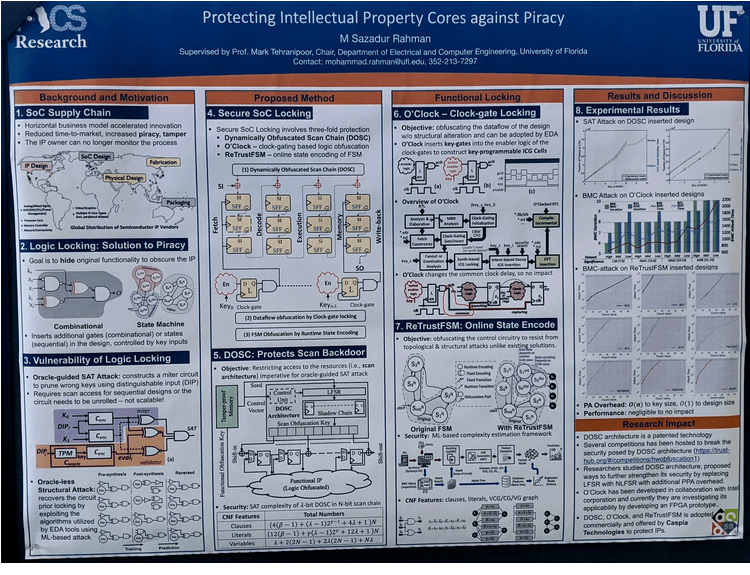

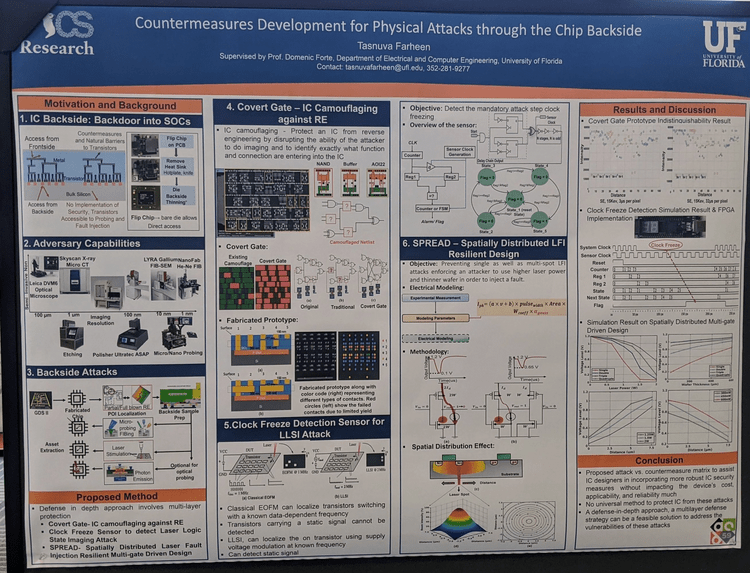

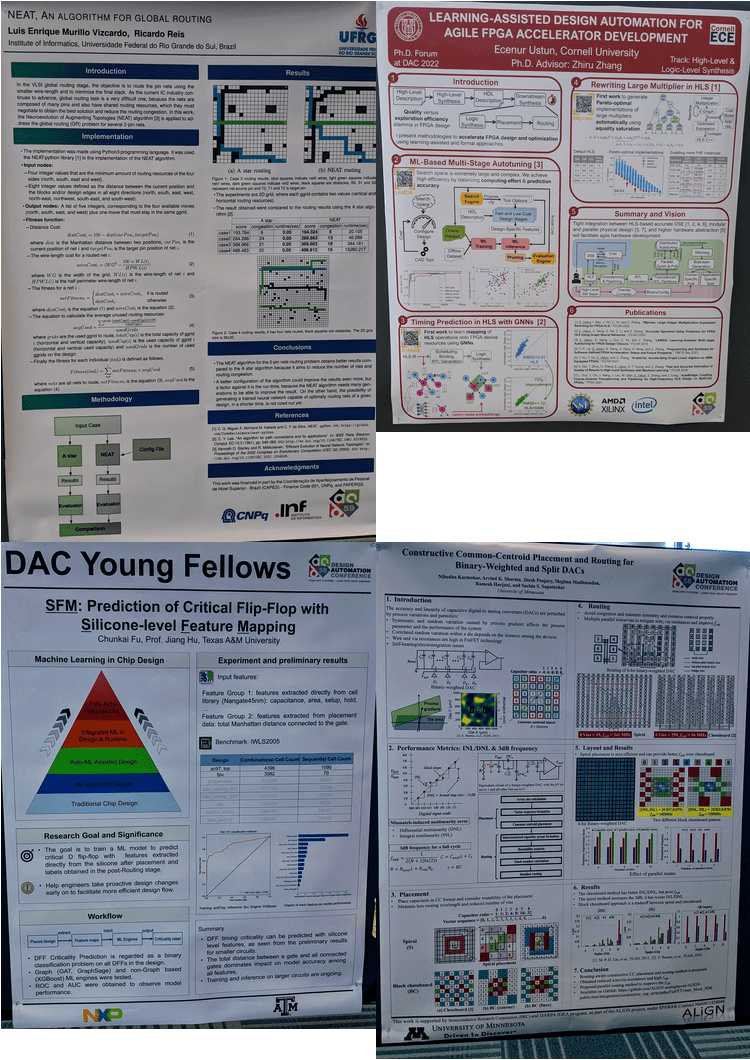

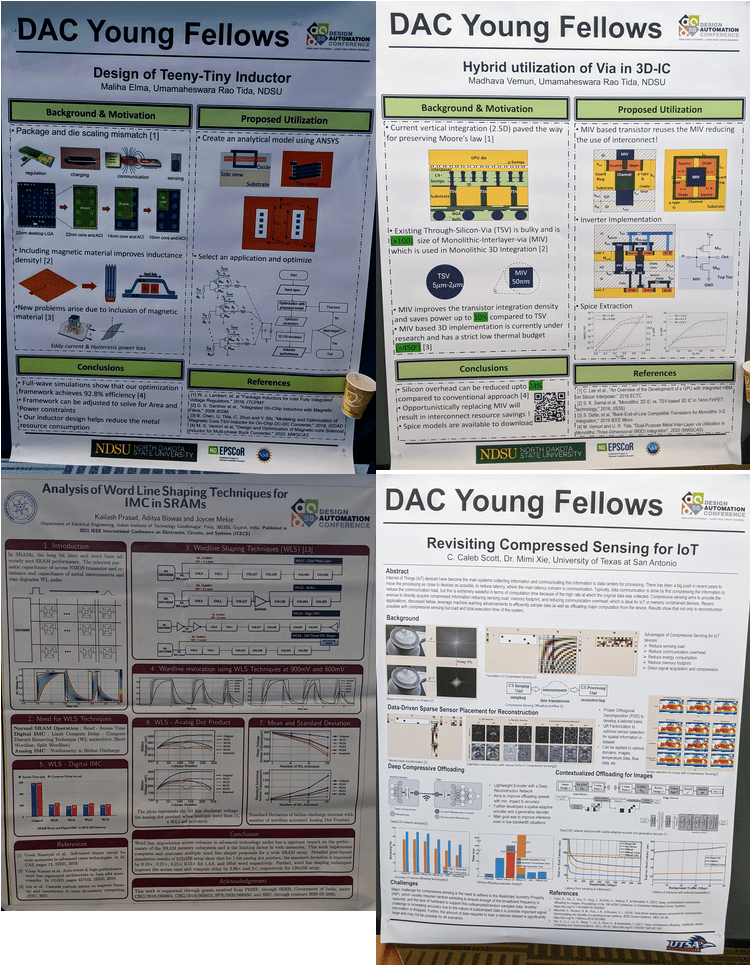

На DAC помимо выставки и официальных докладов есть также и poster session - молодые исследователи из университетов вывешивают в виде плакатов, чем они занимаются. Я методически сфотографировал все постеры во время последней конференции DAC в Сан-Франциско, и вот перед вами картина маслом:

6 постеров по новой модной теме "Приблизительного компьютинга" ("Approximate Computing"), когда вычислениям разрешается быть неточными (например в нейросетке) если это экономит энергопотребление или делается быстрее.

Более 30 постеров так или иначе трогают тему нейросетей:

16 постеров по аппаратному ускорению нейросетей. Из них:

два по теме ReRAM,

два по нейроморфным процессорам,

один по тематике CGRA (Coarse Grained Reconfigurable Array - это такая матрица из недопроцессоров, по аналогии с FPGA, но ячейки соединяются не сигналами, а шинами, и в каждой ячейке есть сиквенсер, типа маленькая программа),

один толерантный к глюкам от прилетевшего из космоса луча.

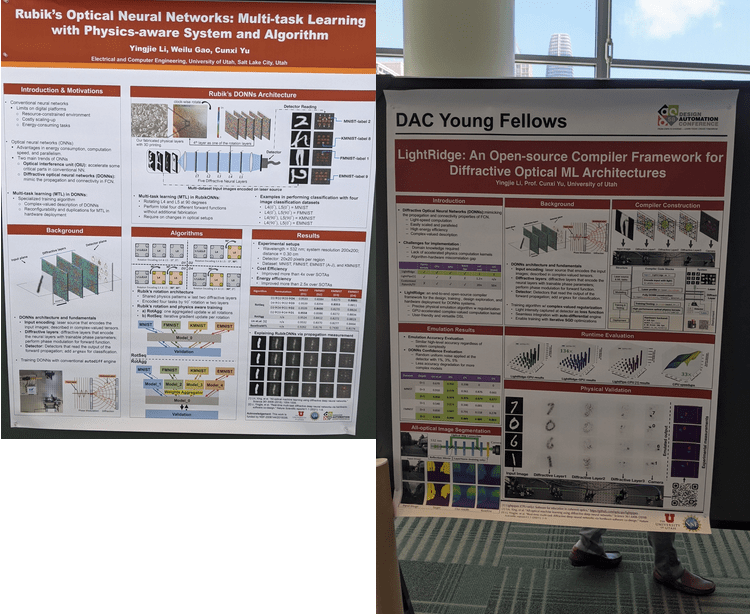

2 постера - по оптическим нейросетям.

3 постера - о нейросетях вообще (без контекста архитектуры ускорителя).

2 постера - о вычислениях в памяти (in memory computing). Не разобрался, что это такое, но это тоже привязывается к нейросетям.

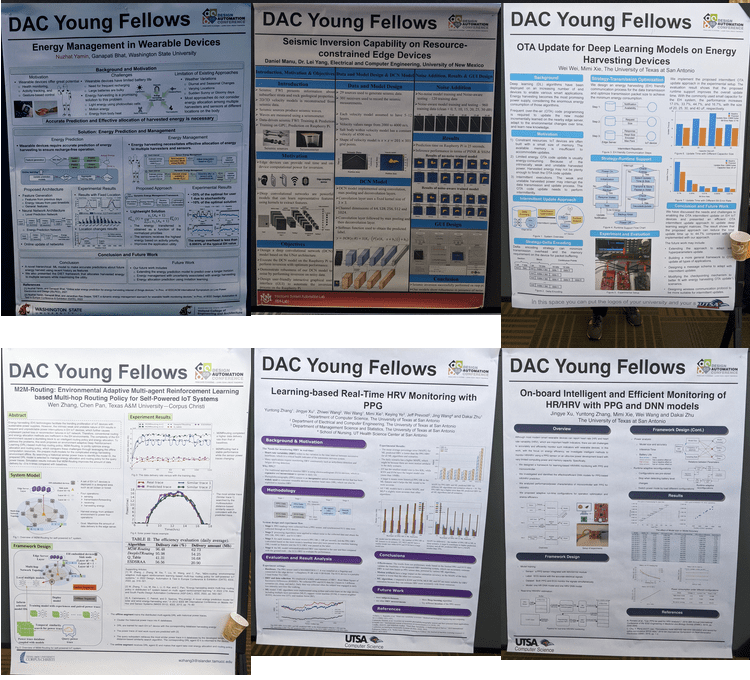

7 постеров - о приложениях нейросетей, в том числе для дронов, сейсморазведки, сбора энергии (energy harvesting - это еще что такое?) и здравоохранения.

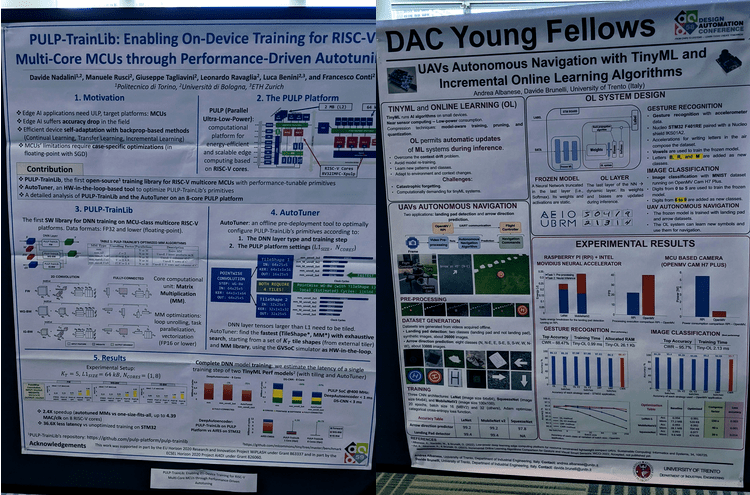

2 постера - все о тех же нейросетях, но на краю, то бишь во встроенных устройствах (Edge AI).

10 постеров про кибербезопасность, в том числе:

про защиту IP блоков,

про аппаратные трояны в микросхемах и платах (а в России говорят "закладок не бывает!"),

side-channel attacks (это было на Хабре) и физические атаки (не понял что это такое)

"аппаратный иммунитет"

нахождение уязвимостей

6 постеров на почтенную тематику физического проектирования, хотя пару раз нейросети влазят и туда:

Постер про энергопотребление

Про проектирование смешанных аналогово-цифровых схем

Про глобальную трассировку (routing) цифровых схем

Про размещение и трассировку цифро-аналоговых преобразователей

2 постера про использование машинного обучения в физическом проектировании

Дальше всего понемножку:

3 постера про высокопроизводительные вычисления (High Performance Computing - HPC)

2 постера про датацентры

1 постер про аппаратный ускоритель, но без слова "нейросеть"

2 постера про моделирование систем на кристалле - System-on-Chip - SoC

1 постер про сети на кристалле

1 постер про сопряжение с биосигналами

2 постера привязаны к архитектуре RISC-V - это умеренно модно, не так как нейросети и трояны

1 постер про проектирование RISC-ядер (не обязательно с архитектурой RISC-V) как комбинацию из конечных автоматов для стадий конвейера (ну, можно рассматривать и так, хотя это неканоническое изложение)

2 постера про вечно молодую тематику высокоуровневого синтеза, который уже 30 лет грозиться вытеснить обычный за 5 лет

4 постера про совсем низкий уровень - катушки, проходы в микросхемах, устройства статической памяти и сенсоры

2 постера про будущее всего человечества - квантовый компьютинг

Постер про панель дисплея

Постер про сравнение процессоров в Бразилии

Постер про формальную верификацию, в котором упоминается Coq, Haskell, SystemVerilog и контроллеры DRAM памяти

Ну и кто-то еще одну сортировку на FPGA написал - такое на таких конференциях бывает

Все постеры:

03. Approximate Computing – Compilers for HPC

04. Approximate Computing – Power-efficient multipliers

05. Approximate Computing – Logic Synthesis

06. Approximate Computing – DNN

07. Approximate Computing – DNN

08. Approximate Computing – DNN

09. Neural Networks – Hardware Accelerators

10. Neural Networks – Hardware Accelerators

11. Neural Networks – Hardware Accelerators

12. Neural Networks – Hardware Accelerators

13. Neural Networks – Hardware Accelerators

14. Neural Networks – Hardware Accelerators

15. Neural Networks – Hardware Accelerators

16. Neural Networks – Hardware Accelerators

17. Neural Networks – Hardware Accelerators

18. Neural Networks – Hardware Accelerators

19. Neural Networks – Hardware Accelerators – ReRAM

20. Neural Networks – Hardware Accelerators – ReRAM

21. Neural Networks – Hardware Accelerators – Neuromorphic

22. Neural Networks – Hardware Accelerators – Neuromorphic

23. Neural Networks – Hardware Accelerators – CGRA

24. Neural Networks – Hardware Accelerators – Fault-tolerant

27. Neural Networks – General – Train only on important samples

28. Neural Networks – General – NVidia-based

29. Neural Networks – General – Spiking

30. Neural Networks – In-memory computing

31. Neural Networks – In-memory computing

32. Neural Networks – Applications – Deploying NN on drones

33. Neural Networks – Applications – To predict energy management in wearable devices

34. Neural Networks – Applications – For seismic computations

35. Neural Networks – Applications – For energy harvesting

36. Neural Networks – Applications – For energy harvesting

37. Neural Networks – Applications – Healthcare

38. Neural Networks – Applications – Healthcare

39. Neural Networks – Edge AI – MCU

40. Neural Networks – Edge AI – MCU

47. Security – Hardware trojans in PCB

48. Security – Side-channel attacks

51. Security – Hardware Immune System

45. Security – Hardware trojans in ASIC

46. Security – Hardware trojans in ASIC

49. Security – Physical attacks

52. High-performance computing – Power and thermal management emulation

53. High-performance computing – Reconfigurable smart switches

54. High-performance computing – Combined with ML

57. Hardware accelerators – ASIC

58. System-level design – Simulation

59. System-level design – Simulation

60. System-level design – Biosignal processing

63. RISC-V – Return-Oriented-Programing attacks

64. RISC-V – Representing a generic RISC microarchitecture as multiple state machines

69. Physical Design – Mixed signal

67. Physical Design – Global routing

70. Physical Design – ML-assisted design

71. Physical Design – ML-assisted design

72. Physical Design – PnR for digital-to-analog converters

73. IC components on low level – Inductor design

74. IC components on low level – Via utilization

75. IC components on low level – SRAM structure

76. IC components on low level – Sensors for IoT

79. Misc – Display panel development

81. Misc – Formal verification – Coq DRAM controllers Haskell SystemVerilog

82. Misc – Serial sorter on FPGA

Если вы хотите почитать еще про DAC, я написал и другие отчеты, в частности:

Комментарии (28)

Brak0del

07.09.2022 11:38+1физические атаки (не понял что это такое)

Это когда например криптопроцессор заставляют неправильно считать, нарушая работу тактового генератора или посылая глитчи по питанию, а также когда вмешиваются в структуру или работу чипа волшебными лучами (сфокусированным ионным пучком и т.д.)

В целом, это класс атак с непосредственным доступом к чипу.

checkpoint

07.09.2022 13:59+2"Side channel attack" это Spectre же ?

А вообще, клёво у вас там в Сан Франциско, на любую саму безумную идею находится потребитель и инвестор.

andy_p

07.09.2022 16:26+1например появление Synopsys на рубеже 1980-1990-х привело к появлению iPhone в середине 2000-х

Довольно смелое утверждение, учитывая, что существуют Cadence и Mentor.

YuriPanchul Автор

07.09.2022 17:40+1Логический синтез на уровне регистровых передач вывел на рынок Synopsys (logic synthesis / register transfer level - RTL). Cadence и Mentor был в нем не первыми, хотя они изобрели другие важные технологии (в симуляции, физической верификации итд).

Без RTL синтеза никаких айфонов конечно же не было бы - миллиарды транзисторов на чипе тыкая мышкой в экран задизайнить нереально.

Вот нагуглил ссылку про историю:

The notions of logic synthesis can be traced back to the early 1970s and work conducted at IBM called Logic Synthesis System (LSS). This was a rule-based transformation system. These looked for patterns in a design and the rule would perform a transformation on that part of the design in order to improve it. Trimeter had a commercial example of this type of system.

Another early development was MacPitts, developed at MIT. MacPitts took system descriptions as input and produced full custom nMOS layouts as output. It was initially commercialized by MetaLogic, but failed to have any success. MIT also licensed the technology to GTE Labs which became the basis for the SILC silicon compiler.

MacPitts and other similar systems were based on algorithmic transformations. These systems basically had two parts, first a technology independent step that made transformations of higher level concepts into Boolean logic and then a second technology mapping phase where the choices of gates or other library elements was made. Algorithmic systems included MIS, BOLD, Silc, AT&T and several other University efforts.

Synopsys (SOCRATES) had a system (originally developed with GE) that was basically a merge of the two approaches. The front end for transformational and the back end had rule based optimization. Synopsys was the first licensee of the Verilog language from Gateway Design Automation (acquired by Cadence who later made Verilog an open language through Accellera and IEEE standardization processes).

Since that time, Synopsys has dominated the logic synthesis market for ASICs, although other tools from Synplicity (acquired by Synopsys) and Exemplar (acquired by Mentor) had success in the FPGA market

As implementation geometries shrank, delays associated with wires grew while gate delays shrank. This created a problem for logic synthesis because timing assumed that gate delays dominated. Wire delays only became known after place and route, which was much further down in the implementation process. Around 90nm, logic synthesis had to become back-end aware. This was not only for timing issues, but required things such as buffer insertion, cell sizing and power reduction techniques, and many other areas where the layout and the design could not be fully separated. This became known as physical synthesis.

andy_p

07.09.2022 18:27Я еще когда студентом на кафедре электроники МИФИ был в середине-конце 80-х, там сплошные разговоры про кремниевый компилятор были. Так что идеи витали в воздухе. Если не Synopsys, так кто-нибудь другой это всё на рынок вывел бы.

YuriPanchul Автор

07.09.2022 19:17+3То, что называли кремниевыми компиляторами в начале 1980-х (например http://caltechconf.library.caltech.edu/184/1/DaveJohannsen.pdf имело слабое отношение к тому, что сделал Synopsys в конце 1980-х.

Вообще в этих делах очень трудно держать правильный баланс между возможным и полезным. Например многие исследователи пытали сделать кремний прямо из алгоритма (высокоуровневый синтез) - что не является решенной задачи и сейчас, 40 лет спустя. А вот уровень регистровых передач, который синтезировал Synopsys, был в самый раз: с одной стороны, как синтезировать кучу always-блоков, в каждом из которых все умещается в такт - довольно понятно, хотя сделать это хорошо непросто. С другой стороны, это радикально повышает производительность труда проектировщика, даже если ему приходится самому придумывать микроархитектуру - как разложить алгоритм в конвейеры, очереди и конечные автоматы.

Я это к тому, что вполне возможно, что без Synopsys исследователи возились бы с попытками более сложного высокоуровневого синтеза еще много лет, а проектировщики продолжали бы делать много вручную, на уровне gates. Такая альтернативная история 1990-х имхо вполне возможна.

livsius

09.09.2022 22:58| Без RTL синтеза никаких айфонов конечно же не было бы

Точно! А если бы не Эдисон, мы бы сейчас работали на компьютерах при свечах.

YuriPanchul Автор

09.09.2022 23:08Лампочки можно придумать многими способами, а вот с повышением производительности труда проектировщика очень легко скатиться в ситуацию, когда замах большой, а выход непрактичен. См. комменты выше https://habr.com/ru/post/686602/comments/#comment_24706454

livsius

09.09.2022 23:27Кто ж спорит. Вопрос только в том, остановился бы прогресс без синопсиса, или все же упомянутые инструменты разработали бы другие конторы?

YuriPanchul Автор

09.09.2022 23:38Альтернативы были и во время Синопсиса, но они были или слишком легковесные, или наоборот, скатывались вот в то, что я описал выше. В любом случае, если бы не было Синопсиса и выросло бы что-нибудь другое, то это что-нибудь тоже в качестве первой выставки, где это показать, скорее всего выбрало бы DAC. Ибо такая была мода в 1980-1990-е когда происходили эти события.

tzlom

07.09.2022 18:12+1<quote>про аппаратные трояны в микросхемах и платах (а в России говорят "закладок не бывает!")</quote>

говорят что не бывает закладок добавленных на фабе, в данных постерах их тоже нет

YuriPanchul Автор

07.09.2022 19:03С фабом все понятно - так как у заказчика производства (проектировщика системы на кристалле) есть на руках сгенерированный им GDSII файл, то он теоретически может вскрыть микросхему, сфотографировать ее электронным микроскопом и написать программку, которая сравнивает фотографию с GDSII файлом. Поэтому фаб вряд-ли будет пытаться вставлять закладки - после первого обнаружения бизнес фаба накрывается.

Моя фраза "а в России говорят "закладок не бывает!"" относится скорее не к инженерам, а ко всяким журналистам общественных СМИ и подобным типам, которые ссылаются на обсуждения закладок как на дремучую паранойю по отношению к светлому Западу. Верилога и GDSII файла эти товарищи конечно в жизни не видели и не знают, что добавить труднонаходимую закладку во время проектирования совершенно реально.

tzlom

07.09.2022 19:32+1У нас видимо разное семплирование журналистов, в моей выборке это ребята ратующие за "собственное производство" т.к. TSMC пришлет зловредный чип.

С PCB все ясно- приделать какой-нибудь чип вообще не проблема, однако статья на полном серьёзе предполагает что завод пришлет с сюрпризом. Сама работа интересная, но для бизнеса это такое же самоубийство что и с фабом.

С FPGA как по мне это софтовая атака, хотя конечно специфика делает её весьма интересной.

Закладка в IP блоке - да, возможно и не тривиально для анализа, но практичность весьма под сомнением. Опять таки обнаружение такой закладки хорошенечко ударит по бизнесу, так что я не думаю что кто-нибудь такое осилит.

YuriPanchul Автор

07.09.2022 19:49+2*** Закладка в IP блоке - да, возможно и не тривиально для анализа, но практичность весьма под сомнением. ***

Как практикующий проектировщик IP-блоков для ASIC-ов я даже готов провести летний лагерь для молодежи по изготовлению закладок в процессоры. Взять открытое RISC-V ядро и с ним химичить. Я об этом писал:

https://skillbox.ru/media/business/interview-yuri-panchul/

— А почему так важно обеспечить критическую инфраструктуру отечественными процессорами? В них действительно могут быть спрятаны «закладки»?

— Отрицать техническую возможность создания таких «закладок» может только человек, который никогда не видел исходный код процессора на языке описания аппаратуры и не имеет представления о маршруте проектирования микросхем. Например, можно спроектировать небольшой блок внутри процессора — конечный автомат, который будет отслеживать данные в регистрах общего назначения или буферах при записи в кэш. При попадании туда байтов ключевой фразы — например, из текста полученного электронного письма — блок может останавливать процессор.

Такой аппаратный блок принципиально нельзя увидеть программными средствами, его не сможет найти никакой антивирус. Шифрование не поможет, потому что на регистры или строки кэша всё придёт в уже расшифрованном виде. Можно ли сфотографировать слои чипа электронным микроскопом и вручную искать несколько тысяч вредоносных транзисторов среди миллиарда других? Это поиск иглы в стоге сена без магнита.

Конечно, можно надеяться, что производители процессоров не будут таким заниматься. Но службы безопасности принимают в расчёт только технические возможности, а не субъективное доверие к тем или иным компаниям. И не только службы безопасности. Вполне возможно, что интерес «Росатома» к МЦСТ частично объясняется тем, что RTL «Эльбруса» написан в России.

*** Опять таки обнаружение такой закладки хорошенечко ударит по бизнесу, так что я не думаю что кто-нибудь такое осилит. ***

Прежде всего, пассивные закладки уже есть. Как по-вашему, обнаруживают, что RTL каких-нибудь ядер в сделанных далеко на востоке системах на кристалле не спионерен? Например по недокументированным результатам исполнения определенной последовательности команд. Каждая из которых сохраняет некое невидимое программисту состояние.

tzlom

07.09.2022 23:48Прежде всего, пассивные закладки уже есть.

Ну вы же понимаете, что имелись ввиду вредоносные действия, а не защита интеллектуальной собственности. Я уж не говорю о том, что при необходимости провести аудит IP блоков вполне возможно, и для этого не надо сидеть с электронным микроскопом.

службы безопасности принимают в расчёт только технические возможности, а не субъективное доверие к тем или иным

Ну и состояли бы они из одного человека коли так.

RTL «Эльбруса» написан в России

Ну и Британский GPU в виде IP блока.

hecatonchires

09.09.2022 10:12Из статьи https://habr.com/ru/post/664740/

UPD2: Пояснения от эльбрусовцев, конкретно от Максима Горшенина:

1. Да, в Эльбрус-2С3 3D-ядра компании Imagination (был выбор из множества, в том числе и ARM, Vivante, etc.)

2. 2D и дисплейный контроллер МЦСТ использует собственной разработки в процах со встроенной графикой (Эльбрус-1С+, Эльбрус-2С3, МЦСТ R2000+), а не покупные.

3. Выдумки про «шлейф от курсора» всего лишь выдумки и предположения.

4. В Эльбрус-1С+ и МЦСТ R2000+ 3D-ускорение от компании Vivante, Эльбрус-2С3 один проц с ядрами компании Imaginarion

P.S. Предусмотрено в процессорах от МЦСТ отключение подачи питания на покупные 3D-ядра. И тогда будет работать только 2D-ядро с видеоускорением, написанное и созданное компанией МЦСТ, что позволяет продолжить работу проца и выводом видеоизображения, но с отключенным 3D-ускорением.

Покупные 3D-ядра работают и взаимодействуют со всем остальным только через дисплейный контроллер собственной разработки МЦСТ. Получается что-то вроде «забора» вокруг покупных ядер. Сделано для безопасности и ограничения влияния/эксплуатации вероятных недокументированных возможностей в покупных ядрах.

amartology

09.09.2022 11:12UPD2: Пояснения от эльбрусовцев, конкретно от Максима Горшенина:

А про французские интерфейсные блоки, через которые идет все общение процессора со внешним миром, он пояснит? )

amartology

07.09.2022 19:03+92 постера — о вычислениях в памяти (in memory computing). Не разобрался, что это такое, но это тоже привязывается к нейросетям.

Это когда для того, чтобы сделать MAC-операцию, вместо умножения и сложения нулей и единичек большим количеством логических вентилей, берут ячейку флэш-памяти (или ReRAM, непринципиально) и умножают аналоговое входное напряжение на проводимость (transconductance) ячейки, а полученные токи потом суммируют между собой, просто соединяя выходы ячеек памяти вместе. Получается очень большая экономия места и электричества, если вас устраивает ограниченная точность умножения, обусловленная тем, насколько вы можете менять проводимость ячейки памяти (обычно речь идет про 4-5 бит).

MAC-операция — ключевой компонент умножения матриц и, соответственно, ключевая операция, необходимая для обсчета нейросеток.

YuriPanchul Автор

07.09.2022 19:24+1Ни фига себе. Ну вот наконец-то увидел внятное объяснение. А то мне еще ректор Иннополиса Тормасов про это говорил и я не понимал о чем это. Спасибо!

KeisN13

08.09.2022 07:40+2

embedded_bat

08.09.2022 21:50Energy harvesting это когда устройство работает не на батарейках/от сети, а на собранной из окружающей среды энергии - энергии солнца, энергии волн в ISM диапазоне, энергии волн в океане и прочих. На постере люди переживают, что раз питание устройства может пропасть в любой момент в силу переменчивости окружающей среды, то нужен алгоритм обновления прошивки устройства, который это учитывает.

Zara6502

для сравнения: когда я учился в захудалом местечковом политехническом "универе" и самое крутое что было - это Турбо Паскаль, мой товарищ учился в НГУ, они собирали/паяли платы, программировали МК, перешивали ПЗУ японской техники и много чего другого (в общаге вообще все сами себе собирали Спектрумы всех видов и модификаций). Так что образование у всех очень разное и на разном уровне.

YuriPanchul Автор

Не совсем понял вашу мысль. Я тоже в 8 классе программировал МК-54 и потом Турбо Паскаль. И?