Здравствуйте! Меня зовут Станислав Полонский. Я представляю Samsung Advanced Institute of Technology (SAIT) - научно-исследовательский центр, специализирующийся на передовых технологиях будущего.

Сегодня мы поговорим о том, что такое архитектура RISC-V (читается, как «РИСК-Пять»). Я расскажу вам о прошлом и будущем этих процессоров, о том, почему эта архитектура так подходит для Интернета вещей, а в конце скажу, как можно продолжить своё образование в этом направлении.

Масштабирование транзисторов (transistor scaling)

Итак, за последние 50 лет в микроэлектронике мы наблюдаем явление, которое называют «масштабированием транзисторов»: размер транзисторов уменьшился в сотни раз, а их энергопотребление возросло меньше, чем на порядок (рисунок 1). Это также называют масштабированием Деннарда.

Роберт Деннард работал в компании IBM и в 1974 году показал, что уменьшение размеров полевых транзисторов приводит к тому, что они работают быстрее, в то время как общее суммарное энерговыделение является более-менее постоянной величиной.

Однако, эта тенденция, длившаяся десятки лет, закончилась. Размеры транзисторов приближаются к атомным размерам. Я не ожидаю, что в будущем что-то сильно изменится — предел масштабирования достигнут.

Тенденции роста производительности процессоров

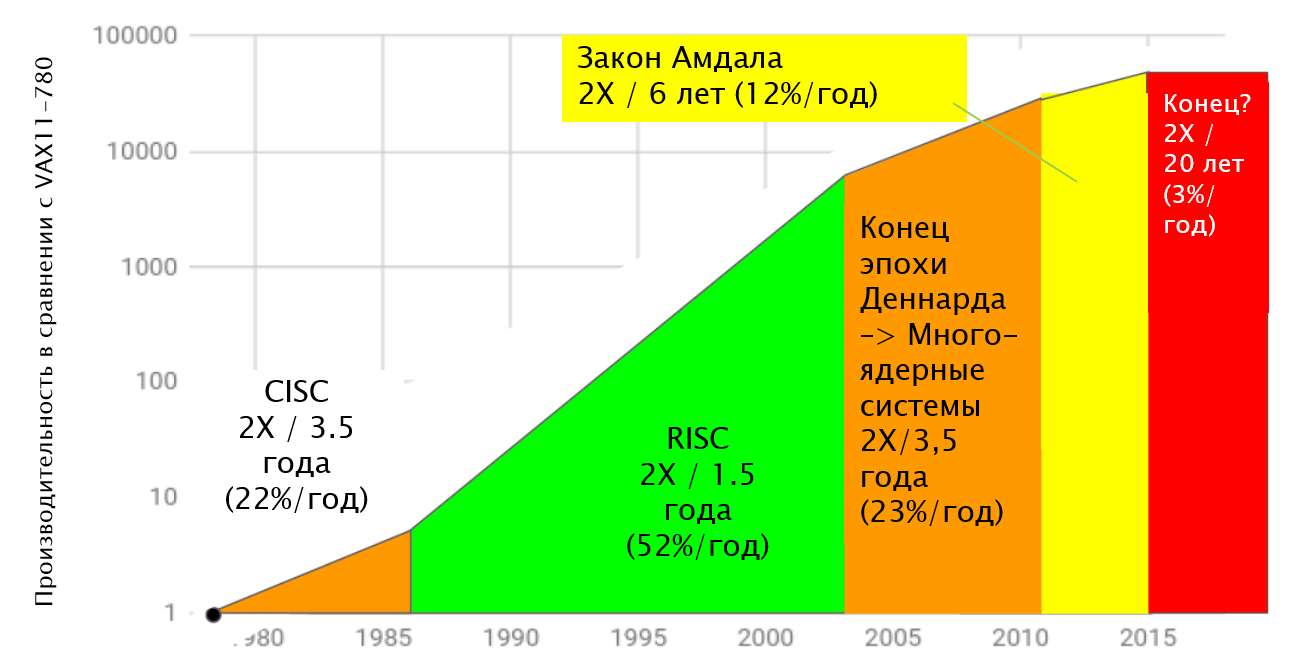

Если раньше мы говорили про одиночные транзисторы, то теперь мы говорим о системах, микропроцессорах, системах на чипе (system-on-chip). На рисунке 2 мы видим, как увеличилась их производительность.

Видно, что производительность увеличилась в сотни тысяч раз (масштаб на графике по вертикали логарифмический) начиная с 80-х годов до настоящего времени.

Вначале программисты имели дело с набором команд процессора, который назывался сложным (CISC — Complex Instruction Set Computer). Люди быстро разобрались с тем, чтобы упростить его и сделать RISC — Reduced Instruction Set Computer. И где-то с 80-х до середины нулевых годов это был основной драйвер роста производительности: транзисторы уменьшаются, архитектуры простые, производительность растет экспоненциально.

К концу эпохи Деннарда произошел переход к многоядерным системам, что добавило ещё производительности. Однако, тут было быстро достигнуто ограничение, обусловленное так называемым законом Амдала, когда производительность многоядерной системы ограничивается наиболее узким местом — доступом к общей памяти среди многочисленных ядер на микропроцессоре.

Сейчас мы находимся в красной зоне — конце масштабирования, насыщении производительности микропроцессоров. Закон Мура (рост производительности в два раза за два года) для микропроцессоров более-менее завершился.

Проблемы архитектуры x86

Что имеем сейчас? Хотя состоялся переход на RISC-процессоры, системы команд продолжали усложняться. Это связано с тем, что возникали новые приложения, а для этих новых приложений требовались новые команды. На рисунке 3 показан рост количества таких команд для архитектуры Intel x86.

Если в середине 70-х была едва ли сотня машинных команд, то сейчас их порядка трех тысяч. Это приводит к усложнению железа. При том, что RISC-железо не должно быть таким: слишком много команд и ограничений на дизайн микропроцессоров.

Сложность архитектуры x86 привела к низкой энергоэффективности, и, как следствие, более энергоэффективная архитектура ARM (Advanced RISC Machine) захватила рынок. Это показательный пример того, как важно поддерживать наборы компьютерных команд как можно более простыми.

Тенденции будущего

Что ждёт нас в будущем? По моему мнению, две важных тенденции:

Мы все знаем про революцию открытых исходников (Open Source) программного обеспечения (ПО). У нас есть компиляторы GCC (GNU Compiler Collection), операционные системы Linux, но есть проблемы, касающиеся открытых компьютерных архитектур (Instructions Set Architectures, ISA). Долгие годы это был удел мегакорпораций. Они контролировали компьютерные архитектуры.

Второй тренд касается специализированных архитектур (Domain Specific Architectures). Если раньше мы говорили про компьютеры фон Неймана, универсальные вычислители, то сейчас, в связи с тем, что рост производительности микропроцессоров более-менее закончился, его улучшение ожидается только за счёт специализации компьютерного железа. Примером тому могут быть графические процессоры, нейропроцессоры, тензорные (очень близки к нейропроцессорам) и data-процессоры (для обработки сетевых данных). Вы можете сказать, что специализированные архитектуры — это удел ASIC (Application-Specific Integrated Circuit). Это, действительно, так, но ASIC не программируемы. А хотелось бы совместить специализацию по областям с программируемостью.

Обращу также ваше внимание на специализированную архитектуру, которой уже, наверное, сто миллионов лет. Это человеческий мозг. Я не хочу сказать, что это доказывает, что специализированная архитектура – будущее микроэлектроники, просто иллюстрирую тот факт, что в голове у нас находится очень успешная специализированная архитектура.

Особенности RISC-V

Что такое RISC-V? Ещё в восьмидесятые годы ученые из университета Калифорнии в Беркли начали говорить о том, что упрощенные наборы команд превосходят сложные системы. RISC лучше, чем CISC. И это было доказано развитием микроэлектронной индустрии.

Почему RISC-V? Начиная с 80-ых годов и где-то до 2010 года эти парни из Беркли сделали несколько наборов архитектур и номер пять является их последней архитектурой. Она получила очень большую популярность, стала бурно развиваться, и теперь о ней знают очень многие люди.

Почему же такая популярность? Созрела потребность в открытой и свободной компьютерной архитектуре. Это хорошо работало в случае Linux, в случае движения открытых исходных текстов ПО. Это нравится академическим исследователям, это нравится маленьким компаниям. Далее интересна масштабируемость от микроконтроллеров до серверов — от «края» облака до самого облака, чтобы одна и та же архитектура покрывала самые различные приложения. Сейчас это не так. В серверах, в основном, используется архитектура Intel, в микроконтроллерах мы имеем ARM, MIPS (Microprocessor without Interlocked Pipeline Stages). Ещё одна важная вещь — компьютерная безопасность. Когда у вас открытые исходники, то их легче отладить. Если у вас открытые ядра, то никто не боится, что в них закладки.

Усложнения системы команд — накладные расходы с точки зрения компьютерного железа. В RISC-V отражен опыт десятилетий развития RISC-архитектур. При этом она простая, эффективная и мощная.

Международная организация RISC-V

Опыт работы с открытыми источниками ПО показал, насколько важно сообщество разработчиков. RISC-V имеет два смысла. Это набор компьютерных команд, а также международная организация RISC-V Foundation, которую недавно переименовали в RISC-V International. Она, собственно, контролирует эту архитектуру, но это не означает, что она препятствует её развитию. Каждый может стать членом этой организации, каждый может внести пассивный вклад в развитие архитектуры. И, что важно, организация старается позиционировать себя как политически нейтральная.

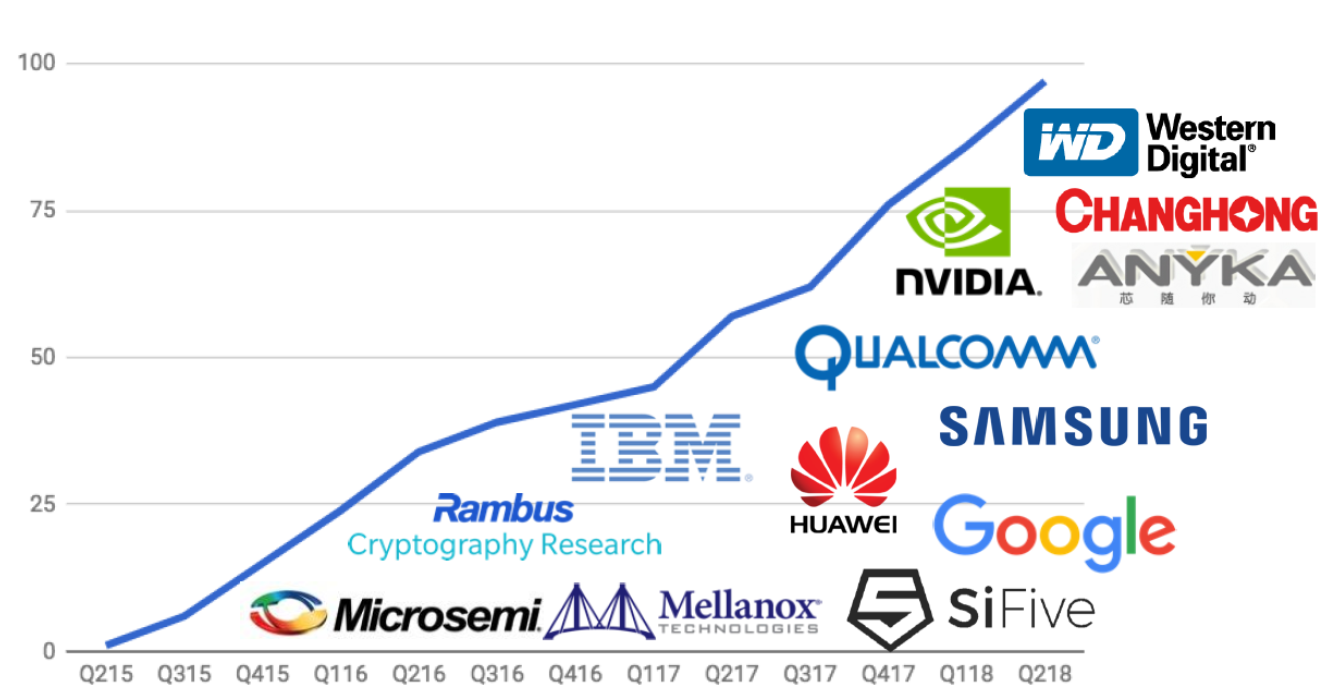

RISC-V International была создана в 2015 году. И сейчас она растёт очень быстро (смотрите рисунок 4).

Среди её членов, как маленькие компании, так и гиганты типа IBM, Samsung, Google. Профессор, который изобрёл эту архитектуру, создал компанию Silicon Five – очень известного, хотя и маленького игрока на этом фронте.

Об интересе со стороны крупных игроков говорят следующие факты:

Октябрь 2021 — Intel делает попытку приобрести SiFive;

Февраль 2022 — Intel объявляет о том, что инвестирует 1 млрд $ в развитие RISC-V;

Март 2022 — AMD размещает вакансии разработчиков RISC-V.

По состоянию на 2022 год она насчитывает 2,400+ участников и ~300 компаний. Такой рост позволяет нам говорить, что RISC-V – это серьёзно и надолго.

Характеристики архитектуры RISC-V

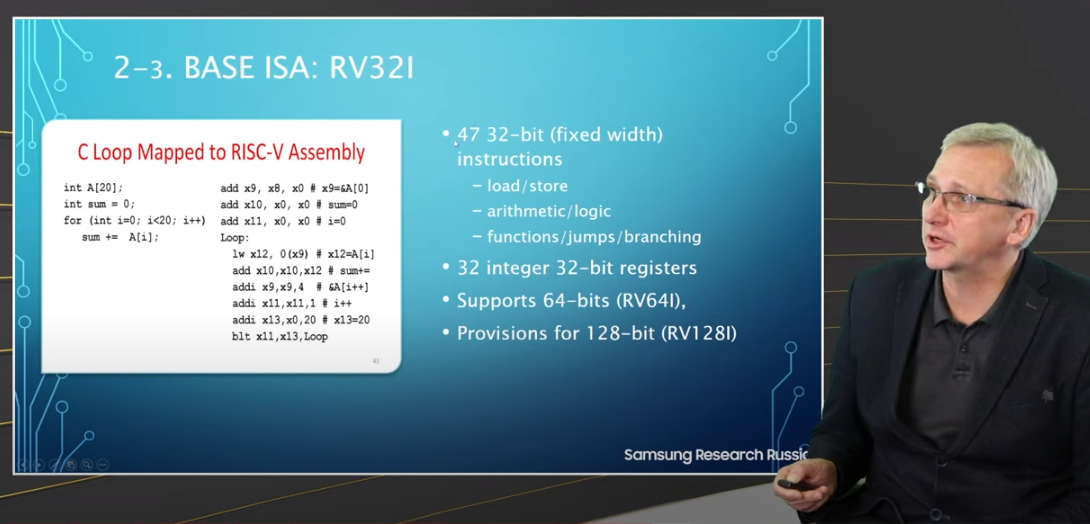

Не вдаваясь в технические подробности, остановлюсь на самых простых характеристиках архитектуры.

RV32I означает архитектуру RISC-V, 32-разрядную, I означает наличие целочисленной арифметики. Эти параметры — джентльменский набор для того, чтобы поднять операционную систему. Это базисная архитектура, которая позволяет запускать операционную систему на микропроцессоре.

Архитектура сама по себе очень простая. В ней всего 47 базисных команд. Эти команды фиксированной ширины по 32 бита. Это работа с памятью, арифметика, логика, работа с функциями. Архитектура поддерживает 32 32-битных регистра, архитектуру 64 бита (масштабирование очень важно), она будет называться RV64I. Также эта архитектура будет распространена на 128 бит (RV128I).

Простота важна, но также важна так называемая модульность. Если раньше компьютерные архитектуры были инкрементальными, то есть поверх старых команд добавлялись новые и в конце концов сложность архитектуры приводила к утере эффективности. В RISC-V уже не инкрементальная, а модульная система команд.

Что это означает? Базисная система команд может быть расширена. Возьмите только то, что вам нужно. Например,

M — целочисленное умножение и деление (RV32IM, то есть процессор, поддерживающий базисную RV32I и целочисленное умножение/деление);

F, D — вычисления с плавающей точкой (F — float, D — double);

A — атомарные операции с памятью (общая память);

C — сжатые 16-битные инструкции (для устройств Интернета вещей (IoT));

E — встраиваемые системы (например, только 16 регистров, это нужно для маломощных процессоров, в том числе для IoT (Internet of Things)).

Если вам нужно будет работать с IoT-устройствами, то стоит использовать расширения C и E.

Применение RISC-V для Интернета вещей

Почему я так убежден, что RISC-V идеально подходит для Интернета вещей? Прежде всего все знают, как в IoT важны низкие цены. Здесь мы имеем дело с открытой архитектурой, за которую не нужно платить лицензию, как в случае, если вы, например, работаете с ARM. Далее, эта архитектура оптимизирована под низкое энергопотребление. В силу модульности вы берете на свой микропроцессор только то, что вам нужно, используйте расширения, которые нужны в вашем приложении, а всё остальное вы можете выкинуть.

Одно из агентств, занимающееся аналитикой компьютерной индустрии, дало оценку того, как будет развиваться RISC-V к 2025 году. Согласно прогнозам, доля RISC-V в IoT будет приближаться к 30%, в то время, как в других вещах, таких как индустриальные применения и автомобили, проникновение RISC-V будет гораздо меньшим. Таким образом, взлет RISC-V я ожидаю в области именно Интернета вещей.

Что очень важно: Интернет вещей страдает тем, что компьютерные хакеры чувствуют себя там как дома. Это реально большая проблема. Большие компании не занимаются IoT, это удел маленьких компаний, там где мало ресурсов и мало специалистов по компьютерной безопасности, в результате Интернет вещей — это охотничьи угодья для хакеров.

RISC-V с самого начала проектировался так, чтобы обеспечить необходимый уровень защиты. Здесь по умолчанию есть поддержка Trusted Execution Environment (TEE), позволяющей разделить доверенный код от недоверенного. Она лежит в основе обеспечения компьютерной безопасности на уровне железа.

С самого начала архитектура RISC-V поддерживает привилегированное исполнение расширений и защиту памяти. Это неотъемлемая часть архитектуры RISC-V и это будет на всех уровнях, начиная от крошечных одноядерных микропроцессоров для Интернета вещей, заканчивая мощными серверными микроконтроллерами. В качестве примера приведу Secure IoT stack от компании Hex-Five.

Начало работы с RISC-V

Если вы хотите изучить RISC-V, то на рынке существует масса отладочных плат, на которых вы можете начать разработку. У организации RISC-V International есть веб-страничка, на которых содержится список плат для разработчиков.

Кроме того, эта организация имеет программу Developer Boards по раздаче плат первопроходцам (early adopters) и образовательным учреждениям. Если вы подадите заявку в RISC-V International и убедите её в том, что занимаетесь интересными с точки зрения организации вещами, то производители этих плат могут вам дать их бесплатно.

В качестве примеров я приведу знакомые многим платы:

Sipeed Maixduino Kit для AI + IoT под RISC-V;

Если RISC-V вас заинтересовала, то следующий шаг – это самообразование. Я бы рекомендовал взять онлайн-курсы. Привожу здесь два таких курса:

«Введение в RISC-V» о международном сообществе RISC-V на платформе EdX (это небольшой курс, можно пройти за день-два);

RVfpga: Complete Courses in Computer Architecture & SoC Design от Imagination Technologies, чтобы поиграться с RISC-V, если у вас есть опыт работы с FPGA (ПЛИС, Программируемые логические интегральные схемы). Здесь вы можете воссоздать RISC-V на FPGA и писать для него программы на ассемблере.

Если вы хотите почитать книги, то рекомендую следующие:

Харрис Д.М., Харрис С.Л., “Цифровая схемотехника и архитектура компьютера: RISC-V” (классическая книга по логическому дизайну, последнее издание посвящено архитектуре RISC-V, на русском вышла в феврале 2022);

D. Patterson, J.L. Hennessy, ”Computer Organization and Design RISC-V Edition: The Hardware Software Interface” (от создателей архитектуры RISC-V, на русский язык пока не переведена);

D. Patterson, A. Waterman, “The RISC-V Reader: An Open Architecture Atlas”; (атлас, в деталях рассказывающий об устройстве архитектуры RISC-V, на русский язык пока не переведена).

Также мне нравится Telegram-канал, который ведёт преподаватель МИЭТ Михаил Попов, рассказывая о компьютерных архитектурах на примере RISC-V.

Спасибо за внимание!

Об авторе

Станислав Владимирович Полонский

Руководитель управления перспективных исследований и разработок Исследовательского центра Samsung в России

Канд. физ.-мат. наук

Комментарии (38)

safari2012

31.05.2022 20:23рост производительности микропроцессоров более-менее закончилсяя бы сказал "замедлился"

checkpoint

01.06.2022 00:42+10RV32I означает архитектуру RISC-V,

32-разрядную, I означает наличие целочисленной арифметики. Эти параметры

— джентльменский набор для того, чтобы поднять операционную систему.

Это базисная архитектура, которая позволяет запускать операционную

систему на микропроцессоре.Здесь серьезная неточность. RV32I это минимальный минимум, всего 38 инструкций! Этого набора недостаточно для того, что бы запускать операционную систему общего назначения с виртуальной памятью (ОС Linux). Для такой ОС требуется поддержка расширений из набора RV32GC. Буква C - это обязательная поддержка системы сжатия иструкций (compressed commands). Буква G - это совокупность букв MAFD, которая расшифровывается так: M - "умножение и деление", A - "атомарные инструкции", F - "операции с плавающей точкой" и D - "операции с плавающей точкой двойной точности". При этом, когда мы говорим о RV32GC (RV64GC или RV128GC) подразумевается, что система-на-кристалле снабжена блоком управления памятью (MMU) который обеспечивает виртуализацию адресного пространства. Блок MMU не имеет своих инструкций по этому не является одним из стандартных расширений RISC-V, но его наличие является обязательным для современных операционных систем.

PS: Для желающих пощупать Linux на живом микроспроцессоре RISC-V есть одноплатный ПК Sipeed Lichee RV на базе СнК Allwinner D1 который содержит ядро RV64GCV (V - векторые вычисления).

amartology

01.06.2022 01:01+4Здесь серьезная неточность. RV32I это минимальный минимум, всего 38 инструкций! Этого набора недостаточно для того, что бы запускать операционную систему общего назначения с виртуальной памятью (ОС Linux).

В процитированном вами сообщении ни слова про Линукс или про другие «ОС общего назначения с виртуальной памятью». Маленькие RTOS для эмбеддед — тоже ОС )

checkpoint

01.06.2022 01:15-3И даже MS-DOS тоже операционная система, только родом из 80-х. Тем не менее в современном мире под ОС понимается как минимум Linux (а чаще - Windows). Таким образом утверждение "Это базисная архитектура, которая позволяет запускать операционную систему на микропроцессоре" вводит неискушенного читателя в заблуждение.

amartology

01.06.2022 01:36+4Тем не менее в современном мире под ОС понимается как минимум Linux (а чаще — Windows).

Нет.

Ну просто нет.

В современном мире гораздо больше копий ОС в разной встраиваемой технике, чем копий windows. И целевая аудитория этой статьи — не обыватели с ютубчика, а люди с айтишным бэкграундом, понимающие, что такое ОС для встраиваемой техники. Иначе зачем им вообще понимать, в чем преимущества RISC-V перед другими ISA?

checkpoint

01.06.2022 03:33+3Уровень статьи - для студента с ардуиной. В целом про RISC-V не написано ничего, кроме того, что это бесплатно и за этим будущее. По этому не надо убеждать меня в том, что автор имел в виду различные специализированные ОС и нацеливался на разработчиков микроархитектур.

PS: В "различной встраиваемой технике" сейчас копий Linux-а существенно больше чем всех остальных ОС вместе взятых.

nixtonixto

01.06.2022 12:59Зачем условной стиральной машине Линукс? Там максимум FreeRTOS, а может быть и вообще самописная машина состояний. Линукса начинаются на девайсах с большим цветным экраном и типа серверов-роутеров, а натягивать Линукс на 64 кБ проц с ОЗУ 8 кБ — только портить…

checkpoint

01.06.2022 15:32Затем, что программировать под Linux гораздо проще чем под FreeRTOS во всех аспектах. Потому, что современное поколение программистов ничего кроме Python-а не знает. Я не поддерживаю такую всеобщую линуксовизацию, но ни Вы ни я повлиять на эти тенденции не можем.

nixtonixto

01.06.2022 15:40В массмаркете на первый план выходит экономия каждого цента, поэтому там скорее запаяют 4-битный микроконтроллер с ОТР-памятью и программисты программно натянут на него ФФТ и плавучку, чем поставят монстра с Линуксом ради облегчения программирования. Поэтому, чем крупнее компания — тем громче стон из её отдела разработок.

checkpoint

01.06.2022 16:19+1Монстр с линуксом сейчас стоит столько же сколько и 4-битный микроконтроллер. Так, что все экономические прелести от удешевления аппаратуры давно нивелированы высокой стоимостью разработки ПО. Более того, сопровождать ПО написаное под Linux существенно дешевле чем натянутое каким-то одним гением FFT на сову, и найти таких людей проще. Гения нет и начинай разработку сначала. Я в своей практике постоянно сталкиваюсь с заказчиками, кторые приходят и говорят "вот нам тут кто-то что-то когда-то разработал для PIC, нельзя ли доработать и добавить пару простеньких но очень нужных фич ?". Ответ всегда один - "можно, но стоимость таких работ превысит стоимость разработки нового изделия на более современной базе с Linux-ом".

Demonter

01.06.2022 19:28+2А кушает монстр с линуксом столько же, сколько и 4-битный микроконтроллер? И обвязки никакой дополнительной не требует? И несколько лет без перезагрузки проработает?

Всему своё место. На чипах под линуксом периодически приходится с ОС бороться за риал-тайм исполнение чего-нибудь, часто именно по причине того, что зачем-то заложили линукс. Но богатая периферия и дополнительные ядра в таких чипах спасают, да.

checkpoint

02.06.2022 01:18-1Дак вопрос надежности уже давно никого не беспокоит - чем чаще железяка ломается, тем лучше - это же понятно даже школьнику. ;) Риал-тайм ? Накиньте больше ядер и все дела. :-)

С ядром Linux-а действительно очень много борьбы. Но так как этой борьбой занят почти весь окружающий мир, то вопросы решаются достаточно быстро. Проблемы начинаются тогда, когда заказчик хочет пересесть с одного дешманского китайского СнК на другой (например с Allwinner T2 на T3). Вот тут свистопляски с драйверами выползают по полной, так как T2 поддерживается последним ядром почти на 100%, а T3 - едва ли на 10%.

amartology

03.06.2022 09:34Вы классно обошли вопрос энергопотребления больших чипов)

А он, тем временем, с распространением IoT становится все актуальнее и актуальнее.

checkpoint

03.06.2022 12:50Это была шутка юмора, или попросту сарказм.

Я прекрасно понимаю все проблемы связанные с "большими чипами", но тенденции таковы, что труд программистов умеющих "натянуть сову на глобус" обходится существенно дороже, и найти таких очень и очень не просто. По этому в подавляющем большинстве имеем Linux и Python там, где без этого можно обойтись.

vadim100

01.06.2022 10:45+1Мне эти утверждения, что RISC лучше CISC непонятны. Да меньше инструкций и быстрее типа CISC, но для того чтобы сделать на малом наборе инструкций что-то надо писать больше кода. Получается меньше аппаратной части, больше программной и где выгода? В скорости точно выгоды не будет. Ну да ARM взлетел и Apple даже ноут выпустила на M1, но для каждой области своя архитектура важна.

nixtonixto

01.06.2022 13:11+2Для того, чтобы на CISC раскрыть все возможности архитектуры — это должен уметь компилятор и программист должен знать нюансы архитектуры, чтобы писать код под неё. Например, в одном из 8-битных семейств контроллеров есть команда «декремент и переход, если равно нулю» — в итоге цикл со счётом от n до 0 выполняется на 1 машцикл быстрей, чем цикл со счётом от 0 до n, где добавляется команда «сравнение с константой n». Но направление счёта должен выбрать программист.

По факту компиляторы оптимизируют далеко от идеала, даже на более примитивных платформах типа STM32, поэтому разница получается не очень заметной.

Brak0del

01.06.2022 13:19+4но для того чтобы сделать на малом наборе инструкций что-то надо писать больше кода.

Чуть больше кода (до 10% что ли) придется рожать компилятору и ассемблерным прогерам, для остальных не изменится ничего. С учётом ограниченного количества регистров общего назначения в типичных x86 и, как следствие, перекидывания операндов из регистров в память, кода там вообще может получиться одинаково.

Получается меньше аппаратной части, больше программной и где выгода? В скорости точно выгоды не будет.

Будет. Скорость определяется несколькими факторами.

Скорость в случае конвейеризации и out-of-order выполнения достигается за счёт извлечения максимального количества параллелизма из инструкций и высокой тактовой частоты. В случае CISC эти инструкции большие и очень разнородные, параллелизм извлекать сложно, нужно учитывать большое количество их правил. В случае RISC инструкции предельно простые и однородные.

Понимая это и стремясь извлечь больше параллелизма из CISC, начиная где-то с 90-х проектировщики CISC-процессоров под капотом раскладывают инструкции на маленькие RISC-подобные микрооперации, при этом имея много гемора с декодингом разнокалиберных CISC-инструкций, выборкой на границе строк кэша, режимами адресации с памятью, спекулятивным выполнением этого всего и откатом в случае ошибок предсказаний (многочисленные примеры проблем есть в этой книжке). Логика для этого не только занимает место на кристалле, но и ухудшает тайминги -- тактовую частоту, и как следствие бьёт по скорости.

Выбрасывание большого количества логики в случае RISC позволяет помещать ешё и более крупные кэши на кристалл, что тоже даёт буст к скорости, за счёт уменьшения числа промахов кэша.

checkpoint

01.06.2022 16:06+2Выгод несколько:

1) Меньшая площадь кристалла, меньшее потребление, дешевле производство. Избыточную площадь можно задействовать под дополнительный кэш или под большие регистровые файлы (хотя от этой идеи отказались из-за проблем с переключением контекста в многозадачных ОС).

2) Более узкие ступени конвейера позволяют достигать тактовых частоты существенно выше чем у CISC (5ГГц и выше).

3) Простота исполнения. Как следствие - меньше трудозатрат, меньше штат разработчиков, цикл разработки существенно короче, продукт быстрее выводится на рынок.

Тезис о том, что для RISC нужно больше инструкций чем для CISC что бы выполнить одну и туже работу давно не соответствует действительности - RV64GC решает эту задучу успешно за счет instruction compression и macro-op fusion. Объем бинарного кода стандартной библиотеки Linux-а для RV64GC на 30% меньше чем для AArch64, в пересчете на мегагерц она исполняется быстрее и имеет меньший отпечаток в оперативной памяти.

Вообще, что бы понять в чем суть идеи RISC нужно плотно ознакомиться с работами Дэвида Паттерсона и Джона Хэннесcи. Возможно, что автор этой статьи в следующих частях посветит нас хотя бы кратенько в суть этих работ, расскажет нам как создавалась система команд RISC-V, в чем её особенность и отличие от других, так же называющих себя RISC, систем. Почему в базовой версии всего 38 инструкций, а не 58 и не 25. Как организованы инструкции и почему в RISC-V ISA нет инструкции MOV.

И еще. Современные ARM ядра очень далеки от RISC. Система команд ARM это помойная яма, такая же как и x86.

byman

01.06.2022 19:07Современные ARM ядра очень далеки от RISC. Система команд ARM это помойная яма, такая же как и x86.

Если в RISC-V реализовать все расширения , то это будет такая же "помойная яма" как и ARM. Если сравнивать 38-инструкций RISC-V , то нужно брать у ARM версию v4. Отличная система команд и на ней когда-то работал Pocket PC.

checkpoint

02.06.2022 00:47+1От части Вы правы. Но нужно понимать, что все расширения набора команд RISC-V они очень минималистичны, добавляют только то, что нужно без избытка. Более того, все инструкции очень тщательно вымеряны и статистически обоснованы. К примеру, мне очень сильно нравится как сделано векторное раширение (RVV) - идея позаимствована у Сеймура Крэя и его машин из 80-х, но доведена до совершенства.

С моей точки зрения, среднестатистический процессор общего назначения архитектуры RISC-V должен соответствовать RV64GCV, это около 70 инструкций. Для сравнения, ARMv8 (A64) содержит целых три набора системы команд в сумме более тысячи инструкций. В ARMv9 накинули еще пару десятков. Так же в ARM есть множество недокументированных (hidden) инструкций, что, по мимо всего прочего, представляет брешь в безопасности.

И еще момент. В RISC-V нет флагов. Флаги это большая заноза для разработчиков суперскалярных OoO микроархитектур так как тянет неявные зависимости между инструкциями, что делает планировщик (декодер) очень сложным. Разрабочики RISC-V ISA решили избавить проектировщиков будущих микропроцессоров от этой проблемы, что, теоритчиески, позволит увеличить производительность при меньших аппаратных ресурсах.

byman

02.06.2022 11:59С моей точки зрения, среднестатистический процессор общего назначения архитектуры RISC-V должен соответствовать RV64GCV, это около 70 инструкций.

G это IMAFD. Простой пересчет строчек в таблице дает 159 команд. Расширение С - 49 строк в таблице. Хотя , С-команды это просто конвертор в обычную команду и её можно даже не считать за код. Количество векторных команд подсчитать сложно, т.к. куча всевозможных вариаций и непонятно как их считать и сравнивать с ARM.

все расширения набора команд RISC-V они очень минималистичны

Если , для примера, взять расширение В, то даже в нем можно увидеть несколько подрасширений :) Обязательная часть и необязательная. Я не представляю как в таких условиях писать софт.

Если взять расширение Р, то на нем можно запросто сгородить полноценный DSP-процессор. Получается , что нет никакого минимализма, а есть попытка покрыть своим знанием все что есть на текущий момент в микропроцессоростроении. И это конечно же не конец. Как только у конкурентов появляется что-то интересное, мы тут же увидим новое расширение RISC-V :)

checkpoint

02.06.2022 12:52Я считал по опкодам и у меня получилось 71 инструкция. Каждая инструкция имеет параметр function которая задает режим её работы. Если рассматривать комбинации opcode + function, то получится около 300 вариантов.

Если , для примера, взять расширение В, то даже в нем можно увидеть

несколько подрасширений :) Обязательная часть и необязательная. Я не

представляю как в таких условиях писать софт.Так как архитектура находится в движении, то писать софт нужно ориентируясь на конкретное железо. Полагаю, что со временем все устаканится, будут приняты/рекомендованы "суповые" наборы расширений типа RV64GC.

Получается , что нет никакого минимализма, а есть попытка покрыть своим

знанием все что есть на текущий момент в микропроцессоростроении.Люди пытаются систематизировать накопленные за 50 лет знания и опыт в микропроцессоростроении - откинуть все лишнее, остальное огранизовать так, что бы была система, с прицелом на упрощение аппаратной реализации. И сделать это доступным для всех.

И это конечно же не конец. Как только у конкурентов появляется что-то интересное, мы тут же увидим новое расширение RISC-V :)

Я наблюдаю обратную тенденцию: ARM начал вычищать свою ISA и делать её более похожей обратно на RISC. А последнее расширение SVE2 так вообще полностью скопировано с RVV. К чему бы это ?

byman

02.06.2022 14:54откинуть все лишнее, остальное огранизовать так, что бы была система, с прицелом на упрощение аппаратной реализации

Я с вами полностью согласен. Плюс еще чтобы и с компиляторами было проще. Но я не согласен только с одним - отбрасывая "что-то лишнее" не стоит говорить, о чем-то гениальном. Наблюдается обычный эволюционный процесс.

byman

01.06.2022 19:18Тезис о том, что для RISC нужно больше инструкций чем для CISC что бы выполнить одну и туже работу давно не соответствует действительности - RV64GC решает эту задучу успешно за счет instruction compression и macro-op fusion.

В вопросе размера кода macro-op fusion вообще не при делах. Это совсем другое. Расширение "С" это конечно хорошая штука, но лично я думаю, что в данном случае решающее значение в размере кода за хорошей командой компиляторщиков и довольно удобной для компилятора архитектурой (около 30 рон).

checkpoint

02.06.2022 00:01В вопросе размера кода macro-op fusion вообще не при делах.

Очень даже при делах. Вот небольшая презентация от Отцов Основателей на эту тему, в конце очень много интересной статистики: https://riscv.org/wp-content/uploads/2016/07/Tue1130celio-fusion-finalV2.pdf

И Вы совершенно правы, RISC-V ISA разрабатывалась для компиляторов без ненужного и давно забытого багажа, как у ARM и x86.

byman

02.06.2022 12:24Спасибо за ссылку на презентацию. Ваша ссылка на macro-op fusion ввела меня в заблуждение. Там вроде в основном о технике, как несколько инструкций кода сжать внутри процессора в одну операцию. Соответственно это не имеет отношения к размеру кода. Но есть еще и другой fusion , который как раз подходит. Это объединение пары типовых команд в одну. Как пример, сравнение а затем переход, у RISC-V это одна команда. Подобный fusion действительно сокращает размер кода.

YuriPanchul

02.06.2022 04:58+4К сожалению, для того чтобы нормально ответить на это вопрос, нужно рассмотреть не только архитектуру (систему команд), но и микроархитектуру (структуру конвейера процессора). Если одной фразой - RISC процессор проще конвейеризировать чем CISC, откуда следует его более высокая энергоэффективность (за счёт уменьшения размера и уменьшения количества переключающейся каждый такт логики), а также следует существенно меньшее количество инженерных ресурсов (человеко-лет) на его проектирование и верификацию.

...... Пропускаю несколько страниц объяснений ....

Таким образом, для реализации CISC необходимо не только изменить front-end процессора (стадии выборки и декодирования инструкций), но и протащить связь исходных инструкций с декодированными микроинструкциями до самого конца конвейера для корректной отмены инструкций в случае возникновения прерывания. CISC также усложняет предсказатель перехода и другие части процессора. CISC сложнее в верификации (= требует бОльших инженерных ресурсов).

Конкретно у x86 при этом ещё и недостаток количества регистров. Двухоперандные команды требуют более сложных байпасов и переименования регистров (алгоритм Томасуло или эквивалент).

Помимо описанных недостатков для процессоров десктопного класса, существует ещё более серьезные недостатки для встроенных процессоров и ядер для микроконтроллеров.

Малое RISC ядро может спроектировать даже один проектировщик и хорошо верифицировать небольшая группа людей. Для x86 это не так даже малое ядро будет сложным и как минимум, проигрывать в энергоэффективности.

YuriPanchul

02.06.2022 06:04+2Если пытаться объяснить с минимумом слов: в RISC (по сравнению с CISC) проще организовать как выполнение инструкций с перекрытием выполнения по времени (пока одна инструкция декодируется, другая выполняется) - конвейерность, так и выполнение инструкций параллельно с учётом зависимостей между ними - суперскаляр.

Это "проще" значит как "с меньшим количеством транзисторов" так и "с меньшим количеством инженеров".

БОльший параллелизм у RISC как в смысле конвейерности, так и в смысле суперскаляра (если сравнивать процессоры с одинаковым количеством транзисторов и одинаковой тактовой частотой) компенсирует его меньшую плотность кода, чем у CISC (где нужно меньше инструкций, чтобы выполнить то или иное действие). Это доказано некоей статьей 1990-го года (могу нарыть - до нее 10 лет спорили на тему) и последующими исследованиями)

Побочным эффектом от этого является бОльшая энергоэффективность RISC (производительность / милливатт).

beduin01

01.06.2022 12:21А есть cisc с осовремененным набором команд?

amartology

01.06.2022 16:29x86, разумеется)

И наиболее навороченные разновидности ARM по факту ближе с CISC, чем к RISC.

beeruser

02.06.2022 01:33Это показательный пример того, как важно поддерживать наборы компьютерных команд как можно более простыми.

Вообще это ни из чего не следует. Так вы до OISC докатитесь.

Во всём нужен баланс. ARMv9 это большой и прагматично созданный набор команд.

Некоторые команды ARM могут заменять несколько команд x86 или RISC-V.

code07734

02.06.2022 04:15Некоторые команды ARM могут заменять несколько команд x86 или RISC-V.Интересно какие.

Вы всегда про armv8-9 говорите, какой он прагматичный и эффективный. Интересно увидеть пример

Так может к oisc однажды и придёт всё

jaha33

А разве "модули" не платные? Насколько я понимаю в арме платят за использование ядра, а у Risc-V, так сказать, "база" предоставляется бесплатно, но различные расширения надо уже приобретать

byman

Никогда не слышал про оплату расширений.

Открыта и свободна. .

вот про пассивный вклад хотелось бы поподробнее.

amartology

Вся система команд, включая все расширения, бесплатна. За деньги можно купить конкретные реализации, как расширений, так и базовой системы команд. Но если платить не хочется, то никто не запретит вам реализовать любую конфигурацию самостоятельно.