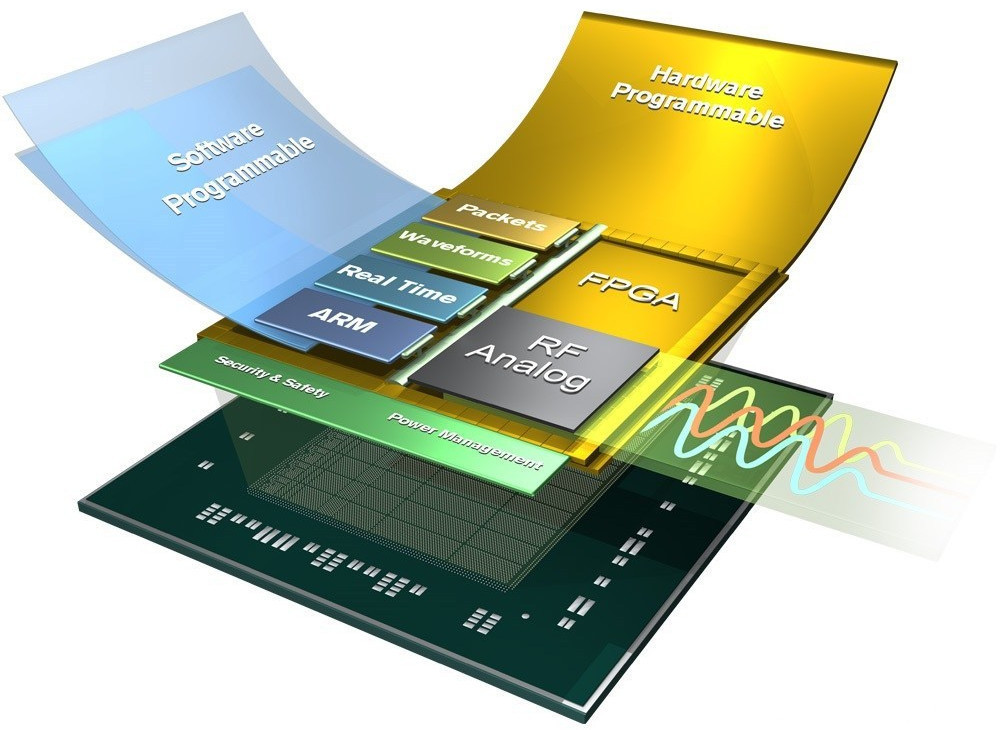

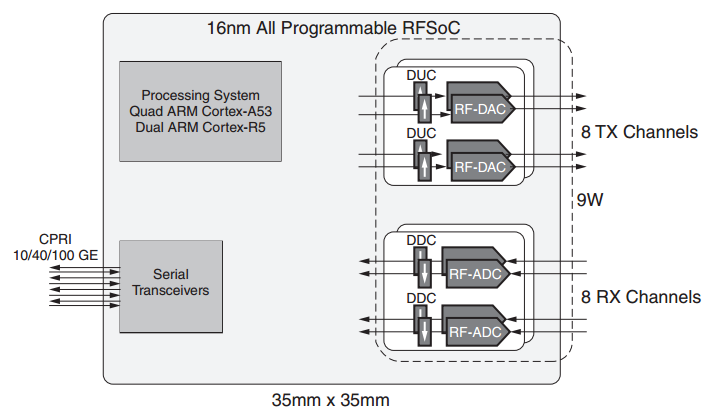

Компания Xilinx тихо и без лишней помпы анонсировала продукт, который может полностью изменить облик и процесс разработки современных радиоприемников и передатчиков. Это маленькая микросхема, которая объединяет 90% вопросов обработки и формирования радиосигналов:

- программируемая логика (FPGA),

- процессоры для обработки сигналов и пользовательских приложений (два ARM’а),

- до восьми 12-разрядных АЦП с частотой дискретизации до 4 ГГц (!),

- до восьми 14-разрядных ЦАП с верхней частотой до 6.4 ГГц (!).

Кажется мы входим в эпоху, когда архитектура трансивера становится такой же универсальной, как архитектура современного ПК. Make SW, not HW!

Эра до Zynq’а

Немного истории. Я представитель небольшой команды, основная деятельность которой в течение последних 10-15 лет — это R&D в области спутниковой навигации.

Чего только мы ни делали за это время! Разрабатывали новые сигналы для ГЛОНАСС, обрабатывали все возможные сигналы, имитировали сигналы навигационных систем, делали системы для обнаружения помехопостановщиков, мастерили микросхемы для антенных решеток, делали приемники размером с телевизор для квантово-оптических станций. В общем, по нашим приключениям смело можно писать Камасутру сигнальной обработки (что мы и сделали)!

Понятно, что при таком зоопарке задач мы никак не можем обходиться стандартными приемниками. Мы любим и знаем модули Геос и NV-08C, даже поучаствовали в этих проектах, но для своих проектов мы всегда использовали собственные разработки.

Единственный способ сделать мелкосерийный приемник — основываться на ПЛИС (FPGA). Тут стоит пояснить, что процесс обработки современных сигналов напоминает работу компьютерной графики. Операции относительно простые, но их нужно делать очень много параллельно. В этом смысле FPGA (или кусок кремния в крупной серии) для приемника как GPU для современного компьютера.

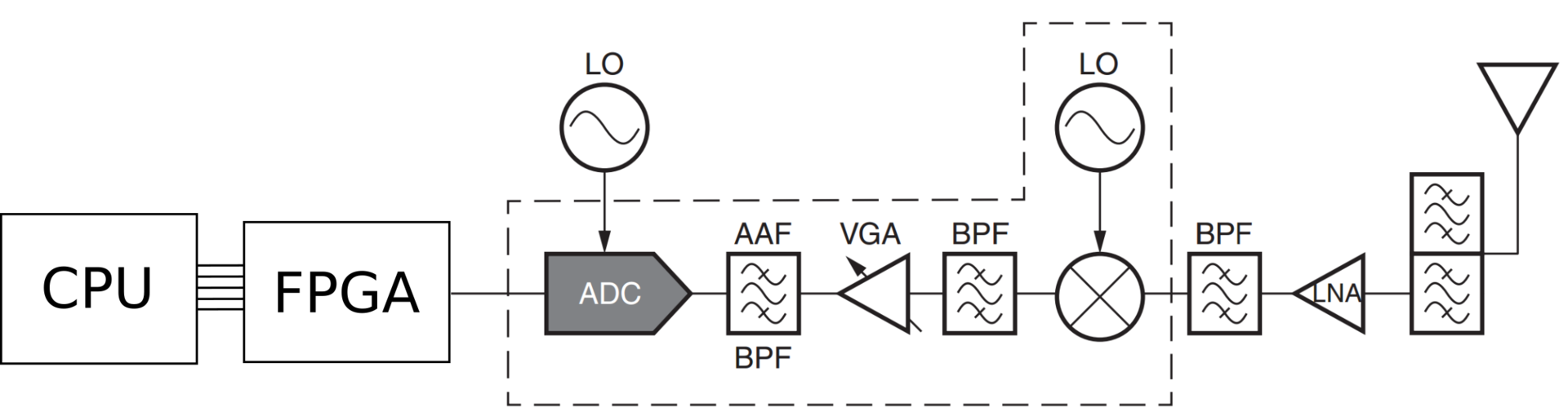

Как же выглядела структурная схема приемника лет так десять назад?

Что плохого в этой схеме? Процессор и программируемая логика разнесены в разные микросхемы. И это порождает кучу проблем.

Специфика обработки сигналов требует постоянного обмена данными между процессором и ПЛИС в режиме строгого реального времени! Потоки для навигационного приемника достигают нескольких гигабит.

Каждая микросхема требует своей обвязки, охлаждения, многослойной платы для соединения и банально занимает место на печатной плате.

И в конце концов, это просто сложно. А сложность в построении систем почти синоним провала.

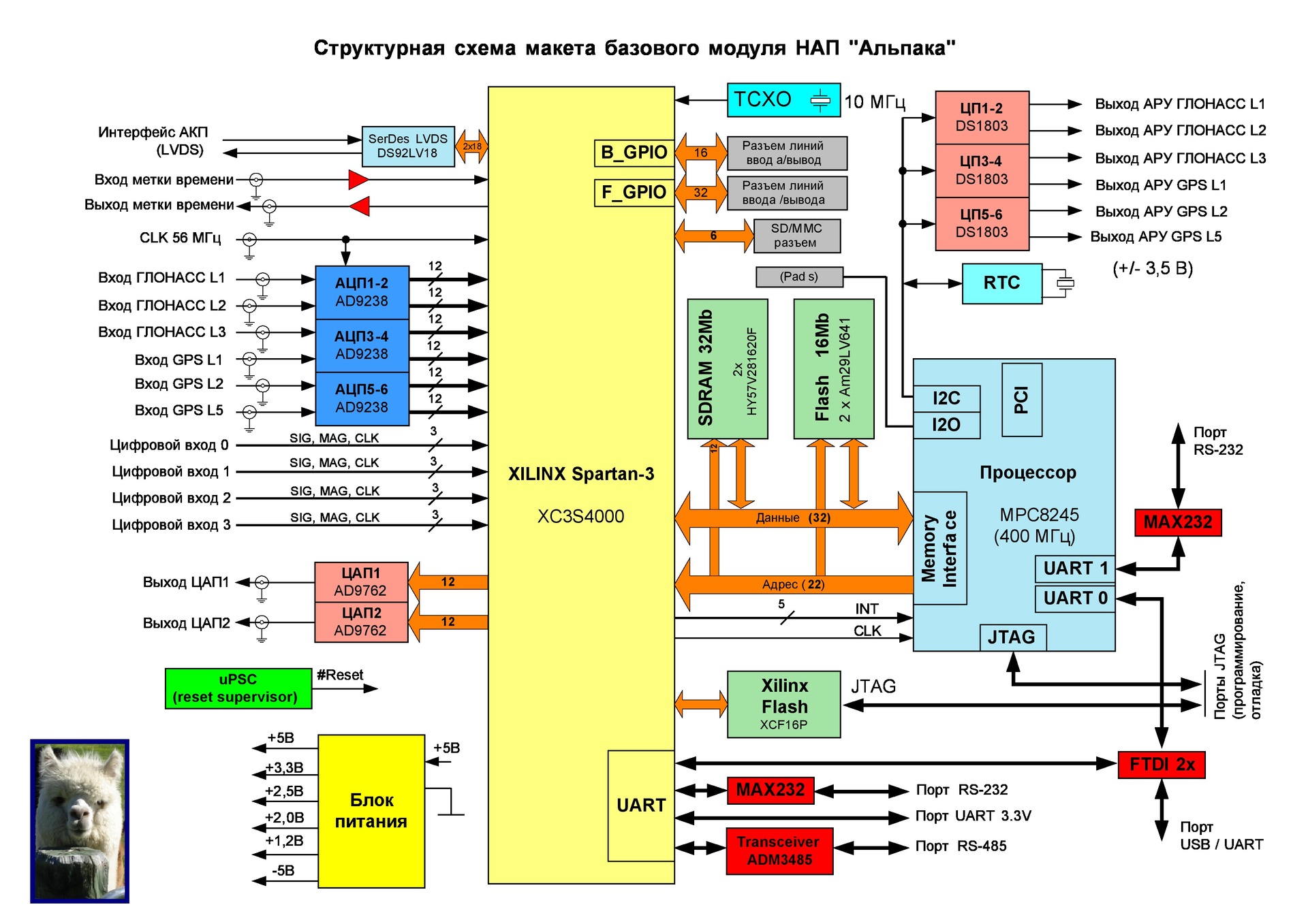

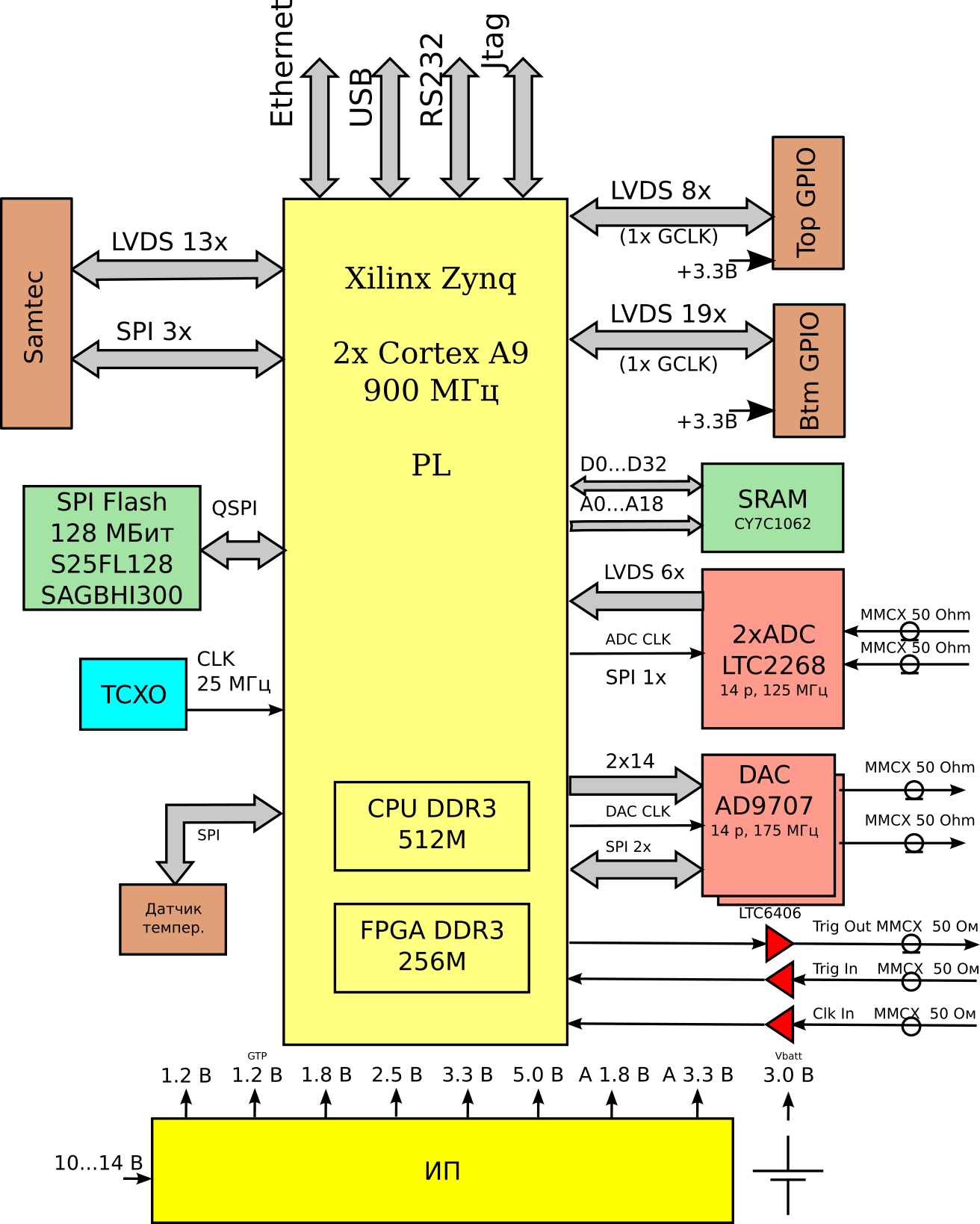

Например, структурная схема приемника, который мы делали в 2007 году:

В качестве FPGA использовался Xilinx Spartan 3, в качестве процессора — здоровенный PowerPC в виде MPC8245. Ушла куча времени на перенос toolchain’ов, поиск драйверов, организации обмена между ПЛИС и процессором и т.д.

Но внезапно мир изменился…

Появление SoC, объединяющих программируемую логику и процессорную систему

Описанная выше боль характерна для мелкосерийного производства и прототипирования. Для связки отдельный FPGA + отдельный CPU характерна высокая себестоимость, дикое потребление и габариты. А что ещё хуже, программная часть продукта была непереносима. Для каждой новой комбинации приходилось переписывать большую часть софта.

Как только продукт мог отбить производство ASIC’а, то производитель разрабатывал собственную микросхему. В такой микросхеме объединялась вся цифровая обработка: АЦП на промежуточную частоту, параллельная логика цифровой обработки, процессор, интерфейсы. По такой схеме построены все современные навигационные чипы.

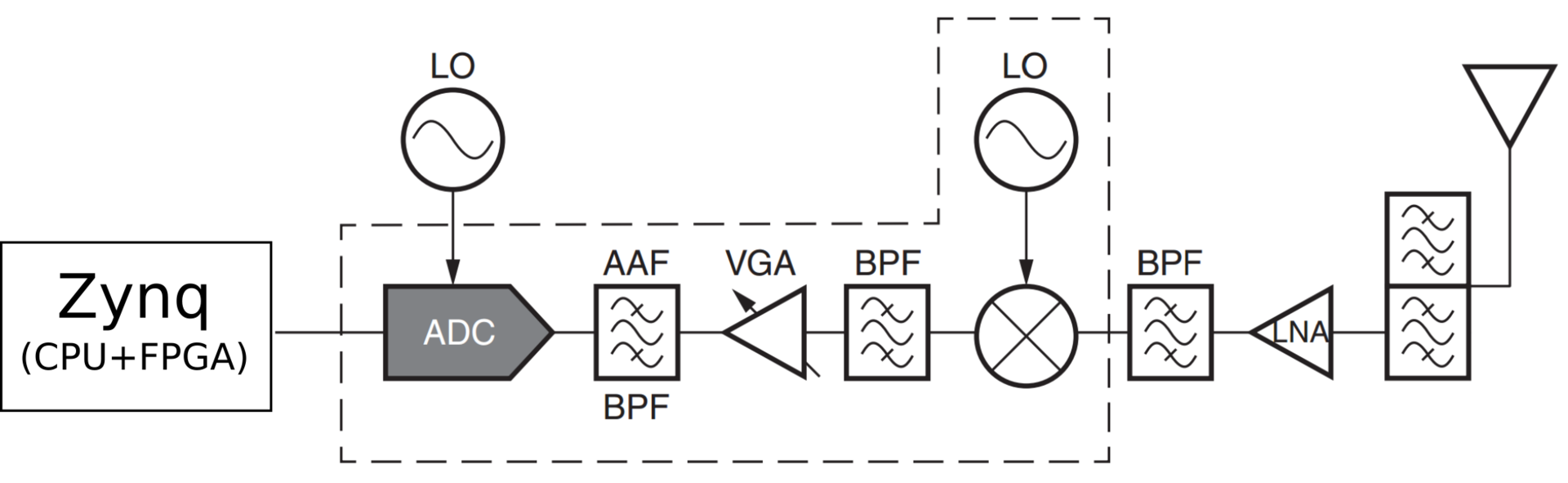

В начале 2010-х Xilinx и Altera анонсировали продукты, которые решили половину наших проблем. Компания Xilinx начала выпускать микросхемы серии Zynq, объединяющие в себе программируемую логику (FPGA) и процессорную систему (двухядерный ARM с полным набором периферии).

Система на кристалле Zynq была огромным шагом вперед. Существенно упростился код, поднялась скорость обмена между процессорной системой и программируемой логикой, упростилась печатная плата. Например, структурная схема одного нашего проекта в 2013 году, почувствуйте разницу:

И самое главное, неожиданно родилось новое качество: теперь наш софт запускался на любой плате с Zynq’ом.

В цикле разработки радиотехнического устройства написание алгоритмов и софта, сопутствующие исследования, отработка занимают 80% времени. Если Java — это cross-platform, то Zynq — это cross-board. Теперь мы можем переложить разработку платы на заказчика, а сфокусироваться на главном — софте.

Кроме того, Xilinx взял на себя вопросы toolchain’ов, драйверов и прочие далекие от радиотехники проблемы.

Через пять лет после запуска Zynq’ов появилось интересное явление — коммерческие продукты на базе программируемой логики. Примером может служить Piksi Multi или Tersus Precise. Да, эти приемники всё ещё потребляют больше аналогичных, построенных на ASIC. Но цена стала сравнима! Маленький Zynq с небольшим количеством программируемой логики сейчас можно купить за $50! А это увеличивает число возможных приложений на порядки!

День грядущий…

Если учесть сказанное выше, то становится логично, что следующий шаг — добавить на кристалл АЦП и ЦАПы. Но компания Xilinx решила сделать сразу два шага вперед.

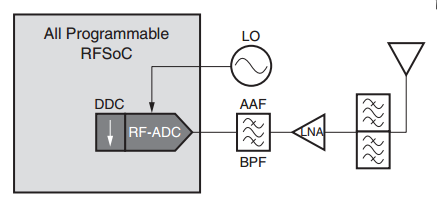

Тут чуть подробнее. Современные приемники или передатчики — это два мира. Цифровой и аналоговый. Например, рассмотрим приемник.

Аналоговый мир:

- антенна, преобразующая электромагнитное поле в электрический сигнал;

- фронтенд, функция которого — отфильтровать, усилить и понизить несущую частоту сигнала, чтобы его потянула цифровая обработка.

Стык между

Далее идет цифровой мир, реализуемый разновидностью компьютера.

Xilinx замахнулся на аналоговый мир!

АЦП с верхней частотой в 4 ГГц позволит переходить на цифровую обработку сразу на несущей! ЦАПы с верхней частотой до 6 ГГц — выкинуть все звенья до усилителя мощности.

И таких АЦП и ЦАПов — по 8 штук! Это закрывает вопросы с многоантенными системами, которые с каждым годом становятся всё актуальнее: MIMO, CRPA, Beamforming, определение ориентации и т.д.

Аналого-цифровые преобразователи реализованы на одной микросхеме, что обещает высокую идентичность их характеристик. При этом они обладают высоким динамическим диапазоном — порядка 65 дБ SFDR.

Таким образом, аналоговая часть приемника сводится до антенны, предварительных фильтров, предусилителя. В передатчике — до усилителя мощности и антенны. И одного этапа гетеродинирования, если ваши рабочие частоты выше указанных.

По заявлениям Xilinx, использование RFSoC позволяет существенно улучшить энергопотребление. В варианте с 8 АЦП и 8 ЦАП указывается энергопотребление в 27 Вт.

Как и в серии Zynq UltraScale, процессорная система представлена двумя процессорами — для радистов (двухядерный Cortex-R5) и для пользовательских приложений (четырехядерный Cortex-A53).

Резюме

Анонс Xilinx’а отражает общую тенденцию в радиотехнике — курс на унификацию и решения всё в одном. Лично мне это напоминает развитие компьютеров в XX веке. Какие последствия для индустрии принесло появления однотипных ПК, что стало с профессией программиста и как изменился мир — напоминать не требуется.

Главный вопрос теперь — а будут ли продавать нам это чудо? Остается надеяться на гражданскую версию за адекватные деньги.

Поделиться с друзьями

itsar

Спасибо! Я пропустил такую новость.

Но жрать такая штука должна очень много.

Для мобильных штук не пойдет, я думаю.

Korogodin

Да, этот изъян пока решается только выпуском ASIC'а. Но в мобильных приложениях прочно засели монстры типа Qualcomm, там тяжело конкурировать.

Другое дело возимые девайсы…

Jef239

27 ватт. Это не описка?

Korogodin

К сожалению, нет. Эта цифра вполне согласуется с моей практикой. У меня сейчас на столе лежит фронтенд на 8 голов, АЦП 14-разрядные. Ест 15 Вт. А в этой микрухе ещё ЦАПы.

Нынешний Zynq ест около 3-5 Вт в зависимости от нагрузки.

Jef239

Ну это означает, что на нем только военку сделать. Или всяких стационарных монстров. GEOS-3 берет где-то до 0.2 ватта, вот с ним и надо сравнивать…

Korogodin

Помимо перечисленных есть большой пласт возимых устройств: automotive, сельское хозяйство, стройка — интересные направления, где ещё не все карты разыграны.

Jef239

Вентилятор на стройке? Вентилятор на поле? Не, или вентиляторное охлаждение — или outdoor с пылью. :-)

Korogodin

Да, такая проблема есть. Младшие камни серии позволяют обойтись без вентилятора, но с топовыми такое не проходит.

В RFSoC у них каждый АЦП и ЦАП дает 1Вт потребления. Тогда для двухчастотного навигационного приемника (нужны только 2 АЦП) можно уложиться в 5 Вт.

Jef239

Ну в общем это не конкурент для GEOS. Вот если бы в тот же кристалл вторичку затолкать (тот же PPP-RTK или угломер) — вот тогда это конкурент нынешней схеме с двумя SoC (в приемнике и в плате).

У нас весь угломер укладывает в один-два ватта (могу уточнить у коллеги). То есть питаемся просто от штатного USB.

Надеюсь, что если частоту семплинга снизить до 80 мегагерц на канал, то энергопотребление придет в разумные рамки.

Korogodin

Потребление там высокое из-за многоразрядности, чтобы его снизить до привычного нам уровня нужно сделать два хода:

1. Понизить частоту

2. Снизить разрядность до 2

Ни того, ни другого не предвидится.

А вторичка в этот кристалл влезает с запасом!

Там два отдельных камня, каждый под ГГц.

Первый для решения вопросов радиотехники с двумя ядрами. Легко можно один забить под сигнальную обработку, второй под вторичку.

Но если этого не хватит — есть ещё пользовательский на 4 ядра.

Jef239

Проблема сделать угломер на одном устройстве — это проблема know how. Одни команды умеют делать первичку, другие вторичку. И каждая имеет вагон know how, которым очень не хочет делиться.

А потом — какие выгоды у угломера на таком ядре? Ну разве что размеры меньше.

1 бит дельта-сигма модуляции на 80 Мгц — вроде достаточно для GPS?

Korogodin

Этот чип просто снизит порог вхождения в тему. Как, скажем, снизила NT1065.

По сравнению с решениями на Геос и NV08C появится возможность работать по сигналам нескольких частотных диапазонов. L3 для угломера был бы сказкой — полоса большая, значительно многолучевость упадет.

Jef239

Можно подробнее про L3?

Korogodin

Сейчас спутников с L3 мало, но если бы он излучался каждым аппаратом, то мы бы получили сигнал с полосой в 20 МГц. А значит, в 10-20 раз меньше страдали от многолучевости.

У него есть и недостаток — длина волны побольше, но там несущественный проигрыш.

Jef239

Не понимаю, почему полоса в 20 мегагерц защищает от многолучевости? И в какой ситуации она защищает?

Улица идет с севера на юг, с двух сторон — железобетонные дома. Сигнал спутника с западной стороны идет через дом и сильно ослабляется. Он же = отражается домом с восточной стороны и приходит с уровнем повыше прямого приема.

Чем тут поможет широкая полоса?

itsar

Интерференционная картина очень зависит от частоты. В широкополосном сигнале будет некоторый узкий «выкол» в частотной области, но в целом энергия все же останется, а узкополосный сигнал может быть подавлен интерференционным нулём полностью.

NelSon29

> Улица идет с севера на юг, с двух сторон — железобетонные дома. Сигнал спутника с западной стороны идет через дом и сильно ослабляется.

Городские каньоны это отдельная головная боль в ГНСС. Однако, учитывая множественные переотражения перед приходом отраженного сигнала, он ослабляется до такой степени, что за ним становится проблематично следить. Основная проблема городских каньонов не в работе по отраженным сигналам, а по малому количеству видимых спутников вообще. Из-за этого страдает геометрический фактор и точность в целом. Японцы свою QZSS сделали именно для работы в таких условиях.

От многолучевости увеличенная полоса помогает следующим образом: при слежении многолучёвые сигналы воздействуют на основной только в пределах корреляционного пика (точнее даже будет сказать его спада, т.к. отражённый сигнал всегда приходит с задержкой). Чем шире полоса, тем уже корреляционный пик. Соответственно, при равных условиях, меньшее количество сигналов влияет на слежение.

Jef239

То есть вы хотите сказать, что влиять будет лишь многолучевость с небольшим временем задержки? А можно в цифрах? То есть что есть сейчас на L1 и что будет на L3?

Korogodin

Более-менее удается специальными методами обработки отсечь отраженные сигналы отстающие более чем на 1/5 длительности чипа. То есть с разностью хода более 100 метров для GlnL1OF и более 3 метров для GlnL3OC. А 3 метра — это уже окрестность потребителя, там всё понятно. На крайний случай, можно снять карту многолучевости и учесть в измерениях.

Jef239

А от фуры в соседнем ряду — удлинение 2-3 метра максимум. И никакой карты — нас фура просто обгоняет.

Если бы хоть информацию иметь, что на таком-то спутнике может быть есть многолучевость… Тогда можно было бы решиться на оставшихся спутниках и удержать фиксацию.

Примерно та же ситуация в точном земледелии. Подъехал грузовик к комбайну — и имеем многолучевость. Одно легче — комбайн повыше легковушки.

Korogodin

Согласен в целом с предыдущими ораторами, попробую ответить более развернуто.

Вами описан крайний случай многолучевости — NLOS, когда мы работаем по отраженному сигналу без прямого. Он самый неприятный, бороться с ним на этапе сигнальной обработки можно только пространственными методами.

Ситуация, когда все спутники NLOS, нетипична. Это indoor навигация по GPS, например.

Типичная ситуация в городских условиях для одночастотного приемника: принимаем пару систем, в сумме около 15 спутников.

Из этих 15 парочка сигналов с NLOS. Ещё около 5 находятся близко к зениту, получаем чистенькие сигналы, многолучевость минимальна (дБ на 30 и более ниже основного сигнала). Остальные — это что-то среднее, отраженные сигналы только на 5-20 дБ подавлены относительно прямого. В итоге мы следим за сигналом прямым, но отраженные постоянно «раскачивают» выход коррелятора, вносят систематические ошибки.

Сигналы с NLOS имеют большую ошибку, отбрасываются на этапе вторичной обработки по невязке решения, в итоговый расчет не идут.

Остаются сигналы чистые и подпорченные многолучевостью.

Увеличение полосы сигнала в 20 раз приведет к сужению корреляционного пика. Отраженные сигналы с большой разностью хода вообще перестанут нам мешать. Отраженные сигналы, которые все ещё будут попадать в пределы корреляционного пика, будут иметь в 20 раз меньший отклик по выходу коррелятора.

В общем, в среднем ситуация будет в 20 раз лучше :-)

Jef239

Нас больше всего интересует ситуация перескока между прямым сигналом и NLOS, то есть появление слипа. Если мы разрешаем фазовую неоднозначность, то как на этом этапе удалить NLOS-сигналы? Получаем фиксированное решение с NLOS и слипы при появлении-пропадании прямого сигнала.

Типовая ситуация — едем по дороге (даже в чистом поле). И тут нас обгоняет фура с металлизированным тентом. Мало того, что полнеба закрыла, так она ещё и отлично отражает сигналы со второй половины. И всё, полезли слипы.

Можно в цифрах, какую многолучевость можно будет отсеять на L3?

Ejny

Напрямую защищает, радионавигация — это не связь.

Если упрощённо, то отражённый сигнал, запаздывающий более, чем на один символ дальномерного кода, отсеивается приёмником. Проблема с теми отражёнными сигналами, задержка которых меньше длительности дальномерного кода. А полоса навигационного сигнала обратно пропорциональна данной длительности. В результате для сигнала GPS L1 C/A длительность символа 1 мкс, что в пересчёте на дальность составляет 300 м и это определяет зону, в которой отражённый сигнал мешает приёму. Для сигнала GPS L1 P/Y полоса в 10 раз больше, а длительность символа в 10 раз меньше (30 м), в результате чего снижается зона, в которой отражённые сигналы воздействуют на приёмник.

Это хорошо описывается графиком огибающей многолучёвости, например, таким:

https://www.hindawi.com/journals/ijno/2008/416380.fig.001.jpg

По оси абсцисс — задержка отражённого сигнала, по оси ординат — вносимая погрешность измерений. Чем меньше площадь по графиком — тем лучше.

В этом плане расширение полосы сигнала — наиболее эффективная мера.

Jef239

В переводе — в наших (RTK) условиях ни фига не защищает. Влияние многолучевости на фазу — от 2 до 8 сантиметров, дальнейшее характеризуется как слип.

Реально надо избавляться от многолучевости до 3-5 метров, вроде фуры, обгоняющей легковушку с RTK.

Ну или хотя бы иметь признак, что в сигнале есть многолучевость и он не очень достоверен.

Ejny

Ну я не утверждаю, что всегда помогает. Для RTK не поможет. RTK вообще практически тепличных условий требует.

Jef239

Ну как сказать… зависит от количества априорной информации. RTK по одной базе, когда ничего не известно — зверь капризнейший. А RTK на фиксированной базе (для компаса) умеет довольно быстро перефиксироваться. Что и спасает.

Про диссертацию Korogodin чуть-чуть в курсе, но это в практику через 20 лет пойдет…

Вот если бы по сигналу можно было бы определить — вот тут прямой прием, а тут — может быть есть многолучевость, то нам бы это прилично помогло. Интуиции что-то подсказывает, что это возможно…

Ejny

Кстати, Korogodin как раз сейчас работу пишет по использованию широкополосных сигналов (сотни МГц) на высокой несущей для навигации. Вот эти сигналы и позволили бы решать озвученную проблему 3-5 м. Но там свои сложности есть.

Korogodin

Оно поможет как раз снизить ту ошибку, которая сейчас 2-8 сантиметров. Плюс значительно снизит СКО кодовых измерений, а значит по разности код-фаза вам будет проще заметить cycle slip, что бы ни было его причиной.

Jef239

Мы на вторых разностях работаем… Но снижение СКО — это нам тоже полезно. А слипы мы ловил уже по остаткам после решения. До решения — только уж очень грубые слипы выкидываем.

Korogodin

А почему не смотрите на простую комбинацию «код минус фаза»? Она наглядна, низкодинамична, по ней большие слипы должны быть сразу видны.

Jef239

Большие слипы (от двух-трех циклов) — они везде видны. А вот слипы на один цикл и на половину цикла…

lelik363

При определенно сноровке можно попробовать кондуктивное исполнение.

Jef239

Там радиатор не нужен будет? При 27 ваттах?

Korogodin

Он уже нужен даже при нынешних 3 Вт на простом Zynq'е.

aamonster

А АЦП до 4 ГГц — это запредельные мегасэмплы в секунду (как это всё обработать-то?) или большая полоса пропускания + АЦП, "выхватывающий" полосу из сигнала (субдискретизация сигнала или полосовой сигма-дельта АЦП)?

Korogodin

Судя по таблицам, они предполагают порядка 100 Мегасемплов за счет digital down conversion. Тут возникает вопрос, как быть с фильтрами? Обеспечить нормальную фильтрацию на несущей тяжело. Пока не знаю, есть ли у них промежуточная фильтрация.

Mogwaika

Ну по первой ссылке пишут GSPS, хотя слабо верится…

Mogwaika

У вас на картинке с цинком DDR3 как-то неоднозначно нарисована, как будто она не на периферии висит, как и флешка. Или это контроллеры типа?

Korogodin

В том проекте мы использовали не сам Zynq, а процессорный модуль с ним. На нем уже висел DDR, поэтому на схеме получилось такое обозначение.

reversecode

кто первый наштампует плат на основе этого чипа по типу конструктора на rpi, тот срубит кучу бабла))

Korogodin

Думаю, что это будет Xilinx или его ближайшие друзья типа Digilent'а.

Mogwaika

У Xilinx будет слишком дорого и как rpi по цене и близко не получится, китайцы или digilent, думаю, могут сделать по цене как 10 rpi…

Korogodin

Есть такие ребята на CrowdSupply, которые сделали подобное на нынешнем Zynq'е. Получилось $100 (изначально отдавали за $55), крауд оказался успешным.

Правда они уже почти год нас «кормят завтраками», платы пока так и не приехали.

Mogwaika

Я redpitaya спонсировал, тоже долго слали…

Korogodin

Сейчас всё так быстро развивается, что задержка на год — смерти подобна.

blacklion

Я боюсь цены там будут такие, что никакой кучи бабла именно на платах по типу rpi или там HackRF/BladeRF не получится. Я смотрю на характеристики и вижу цены за чип порядка $10K и, думается мне, это я оптимист.

Это всё в радары, базовые станции (пикосоты) и прочее, тоже SDR, да другой.

Korogodin

Xilinx видит основной рынок в 5G сотовой связи.

$10к — перебор для Xilinx, это будет значительно дороже существующих аналогичных решений. Мне видятся $1k за младшие модели.

blacklion

5G — я и говорю, базовые станции, пикосоты (которые вроде как видятся будущим 5G сейчас), такое. Не клиентское оборудование.

Про цены — я, видимо, отстал от жизни. Да, я смотрел цены на ADC/DAC с такими характеристики последний раз года 2 назад, но тогда один канал на 4 гигасемпла в секунду 12-14 бит стоил больше тысячи. В любую сторону. А тут таких каналов 8+8 помимо всего остального (FIR-фильтр для DDC на такую скорость сколько коэффициентов будет?). И мне вот не очевидно, что проще сделать 8 каналов на одном кристалле, чем раздельно.

Какие сейчас есть существующие аналогичные решения? Ettus USRP X310 стоит почти 5 тысяч евро. И даже близко не приближается к параметрам этого чипа по DAC/ADC (хотя, конечно, это законченное решение, включая PCIe и 10G-трансиверы, а не один чип, но это всё будет нужно и решению на новой микросхеме).

Korogodin

Да, всё это будоражит! В качестве аргументов могу предложить следующее:

1. В младших моделях серии будет меньше АЦП и ЦАП.

2. Высокая цена существующих АЦП обусловлена маленькой серией, на которой им приходится отбивать высокий NRE. Если почитать IEEE'шную статью от Xilinx, там указано, что они умещают один канал на 1 кв. мм по 16 нм технологии. То есть себестоимость непосредственно производства будет не велика. А дальше вопрос маркетинга.

blacklion

Ну, посмотрим! Для идеального SDR для радиолюбителя, конечно, хватит и по одному каналу. Другой вопрос — граница и ФСБ. Но это наша российская специфика, она Xilinx не очень волнует, я думаю :)

Korogodin

С нашими вопрос решаем, куда тяжелее со списками госдепа

blacklion

Ну, я на это смотрю как частное лицо, которое может если надо покупать на американские адреса и возить в чемодане. Если речь о готовых девайсах (типа того же USPR), а не о чипах партиями, это выход, но идя через зелёные ворота в аэропорту придётся быть очень самоуверенным.

Korogodin

Страшно рисковать свободой ради микросхемы. Есть специализирующиеся на этом конторы, которые проблему переведут в затраты.

CraSS

А в какие радары-то, например?

Возьмем морскую навигацию, там длина волны 3 см, т.е. 9 ГГц, тут насколько я вижу, АЦП только на 4ГГц. То есть, без понижения частоты все равно никак

Или я что-то не так понимаю?

NelSon29

Совсем без преобразования частоты это уже поле радиофотоники. Тут однократное гетеродинирование всё-таки нужно будет.

blacklion

Один раз частоту понизить придётся, ну так и для 5G придётся, там частоты типа 28 GHz планируются среди прочих. Но зато такая штука может одним ADC сразу кучу каналов смотреть.

Korogodin

Складывается ощущение, что вы хорошо разбираетесь в таких АЦП. Мне на практике с ними сталкиваться не приходилось, никогда не изучал их структуру. Я их воспринимал как некоторый самообман — гетеродинное преобразование в кремнии. То есть АЦП с высокой верхней частотой (в 4 ГГц), но привычной частотой дискретизации (100-200 МГц).

Судя же по вашим сообщениям, это именно дискретизация на частоте в 4 ГГц. Я правильно понимаю? Как его тогда обрабатывать в FPGA, в которой тактовая частота логики будет 100-200 МГц?

blacklion

Это я только умные слова умею говорить! Т.е. я довольно много про это читал, но так и не щупал руками. Теоретик чёртов.

Вообще, есть два подхода — работа в первой полосе найквиста (собственно, как мы привыкли думать об АЦП, как работают АЦП в звуковых картах) и в кратной (N'ной).

Для второго есть специальные АЦП, и они устроены как вы пишете тут, у них очень широкая аналоговая полоса, перед ними ставится не LP-фильтр, а полосовой (вокруг интересующей частоты несущей), но семплирование идёт на не очень (относительно сигнала!) высокой частоте, и полоса пропускания разумная. Мы семплируем прямо антенну с LNA и BPF, но видим немного сигнала, который спускается к нулю по частоте через aliasing (а то, что там нет всего что в эфире между нулём и частотой канала нам обеспечивает аналоговый BPF). Самый обычный АЦП так работать (нормально) не будет, так как его аналоговые цепи всё убьют на частоте заметно превышающую частоту семплирования и он в такой ситуации увидит тишину.

Есть же по-настоящему высокоскоростные АЦП, у которых частота семплирования очень высокая, и сопоставимая с полосой пропускания аналоговой части. И вот они стоят бешеных денег, являются товаром двойного назначения, etc.

Xilinx явно выбрал второй путь, потому что в заметке для IEEE Journal прямо вот есть название раздела: «A 13b 4GS/s Digitally Assisted Dynamic 3-Stage Asynchronous Pipelined-SAR ADC». Тут как бы сомнений не остаётся, потому что указана не полоса пропускания в герцах, а именно число семплов в секунду — 4GS/s, что даёт нам полосу от 0 до 2GHz (что там с работой в кратных полосах Найквиста не ясно, думаю, что ничего хорошего всё же).

Судя по структурной схеме в вашей же заметке, там сразу после DAC будет стоять digital down convert, т.е, видимо, NCO (генератор косинуса, числовой), умножитель (аппаратный), и дециматор с LPF. Который и будет из всех 2Ghz входной полосы выделять нужные каналы и приводить их к более обрабатываемому потоку данных. На сколько этот блок будет конфигурируемым и настраиваемым и каковы его пределы скорости (на сколько МАЛО можно будет децимировать и всё равно что-то успевать делать) — непонятно.

Но всё, что выше 2Ghz, да, надо будет спускать к этой частоте аналоговыми методами, видимо. Если этот ADC ещё и умеет нормально видеть кратные полосы Найквиста — это вообще чудеса будут.

При этом, в статье говорится, что такой ADC может работать на 4GS/s на один вход или на 2GS/s на два входа (!). Что прямо ведёт к I/Q семплированию после аналогового смесителя. Т.е. до 2GHz мы работаем прямо после фильтра преселектора и антенных усилителей, а на частотах выше квадратурный смеситель нам делает два сигнала (I и Q) на частотах ниже 2Ghz, и мы получаем сразу комплексный сигнал, не тратя это цифровых ресурсов!

Korogodin

Да, в удивительное время живем))

В перестраиваемый NCO с цифровым фильтром на 2 ГГц я поверить могу. Но теперь понимаю ваши опасения о стоимости микросхемы :-)

nerudo

4 ГГц АЦП сейчас уже вполне реальность, работают с ними путем распараллеливания отсчетов. Т.е. с АЦП мы получаем, к примеру, параллельно 16 отсчетов, которые во временной области стоят друг за другом. После этого и так нетривиальная математика цифровой обработки становится и вовсе сумасшедшей, как в плане сложности, так и попросту затрат ресурсов…

Конечно же в наше время вся полоса сразу нужна далеко не всем, так что стараются отфильтровать нужную полосу и продицемировать, чтоб обрабатывать по 1-2 отсчета за такт.

Korogodin

Если такую фильтрацию проделать в постоянном кремнии, а не в программируемой логике, то в целом всё получает user friendly.

Как и ожидалось, АЦП отдельно стоят порядка $2k.

Crunch-f

Хороший можно сделать осциллограф

Korogodin

Да, это одно из интересных приложений, т. к. динамический диапазон АЦП и ЦАП приличные, ни говоря уже о полосе.

Если разобрать любой векторный генератор, осциллограф или анализатор спектра Rohde&Shwarz, то внутри всё окажется банально. Высоколинейные тракты, АЦП и ЦАПы, FPGA типа Spartan'а, микроконтроллер и компьютер на Intel'е. Всё можно упростить ровно в той мере, что я описал в статье, если решить вопрос с фильтрацией и удовлетворят характеристики.

NelSon29

Очень интересный девайс, сразу захотелось поработать.

Единственное, что смущает, так это что ни на одной отладочной плате я не вижу разъема для собирания трасс (ARM Trace). Безумно удобная вещь при отладке приложений, работающих в реальном времени.

Korogodin

Не приходилось пользоваться. Быстро полистал доки, в целом идея понятна, но всё-таки было бы интересно получить информацию из первых рук! Что на практике дает ARM Trace? Как выглядит процесс использования?

NelSon29

Если просто, то он во время работы записывает выполненные инструкции с частотой процессора (т. е. неинвазивно и не влияя на ход исполнения программы). Опционально позволяет записывать время выполнения и регистры, тем самым полностью воссоздавая ход программы.

Очень помогает при работе на голом железе, без ОС. Отслеживать прерывания, замерять производительность, искать баги и всё прочее. Сейчас работаем с нашим новым чипом, одно удовольствие, времени на исправление программных ошибок тратиться гораздо меньше.

Korogodin

Звучит здорово! Какой интерфейс между платой и ПК при этом?

NelSon29

Плата подключена к JTAG-отладчику (например, DStream), в котором стоит ОЗУ на несколько гигабайт. Туда с большой скоростью пишутся трассы, а потом уже оттуда вычитываются компьютером. У нас отладчик подключен вообще через Ethernet, так как стенд находится на другом конце комнаты, чтобы поместился векторный генератор, осциллограф, блок питания и прочие. :)

Korogodin

То есть нужен только JTAG на плате? Он у всех выведен.

NelSon29

Не совсем. Внутри ядер ARM есть два отладочных блока: ETM и ETB. Первый — высокоскоростной интерфейс, он может быть выведен на ножки микросхемы для последующего подключения через, например, Mictor-коннектор. В таком случае можно использовать всю доступную память в отладчике.

ETB это отладочный буфер, чаще всего размером 8 КБ. Он осуществляет работу именно JTAG-отладчиков (с подключением через 20-пиновый разъём). В этот буфер тоже можно писать трассы, но тогда надо чётко указывать места начала и конца, т.к. в 8 КБ влезает примерно 10к инструкций, не более. Этого количества часто не хватает.

Korogodin

Можно модельку отладчика, которым пользуетесь? Хочу посмотреть конкретный разъем, сколько линий и т.п.

NelSon29

Конечно, вот отладчик, а вот хороший документ с описанием разъёмов и линий

Korogodin

Спасибо, как раз сейчас разводим новую плату, информация своевременная.

Судя по фото и характеристикам, этот DStream должен стоить прилично. Не знаете, какой хотя бы порядок цен?

NelSon29

Порядка $2500-3000. С ним часто идёт лицензия на DS-5, IDE от ARM.

Для индивидуального разработчика сумма приличная, однако в масштабах предприятия уже незаметно. Насколько мне известно, нам он вообще достался со скидкой, т.к. мы его покупали вместе с лицензией на ядро ARM.

Korogodin

В целом это объясняет тогда, почему ARM Trace редко встречается. Высокоскоростной разъем под него — порядка $10-20, а пользоваться смогут единицы.

NelSon29

Согласен, встречается редко и на достаточно продвинутых платах. Учитывая возможности Zynq-ов, ожидал тут увидеть, только и всего :)

GPavlikh

Стоит сказать, что сам чип TRACE умеет, и даже выводить его напрямую в ПЛИСовую часть, где его можно крутить-вертеть самому.

Korogodin

Есть примеры? Данные потом через ChipScope вытаскивать? Или в DDR сгружать?

GPavlikh

Сам таким никогда не пользовался, в даташите подсмотрел :) Если глянуть их UG585, то там это разделы 27.4 Programming Model и 28.2.7 Trace Packet Output (TPIU).

ValeriyS

Подозреваю, что 13/14-bit ADC и DAC с частотой сэмплирования 4/6.8 ГГц не пропустит экспортный контроль. Кто-нибудь знает какие сейчас параметры ограничения экспорта?

Korogodin

На 12-разрядные АЦП было 200 МГц, насколько помню.

itsar

До всяких событий было 8 бит, 10 МГц.

Alexufo

Это связано с ограничениями из-за возможной военной деятельности?

Korogodin

Им приходится находить компромисс между потребностями:

— производителей чипов,

— национальными HW компаниями,

— гос безопасностью

Запрещая экспортировать технологические новинки зарубеж, они создают дополнительные конкурентные преимущества своим HW-компаниям и военке.

Но с другой стороны, для производства чипов нужен рынок. Во-первых, чтобы производители этих чипов могли зарабатывать и развиваться. Во-вторых, стоимость чипа обратно пропорциональна объему рынка (ожидаемым продажам), а дешевый чип — дополнительное преимущество для тех самых HW-компаний и военки.

Electrovoicer

Были и остаются задачи с большИм ДД, вроде широкополосного многоканального приема, где без внешних АЦП выского класса не обойтись, SFDR=60..65db это не совсем серьезно, а бОльшего в таких интегрированных решениях не будет. Так что, вещь хорошая, в некоторых классах приложений найдет место. Но не панацея от всех болезней.

Korogodin

Никогда не делал широкополосных систем связи, поэтому позвольте поинтересоваться: какая связь между полосой сигнала и SFDR? То есть, зачем нужен высокий SFDR для широкополосного приема?

Что-нибудь типа пик-фактора из-за большого количества каналов?

punzik

Книги уже раскупили. Планируете дополнительный тираж?

Korogodin

То издание уже морально устарело, с тех пор много воды утекло. Когда смотришь на свой старый код, обычно возникает желание все переделать. С книгой так же, поэтому сейчас пишем новую версию.

gapel

И тут стало грустно. Т.е. здорово что это все есть, оно реально крутое и просится в использование, но если его не купить а только облизываться, то зачем это все…

itsar

Есть надежда, что Мы по-облизываемся-по-облизываемся, а потом все таки сделаем.

Но надежда грустная такая, безнадёжная, тут Вы правы)

man55

а если по теме — на взгляд со стороны «в лоб» более эффективно было бы интегрировать гетеродин+смеситель, чтобы заниматься обработкой все-таки на ПЧ

Чем вызвана необходимость обработки сразу на несущей? Сигналы не настолько широкополосные же?

И стоить baseband будет как один космолет, а не как десять, жрать будет меньше, под продукцию двойного назначения и запрет на ввоз меньше шансов попасть

Korogodin

Согласен насчет арабской записи. Могу предположить, что они передатчики делают чаще приемников. Непривычно.

Профит в универсальности и том, что микросхема получается полностью цифровой. Чтобы не совмещать аналоговую обработку и цифровой в одной микросхеме.

gritway

Вот у кого надо гитарный процессор заказать!!!

en1gma

всё равно такая игрушка всё не покроет…

например, нам вот нужно enob эдак 25-26 всего на паре килосэмплов… но нужно шесть независимых каналов с синхронным запуском… а если вход будет несимметричным (да ещё и «высоковольным») — так это вообще фантастика…

NelSon29

Попробуйте посмотреть в сторону модулевских чипов (1879ВЯ1Я и К1888ВС018). Там по четыре АЦП, но зато относительно высокоскоростных и с блоком предобработки сигналов с независимыми каналами с синхронным запуском. Может быть, это решит вашу задачу.

en1gma

я слаб в цифровой обработке сигналов, но, насколько я понимаю, вы предлагаете собрать сигма-дельта мультибитник?

ну и верхнее чисто_на_пальцах_теоретическое ограничение увеличения разрядности log4(80М/2К) = 7,6 бит… что совсем печально… те же ads12xx имеют дд куда шире, например, при внешней растяжке сигналов они на невылизанной плате дают эноб за 18 на 1к. при куда меньшем энергопотреблении и сложности софта.

как раз сейчас и пытаемся натянуть сову на глобус, используя схемотехнические решения, пытаясь выполнить вышеозвученные требования заказчиков