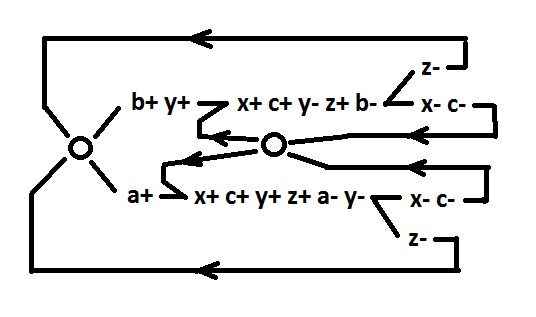

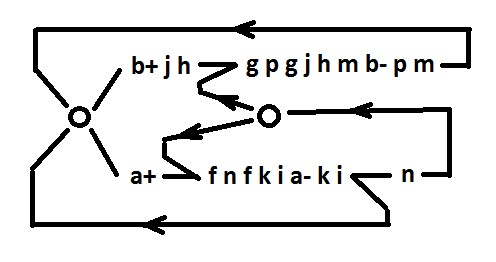

Нашел пример, как делать схемы с помощью Petrify. Исходное задание выглядит так:

В результате получилась вот такая SI схема:

Да, от Маллера ушли не далеко, ну только что C-элементы подвесили. Думаю, все-таки надо показать, как надо делать асинхронные схемы. Для начала лучше ознакомиться с этим.

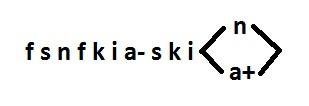

А здесь разберу приведенный пример. Для начала нарисую исходное поведение поудобнее и заменю длинные имена сигналов:

dsr — a

dsw — b

ldtack — c

lds — x

d — y

dtack — z

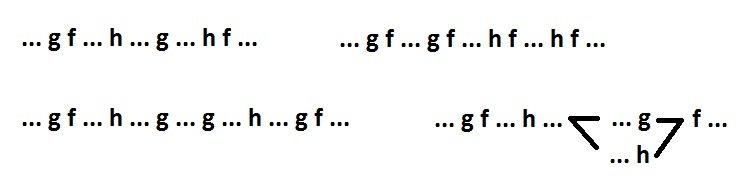

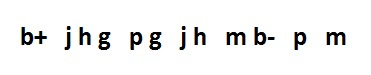

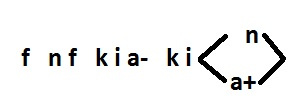

Чтобы синтезировать SI схему на двухвходовых элементах, надо дополнить исходное поведение новыми сигналами так, чтобы каждый невходной сигнал (f) можно было бы вписать в один из следующих шаблонов (или в их комбинацию):

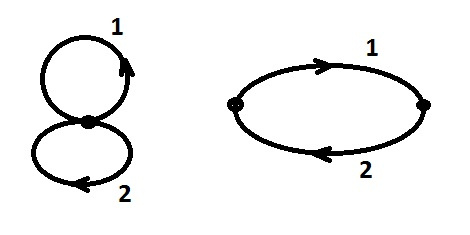

Чтобы понять, как пользоваться шаблонами применительно к поведению с выбором, рассмотрим поведение, состоящее из двух альтернативных ветвей. А потом рассмотрим поведение из тех же двух ветвей, но расположенных последовательно друг за другом.

Нетрудно проверить, что логические функции для обоих этих поведений одни и те же. Это и понятно, второе поведение это то же что и первое, только с зафиксированной дисциплиной переключений входных сигналов. Соответственно, чтобы использовать шаблон применительно к поведению с выбором, нужно последовательно хотя бы один раз пройти по всем ветвям в произвольном порядке (но только таком, который допускает исходное задание). И еще одно замечание: дополнительные сигналы будут вставляться без фиксации знака. Знаки будут расставлены в самом конце.

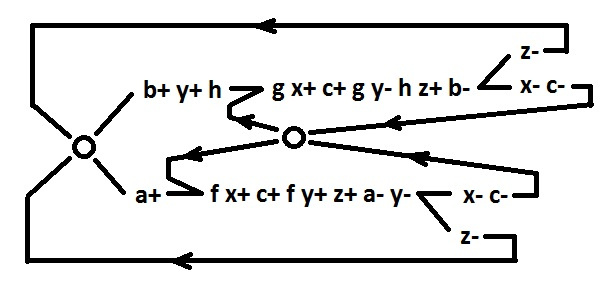

Итак, посмотрим на исходное поведение. Проблема, которую нужно решить в первую очередь: выбор происходит одновременно с параллельной ветвью x- c-. Необходимо синхронизировать эту ветвь. Имея в виду дальнейшее дробление поведения, лучше синхронизацию сделать отдельно для каждой альтернативной ветви. а заодно и изолировать сигнал c.

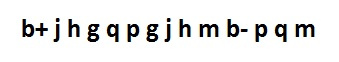

Добавленный сигнал f вписывается в шаблон (т.е. имеет двухвходовую реализацию) с помощью уже имеющихся сигналов (f= ac). Сигнал g можно было бы вписать в шаблон с помощью сигналов y и c, но лучше добавить сигнал h, который позже можно будет использовать для изоляции сигнала y. Сигналы f, g объявляем псевдовходными, т.е. запрещаем перед ними ставить новые сигналы (чтобы не испортить двухвходовую реализацию).

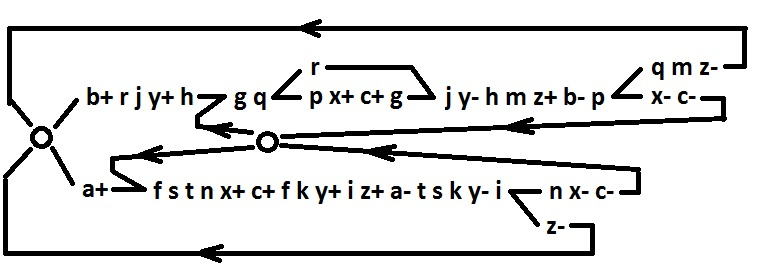

Исследуемое поведение четко разделяется на две альтернативные ветви. Поэтому его можно разделить на два независимых поведения, каждое из которых будет представлять из себя одну из альтернативных ветвей. Для этого нужно изолировать сигналы, встречающиеся в обеих ветвях. Изолировать сигнал x — значит получить двухвходовую реализацию (вписать в шаблон) для этого сигнала x и для всех сигналов-следствий (сигналов, переключения которых являются следствием переключения сигнала x). Таким образом мы устраним влияние сигнала x на схему и далее его можем не рассматривать.

Общими для обеих ветвей являются сигналы — c, x, y, z. Сигнал c — входной, реализации не требует. Его следствия f, g уже реализованы. Следствия сигналов x и z — входные сигналы, для них реализация не требуется. Для следствий сигнала y используем h и новый сигнал i (h=yb, i=yb). Сигналы h и i теперь псевдовходные. Для реализации сигнала y вставим новые j и k (y=jk). Сигнал z реализуем с помощью уже имеющегося сигнала i и нового сигнала m (z=im). Для реализации сигнала x добавим новые сигналы n и p (x=np). Сигналы y, z, x — теперь псевдовходные.

Удалим из графа изолированные сигналы. Действия такие же, как при добавлении сигнала, только последовательность обратная. Основание для удаления сигналов следующее: чтобы синтезировать схему для поведения с изолированными сигналами, достаточно построить схему для того же поведения, но с удаленными изолированными сигналами.

Сигналы a, b — входные, f, g, h, i — псевдовходные.

Чтобы синтезировать схему для такого поведения (с уникальными сигналами в каждой ветви), достаточно синтезировать две схемы для каждой альтернативной ветви по-отдельности. То что ветвь n параллельна точке выбора, не является препятствием, т.к. эта ветвь синхронизирована псевдовходным сигналом g.

Рассмотрим отдельно верхнюю ветвь.

Сигналы b, g, h — входные или псевдовходные.

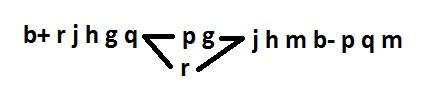

Рассмотрим готовность к декомпозиции. Нарушений CSC нет. Сигнал m уже имеет двухвходовую реализацию (m=ph). Для сигнала j в качестве дуального можно использовать сигнал g. Для сигнала p необходимо добавить дуальный сигнал q.

Теперь найдем логические функции. Пока знаки не расставлены — вид функции условный.

m=qh

p=bq

q=gp

j=g+bp или j=g+bq

Проведем декомпозицию j (тем самым введем новый сигнал r).

j=rg

r=bp или r=bq

Запомним, что r может быть следствием p (вместо — q). Это может пригодиться при расстановке знаков.

Теперь рассмотрим отдельно нижнюю ветвь.

Сигналы a, f, i — входные или псевдовходные.

Нарушения CSC есть. Это последовательности: n f n f и k i a- k i a+. Устраняется единственно возможным способом (сигнал s).

Сигналы n, k уже имеют двухвходовую реализацию (n=si, k=fs). Для сигнала s необходим дуальный сигнал t.

Теперь логические функции выглядят так:

n=ti

r=fs

s=ft

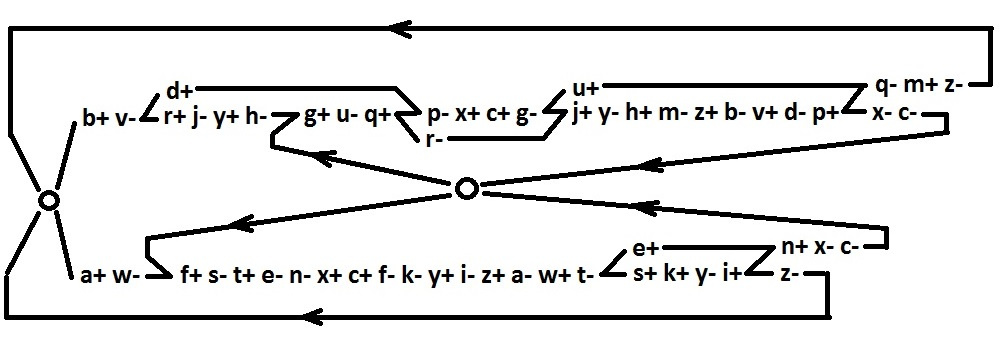

t=as

Для обеих альтернативных ветвей все сигналы приведены к реализуемости в двухвходовом базисе. Теперь восстановим поведение в полном объеме, со всеми добавленными сигналами.

И наконец, расставим знаки. Возникшие рассогласования входов для сигналов i, f, q, p, n исправляются добавлением инверторов v, w, u, d, e соответственно.

А вот логические функции для всех сигналов.

Схема выглядит так:

Посчитал транзисторные пары. Оглушительного превосходства не получилось. 78 на 94, если не ошибся. Ну, да ладно. Зря старался, что ли. Публикую.

Комментарии (13)

ajrec

26.06.2017 16:08Пожалуйста, не грузите меня железками, я об этом действительно ничего не знаю. Я узкий специалист по синтезу асинхронных схем. Зато в этой области рядом со мной вообще никого нет. Ни близко, ни далеко. К петрифаю я привязался только по одной причине, он единственный, кто гордится своими результатами. И публикует их. То что интерфейс старый или новый мне вообще по барабану. Был в книжке пример с исходным заданием и полученным результатом, я его и сделал. Настругать такую схемку полчаса работы. Статью писать гораздо гумознее. В статье я не хвастался, что сделал какой-то VME (да хоть BBE), на примере я показал, как применять мой метод. Пример взят не потому, что он маленький или большой. Он весьма не плох для демонстрации.

Des333

26.06.2017 22:48А можно какой-нибудь реальный пример, где используются асинхронные схемы?

Пусть будет просто ссылка. Но именно не демо, а так сказать «подакшн».

Естественно, с исходным кодом.

Спасибо!

ajrec

26.06.2017 23:41К сожалению, я не инженер, я только на бумажках рисую. О нужности, ненужности асинхронных схем судить не могу. Но вроде как существует мнение, что асинхронные схемы это хорошо, единственная загвоздка — не очень понятно как их делать. Я, как мне кажется, с этим разобрался. Что касается реальных примеров, то в книжке, фото обложки в начале статьи, как мне показалось, и приводятся реальные примеры. Правда, там вся асинхронность сосредоточена в управляющих схемах. Но я думаю, асинхронные принципы можно распространять и на данные, и на адреса…

Khort

27.06.2017 08:14Вот, к сожалению, данные, адреса и любые операции над ними не годятся для графового представления. Если придумаете как это сделать — будет революция.

А без данных, адресов и арифметики, лучшее что можно сделать асинхронным (с помощью графового метода) — машину Тьюринга. Но никак не процессор, к примеру. Поэтому тематика и заброшена, уже 20 лет как.

ajrec

27.06.2017 23:50Буду осторожен, все-таки вступаю на чужую территорию. Может я неправ, но мне видится так. Дешифрация адреса — это последовательность из N «выборов по уровню». Вернее двоичное дерево. N — разрядность адреса, «выбор по уровню» — выбор в зависимости от состояния ячейки адреса (подробнее в общем обзоре, класс проблем, связанных с входными сигналами). Конечно записывать это в STG дико. Я и говорю, что STG несколько неадекватен. А вот язык наподобие языка программирования (с рекурсиями, вложенными функциями) вполне справился бы. Сам же синтез не так страшен, как кажется. На первый взгляд кажется, что там 4 типовых решения, и их надо раскидать, в зависимости от предыдущего количества 0 и 1 адреса.

Что касается данных, то тут даже попроще. Схема разряда данных, а может даже вместе с разрядом второго операнда, хранит свое состояние. Сигнал на операцию определяет выбор. Далее детерминированная последовательность событий. Копирование это выбор по уровню. А вот между памятью и регистром должна быть схема, представляющая из себя выбор на множество ветвей (по количеству адресов). Для каждой ветви решение типовое. В общем может и коряво, ну это первое что в голову пришло. Да, интересно было бы в этом поковыряться.

lingvo

27.06.2017 13:41Насколько я понимаю, реализация асинхронных схем на реальном железе требует очень объемной верификации и тестирования, не говоря уже о квалификации разработчика. Собственно поэтому их и применяют в различных ASICах, где борются за каждый гейт. Ну или еще для быстродействия, но опять же с появлением последовательных высокоскоростных шин (которые собственно и убивают VME сегодня) этот вопрос тоже перестал быть актуальным.

В ПЛИСах уже давно используются синхронные схемы, которые хоть и проигрывают в быстродействии асинхронным, но требуют гораздо меньшей верификации и квалификации разработчика.

ajrec

27.06.2017 21:14Абсолютно согласен. Только первое (трудность верификации) прямое следствие второго (квалификация разработчика). Правильно, грамотно сделанная схема просто по определению должна на «ура» проходить все верификации, моделирования. Уже при синтезе асинхронной схемы закладываются более жесткие условия, чем при моделировании.

lingvo

28.06.2017 00:33Там не только дело в квалификации разработчика. Чтобы схема заработала в железе, синтезатор и P&R должен четко знать все требования по времянкам между различными сигналами, hold, setup time и пр. И эти все констрейны разработчик должен знать и программировать ручками для каждого из сигналов.

В случае же с синхронными схемами, синтезатор легко генерирует констрейны самостоятельно, стоит только задать частоту тактового сигнала. И разработчику не надо об этом париться.

lingvo

27.06.2017 13:46Дык приведенная схема и используется в продакшн — в BUS контроллере VME. Только люди, ее разрабатывавшие, уже, наверное, умерли.

Khort

Коллега, вы хоть представляете, что такое VME? У Вас в статье нет и десятой части сигналов этого интерфейса. Нет шины адреса, модификатора, шины данных, вообще опущена система выставления и обработки прерываний, географическая адресация. По сути, Вы взяли малююсенький кусок автомата записи, ответственного за хендшейк передачи, да и то — только в одном из нескольких режимов. А как же блочные передачи, чтение, как же Read-Modify-Write, как же снятие прерываний? Это у Вас вообще ни разу не bus controller.

Не говоря уже о том, что интерфейс старый как г-но мамонта; когда я защищал свой диплом по теме моста PCI-VME в 2001 году, уже тогда этот интерфейс был чудовищно устаревшим.

p.s. эту книгу можно найти целиком в интернете — ищите. Ну или по почте скину, если не найдете.