Вспомнить бы что такое триггер

Классический D-триггер является базовой единицей хранения информации в современных цифровых микросхемах. На высоком уровне абстракции он представляет из себя устройство памяти с входом данных D, выходом данных Q, а также входным управляющим тактовым сигналом (clk — clock в английской терминологии). Все сигналы здесь — логические, могут пребывать либо в логическом 0 (далее «0») либо в логической 1 (далее «1»). Абсолютное значение напряжений в вольтах нас пока не интересует. При поступлении на тактовый вход фронта сигнала, т.е. перехода из «0» в «1», триггер запоминает текущее значение на входе данных D и передает его на выход Q. Во всех прочих ситуациях триггер продолжает хранить свое старое значение. Также у триггера могут присутствовать и другие управляющие сигналы, в частности сигнал асинхронного сброса aclr, устанавливающий триггер в «0», невзирая на другие входы.

Любой триггер имеет два временны?х параметра (требования), которые необходимо выполнять для корректной работы:

- Ts — setup time — время предустановки. Время в течение которого сигнал на входе D должен оставаться стабильным перед приходом фронта тактового сигнала;

- Th — hold time — время удержания. Время в течение которого сигнал на входе D должен оставаться стабильным после прихода фронта тактового сигнала;

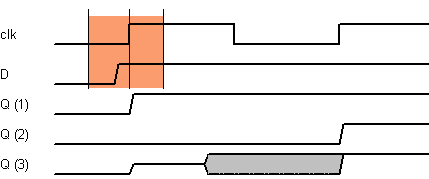

Сумма этих двух параметров дает нам временно?е окно в окрестностях фронта тактового сигнала в течение которого входные данные должны быть стабильны. Аналогичные параметры есть и для других входов, в частности для входа асинхронного сброса (их называют recovery and removal time). Невыполнение данных требований приводит к неопределенному состоянию триггера. В простейшем случае это будет либо «старое» либо «новое» значение пришедшее на вход данных D в непосредственной близости от фронта клока, но какое именно — неизвестно. Во многих ситуациях с этим можно смириться. На следующей картинке выходы Q(1) и Q(2) — две реализации срабатывания триггера при нарушении входных временных параметров.

Монета, зависшая в воздухе

Однако иногда при нарушении временных параметров происходит выход за границы «цифрового мира» и вместо того, чтобы принять состояние четко соответствующее «0» или «1», выход триггера начинает болтаться в промежуточном состоянии с напряжением примерно соответствующим половине напряжения между «0» и «1». Грубая аналогия из «механического мира» вынесена в заголовочную картинку. В стабильном положении шарик находится слева или справа. Чтобы он попал в другое состояние — его нужно толкнуть. Если сделать это достаточно сильно — он без проблем перевалит за вершину и очутится с другой стороны (нормальное переключение триггера). Если толкнуть слишком слабо — сразу скатится назад. Если же вы человек везучий, то есть шанс, что толкнув шарик, вы заставите его застыть ровно на вершине.

Именно этот эффект и называется метастабильностью. На картинке выше этот вариант обозначен как Q(3). В конечном итоге триггер «свалится» в одно из определенных состояний, но точно сказать когда это произойдет невозможно. Время пребывания триггера в метастабильном состоянии является вероятностной величиной и зависит от технологических параметров элементной базы, температуры и т.п. На осциллографе эта картина выглядит примерно вот так (синим цветом показан входной сигнал, нарушающий временные параметры триггера, розовым — выход триггера):

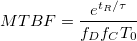

Почему метастабильность — это плохо? Во-первых, это состояние само по себе неопределенно и порождает неизвестный результат в последующих элементах. Более того, во многих случаях выходной сигнал одного триггера подается сразу на несколько других элементов, которые из-за неидеальности технологической базы могут иметь немного разные пороги срабатывания. А значит, один и тот же сигнал может трактоваться как «1» в одном месте и как «0» в другом. Это может привести к рассинхронизации работы различных частей устройства и общему сбою (т.е. такой ситуации из которой устройство само выйти неспособно). Более того, если метастабильное состояние продержалось до прихода следующего тактового сигнала, то оно может ввести следующий в цепочке триггер так же в метастабильное состояние. Вероятность этого невысока, т.к. диапазон входных напряжений при котором триггер попадает в метастабильность чрезвычайно узкий. Однако с учетом того, что подобная ситуация будет происходить регулярно с высокой частотой (современные схемы могут работать на частотах до 1 ГГц, а то и выше) это событие вполне реально. Опять таки, вероятность такого события можно оценить с учетом параметров устройства, частоты тактирования и частоты изменения данных. Общая формула оценки времени наработки на отказ выглядит следующим образом:

, где

, гдеt_R — временной интервал «защиты» от метастабильности. Для грубой оценки можно считать, что равен 0 для одного триггера, периоду тактового сигнала за вычетом задержек на предустановку и распространение для второго триггера и плюс по периоду для каждого последующего;

\tau — параметр зависящий от технологии, для современных устройств единицы/десятки пикосекунд;

T_0 — временное окно попадания в метастабильность. Десятки/сотни пикосекунд;

f_c — частота тактового сигнала. Сотни мегагерц;

f_D — частота изменения данных. В диапазоне от 0 до f_c.

Для современной аппаратуры период попадания первого триггера в цепочке в метастабильное состояние измеряется микро/миллисекундами, второго — часами, третьего — миллиардами-триллионами лет.

Эффект метастабильности может возникнуть в нескольких классических ситуациях:

- Явное нарушение параметров Ts и Th триггера. Обычно возникает, когда устройство пытаются заставить работать на частоте, на которой оно физически работать не может из-за слишком длинных путей распространения сигналов. Данная ситуация контролируется временным анализатором и при нормальной работе (при выполнении временных требований) встречаться не должна.

- Нарушение временных параметров по входам асинхронного сброса. Удивительно, но несмотря на то, что сброс асинхронный, он должен быть синхронен тактовому сигналу того триггера, который сбрасывает, т.е. его временные параметры декларируются относительно фронта тактового импульса. Об этом часто забывают, подавая сброс откуда ни попадя. Опять-таки, если сигнал сброса порожден с помощью того же тактового сигнала, как и тактовый сигнал сбрасываемого триггера, то временной анализатор разберется самостоятельно.

- Сигналы, подаваемые синхронно (на той же частоте с известной задержкой) из других устройств — здесь простейший временной анализ (т.е. декларирование только тактовой частоты) не работает и необходимо явно задавать временные характеристики ваших входных/выходных сигналов. Это является отдельной непростой (но вполне разрешимой) задачей временного анализа.

- И, наконец, самый тяжелый случай — сигналы передаются асинхронно, может быть совсем на другой тактовой частоте (и с неизвестными сдвигами фазы) относительно приемных триггеров. Их источником может быть как внешнее оборудование (хоть кнопка на плате или последовательный порт) так и блоки той же микросхемы, работающие на другой тактовой частоте. Именно об этой ситуации и пойдет дальнейший разговор.

Но сперва несколько слов о том, откуда же берется множество тактовых сигналов. Безусловно, самый простой и приятный вариант — когда тактовый сигнал только один. Тогда работать с проектом просто и удобно. К сожалению это возможно лишь для совсем простых устройств. Любое более-менее сложное устройство обычно общается с несколькими внешними устройствами/интерфейсами, каждый из которых может иметь свой собственный тактовый сигнал. К примеру, нам надо принять данные с АЦП, буферизировать их во внешней динамической памяти после чего передать по Ethernet. В этом случае у нас будет как минимум 3 несвязанных друг с другом тактовых домена — интерфейса АЦП, системной шины и DDR-памяти, а так же клок Ethernet-интерфейса. А значит перед нами стоит задача корректно передавать данные (а так же параметры, управляющие сигналы, флаги статуса и т.п.) между этими тактовыми доменами.

Как бороться

Для начала плохая новость: полностью эффект метастабильности побороть невозможно, поэтому всегда остается вероятность того, что ближайшая АЭС внезапно взорвется или ваш самолет внезапно упадет. Однако рядом простых действий можно данную вероятность значительно уменьшить, примерно сравняв с вероятностью того, что завтра вострубит архангел Рафаил и объявит Судный День. Общая тактика понятна: ставим подряд несколько триггеров (как показывает формула выше, для реалистов вполне достаточно двух синхронизирующих триггеров) после чего данными можно пользоваться. Однако есть ряд технических нюансов, которые зависят от рода передаваемых данных.

Самый простой случай — передается псевдостатический скалярный (одноразрядный) сигнал. Например сигнал выбора режима и т.п. — переключающийся крайне редко. В этом случае нашей единственной заботой является защита от метастабильности — ставим два триггера приемной частоты и дело в шляпе. С неопределенностью 1 такт (нас не волнующей) он будет передан от источника к приемнику.

Сигнал разрешения длительностью 1 такт. Сложность заключается в том, что при несовпадении частот есть высокая вероятность либо совсем потерять сигнал (если приемная частота ниже исходной) либо растянуть его на несколько тактов, что тоже не здорово.

Общий подход, применяемый в этом случае — «удлинить» сигнал не несколько тактов, перенести его в новый тактовый домен известным способом и там выделить событие фронта, заново сформировав сигнал длительность 1 такт.

Многоразрядная шина, передающая единое псевдостатическое значение (например конфигурационный параметр). Казалось бы, все просто — ставь по паре триггеров на каждый разряд шины — что еще надо? Однако нам известно, что после выхода из метастабильного состояния триггер может принять как старое, так и новое значение. Более того, даже без входа в метастабильность, просто за счет чуть отличающихся параметров триггер одного из разрядов может успеть защелкнуть новое значение, а триггер другого — старое.

В данном случае в течение как минимум 1 такта на выходе шины будет присутствовать некорректное значение. Оно не будет равно ни старому, ни новому из поданных на вход. Для каких-то схем это может не иметь значения, а для каких-то может быть важно. Поэтому стараются создать более надежную схему с сигналом-подтверждением, указывающим в какой момент можно безопасно перещелкнуть входные данные на выход.

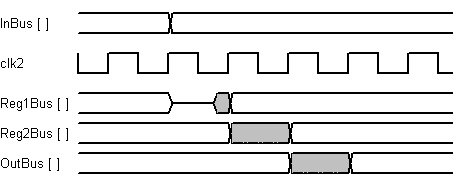

И, наконец, самый сложный случай — поток данных, передающихся из одного тактового домена в другой. Если данные относительно редкие (1 слово данных на 10 и более тактов клока), то можно реализовать схему с рукопожатием, аналогичную предыдущему пункту. Но как быть, если данные идут на каждом такте (или близко к тому)? Здесь нам на помощь придет специальный аппаратный блок — двухпортовая память с независимыми тактовыми сигналами. Такая память есть как в современных FPGA, так и в технологических библиотеках для заказных микросхем. Ее можно писать и читать совершенно независимо через два отдельных порта. Единственным ограничением является одновременное обращение на запись и чтение по одному и тому же адресу памяти — оно может привести к неопределенному результату. На основе такого блока памяти зачастую создается модуль FIFO, который позволяет с одной стороны записывать данные из одного тактового домена, а с другой — забирать в другой тактовый домен. Заодно логика FIFO следит за тем, чтобы не происходило обращения к одной и той же ячейке памяти.

Заключение

Напоследок хочется подвести итог и дать несколько полезных советов:

- Чем меньше тактовых сигналов, тем проще работа с вашим проектом

- Базовым сихронизатором является два (или более) стоящих друг за другом триггера

- Между всеми асинхронными тактовыми доменами должен быть продуман механизм передачи данных. Лучше всего еще на этапе системного проектирования нарисовать тактовую структуру проекта

- Все внешние сигналы, асинхронные по отношению к вашему устройству, в том числе сигналы асинхронного сброса, должны быть синхронизированы

- Внутри одного модуля лучше использовать только один клок

- Если внутри модуля больше одного клока, то для каждого внутреннего сигнала нужно четко представлять, каким клоком он формируется и как потом используется. Надежнее закодировать прямо в имени сигнала

- Будьте особо внимательны на верхнем уровне проекта: именно здесь очень часто происходит ошибочное подключение сигнала из одного тактового домена в другой без пересинхронизации

- Тактовые сигналы, порожденные на внутренних модулях умножения частот (PLL/DCM/MMCM и т.п.) обычно синхронны, они рассматриваются временным анализатором и для них пересинхронизация данных чаще всего не требуется. Хотя и не помешает.

- Современные средства проектирования стараются самостоятельно обнаруживать ситуации передачи данных между тактовыми доменами. Например Design Assistant у Альтеры (встроен в Quartus), ALINT у Aldec. Стоит прислушиваться к выдаваемым предупреждениям и советам

И в завершение несколько комментариев по возможным техническим вопросам.

Временные диаграммы рисовались с помощью простой бесплатной программы TimingEditor. Некоторые проекты собирались в Quartus — исключительно из-за удобства его схемного редактора. Все то же самое может быть (и должно быть!) реализовано на чистом HDL (VHDL/Verilog). Если хочется более глубокого понимания физики метастабильности, то подробнее данную тематику можно изучить по ключевым словам metastability и clock domain crossing. Например, довольно подробное исследование Steve Golson «Synchronization and Metastability» и более краткий документ Ran Ginosar «Metastability and Synchronizers», а так же многие другие доступны в интернете.

Только зарегистрированные пользователи могут участвовать в опросе. Войдите, пожалуйста.

Комментарии (53)

NiOS

17.04.2015 13:49>сброс асинхронный, он должен быть синхронен тактовому сигналу

На практике как раз реализуют синхронизацию снятия асинхронного сброса, тк возможность метастабильности при установке асинхронного сброса не важна (и флип-флоп сбросится еще до начала генерации клока).

Если асинхронный сброс полностью синхронен к клоку, то логичней использовать вход «синхронного сброса», чтобы не использовать флип-флопы со входом асинхронного сброса/установки, которые занимают большую площадь.

nerudo Автор

17.04.2015 14:16Что касается синхронного/асинхронного сброса в целом — все зависит от элементной базы. Для заказных микросхем действительно асинхронный сброс требует больше ресурсов. Но для FPGA — он там уже есть и доступен «бесплатно». Более того, синхронный сброс задействует дополнительный мультиплексор, который иначе может быть задействован в «пользовательском» режиме синтезатором.

С моей точки зрения, как разработчика на FPGA — если уж снятие сброса подсинхроизировано, то и установку проще тоже подсинхронизировать, просто пропустив сброс через цепочку триггеров, чем еще что-то городить. Хотя может я не знаком со всем многообразием ситуаций…MichaelBorisov

17.04.2015 15:03Вообще, если принимать во внимание явление метастабильности — то использование асинхронного сброса оказывается себе дороже. Когда я стал проектировать под FPGA с учетом метастабильности — то в моих проектах триггеры с асинхронным сбросом исчезли как класс. Если заботиться о борьбе с метастабильностью — то асинхронный сброс ничуть не упрощает схему по сравнению с использованием синхронного сброса.

Неудивительно, что в новых сериях FPGA Xilinx (Artix-7, Kintex-7) асинхронный сброс триггеров отсутствует.

nerudo Автор

17.04.2015 15:30Не пугайте так — асинхронный сброс в 7 серии остался, просто теперь он является разделяемым с синхронным. Т.е. одновременно и того и другого [аппаратного сигнала сброса] у триггера быть не может. А так и синхронный и асинхронный поддерживаются. Иначе это был бы слишком кардинальный шаг, ломающий совместимость с 90% существующего кода.

NiOS

17.04.2015 15:40+2Не следил за текущей ситуацией.

Но поползновения отказаться от асинхронных сбросов начались еще у Altera лет 5 назад. Хотели так сделать, но не знаю сделали по факту в каком-то семействе.

Как раз рассматривали такой вариант по совокупности причин, что в FPGA все заточено на синхронный дизайн + отдельные линии/площадь нужны для асинхронные цепей + флип-флоп занимает больше места, но тогда ресет включался бы в расчет пути данных и требовал бы еще задержку+площадь на один гейт перед входом флип-флопа.

MichaelBorisov

17.04.2015 15:46+2Хм, я ошибся, действительно, асинхронный сброс остался. Но его использование не рекомендуется. Есть параграф в UG429 (7 Series Migration Guide), где указаны его недостатки и рекомендации по устранению его использования.

whiteTigr

20.04.2015 09:34+1> Если заботиться о борьбе с метастабильностью — то асинхронный сброс…

Извиняюсь, что вырываю фразу из контекста. Асинхронный сброс опасен не только метастабильностью, но и тем, что он может поймать «иголку» — явление, когда, допустим, компаратор выдает короткий сигнал из-за того, что ему на вход пришло промежуточное состояние шины (сравнивает на 0b0000, счетчик при переходе из 0b0111 в 0b1000 «случайно» прошел через промежуточное состояние 0b0000), — и сбросится не по своему условию.

Ну и второй момент — если клока нет, то зачем сбрасывать, все равно ведь ничего работать не будет.MichaelBorisov

20.04.2015 13:12+1тем, что он может поймать «иголку»

Вот, очень разумное замечание! Разработчик, пользующийся асинхронным сбросом, должен принимать во внимание все эти иголки, которыми кишмя кишат комбинационные схемы.

если клока нет, то зачем сбрасывать

Ну, например, чтобы перевести выходные сигналы в наиболее безопасное состояние, чтобы все было отключено, токи не шли, одним словом — чтобы система (включая ее исполнительные органы) не ломалась.

whiteTigr

20.04.2015 13:47Ну, например, чтобы перевести выходные сигналы в наиболее безопасное состояние, чтобы все было отключено, токи не шли, одним словом — чтобы система (включая ее исполнительные органы) не ломалась.

Хм, логично. Хотя тут реализации могут быть разными — возможно, не асинхронный сброс регистра, а например, мультиплексер перед выходом, по сигналу «clk_stopped» от dcm. И даже при всех советах о синхронных дизайнах, сам xilinx в dcm ядре использует асинхронный сброс. Насколько я понимаю, нас пытаются уберечь от неправильного использования, но при аккуратном использовании асинхронный сброс все же полезен в некоторых критичных местах.MichaelBorisov

20.04.2015 20:05мультиплексер перед выходом

Мультиплексоры — это трата ресурсов FPGA и дополнительная задержка сигнала на выходе. Если есть возможность, я предпочитаю выводить наружу сигналы прямо с триггеров, а если есть возможность — то и с IOB FFs.

Ну а так да, я согласен с вами, что применение асинхронного сброса (если разрабатывать по науке) очень ограничено, поэтому его следует постепенно выпилить из базовых логических ячеек FPGA, а если оставить — то только в небольшом их подмножестве.

То же касается использования триггеров в режиме Latch (проходная защелка). В моем довольно крупном проекте нет ни одной такой защелки. На D-триггерах все получается менее запутанно и более надежно. Эту функцию тоже можно постепенно выпиливать.

NiOS

17.04.2015 15:34+1Я здесь хотел акцентировать внимание именно на ситуации, что хотя входы и называются «асинхронными», но при снятии асинхронного ресета происходит переход у синхронному состоянию работы. И именно в этот момент образуется проблема метастабильности про которую вы пишите.

Те отделить «мух от котлет» и показать суть проблемы в этом случае, а не ограничиться шаблоном делайте всегда вот так.

valeriyk

05.05.2015 21:42+1Синхронный сброс требует тактового сигнала, но иногда бывает нужно сбросить все триггеры до того, как тактовый сигнал появится (например, в контроллере JTAG, если он тактируется сигналом TCK, а не внешним тактовым сигналом).

Именно поэтому самый универсальный вариант — асинхронная установка сигнала сброса и синхронное снятие, то есть сбрасываем сразу, как только пришел сигнал сброса, а выводим из ресета только после синхронизации, чтобы быть уверенными, что все триггеры выйдут из ресета одновременно (на одном такте).

valeriyk

06.05.2015 15:37Правда, такой «универсальный» вариант, скорее всего, не будет работать для DFT-шного scan-теста (но это актуально только для ASIC-ов).

Поэтому самый универсальный вариант такой:

input clk; input bad_reset; input dft_mode; output good_reset; reg [1:0] rst_sync_r; always @(posedge clk, posedge bad_reset) if (bad_reset) rst_sync_r <= 2'b11; else rst_sync_r <= {rst_sync_r[0], 1'b0}; assign good_reset = (dft_mode) ? bad_reset : rst_sync_r[1];

Alexeyslav

17.04.2015 13:50Видимо половина питания на выходе получается из-за того что открываются оба ключа на выходе на "+" и "-" шины. Вроде бы как недолго в таком состоянии находится, но если это сделают сотня триггеров одновременно? какие иголки по питанию пойдут при этом…

MichaelBorisov

17.04.2015 15:51+1Половина питания (примерно) на выходе получается из-за того, что если нарисовать схему триггера полностью и рассмотреть ее как аналоговую — то именно в этом положении у нее имеется состояние неустойчивого равновесия.

Простой пример — рассмотрите схему триггера Шмитта. Это усилитель (идеальный ОУ) с положительной обратной связью. Существует такой уровень входного напряжения, при котором выходное напряжение равно ему, и отсутствуют процессы, стремящиеся вывести схему из этого состояния (т.е. напряжение на входах идеального ОУ равно 0).

И это не зависит от схемотехники конкретного логического семейства, будь то КМОП, ТТЛ или даже РТЛ. Везде, в любых триггерах, существуют состояния неустойчивого равновесия. Различаться могут только конкретные уровни напряжения, соответствующие этому состоянию.

andy_p

17.04.2015 14:06Есть такая вещь, как самосинхронные схемы, которые избавлены от этого недостатка.

nerudo Автор

17.04.2015 14:36Я слабо знаком, но у меня есть ощущение, что они существуют пока только на бумаге (ну или в каких-то нишевых решениях). Тот же Achronix, обсуждавшийся давеча, пытался сделать «асинхронную» FPGA, но пока так и не сделал…

Halt

17.04.2015 14:59+1В статье www.russianelectronics.ru/leader-r/review/2189/doc/49789 пишут о том что подход вполне применяется. Делают как FPGA так и целые ARM ядра.

andy_p

17.04.2015 20:42+1Дядька мой этой темой занимается.

m.mathnet.ru/php/archive.phtml?wshow=paper&jrnid=ia&paperid=332&option_lang=rus

nerudo Автор

17.04.2015 22:33+1О как, я как раз увидев фамилию автора статьи и посмотрев ваш профиль подумал — не родственники ли, часом ;)

valeriyk

05.05.2015 21:55+1Что-то никакого промышленного применения не наблюдается. ARM-ядро (AMULET) было сделано, если мне не изменяет память, где-то в 1995 году, т.е. 20 лет назад.

Есть хорошая книга про асинхронные схемы, правда стоит $245 на Амазоне: www.amazon.com/Principles-Asynchronous-Circuit-Design-Perspective/dp/0792376137/ref=sr_1_1?ie=UTF8&s=books&qid=1247408117&sr=8-1

А вот ее совершенно бесплатная (легальная!) версия, чуть-чуть урезанная: eecourses.technion.ac.il/048878/book.pdf — не благодарите :)

Самое интересное, что это одна из немногих областей, где был заметный в мировом масштабе вклад отечественных ученых (Варшавский и компания из ЛЭТИ).

Halt

06.05.2015 07:26+1За ссылку спасибо. А про Варшавского я в курсе, из других источников правда :) Насколько я помню, русскоязычный коллектив занимался этим в университете Айдзу в Японии.

Можно наверное спросить rg_software что там сейчас происходит и развивают ли тему.

amartology

19.04.2015 12:59А с чего, простите, у них нет этого состояния? Там точно такие же триггеры, как и везде.

valeriyk

05.05.2015 22:10Для метастабильного состояния нужен тактовый сигнал, а там его нету

amartology

06.05.2015 12:36Для метастабильного состояния нужен не тактовый сигнал, а наличие обратной связи, которая в самосинхронных схемах вполне себе есть.

canny

17.04.2015 14:38Из литературы я бы еще посоветовал статьи И. Каршенбойма цикл «Краткий курс HDL».

Автору — пишите еще. )))

MichaelBorisov

17.04.2015 15:07Я бы еще рекомендовал статью «Fourteen Ways to Fool Your Syncrhonizer». Там подробно рассматриваются типичные ошибки при проектировании схем синхронизаторов, объясняется, почему они не работают, и приводятся правильные решения.

Что же касается двухпортового ОЗУ — то само по себе оно еще не реализует асинхронное FIFO. Для реализации асинхронного FIFO нужно еще много интересных блоков, таких, как счетчики в коде Грея и прочие синхронизаторы. О проектировании асинхронного FIFO можно было бы написать отдельную статью.

MichaelBorisov

17.04.2015 15:30+1Триггер можно сравнить с маятником на жестком стержне. У этого маятника есть два состояния равновесия. Первое — когда маятник внизу, а второе — когда он наверху. Первое состояние устойчивое, второе — нет.

Если маятник находится не совсем точно в положении устойчивого равновесия, или если на него подействовать силой — то он будет самопроизвольно возвращаться к положению равновесия. Колебательный процесс затухнет через некоторое время из-за трения.

Если же маятник находится в состоянии неустойчивого равновесия — то любое сколь угодно малое отклонение, или любое малое воздействие, приведет к возникновению силы, стремящейся увеличить отклонение от неустойчивого равновесия. Чем дальше маятник от положения неустойчивого равновесия — тем больше эта сила. В конце концов, поскольку физически невозможно поставить маятник точно в верхнее положение, и поскольку в реальном мире постоянно действуют (хоть и малые) возмущения — маятник рано или поздно выйдет из положения неустойчивого равновесия и самопроизвольно в него больше не вернется.

Однако сила, удаляющая маятник от положения неустойчивого равновесия, пропорциональна его отклонению. Поэтому, если маятник исходно установлен близко к положению равновесия — то эта сила может быть сколь угодно мала. Фактически, около положения равновесия, траектория маятника является возрастающей экспонентой. Хоть экспонента возрастает быстро, но в левой координатной полуплоскости она за бесконечное время возрастает на конечную величину. Поэтому, если маятник поставить в положение неустойчиовго равновесия с большой точностью, время, за которое он сам выйдет из этого положения, может быть сколь угодно большим.

В схеме любого триггера (хоть RS, хоть D, хоть JK, хоть Шмитта) есть два основных элемента, хоть иногда и не выделенные явно:

1) усилитель с ограничением выходного сигнала

2) положительная обратная связь

Эта схема имеет два положения устойчивого равновесия и одно — неустойчивое. Около положения неустойчивого равновесия триггер ведет себя как чисто аналоговая схема, которую можно изобразить в виде операционного усилителя с положительной обратной связью. Зависимость выходного сигнала от времени (если исходное значение сигнала находилось близко к положению неустойчивого равновесия) является возрастающей по экспоненте синусоидой, т.е. exp(k*t)*sin(2*pi*f*t), где f — частота резонанса, k — константа, зависящая от коэффициента усиления усилителя).

То, что процесс является колебательным (с возрастающей амплитудой), вносит дополнительные схемотехнические трудности. Схема, измеряющая выходное состояние триггера при его выходе из метастабильного состояния, может зафиксировать колебания. Если это асинхронный счетчик — то его значение может увеличиться на произвольную величину.MichaelBorisov

17.04.2015 15:35+1Так что триггер Шмитта (который совсем уж явно является усилителем с положительной обратной связью) тоже подвержен метастабильности.

janatem

17.04.2015 16:21+4За кадром осталось самое вкусное: как FIFO на границе тактовых доменов будет работать в качестве не только переходного блока, ни и как собственно FIFO. То есть, когда требуется отследить переполнение очереди (и наоборот, попытку чтения из пустой очереди). В этом случае придется передавать значения указателей rx и tx через границу доменов, но, поскольку это можно делать не очень точно (разрешается использовать немного устаревшее значение), спасает код Грея. А у него в основе которого лежит довольно красивая математика, с которой было бы неплохо ознакомить публику.

nerudo Автор

17.04.2015 16:29Мифическое мировоззрение порой заметно облегчает жизнь: это чертова черная магия (англ. pure fucking magic), которая работает ;-)

PS Рассказывать это долго, сложно, и не уверен, что здесь нужно. Может в следующий раз…

whiteTigr

20.04.2015 09:41IP-ядра в ISE/Vivado так и делают. Они передают значения счетчиков в коде Грея, а на принимающей стороне преобразуют обратно. Хотя, вроде бы, не советуют пользоваться этими счетчиками и советуют использовать только однобитные сигналы состояния FIFO.

amarao

17.04.2015 16:31+1Спасибо, я узнал ещё одну вещь, которую я знать не хочу. Оно как-то работает, может навернуться в любой момент, и все отвернулись и делают вид, что так и должно быть.

VioletGiraffe

17.04.2015 19:48+1Где вариант «когда-то изучал FPGA, но пошёл работать программистом и всё забыл»? :)

Хотел заниматься FPGA, но предложений работы в этой сфере после университета не получил, поэтому пошёл прокачивать навыки програмирования — благо, этому тоже учили. Не жалею, но обидно, что учил ненужное вместо нужного.

Хотя, разносторонний кругозор — тоже неплохо.

nata16k8

17.04.2015 22:081. «Метастабильное состояние — состояние квазиустойчивого равновесия физической системы, в котором система может находиться ДЛИТЕЛЬНОЕ время». (Википедия). На первом рисунке из статьи показано нестабильное состояние, а не метастабильное состояние.

2. Не знаю ни одного прочитанного учебника, где-бы показывалось наличие метастабильного состояния в схемах триггеров. Однако метастабильное состояние очень просто возникает при МОДЕЛИРОВАНИИ схем: в реальных устройствах всегда присутствуют шумы, помехи и т.п., которые могут являться первопричиной переключения, а при моделировании схем таких причин нет. Поэтому график для Q(3) на четвертом рисунке, и графики на пятом рисунке, возможно, возникают только при моделировании.

3. К сожалению не зная схемотехники триггеров говорить о наличии эффекта метастабильности в них сложно. В работе, возможно, описывается известное явление «состязания» в цифровых схемах.

nerudo Автор

17.04.2015 22:45+3Всей нити рассуждений не уловил в виду вечера пятницы, но должен расстроить: метастабильность — эффект физического мира. Пятый рисунок получен осциллографом подключенным прямо к микросхеме. Вот тут в первом абзаце краткая история признания этого эффекта (с исторической картинкой, хотел сперва ее спереть для публикации).

Состязания (гонки) в цифровых схемах — другой эффект, возникающий из-за разного времени распространения сигнала через участки комбинационной схемы. Гонки проявляются в виде множественного переключения пока схема не перейдет в статическое состояние.

nata16k8

18.04.2015 00:05+1Прочитал о 50-летней истории эффекта в триггерах, за ссылку спасибо.

Хорошо бы поправить первый Ваш рисунок в соответствии со статьей в википедии и физическом словаре. Он испортил первое впечатление и вызвал недоверие к Вашей, теперь, после перечтения поправляюсь, очень хорошей статье.

MichaelBorisov

18.04.2015 13:23+3Не знаю ни одного прочитанного учебника, где-бы показывалось наличие метастабильного состояния в схемах триггеров

Попробуйте почитать Хоровиц и Хилл «Искусство схемотехники», глава 8, параграф 8.34

MichaelBorisov

18.04.2015 13:42+1К сожалению не зная схемотехники триггеров говорить о наличии эффекта метастабильности в них сложно.

Вот вам схема триггера Шмитта:

с использованием идеального операционного усилителя.

Если теперь представить начальное состояние, в котором IN=OUT=2.5В, то напряжение между входами ОУ = 0, поэтому такое состояние допускается математической моделью, и нет никаких причин для изменения выходного сигнала ОУ.

Это состояние равновесия неустойчиво, и из-за возмущений и неточной реализации начальных условий схема рано или поздно выйдет из этого состояния. Но, как уже было рассмотрено выше, процесс выхода может занять сколь угодно длинное время. Правда, вероятность длительного выхода убывает по экспоненте, так что на практике реально длительное сохранение такого равновесия будет наблюдаться чрезвычайно редко.

nata16k8

18.04.2015 15:051. В книге «Искусство схемотехники» (П. Хоровиц, У. Хилл) метастабильное состояние только упоминается, как любопытный эффект, но не рассматривается и не объясняется.

2. Схема триггера Шмитта находится в НЕУСТОЙЧИВОМ состоянии. МЕТАСТАБИЛЬНОЕ состояние — это 3-е, особое состояние (см. википедию или физическую энциклопедию).MichaelBorisov

18.04.2015 20:12+1только упоминается, как любопытный эффект, но не рассматривается и не объясняется.

К чему эти придирки? Вы ведь явно не читали этот учебник и многие другие, если сами признались, что не знаете схемотехнику триггеров. Схемы триггеров приводятся, я думаю, в любом уважающем себя учебнике по электронике и рассматриваются на лекциях в вузах.

Для меня лично, когда я читал этот учебник, явление метастабильности врезалось в память, хоть Хоровиц и Хилл пишут о нем полстраницы из всего талмуда в более 1000 страниц. Потому что это важная, критическая информация, от которой может зависеть работоспособность схем. И, когда я уже в реальной деятельности столкнулся с предупреждением о возможной метастабильности — то потрудился загуглить и найти все подробности. Чего и вам желаю. А то выглядит так, будто вы сюда спорить пришли и самоутверждаться, а не обогащать свой кругозор новыми знаниями.

см. википедию или физическую энциклопедию

Это спор о терминологии. Все дело в том, что в английском языке для описания того явления в цифровых схемах, которое рассматривается в статье, используется термин «metastable state», который часто переводят на русский язык буквально: «метастабильное состояние».

Посмотрел по ссылкам в Википедии. Тут я склонен с вами согласиться. Возникает впечатление, что в обоих языках для описания явлений в триггерах применение этого термина ошибочно. Там отсутствует равновесное состояние, устойчивое к малым возмущениям, кроме двух «обычных» состояний. Поэтому следовало бы говорить не о метастабильности, а о состоянии неустойчивого равновесия, о котором я писал во многих комментариях здесь.

Тем не менее, это сложившаяся терминология в данной области.

nata16k8

19.04.2015 00:16+1Уж извините, что не так. Просто хотелось обратить внимание автора и читателей на некорректный первый рисунок в статье, на котором показано нестабильное состояние, а не метастабильное состояние.

MichaelBorisov

19.04.2015 01:08Нет проблем. В самом деле, вы оказались правы, это ошибочная терминология принята в электронике.

Alexeyslav

20.04.2015 08:38Похоже, что любой триггер подвержен такому состоянию. Больше-меньше но подвержен. несложно представить из-за чего это происходит — триггер это схема с обратными связями, пути сигналов синхронизации и данных проходят через разные элементы, а значит существует такая комбинация сигналов на входе которая может нарушить внутреннее состояние схемы. Чем точнее подгоним эти пути тем меньше будет «окно», но оно будет всегда.

NiOS

20.04.2015 15:32Как-то странно написано. «Окно» всегда есть, но есть шаги/решения, которые гарантировано позволяют избежать этих проблем. Соответственно при правильной реализации в принципе не может быть «такая комбинация сигналов на входе которая может нарушить внутреннее состояние схемы».

valeriyk

05.05.2015 21:45В статье неявно сказана одна очень важная вещь, которую надо бы особо выделить: критически важно триггеры синхронизатора располагать как можно ближе друг к другу, это прямым образом влияет на время наработки на отказ, причем разница может быть на десятки порядков: www.aspenlogic.com/images/alj001.pdf

AEP

Занимаюсь электроникой, но метастабильность у меня больше ассоциировалась с приемом внешних аналоговых сигналов, и поэтому для меня странно, что в статье не упоминается триггер Шмитта, который по идее надо бы поставить перед D-входом первого тактируемого триггера.

nerudo Автор

Согласен, это упущено. Попробую дополнить потом.

Но, с одной стороны, я все таки больше ориентировался на внутренние асинхпрнные клоки, а с другой — в большинстве современных FPGA внутри входного пина триггера Шмитта нету, а ставить внешние по всем входам — слишком дорогое удовольствие. Да и бессмысленное, честно говоря, т.к. он окончательно проблему все равно не решит — время переключение отлично, от нуля, а значит вероятность попадания стоящего за ним триггера при неудачном совпадении фронтов остается.

amartology

Кроме того, ни слова не сказано про возникновение метастабильности и последующую возможность переключения в неизвестное состояние при подаче питания на микросхему. А ведь для того, чтобы ее избежать, приходится делать достаточно большие цепи глобального сброса.

А еще нежелательные стабильные состояния бывают не только у триггеров, но и у многих аналоговых схем, где для борьбы с ними тоже применяется много интересного.

А в целом — хорошая и полезная статья, спасибо.

nerudo Автор

Ну стартовая инициализация — весьма отдельная непростая тема, к которой я не готов ;) Могу лишь сказать, что пользователям FPGA в этом смысле значительно проще, там много сделано сразу «из коробки», а вот если самому с нуля микросхему проектировать… страшно представить.

amartology

А бывает еще стартовая инициализация аналоговых микросхем, которая часто некорректно моделируется)