В 2023 году появилось много всего интересного, связанного с FPGA. Компании ставят рекорды, выпускают новые чипы и разрабатывают технологии, которых не было раньше. Сегодня обо всём этом и поговорим. Что же, самое интересное — под катом.

Самая большая чиплетная ПЛИС от AMD

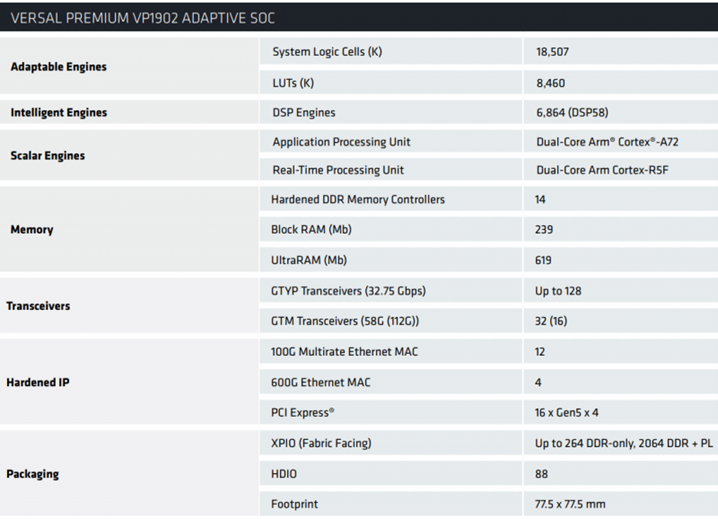

Корпорация AMD активно развивает своё присутствие на рынке современных чипов. Так, благодаря технологиям, которые достались этой компании от Xiling, в плане разработки программируемых матриц, AMD удалось достичь интересных результатов. Компания смогла создать самую большую и сложную FPGA, причём сделала это уже который раз. Если ранее это была Xilinx VU19P, то сейчас речь идёт об AMD VP1902, пополнившей серию Versal Premium.

Стоит упомянуть и чиплетную индустрию, которая даёт возможность создавать очень сложные и весьма мощные решения. Новая матрица, AMD VP1902, как раз из таких. Она состоит из четырёх чиплетов. Они объединены высокоскоростным программируемым интерконнектом в массив с размерами 77 × 77 мм.

Зачем увеличивать сложность FPGA? Дело в том, что чем больше эмулируется ядер, тем большее количество логических ячеек требуется.

Кроме этого, в состав чипа входят также 14 защищённых контроллеров DDR, четыре MAC-блока Ethernet-класса 600G (100–400GbE) и 12 блоков 100G (10–100GbE), а также четыре фиксированных блока PCIe 5.0 x16.

Ну а первые образцы системы появятся в III квартале 2023 года, массово же чип будут производить в первой половине следующего года.

IntelFPGA Agilex 7 с поддержкой PCIe 5.0 и CXL от Intel

Не стоит в стороне и корпорация Intel. Ещё в мае 2023 года она заявила о запуске производства программируемых вентильных матриц (FPGA) семейства Agilex 7, предназначенных для ускорения выполнения различных задач, связанных с обработкой данных.

У этих решений гетерогенная многокристальная архитектура. В центре — как раз FPGA, которая соединена через мост Intel Multi-Die Interconnect Bridge (EMIB) с трансиверами. Каждый чиплет специализируется на выполнении определённых функций.

Что касается текущего семейства матриц, в их состав входит R-Tile. Она, в свою очередь, включает блоки PCIe 5.0 x16 и CXL 1.1/2.0. Это даёт возможность обеспечить высокую гибкость при использовании в сетях передачи данных, в «облаках», HPC и для решения других задач. Быстродействие для одной линии — 32 GT/s.

Новинка позволяет повысить эффективность работы ЦОД и сократить затраты. Систему можно использовать в серверах на базе процессоров Intel Xeon Sapphire Rapids.

AMD усилилась благодаря покупке разработчика ИИ-решений для FPGA из Франции и объединяет усилия с Xilinx

Этим летом появилась и ещё одна интересная новость: дело в том, что AMD расширила свои возможности в плане производства FPGA, приобретя французскую компанию Mipsology из Палезо (Франция), специализирующуюся в области программного обеспечения для искусственного интеллекта. По словам представителей обеих сторон, эта сделка позволяет AMD дополнить собственный стек ИИ-решений.

Сама Mipsology разрабатывает передовые решения для инференса и инструменты оптимизации нагрузок, адаптированные для оборудования AMD. Раньше компании активно сотрудничали, но сейчас всё это закончилось поглощением.

«ИИ является нашим главным стратегическим приоритетом и важным фактором роста спроса на полупроводники в ближайшее десятилетие. Приветствуя квалифицированную команду Mipsology в AMD, мы продолжим расширять возможности нашего программного обеспечения, чтобы позволить клиентам по всему миру использовать огромный потенциал повсеместного ИИ», — отметил представитель AMD в блоге компании.

Ну а в отношении Xilinx всё ещё интереснее. Дело в том, что AMD и Xilinx объединились ещё в 2022 году. Сейчас AMD отвечает за финансирование деятельности партнёра. Для того чтобы стимулировать развитие новых технологий, AMD выделила $135 млн на развитие.

Инвестиции направлены на финансирование важнейших направлений работы, что, видимо, вскоре ознаменуется выходом новых матриц или связанных с отраслью решений. Пока что создан единый исследовательский центр, в рамках которого и выполняются научно-исследовательские работы.

Мощные SoC Versal HBM для ИИ-задач от AMD

И снова в центре внимания — AMD, сегодня уж так получилось. Так вот, компания несколько дней назад анонсировала организацию выпуска однокристальных систем (SoC) серии Versal HBM. Они могут применяться как для работы в облачных платформах, ИИ-решениях, так и для периферии.

По словам разработчика, здесь удалось добиться шестикратного увеличения пропускной способности, а также сокращения энергопотребления примерно на 65% из расчёта на бит.

Уже готов и комплект VHK158 Evaluation Kit для тестеров. Он получил 32 Гб памяти HBM, два слота DDR4-3200 DIMM, интерфейсы PCIe 5.0 x8 и PCIe 4.0 x16. В качестве процессора приложений задействован чип с двумя вычислительными ядрами Arm Cortex-A72.

Что касается платы, то разработчики предусмотрели слот microSD, трансиверы 112G PAM4, разъёмы QSFP28 и QSFP-DD, коннектор FMC+. Пропускная способность памяти HBM достигает 819,2 Гб/с. Габариты составляют 247 × 220 мм.

Стоит всё это, конечно, много — от $15 000.

Комментарии (10)

NutsUnderline

28.09.2023 07:05+3Какие то тут все ПЛИС не просто большие а огромные. Есть че нить типа tqfp32 ?

checkpoint

28.09.2023 07:05+4Смотрите на Gowin GW1N и Lattice iCE40. Дешево. Сердито. Поддерживаются в Yosys.

ПЛИСы про-ва Altera и Xilinx давно превратились в монстров и ПЛИСами, в классическом понимании, более не являются, так как у них более половины площади кристалла содержат специализированные IP блоки и ARM яра. Также они требуют установки проприетарной среды и получение дорогостоящих лицензий на работу в ней и с IP блоками. Есть ограниченные условно-бесплатные версии, но с большей частью наворотов этих ПЛИС поработать не получится.

NutsUnderline

28.09.2023 07:05точнее то конечно https://www.gowinsemi.com/en/product/detail/46/ но там надо зарегаться для скачки

checkpoint

28.09.2023 07:05+1Пользуйте Yosys, в нём достаточно неплохо поддеживаются ПЛИС Gowin и без регистраций. :)

AlexanderS

28.09.2023 07:05Интересно стало поиграться) А правильно я понимаю, что для того чтобы синтезировать/имплементировать нужно поставить Tabby CAD -> OSS CAD Suite -> yosys?

checkpoint

28.09.2023 07:05+6TabbyCAD это попытка создателей Yosys создать коммерческий продукт на базе уже разработанных open source утилит, это больше подходит для бизнеса который не хочет заморачиваться с установкой различного СПО с его зависимостями. :-) Можно конечно зайти и с этой стороны. Но мне кажется, что поставить Yosys и сопутствующие утилиты из репозиториев не так сложно и у Вас будет возможность постоянно апдейтиться. Установить нужно следующее:

https://github.com/YosysHQ/yosys.git - Yosys synthesis tool.

https://github.com/YosysHQ/nextpnr - Place and route tools, depend on chip.

https://github.com/YosysHQ/apicula - Tools and database for Gowin GW1N.

https://github.com/trabucayre/openFPGALoader - Tool for flashing FPGAs.

В некоторых дистрибутивах ОС Linux, а также в ОС FreeBSD, все это можно установить из пакетов, т.е. командой вида apt-get install yosys.

UPD1: Вот тут доступны готовые сборки: https://github.com/YosysHQ/oss-cad-suite-build/releases/latest

UPD2: Юрий Панчул выложил большой набор обучающих дизайнов в виде лабораторных работ для большого спектра FPGA плат. Лабы постороенные по мере увеличения сложности, начиная от простой работы с логикой (Де Морган) и заканчивая конвейерной обработкой. Доступно тут: https://github.com/yuri-panchul/basics-graphics-music

NutsUnderline

28.09.2023 07:05Насколько я понял Tabby CAD вроде все таки не надо, надо OSS CAD Suite , либо самому компилировать по кускам, в общем - перемещаться в весьма сторонние от FPGA вещи

VBKesha

28.09.2023 07:05Самая большая чиплетная ПЛИС от ADM

Может таки AMD всё таки.

Зачем увеличивать сложность FPGA? Дело в том, что чем больше эмулируется ядер, тем большее количество логических ячеек требуется.

Что что эмулируется?

strvv

28.09.2023 07:05+1в том же разделе и Xiling...

чем больше увеличивается сложность - тем больше шансов удлинить цепочку и тем самым ограничить скорость распространения сигнала.

nckma

Ну и написали бы еще про последнюю ПЛИС от Миландра.

Для сравнения так сказать.