Продолжая тему самодельного простого интерфейса https://habr.com/ru/articles/769986/ , как всегда, интереса ради и просто так, разработал концепцию сети на описанном ранее протоколе нижнего уровня. Представленная сеть, может быть пригодна для связи между несколькими ПЛИС внутри печатной платы (ПП); связи между ПП внутри блока, а также связи отдельных блоков с длиной линии передачи между узлами сети до 50м, а может и более.

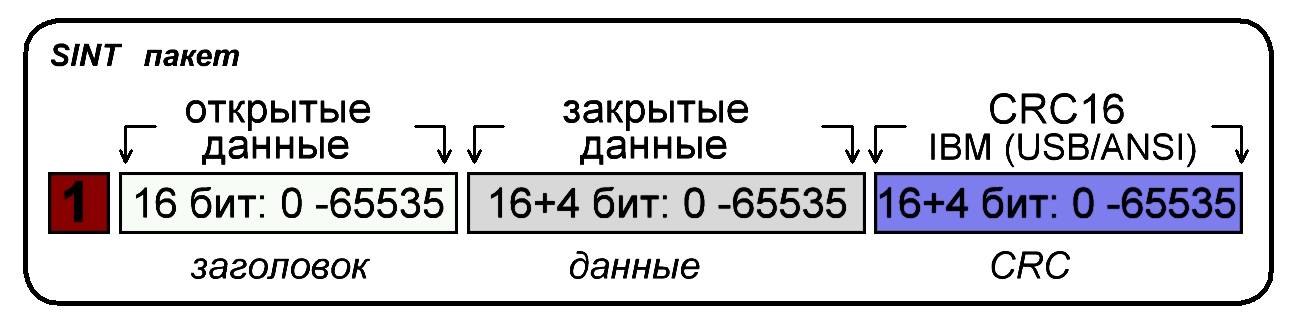

Сеть разделяется на несколько уровней, первый уровень аппаратный – в него входят непосредственно линия связи, метод кодирования и модули приемника и передатчика. Более подробно модули приемника и передатчика рассмотрены в https://habr.com/ru/articles/769986/ . Однако, для дальнейшего повествования необходимо определиться в терминологии, в чем поможет рисунок 1, на котором подставлена структура SINT пакета.

SINT пакет состоит из заголовка в виде блока из 16 бит, зашифрованной области данных с «солью» и 16 битное CRC.

Следующий уровень – уровень контроллера кольцевой шины, обеспечивающий взаимодействие до 65K равноправных узлов в одном кольце (зависит от параметра максимального времени ожидания «эхо» ответа). На этом уровне происходит проверка на коллизии, арбитраж шины, проверка целостности данных, реализованы разные режимы отправки.

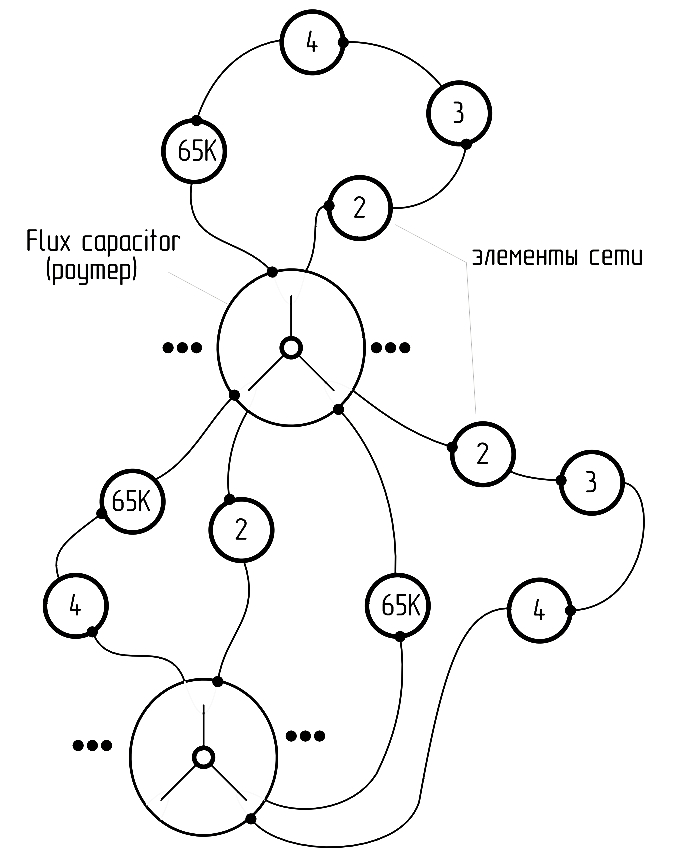

Третий уровень – уровень разветвленной сети, который является необязательным и нужен только для организации сложных многосвязных сетей с возможностью образования мостиковых связей. На данном уровне некоторые узлы кольцевой шины реализуют функции роутера и позволяют соединять несколько кольцевых сетей в одну связанную область пузырьковой сети, как показано на рисунке 2.

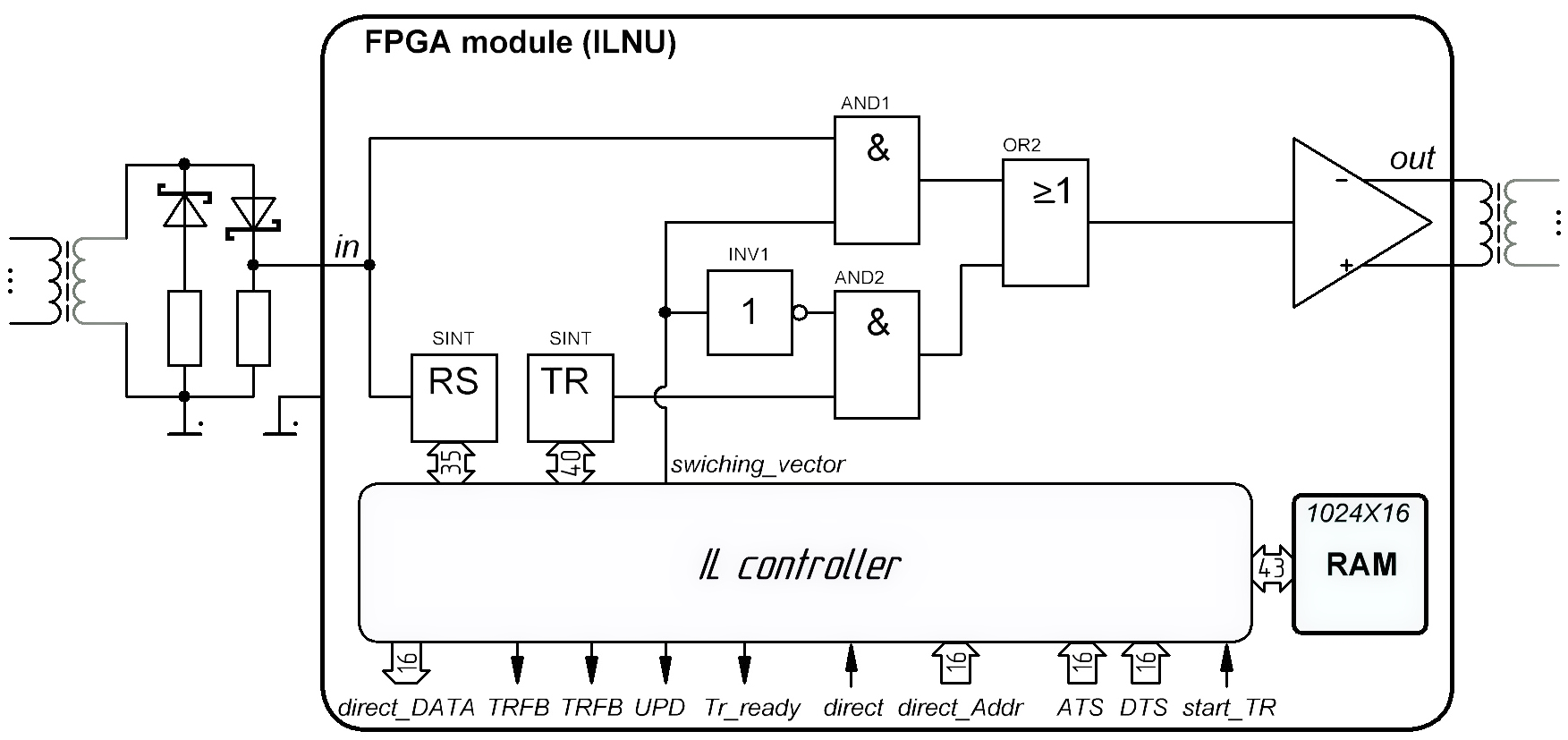

В любом случае, на третьем уровне находится процессорный модуль, выполняющий целевую программу узла и функции роутера, обрабатывая адресацию по смежным кольцам, а также некоторые сложные моменты, такие как критические проблемы при потоковой передаче или неразрешимые коллизии. В любых остальных случаях разноуровневые контроллеры кольцевой сети берут на себя все задачи по сетевому взаимодействию, а для процессорного модуля и основной программы, исполняемой на нем, работа с сетью подчиняется принципу – отправил и забыл. Упрощенно структура узла сети «IL_net» показана на рисунке 3.

На нижнем уровне протокол сети «IL_net» основан на интерфейсе «SINT» и реализующих его модулях приемника и передатчика «SINT_RS» и «SINT_TR».

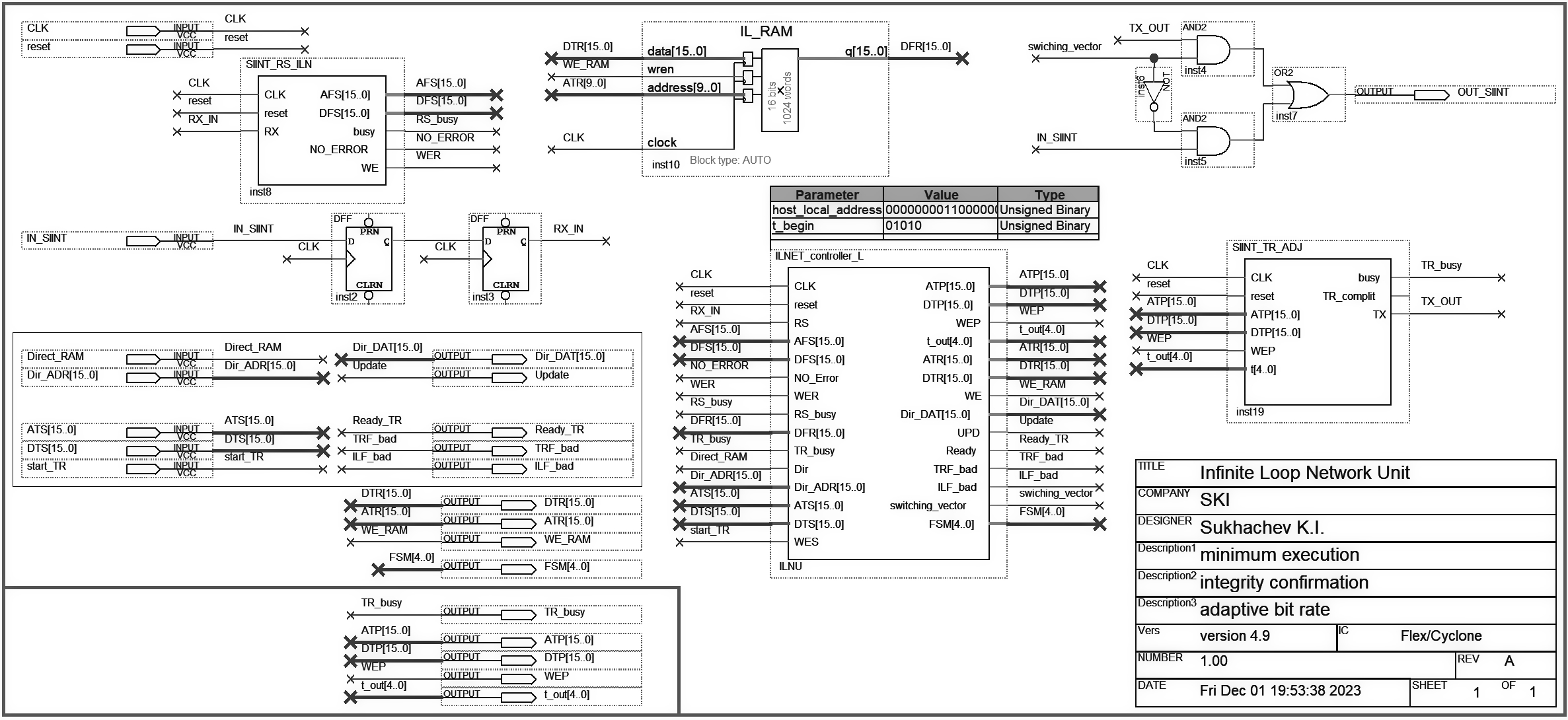

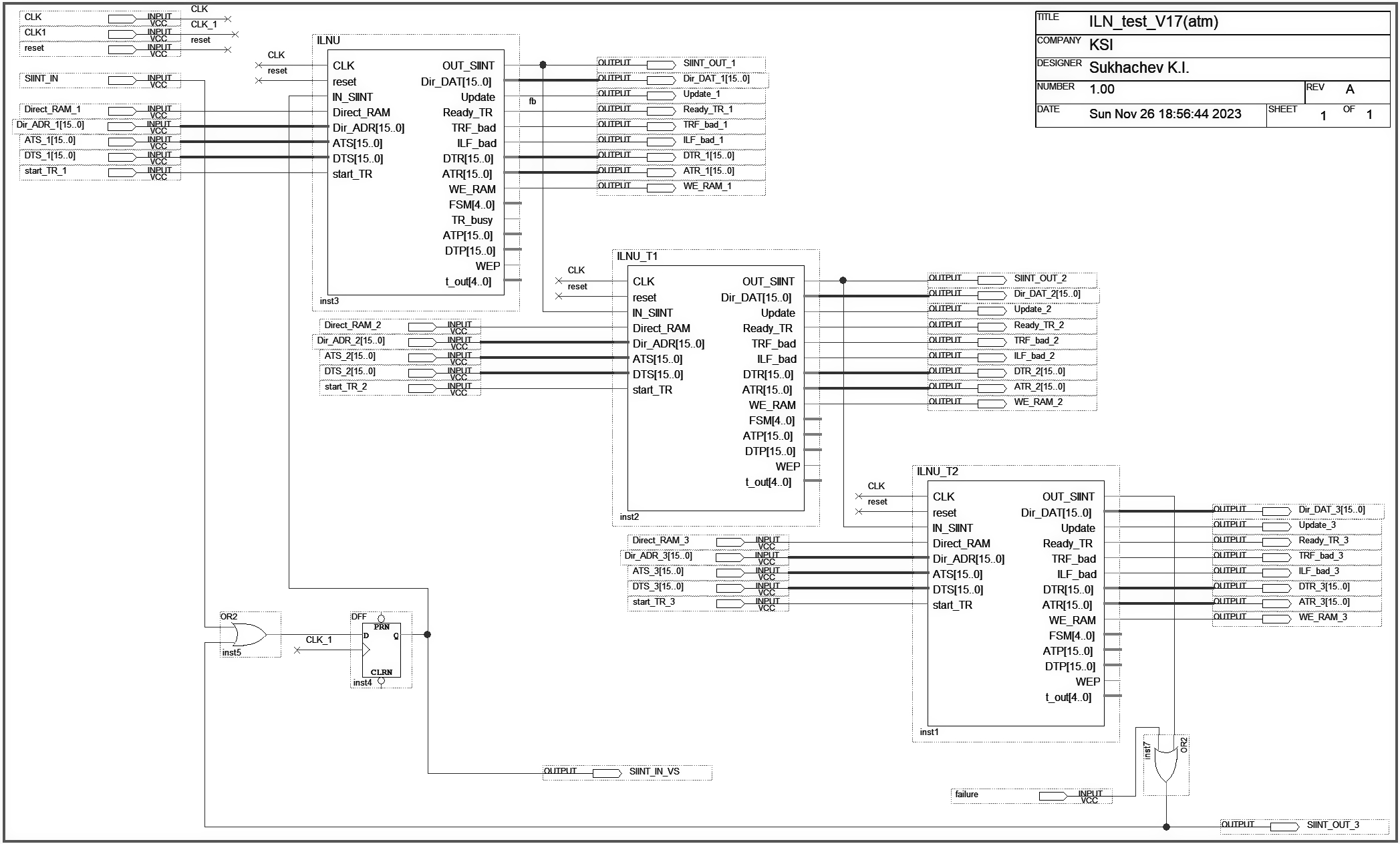

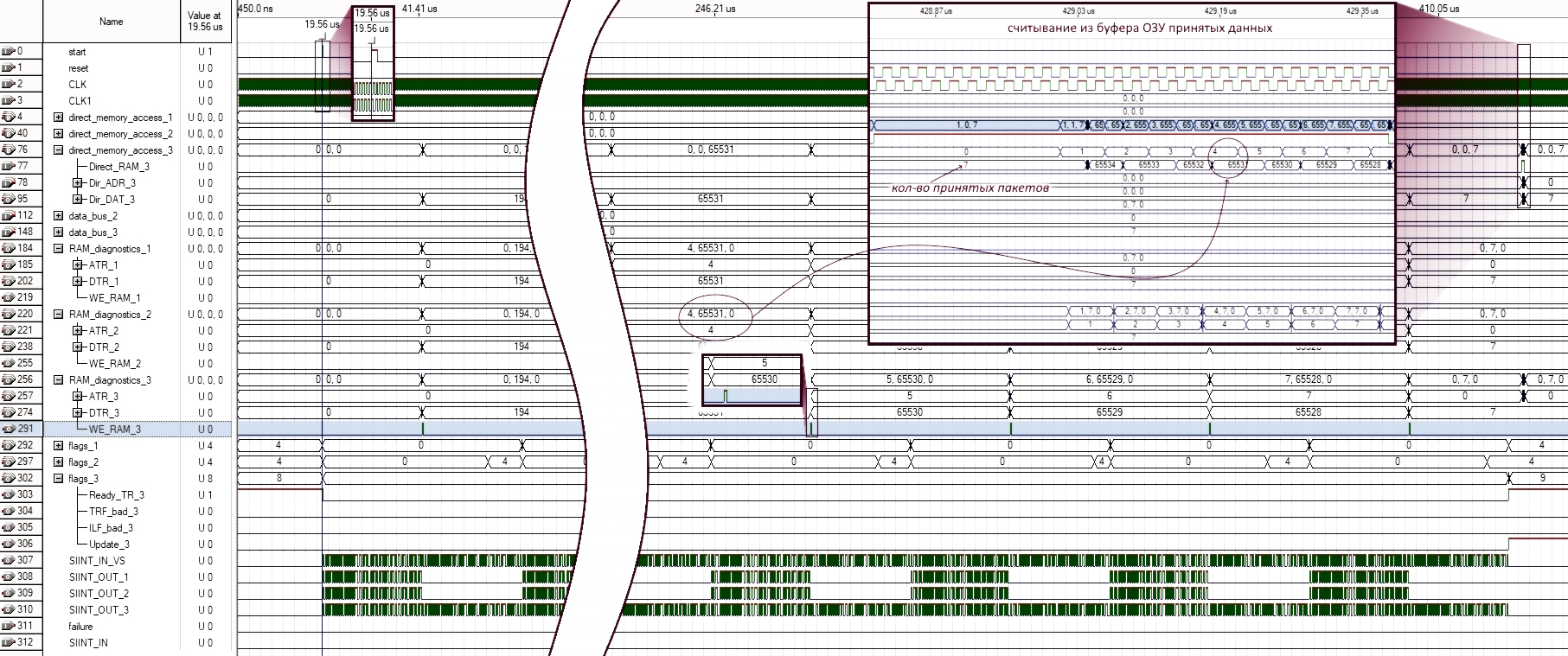

Контроллер сети первого уровня в рамках одного узла сети объединяет и координирует работу трех модулей: приемника (SINT_RS_ILN), передатчика(SINT_TR_ADJ), и буфера ОЗУ (IL_RAM). Контроллер сети так же выполняет функцию арбитра кольцевой шины и позволяет разрешать потенциальные коллизии, кроме того, он отвечает за механизм адаптации скорости передачи по кольцевой шине, осуществляет проверку целостности данных, и, при необходимости, осуществляет повторную отправку поврежденных пакетов. Схема модуля такого узла (Infinite Loop Network Unit) показана на рисунке 4.

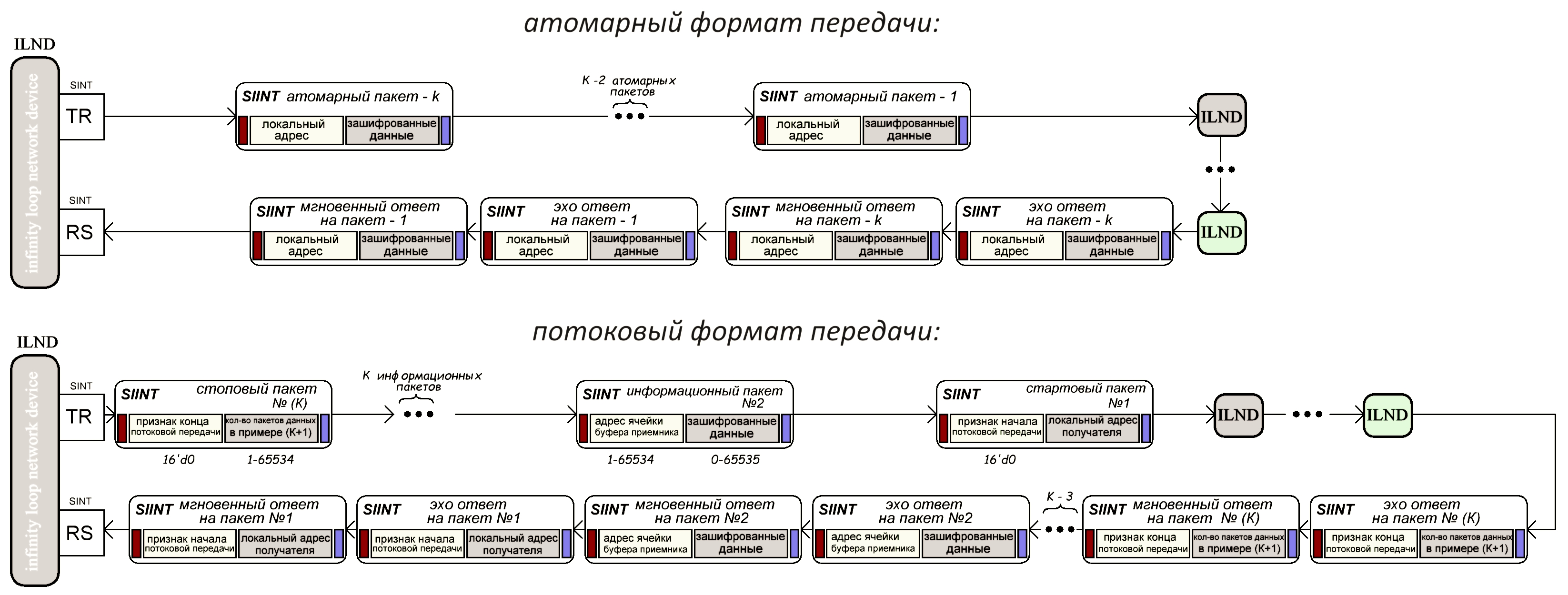

Контроллер сети первого уровня поддерживает 2 режима передачи: атомарный, когда отправка идет по одному пакету, и потоковая передача, когда адресат открывает прямой доступ к буферу памяти и записывает все пакеты до получения маркера остановки. На рисунке 5 условно показаны процессы передачи в этих двух режимах.

Для иллюстрации процесса передачи в атомарном режиме была собрана тестовая схема, показанная на рисунке 6.

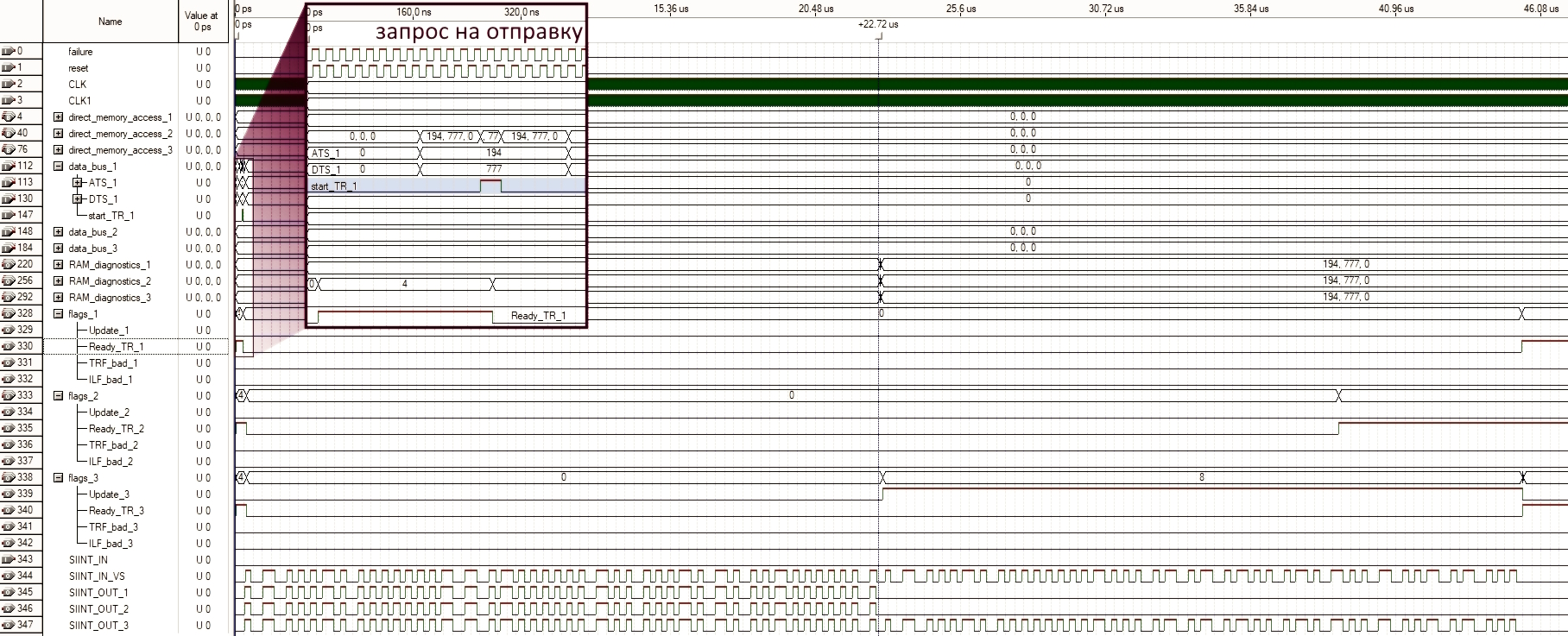

Временные диаграммы отправки одного атомарного пакета по адресу 194, узлом с адресом 192 показаны на рисунке 7. В режиме атомарной передачи заголовок пакет содержит явно указанный адрес получателя далее 16 бит закрытых данных и 16 бит CRC. Контроллер отправителя проверяет, есть ли флаг свободной шины, и, если он есть - начинает передачу в указанном формате. Все узлы сети слушают линию и каждый предыдущий узел сети ретранслирует пакет следующему, без внесения в него изменений, при этом усиливая сигнал. Отправитель пакета по закольцованной шине получает «мгновенный отклик» через задержку, связанную с распространением пакета и его многократной ретрансляцией (прием «мгновенного отклика» должен начаться до завершения отправки пакета). Если один из узлов сети получает пакет с его адресом и полученные данные прошли проверку CRC, то контроллер приемника отправляет эхо полученных данных дальше по кольцевой шине и одновременно дает сигнал внутренним модулям узла о приеме 16 бит из сети. Отправка ЭХО пакета осуществляется на той же скорости что и принятый пакет.

В случае, если пакет не нашел своего адресата, или если адресат есть, но не пройдена проверка CRC, ни один из узлов сети не сгенерирует «эхо» пакет. Контроллер отправителя увидев «мгновенный отклик», но не получив «эхо», сделает вывод, что кольцевая шина физически исправна, но адресат получил поврежденные данные или не успевает обрабатывать последовательный сигнал на данной частоте, поэтому частота будет снижена и осуществлена повторная отправка. Операция будет повторяться до указанной в качестве параметра минимальной скорости передачи данных по шине. Если «эхо» ответа так и не поступит, то можно сделать вывод, что узла сети с таким адресом не существует, контроллер выставляет флаг о неудачной отправке сообщения и прекратит попытки. Если не получен «мгновенный отклик», контроллер выставляет флаг о физическом нарушении кольцевой шины. Перед отправкой сообщения контроллер проверяет свободна ли шина, флаг о доступности шины выставляется автоматически после прекращения детектирования сигнала на кольцевой шине и обязательной задержки, которая необходима для формирования потенциального «эхо» ответа от стороннего узла. После обязательной задержки выдерживается рандомная пауза, позволяющая кому-то из конкурирующих узлов занять шину первым. Такой же механизм выдержки паузы контроллер осуществляет при повторной отправке пакетов в случае отсутствия эхо, так как пакет мог быть поврежден из-за коллизии в сети, которая при проверке свободной шины маловероятна, но все же может произойти. В результате одному из конкурирующих отправителей повезет больше, он займет шину первым и сумеет доставить пакет, остальные же выставят флаг о коллизии для принятия решения на более высоком уровне.

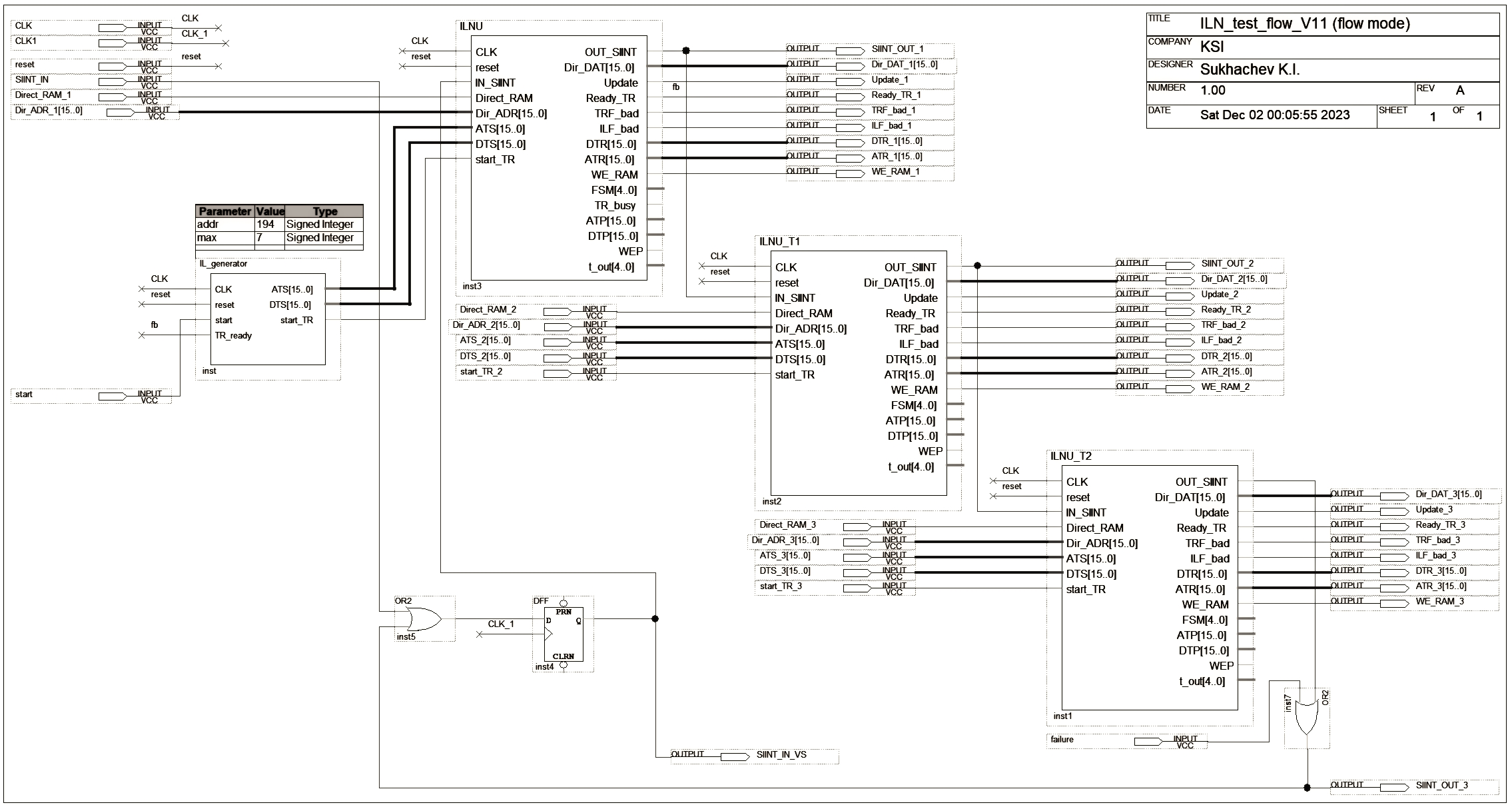

Для визуализации потоковой передачи была применена тестовая схема соединения модулей, показанная на рисунке 8.

Для активации режима потоковой передачи в открытом поле адреса контроллер отправителя должен отправить все «нули», а в поле закрытых данных указать адрес приемника (рисунок 9).

Все узлы сети получат пакет с нулевыми данными в открытой области и проверят поле закрытых данных на совпадения со своим адресом, если совпадения нет, то узел переходит в режим ретранслятора и будет прослушивать только открытую область пакетов в ожидании «всех нулей». Это будет свидетельствовать об окончании потоковой передачи. Узел, находящийся в режиме ретранслятора при сторонней потоковой передачи, удерживает флаг свободной шины в нуле, что запрещает ему начинать собственную передачу и как-то вмешиваться в поток. Вопрос, связанный с возможными проблемами на стороне отправителя при потоковой передаче, например зависание ЦП узла и невозможность сгенерировать завершающий пакет, решается на более высоком уровне сети, но суть решения состоит в том, что кто-то из узлов при выполнении ряда настраиваемых условий разрывает кольцевую шину на себе, и после необходимой паузы сам генерирует стоповый пакет потоковой передачи.

При штатной работе кольцевой шины во время потоковой передачи, узел адресат, получив пакет с нулевой открытой областью, пытается расшифровать закрытую и сверить результат со своим адресом. При подтверждении адреса узел открывает доступ приемника к буферу памяти. Следующий полученный пакет будет интерпретироваться иначе: открытая область будет содержать уже непосредственно адрес ячейки буфера памяти узла приемника, а закрытая область — это данные, которые будут записаны в указанную ячейку. При этом контроллер на каждый пакет также формирует отклик в формате «эхо» после проверки CRC, поэтому в случае ошибок контроллер отправителя будет повторно высылать «проблемный» пакет, снижая скорость передачи, пока, в итоге не запишет корректные данные в нужную ячейку буфера узла приемника. Для завершения потоковой передачи контроллер узла отправителя должен снова выслать нули в открытой области пакета, что отправлять в закрытой области для остановки потока значения не имеет. Однако узел, принимавший поток, детектировав нулевой адрес все-таки запишет в нулевую ячейку буфера последние полученные в пакете данные, и только потом выйдет из режима потокового приема, выставив соответствующий флаг об обновлении содержимого буфера. При этом более высокий по иерархии модуль может получить прямой доступ к буферу и считать его содержимое. Для исключения необходимости очищать буфер и считывать его целиком при завершении потокового приема, передатчику в последнем пакете с «нулевой» открытой областью крайне рекомендуется в закрытой – передавать количество переданных пакетов. Таким образом, более высокий уровень узла приемника, по завершению приема, считав содержимое нулевой ячейки буфера памяти сразу будет знать глубину актуальных данных. Также рекомендуется вести передачу по порядку с 1ого адреса по N. Максимальная глубина буфера 65535 слов по 16 бит. Важно, что завершающий пакет так же проходит проверку CRC и получение подтверждается «эхом», поэтому передатчик всегда будет знать, что все данные из потока корректно переданы и записаны, а приемник знает сколько данных считывать из буфера.

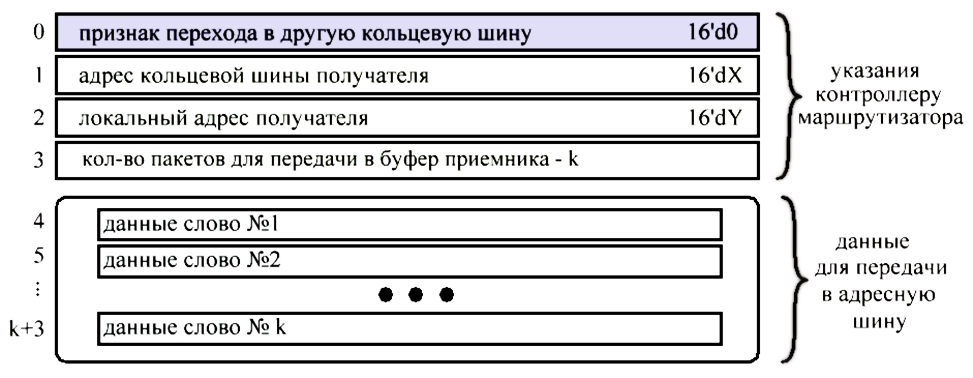

Взаимодействие между кольцевыми шинами осуществляется через специальные узлы – маршрутизаторы. Передать данные от узла одной кольцевой шины узлу другой - смежной шины можно только через потоковую передачу. Для этого на маршрутизатор объединяющий смежные шины необходимо передать пакет, формирующий в буфере приемника потоковой передачи структуру данных, показанную на рисунке 10.

Отличительным признаком является содержимое нулевой ячейки буфера. При потоковой передаче внутри одной кольцевой шины в нулевую ячейку буфера приемника передающий узел записывает количество переданных (подлежащих считыванию) слов. Если нулевая ячейка будет пустой, то контроллер кольцевой шины не будет взаимодействовать с содержимым буфера. Однако для маршрутизатора пустая нулевая ячейка будет признаком запроса передачи содержимого буфера в смежную шину.

Маршрутизатор сети при обнаружении признака перехода в другую кольцевую шину, считывает еще три ячейки буфера 1-3, в которых содержатся указания контроллеру (см рис. 9). После чего маршрутизатор проверяет свободна ли адресуемая кольцевая шина (адрес из 1-ой ячейки) и формирует запрос потоковой передачи узлу с адресом, считанным из 2-ой ячейки буфера. После чего происходит потоковая передача данных из буфера начиная с 5-ой ячейки. Количество переданных слов задается данными из указаний контроллеру (3-я ячейка). После передачи всех данных, формируется завещающее слово – записывающее в буфер адресата содержимое 4-ой ячейки буфера маршрутизатора. 4-я ячейка записывается в нулевую ячейку буфера адресата, для возможности формирования передачи через каскад кольцевых шин. Для возможности обратного взаимодействия в данные для передачи желательно добавлять всю историю маршрутизации, что позволит при необходимости сформировать ответный пакет.

Важной особенностью кольцевой шины является то, что в сеть могут быть встроены устройства способные работать на разной скорости. Если узлу сети приходит сигнал на высокой частоте и сам узел в принципе не в состоянии сигнал обработать, то функции ретранслятора он все равно выполняет лишь внося регламентированную задержку распространения без нарушения формы. Таким образом, в шине могут быть и быстрые и медленные устройства и общение может происходить на любых доступных хотя бы двум узлам сети скоростям.

Когда в кольцевой шине есть быстрые и медленные узлы, возможны следующие варианты:

· Обмен между двумя быстрыми - остальные узлы не понимают посылку и даже не в состоянии декодировать адрес, но функции ретранслятора выполняют.

· Быстрое устройство передает посылку медленному - что возможно на предварительно сниженной скорости, либо при повторных автоматических попытках, происходящих с понижением скорости.

· Медленное устройство передает данные быстрому - передача проходит штатно, так как быстрое легко подстроится под частоту медленного по стартовому биту.

· Общаются два медленных узла - все остальные устройства работают штатно, декодируя адрес и ретранслируя мгновенные ответы дальше по кольцевой шине.

Для разных семейств ПЛИС

были проведены тестовые размещения узла сети и временное моделирование работы.

Результаты тестов представлены в таблице №1 (данные могут незначительно

отличаться, т.к. описание узла постепенно улучшается).

Таблица №1 – параметры узла IL_net развернутого в FPGA INTEL

Параметр |

EPF10K100 EBC356-3 |

EP2C8F 256C8 |

EP3C120F 780C8 |

EP3C16F 256C6 |

EP3SL340 F1517C2 |

Занимаемый объем |

1091 (22%) |

899 (11%) |

901 (<1%) |

897 (6%) |

937 (<1%) |

Максимальная частота тактирования |

25,7МГц |

73,3МГц |

165,7МГц |

196,9МГц |

328,1МГц |

Максимальная скорость передачи полезных данных |

1,55Мбит/с |

4,42Мбит/с |

8,97Мбит/с |

11,89Мбит/с |

19,82Мбит/с |

Задержка ретрансляции одного узла |

10,3нс |

7,5нс |

10,0нс |

5,7нс |

10,4нс |

Максимальное время ожидания мгновенного ответа, при максимальной скорости передачи |

14902нс |

5232нс |

2579нс |

1945нс |

1167нс |

Максимальное кол-во узлов кольцевой шины при работе на максимальной скорости передачи |

1446 |

697 |

257 |

341 |

112 |

Ссылка на архив с файлами проекта: https://disk.yandex.ru/d/D7Qyv2ISgUc83g

Avsmirn0ov

Ух каких динозавров вы нашли для синтеза, флекс и второй циклон это из той эпохи, когда такой интерфейс мог успешно дома заменить LAN, при наличии карточки переходника с 10base-t на это. Внешний phy прикрутить, чтобы эквалайзингом занимался, и можно ещё более серьезные скорости получить :)

А вообще статьи крутые, почти методичка для начинающих плисоводов по работе с сетью

Sukhachev_KIR Автор

да, динозавры те еще, но, скажу так... с намеком... что эти модели выбраны не просто так и иногда на них приходится работать (((

JerryI

Cyclone II довольно доступный камень. Для обучения самое то и задачки неплохо решает

yatanai

Зачем мучать динозавров? Есть тот же 4 циклон в котором и логики по больше и интерфейсы по быстрее и стоит оно относительно не дорого. Ну может тебе всё ещё нужна 5В логика, но не вижу больше никаких поводов совсем старые циклоны брать.

Sukhachev_KIR Автор

у динозавров есть полные аналоги)

JerryI

Ну bga сложно паять. В Quartus циклон I проще всего настраивается в принципе. Я бы дальше пошел и даже начинал изучение с Max II. Плату Марсоход скажем, в самом начале всей этой логики нафиг не нужно, на максах можно хоть фоторамку намутить уже, те ресурсов там с головой.

В целом про динозавров, это как с Arduino, там меги 168ые - по сути динозавры, но из все равно хватает для большинства нужд)

PS: абсолютно некорректное сравнение с 5В логикой, все циклоны идут из одной семьи и качественных различий в них мало. В основном количественные + пару шин дополнительных

Sukhachev_KIR Автор

я если честно циклон 3 люблю - да, кушает побольше потомков, но он такой суровый и довольно быстрый камень, вообще без излишеств, а главное есть корпус в 240 ног без BGA (можно в 2х слоях легко развестись) и пока его еще можно купить... я ими затарился впрок. Из плюсов, как нестранно это слышать, довольно дубовый техпроцесс, что иногда бывает важно)

yatanai

А разве всё ещё используются где-то кольцевые сети? Мне вот вбили в голову что это крайне идиотская идея, максимум на какой-нибудь ограниченный короб 10х10х10см подойдёт, как CAN условный.

Sukhachev_KIR Автор

да, в больших скоростных сетях использовать кольца конечно не нужно! Конкретно эту концепцию я, прикола ради, использовал в своем умном доме... (да, умный дом на ПЛИС...). Ну и применял в закрытой системе побольше чем куб на 10 см, но тоже ограниченной (когда альтернатив этому не было)... А вообще, идея в том, как на "динозаврах" сделать что-то легкое, но при этом функциональное) при минимуме внешних элементов - только ПЛИС, феррит и провода...