Встречайте ZedRipper – 16-ядерного зверюгу, работающего на частоте 83 МГц на базе процессоров Z80 – настолько же портативного, насколько и непрактичного. Это моя самая свежая на сегодня попытка собрать компьютер ради прикола, причём удовлетворив сразу несколько желаний:

- Использовать, наконец, гигантский FPGA, который валялся у меня без дела.

- Поиграть в альтернативную историю создания компьютеров, подойдя к вопросу многозадачности с позиции железа.

- Собрать компьютер, на котором я мог бы писать забавные короткие программки по пути на работу в поезде.

- Собрать платформу, на которой можно было бы проводить относительно несложные эксперименты с компьютерной архитектурой.

Гламурные фоточки

Если у вас нет времени читать простыню текста о непрактичной компьютерной архитектуре…

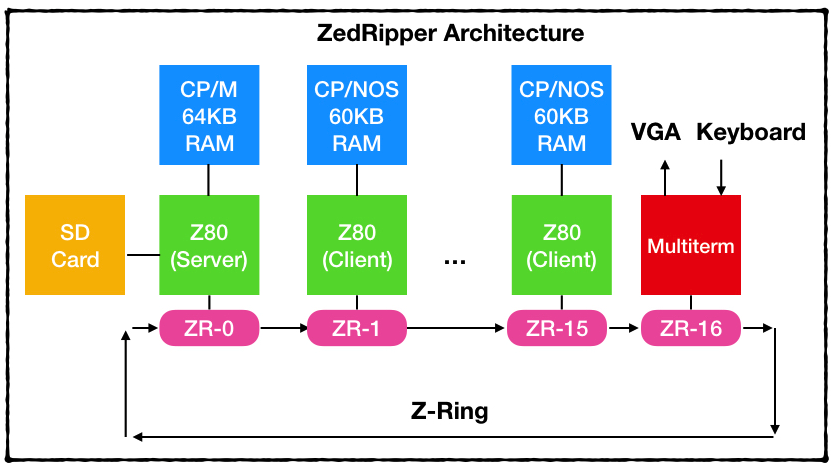

Так что это за зверюга?

ZedRipper – это результат попытки построить самый крутой компьютер с CP/M 2.2:

- 16 процессоров Z80, работающих на частоте 83,33 МГц.

- 64 Кб выделенной памяти под каждый Z80.

- ANSI-совместимый ускоритель терминала с 16 выходами.

- Все процессоры и устройства соединяются полностью синхронной однонаправленной кольцевой сетью, работающей на 83 МГц.

- Накопитель на 128 Мб на SD-карточке (16 х 8 Мб накопителей в CP/M).

- «Серверное» ядро, загружающееся в CP/M 2.2 и запускающее файловый сервер CP/NET (написанный на Turbo Pascal 3 на самом же компьютере!), обеспечивающий общий доступ к SD-карте.

- 15 «клиентских» ядер, запускающих CP/NOS из ROM. У каждого клиента есть доступ в общее хранилище, и каждый может запускать любые программы CP/M 2.2, не соперничая за ресурсы с другими ядрами.

Другая дорога

Это что, шахматы и Planetfall, отвлекающие меня от моего редактора Turbo Pascal?

После моих приключений с портированием игр на Kaypro у меня осталось удивительно тёплое впечатление от этой примитивной операционной системы 40-летней давности, и у меня появилась идея, которую я решил развить: что, если бы история свернула в другую сторону, и ПК пошли бы по пути развития с множеством CPU прямо сразу? Даже в 1980-х сами процессоры (а вскоре и RAM) были относительно недорогими, однако многозадачность ПК базировалась исключительно на разрезании отрезков времени, когда один большой ресурс (RAM или CPU) делили между соревнующимися программами. Железо не справлялось с этим (и было очень сложно заставить программы вести себя хорошо в таких ОС, как DOS), пока мы не перешли в эру 386-х и компьютеров с объёмом памяти более 4 Мб.

В процессе занятий моими историческими хобби с компьютерами я наткнулся на нечто очень для меня интересное: на ранних этапах развития ОС CP/M поддерживала «сетевую» версию под названием CP/NET. Её идея знакома большинству людей и сегодня – поставить в офисе одну-две «настоящие» машины с большими накопителями и принтерами, ресурсы которых делили бы между собой тонкие клиенты, терминалы с CPU и RAM. Каждый пользователь работал бы так, будто у него есть собственная машина под управлением CP/M с доступом к объёмным дискам и принтерам.

Как я упоминал, CPU и RAM (обычно у Z80 было 64 Кб DRAM) были не особенно дорогими, однако все внешние приблуды, необходимые для создания полезного компьютера (диски, принтеры, мониторы,..) добавляли итоговой стоимости. В то время добавление в компьютер нескольких CPU/RAM казалось несколько декадентским подходом для обеспечения одного пользователя несколькими CPU и RAM. Даже CP/M пошла по пути разделения отрезков времени для MP/M OS.

Я обнаружил, что ближе всех к этому подошла компания Exidy – в 1981 году они выпустили свою машину Multi-NET 80, позволявшая добавлять до 16 карточек, на каждой из которых был Z80 и RAM. Однако она была предназначена для работы до 16 отдельных пользователей, а не для работы одного пользователя, одновременно запускавшего 16 программ.

Так близко…

Перенесёмся на 40 лет вперёд – транзисторы реально подешевели. Мне по наследству после закрытия лаборатории досталось несколько чудовищных по размеру FPGA (Stratix IV 530GX), и я думал, что бы такого интересного сделать с одной из них. В какой-то момент я наткнулся на очень интересный проект Гранта Сёрла Multi-Comp, и собрать рабочую машину с CP/M и одним CPU оказалось довольно легко. Но мне нужно было больше. Я решил посмотреть, удастся ли мне создать многоядерную машину на CP/M с реальной многозадачностью – ничего хитроумного, просто метод грубой силы.

Настраиваем и запускаем софт

В этом проекте я в основном концентрировался на железе, и не написал ни одной строчки кода на ассемблере. CPU 0 грузится прямо с ROM, который я взял у Гранта, а остальные узлы грузятся с 4KB CP/NOS ROM, которые я взял у симулятора Atari.

Оба ROM ожидают соединения с последовательным терминалом по стандартному интерфейсу, а клиенты CP/NOS ожидают ещё одного последовательно порта, соединённого с сервером. На таких крупных FPGA легко проектировать собственную логику. Я разработал свою логику декодирования адресов, благодаря которой Z-Ring для каждого CPU появляется в схеме отображения адресов там, где надо.

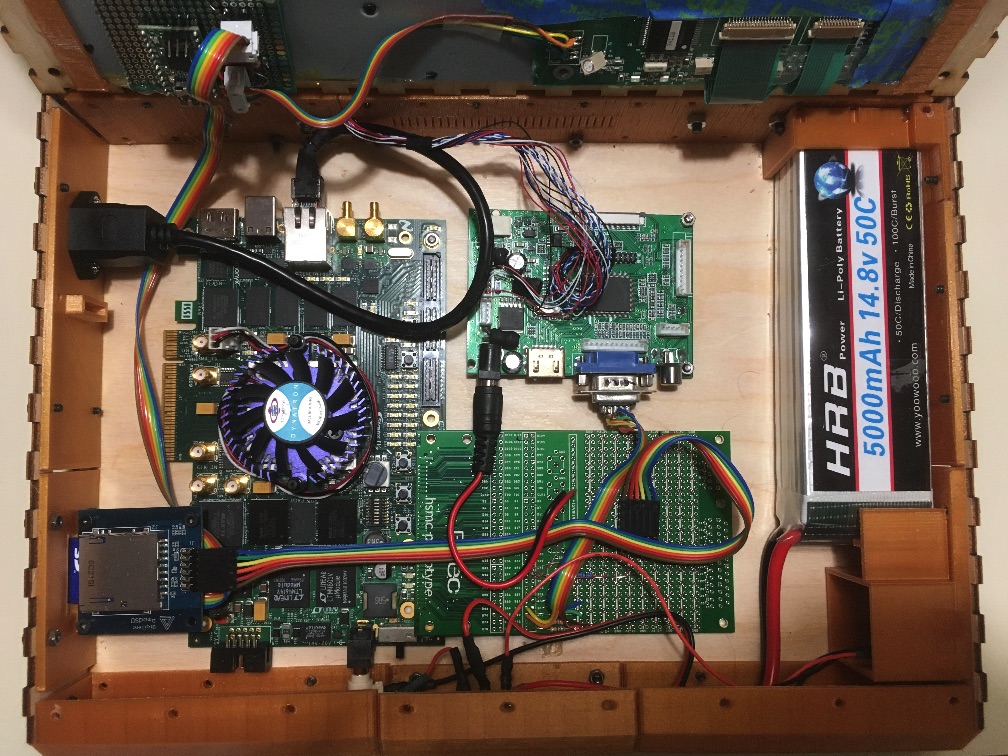

Внутренности

Сердце ZedRipper – одна из этих огромных Stratix IV 530GX FPGA. Карта HSMC используется для дисплея, получения данных от контроллера клавиатуры и соединения с SD-картой. Для загрузки прошивки используется ethernet, поэтому сбоку корпуса есть такой порт, вместе с адаптером SD-карты и слотом для внешнего последовательного порта (пока не используется).

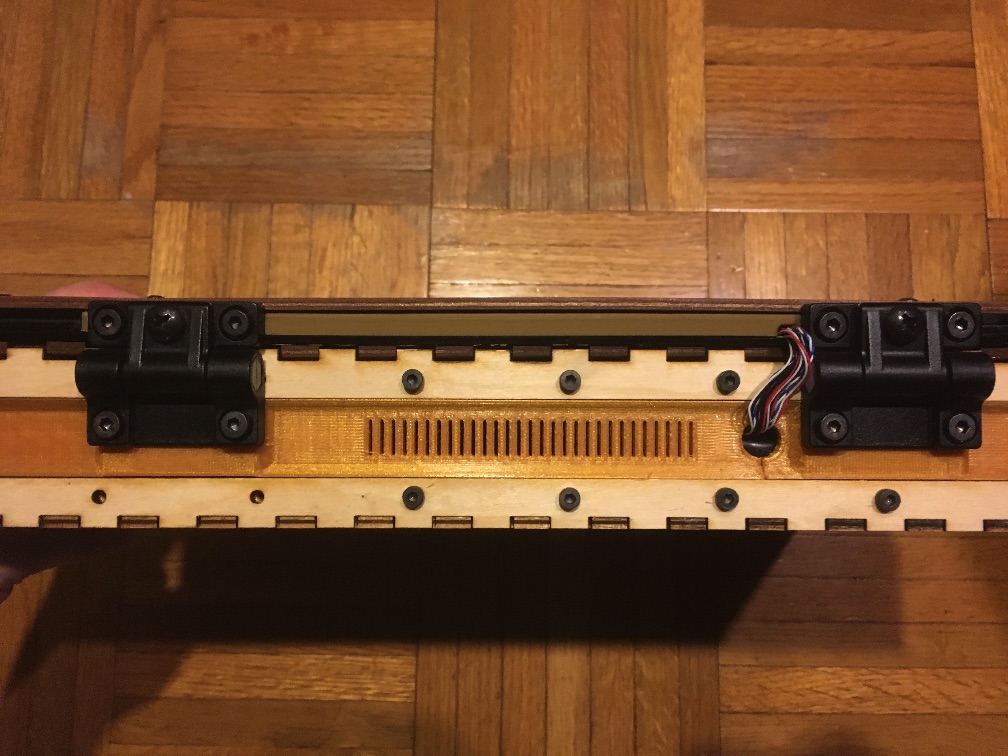

Клавиатура и контроллер

Клавиатура и отверстие на переднем плане, куда потом будет установлено позиционирующее устройство

У меня валялась компактная клавиатура PS/2 (от одного из моих старых проектов с ноутбуком), и я хотел подсоединить её к 2,5 В I/O моего FPGA. Я решил пойти по лёгкому пути, и добавить в связку микроконтроллер Teensy 2.0.

Контроллер на горячем клее снизу клавиатуры

Это позволило транслировать PS/2 в ASCII, а также легко разметить некоторые из дополнительных клавиш (F1-F12) на «волшебные» последовательности терминальных команд, для пущего удобства. Затем контроллер выдаёт Z80 байты по UART на 9600 бод (при помощи простого делителя напряжения, меняющего 5 В на 2,5 В для FPGA). Учитывая, что этот проект был собран из разного хлама, валявшегося у меня в мастерской, это было удобное решение, хорошо показавшее себя в работе.

Дисплей

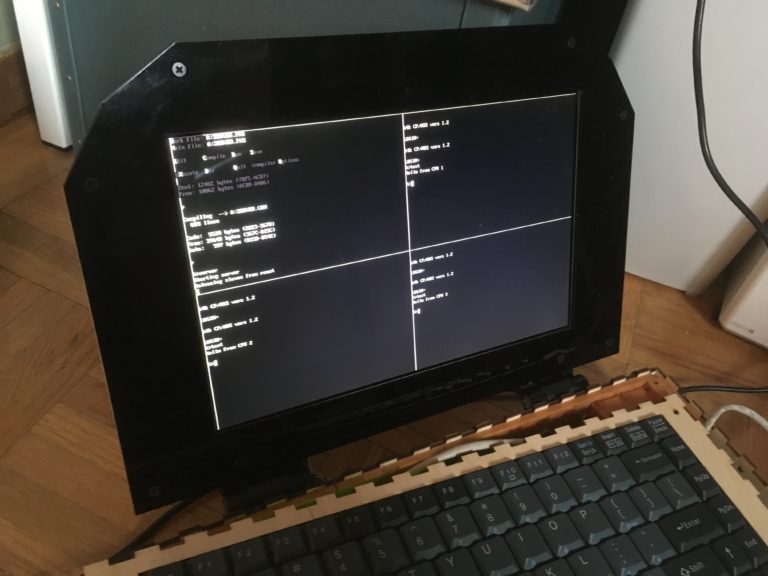

Экран загрузки, в левом верхнем углу работает сервер, а на отдельных ядрах работают три разные пользовательские программы

Характеристики дисплея: 1280?800 10.1?, и он понимает VGA. FPGA использует простую сеть из резисторов для выдачи до 64 цветов (R2G2B2). Дисплею требуется таймер 83,33 МГц (1280?800@60Hz), поэтому для простоты вся схема работает на этой частоте.

В проекте Гранта, Multicomp, был код VHDL для простого ANSI-совместимого терминала. Я переписал его логику на Verilog, а потом разработал видеоконтроллер с поддержкой 16 независимых терминалов, соединённых через один узел Z-Ring. Дисплей 1280?800 считается дисплеем размером 160х50 символов (со шрифтом 8х16), а каждый терминал работает как «спрайт» 80х25, который можно переместить в любое место экрана (со списком приоритетов, настраивающим последовательность отрисовки терминалов). Поскольку каждый терминал работает независимо от других, у него есть собственный конечный автомат, с 2 Кб RAM для символов и 2 Кб RAM «атрибутов» (для хранения информации о цветах). Каждый символ поддерживает 4-битный цвет фона и символа. Поскольку у всех терминалов символы должны иметь одинаковые отступы, а в «ячейке» 8х16 может содержаться только один символ, все терминалы могут пользоваться одним и тем же 2 Кб ROM, содержащим шрифт. В целом логика дисплея использует около 66 Кб блочной RAM.

В целом получается очень простой менеджер окон для моих терминалов CP/M, почти полностью работающий за счёт железа. Это одна из наиболее богатых для исследования областей – пока что переставлять терминалы местами умеет только серверный CPU, но у меня есть далеко идущие планы по добавке позиционирующего устройства типа мыши, которое позволит, пользуясь только средствами железа, перетаскивать окна и менять приоритет дисплеев.

Поскольку контроллер терминала – это просто один из узлов Z-Ring (а перенаправлять этот интерфейс для любого из Z80 очень просто), среди будущих планов – возможно, добавление «полноэкранного» терминала 160х50 (возможно, как «фон»), и реального дисплея 1280x800x64 цвета при помощи быстрой внешней SRAM на плате.

Z-Ring

Как соединить вместе кучку Z80? На моей работе я прочно усвоил одну вещь: разрабатывать сети сложно. Общими целями данной сети были:

- Простая реализация.

- Простой интерфейс.

- Произвольная расширяемость.

- Адекватное быстродействие.

Как я уже упоминал, мои Z80 ожидают подключения к последовательным портам, поэтому интерфейс сделать было довольно просто – его нужно было замаскировать под последовательный порт! По сути, Z-Ring – это синхронная однонаправленная кольцевая сеть, использующая «кредиты» для управления потоком. У каждого узла есть 1-байтовый входящий буфер для каждого из остальных узлов сети. После сброса у каждого узла есть 1 «кредит» для каждого из остальных узлов сети. Схема параметризирована, поэтому легко масштабируется до сотен узлов с добавлением совсем небольшого количества логики, однако на сегодня Z-Ring поддерживает до 32 узлов (поэтому каждому узлу нужен 32-байтный буфер).

Сама «шина» состоит из бита допустимости, ID «источника», ID «цели» и 1-байтной полезной нагрузки (19 бит). Думаю, её было бы довольно просто реализовать при помощи логики TTL (если бы человек провалился в 1981 год и не нашёл себе FPGA). У каждого «узла» есть 2 конвейера для триггеров шины – 0 и 1 этапа – и при вводе сообщения оно ждёт, пока не опустеет 0-й этап, а потом вливается в 1-й. Сообщения вводятся на узле-«источнике», и путешествуют по кольцу, пока не дойдут до цели, после чего они оказываются в соответствующем буфере и обновляют флаг «готовности данных». Когда принимающий узел считывает буфер, он заново вводит оригинальное сообщение, продолжающее путешествовать по кольцу, пока снова не дойдёт до источника, возвращая «кредит». Если отправить пакет по несуществующему адресу, кредит вернётся автоматически, пройдя полный круг.

Поскольку каждая остановка на кольце состоит из двух конвейерных этапов, а обратное давление отсутствует, у каждого сообщения уходит не более 2*(количество узлов) циклов на доставку. У текущей реализации 17 узлов (16 CPU + контроллер дисплея/клавиатуры), и она работает по таймеру 12 нс, поэтому на доставку сообщения и возврат кредита уходит порядка 400 нс. Контроллер дисплея может отправлять трафик со скоростью поступления, поэтому у каждого CPU есть 2-2,5 Мб/с пропускной способности к своему терминалу (шина пропускает достаточно, чтобы обеспечить все 16 CPU), что довольно много для терминалов.

В текущей конфигурации всё работает отлично, однако можно сделать несколько очевидных улучшений:

- Углубить получающие буферы, что позволит увеличить пропускную способность узлов – на FPGA есть много свободных блоков по 1 Кб RAM, что позволит поддерживать 32 узла по 32 кредита, поэтому каждый CPU в теории может насытить шину.

- Добавить поддержку адресного режима. Добавление 16-битных (и более) адресов позволит организовать прямой доступ к памяти (DMA) (а добавить DMA к каждому узлу будет просто). У FPGA есть огромное количество дополнительного железа (несколько мегабайт статической RAM и порядка гигабайта DDR3).

- Добавить управление потоком (и буферизацию) между узлами.

Но всё это может подождать до лучших времён.

Питание!

Отладочная плата с FPGA требует входного питания в 12-20 В, дисплею нужны 12 В, а клавиатуре и контроллеру нужны 5 В. Удобно, что на FPGA есть регуляторы на 3,3, 5 и 12 В, к которым довольно легко подключиться, поэтому FPGA получает питание напрямую от литий-полимерной аккумуляторной батареи на 5000 мА*ч с напряжением 14,4 В, и потом раздаёт питание всем остальным устройствам. Одна из сложностей заключалась в том, что мне не хотелось разбирать ноутбук каждый раз для зарядки, но у батареи был обычный разъём питания + / -, а также «балансировочный» разъём, подсоединяемый к каждой отдельной ячейке. Моё неидеальное решение состоит в том, что кнопка включения переключает соединение с батареей между питанием FPGA и зарядным разъёмом, находящимся в углублении, закрытом сдвижной крышкой. Не очень удобно, однако можно просто сдвинуть крышку, и вытащить оттуда коннекторы, чтобы подсоединить их к зарядке, не пользуясь шестигранными ключами.

Зарядка выглядит странновато

Я не тестировал батарею тщательно, но она держит не менее 3 часов (чего с лихвой хватает для покрытия моих поездок на поезде). Скорее всего, она продержится порядка 6 часов без какой бы то ни было оптимизации потребления. Она не поддерживает использование одновременно с зарядкой, однако от батарейки ноутбук работает достаточно долго для того, чтобы это не было проблемой.

Корпус

Корпус стандартной «хакерской» конструкции – комбинация из 3 мм фанеры лазерной резки и пластика, распечатанного на 3D-принтере. Я подпружинил экранные петли, поэтому в деле он ощущается как обыкновенный, пусть и несколько медленный, ноутбук. Мне хотелось придать ему вид 1980-х, поэтому верхние углы экрана немного напоминают Cray, а под запястья сделана подставка из искусственной кожи. Край резаной лазером фанеры очень неприятен для рук, поэтому такая подставка оказалась удивительно функциональной.

Скорость

Не пробовал ни одного бенчмарка специально для CP/M (предполагаю, что они бывают, но особенно не искал). Поскольку эта машина была сделана для написания программ на Turbo Pascal, я попробовал несколько микро-тестов на скорость. Получилось 15-35 К операций с плавающей запятой в секунду (с использованием 48-битного типа Real в TP), и порядка 1 млн целочисленных операций в секунду (с 16-битным типом Integer). Неплохо для 8-битного CPU и достаточно удобной среды для программирования.

Интересным проектом на будущее может быть разработка ускорителя для операций с плавающей запятой.

Утилизация FPGA

Вся логика, как я уже говорил, довольно лёгкая, и отнимает всего около 7% ресурсов чипа (хотя 40% от общей блочной RAM и 100% от M144k RAM).

- Combinational ALUTs 31,808 / 424,960 ( 7 % )

- Memory ALUTs 0 / 212,480 ( 0 % )

- Dedicated logic registers 10,231 / 424,960 ( 2 % )

- Logic utilization 10 %

- Total registers 10231

- Total block memory bits 9,005,056 / 21,233,664 ( 42 % )

- DSP block 18-bit elements 0 / 1,024 ( 0 % )

Планы на будущее

В моих ближайших планах (то есть, железо уже лежит в мастерской, просто надо найти время на пайку):

- Покрасить всё это. Ноутбук сделан из фанеры, и его очень хочется чем-то покрыть.

- Позиционирующее устройство типа джойстик. Соединить его с клавиатурным контроллером.

- Отслеживание батареи. ADC на контроллере клавиатуры позволит достаточно легко отслеживать батарею, чтобы мне было понятно, на каком уровне заряд.

- WiFi – у меня валяется ESP32 для запуска Zimodem! Вместе с телефоном в режиме точки доступа это должно позволить мне выходить в интернет в пути. Для CP/M есть хорошие терминальные приложения, однако было бы прикольно написать что-то типа IRC-клиента или простейшего веб-браузера. Также будет удобно использовать протокол передачи файлов Kermit на современный компьютер под управлением Linux.

- Последовательный порт, доступный снаружи, для соединения с другой машиной (для него уже распечатан разъём, его нужно только припаять).

- Светодиод, сообщающий текущий статус. Для него уже есть отверстие спереди – сейчас я планирую соединить его с сигналом доступа к SD-карте.

В более долгосрочной перспективе рассчитываю на разные железячные идеи, с которыми будет прикольно поэкспериментировать:

- Как сильно можно разогнать Z80? Первый шаг – отвязать скорость процессора от пиксельного таймера, однако также будет интересно попробовать применить современные компьютерные техники к Z80 (конвейеры, переименование регистров, предсказатель переходов, и т.п.).

- Может быть интересно добавить специальные ускорители для таких вещей, как операции с плавающей запятой. На чипе есть 1024 неиспользуемых DSP-блоков, и думаю, что никто ещё не пробовал построить ускоритель для 48-битного формата Real в TP.

- Использовать существующее железо! У меня остаётся куча неиспользованной памяти, а именно:

- 512 MB DDR3 SDRAM with a 64 bit data bus

- 128 MB DDR3 SDRAM with a 16 bit data bus

- Two 4 MB QDR II+ SRAMs with 18 bit data buses

- 64 MB flash

- 2 MB SSRAM

- Улучшить видео! Первый шаг – добавить поддержку «полноэкранного» терминала 160х50, и возможность масштабировать до обычного терминала 80х25 в 2 раза. С использованием внешней SSRAM будет просто добавить режим 1280?800@6-bit.

- Расширить возможности текущего терминала. Думаю, я смогу добавить совместимость с терминалом типа ADM-3A (и добавить поддержку графики), который используется в Kaypro/84, тогда у меня будет доступ к более широкому спектру ПО (и не придётся портировать DD9).

Итоги

Пока что машина работает всего несколько дней, однако могу сказать, что мне всё очень нравится. Экран приятный и чёткий, клавиатура большая и удобная, корпус громоздкий, но весит мало (и влезает в рюкзак). Ноутбук оказался даже на удивление эргономичным для работы в поезде.

Мне кажется, я на верном пути. Возможность открыть текстовый редактор в одном окне для заметок, отлаживая код на TP в другом, чрезвычайно удобна (или возможность делать заметки, играя в Zork!). Чувствуется, что такой подход к созданию недорогих многозадачных компьютеров на базе CP/M мог существовать.

Хочется построить такой же?

Пока что у меня нет лёгкого способа доставать файлы из машины, поэтому самая полезная часть ПО (файловый сервер CP/Net, написанный на Turbo Pascal), находится в ловушке. Оставайтесь с нами, и следите за новостями (или напишите мне емейл, если совсем не терпится). В какой-то момент я, наверное, присоединюсь к XXI веку и открою учётку на github. Увы, всё упирается в то самое «свободное время».

Комментарии (49)

staticmain

16.12.2019 10:46Зачем делать корпус из фанеры, если есть 3D принтер?

vesper-bot

16.12.2019 10:50+1Тридэ-принтер с такой большой станиной, чтобы отпечатать полноразмерный корпус ноутбука, как бы не дороже всего остального хлама в гараже автора. Кроме того, самоделкин не будет забивать гвозди микроскопом, особенно если у него есть в доступе хороший молоток.

Fox_exe

16.12.2019 12:53+1А кто мешает сделать модульную конструкцию (Хотя это и сложно) или банально разрезать-распечатать-склеить?

Я так корпус для монитора 15" (320мм) делал на принтере с базой в 200мм. Получилось вполне годно.

Goron_Dekar

16.12.2019 14:56+1ЧПУ лазер для фанеры не менее приятная штука, и скорость производства заметно выше.

vesper-bot

16.12.2019 14:56Возможно, нехватка специфических знаний по проектированию такой структуры для трехмерной печати, вроде необходимого количества ребер жесткости, а также нехватка времени на их получение, проектирование, распечатку, облом и повторение процесса. А также потенциальное владение этой спецификой под фанерный корпус.

Elmot

18.12.2019 10:38Нет. Просто разумный подход и незацикленность на 3д печати. Фанера — это вообще классный материал. А уж если делать закос под «старину» — то и вообще идеальный.

Elmot

18.12.2019 10:32Фанера — это даже более прикольно, чем 3D печать. Как минимум, печать такого размера — это море времени и куча склеек, огромная постобработка. Фанерные же части будут нарезаны за несколько минут.

questor

16.12.2019 11:26Офигенно тёплое, ламповое чудо. Долго разглядывал фоточки с восхищением.

PS У меня в детстве был синклер в коробочке примерно такого же размера, только без монитора разумеется, без rj-45 и т.п.

NickViz

16.12.2019 11:29+1эм. а процессоры он тоже в стратиксе реализовал? я как-то ждал линейку DIP40 корпусов…

valis

16.12.2019 11:46Ага, было бы совсем лампово. А так FPGA за 4+ килобаксов. Парень бесспорно крут, но прикольно бы увидеть кластер настоящих Z80

EddyEm

16.12.2019 19:49На недорогих STM32 очень даже хорошо выходит эмулировать Z80, так что…

namikiri

18.12.2019 10:36Тоже не то!

EddyEm

18.12.2019 10:41-3Ну, лично я считаю, что Z80 — древнее старье, которое вообще никакой ценности не представляет. Ладно — эмуляторы на микроконтроллерах: можно поднатаскать свой скилл в электронике и программировании. Но реально пытаться что-то на этой дряни сделать…

Mirn

16.12.2019 11:49Да, ПЛИС (FPGA) это такие штуки в которых можно аппаратно реализовать любые процы.

Это массивы готовой аппаратной логики которую можно настроить, инициализировать первичное состояние и скоммутировать программным способом. А всё остальное это уже работа аппаратуры, логических элементов и тд, грубо говоря внутри пара миллионов DIP40 в мелкой логике.

Например, на нескольких тыщах Combinational ALUT можно реализовать ARM Cortex M1 с быстродействием 300-400 mega MACS. А внутри этой штуки 400к таких, т.е. теоретически сотня ARMов влезет (если забыть про интерфейсы, память и логику чипсетов).

Есть интересное продолжение идеи мультипроцессорности в плис: лет 10 назад интузиасты реалзовали аппаратное кодирование H264 на несколько тысячах процессорах внутри FPGA. Причём каждый такой проц был адаптирован под свой этап конвеера алгоритма H264. Быстродействие вышло просто чудовищным по тем временам.

sim2q

17.12.2019 02:12класс!

но да, тоже ожидал стопку корпусов…

ps с последними зеленоградскими моделями где на плате уже шла ПЛМ, от этого уже «что-то было не так»

eugenk

16.12.2019 12:50Мегакруто! Респект и уважуха! А я вот в свободное от работы время, на граздо более скромной FPGA пытаюсь возродить PK-11, который Союз-Неон. В своё время машинка произвела на меня просто неизгладимое впечатление. Круче современных с ним PC-AT 286.

Sdima1357

16.12.2019 18:541806ВМ2. Разработан в 1985 — ...(ангстрем продает до сих пор) — 64Кб адресуемой памяти(1-4MB tr. pages), 5-8MHz, система команд PDP11.

Его современник это Intel 386(1985-2007), а не 286(1982-1991)

eugenk

17.12.2019 21:58Там не ВМ2 более всего интересен, а видеокнтроллер. Это ошизеть, АППАРАТНАЯ (!!!) поддержка окон в 1988 году!!! Думаю не будь тогда Союз при смерти, история персональных компьютеров могла бы сложиться совсем иначе… Надеюсь скоро опубликовать здесь на хабре статью. Когда хотя бы добьюсь на верилоге генерации стартового экрана. Увы, сейчас работаю за деньги, причем очень несабые, и выкладываться приходится на все знаменитые 146%. Поэтому для хобби-проектов времени почти нет. Ладно, надеюсь дальше будет чуть свободнее…

bat654321

18.12.2019 12:12+2История ПК сложилась бы иначе, если бы партноменклатура не требовала копировать западные компьютеры.

eugenk

18.12.2019 12:42Тут увы ничего не остаётся, кроме как безоговорочно согласиться. Вообще парадокс. Потрясающе талантливый народ. Особенно во всяких инженерных и вообще научно-технических вещах. И совершенно никчёмные правители. С царских времён т по сей день. Очень надеюсь, что сейчас это изменится.

bat654321

18.12.2019 16:30-1В этом нет никакого парадокса, а есть лишь тонкий расчёт. Когда усилиями Сталина провалился план по созданию мировой коммунны, то приключилась Вторая мировая война — очередная попытка глобализации евразийского континента. Однако, даже несмотря на предательство части армейских командиров, СССР не только не отдал свои ресурсы, но и "освободил" Европу.

Поняв, что снаружи СССР не победить, было принято решение развалить его изнутри. Убили Сталина, перекорёжили экономику, исказили идеологию, создали дефицит, и… наивный народ радостно сам всё просрал в обмен на жвачку и джинсы.

eugenk

18.12.2019 05:20Думается там всё было сильно сложнее. И не так прямолинейно. Мне почти 60. И СССР я наблюдал во вполне сознательном возрасте, успев там и в армии отслужить и поработать, и даже пожить на крайних северах. Так что знаю о чём говорю. К сожалению хабр вне политики. Поэтому если хотите, давайте встретимся на какой-нибудь другой площадке, где такие разговоры более уместны.

trolley813

16.12.2019 13:02+2Утилизация FPGA

Из Большого толкового словаря:

УТИЛИЗАЦИЯ, -и; ж. [от лат. utilis — полезный] Использование чего-л. ненужного (отходов производства, быта и т.п.) или не приносящего непосредственной пользы человеку в целях получения (после переработки) какой-л. продукции, энергии и т.п.

Может, не стоит-таки утилизировать FPGA? Это ведь вещь очень полезная...

vesper-bot

16.12.2019 15:00Это второе значение слова, первое — использование по назначению, т.е. == использование. Однако так как попугаеметры все англоязычные, количество использованных элементов в FPGA исторически (сообразно с процентом использования времени ЦП) переводится как "процент утилизации". /КО

WinLin2

16.12.2019 13:0416 процессоров Z80, работающих на частоте 83,33 МГц.

ru.wikipedia.org/wiki/Zilog_Z80

Тактовая частота (МГц): 2,5 — 8 для основной версии; КМОП-версии от 1 (версия Z80L Z8300-1) до 20

VBKesha

16.12.2019 14:10Это не реальные микросхемы с Z80 это их реализация в FPGA там частота может быть выше.

mokhin-denis

16.12.2019 14:17А я в детстве на спекки в симсити и твин турбо гонял… А тут вон че! Ну класс же! Круто!

algotrader2013

17.12.2019 21:58Возможность открыть текстовый редактор в одном окне для заметок, отлаживая код на TP в другом, чрезвычайно удобна (или возможность делать заметки, играя в Zork!).

А для многопоточных программ сойдет? СУБД с межпоточными блокировками таблиц, например. Или игра, где за ИИ каждого врага отдельное ядро отвечает?

GeBoN

18.12.2019 11:05+1Видите, Балаганов, что можно сделать из простой швейной машинки Зингера?

Круто!!!

С батарейкой непонятны траблы — можно на али заказать платы балансировки-зарядки за бакс-полтора.

VitalyNasennik

18.12.2019 12:20Настоящий маньяк! Эту бы энергию да в мирное русло!

PS В эту монструозную Stratix IV GX 530 можно запихать штук 8 PowerPC ядер, на которые поставить линукс…

algotrader2013

18.12.2019 21:36А по Вашему опыту, что самое крутое можно на таком девайсе запилить? Из того, что знаю я, для HFT торговли их любят, чтобы в обход шины работать (через встроенный ethernet пакет поймал, «на месте» решение принял, через тот же ethernet пакет с решением выплюнул).

И что у многих руки чешутся для работы с большим объемом интернет траффика задействовать. Но вот до реализации не особо доходит.

На Мосбирже N лет назад думали для раздачи котировок заюзать, посмотрели на задержки своего решения, на FPGA решения, и решили, что «и так сойдет».

В Cloudflare пришли к выводу, что тема как-бы хорошая, но вот зоопарк из железа обойдется дороже, и в итоге, как менее радикальное решение, внедрили ARM процы, которые тоже им выгоднее x86, но повместимее.

Mirn

18.12.2019 04:19+1Я конкретно для HFT ничего не разрабатывал, только для самого езернета, но могу предположить что причины в следующем:

1. FPGA разработчиков гораздо меньше чем C/C++, а утилиты и готовые корки стоят ну очень дорого, а порой просто недоступны в странах СНГ из за санкций (например старшие и новые стратиксы, скоростные ацп и тд)

2. задержки и время реакции часто упираются в вещи не зависящие от FPGA — например на тайминги езернета, размер блока принятия решений (например надо накопить три блока), размера FIFO очереди и тд, всё это приводит к тому что старший АРМ и прога на baremetal с ручным управлением DMA даст сопоставимые задержки, разница между FPGA порой всего в полтора — два раза.

3. Время отладки и проверки алгоритмов — верификация и симуляция на FPGA это очень больная и трудо- и время-затратная тема, это дни а порой недели, даже я научившись симулировать миллиард умножений с накоплениями в секунду на обычном PC сталкиваюсь с тем чтобы проверить все кейсы нужна неделя. И то мой вариант скорее проверка RTL-мат модели на си с точностью только до такта, а часто нужно точнее.

4. Физика будь она неладна: редко когда в дизайне есть фпга дерево частот порождённых делением на целое одной максимальной частоты, почти всегда есть несколько асинхронных независимых частот. А это метастабильность, т.е. полное отсутствие гарантий 100% надёжности, что ОЧЕНЬ не любят финансисты, и они не хотят чтоб железяка встала колом только потому что например в выражении типа (C and A) or (B and (not A)), переменная А стала одновременно равна, и 1, и 0.

4В. Плюсом ко всему готовые блоки и IP корки и прочие либы от производителя которые нередко плохого качества, закрыты, нередко исходники даже интефейсного адаптера зашифрованы и в принципе никому ни за какие деньги не даются. А в workaround ерраты простая фраза «понять и простить» самая частая.

5. Время компиляции… часы… порой дни, распараллеливанию на разные машины компиляция и фиттинг не поддаётся в принципе. Жрёт десятки и сотни гигабайт (даже на дишманский и устаревший CycloneV архитектуры чуть ли не 10 летней давности жрёт до 40 гигов озу в среднем а не в пике). А в HFT наверняка оперативность тоже важна.

6. Devops, кодестайл и организация труда и «быдлокод», всё это очень тяжоло и не прощает мельчайших ошибок, сделал в одном месте неосторожный цикл вместо присваивания шины целиком, или y = x << z; и всё, время компиляции только этого места добавит десятки, сотни, а порой тыщи минут. Ок в своей компании, в своей кодовой базе, предположим, всё идеально, но внешние либы от производителя… хех см пункт 4В.

Если есть разрабы FPGA для HFT то просьба ставить минус в карму не молча, а научить меня неразумного в каких допущениях я ошибся, заранее спасибо.

eugenk

18.12.2019 07:07Поставил плюс вместо минуса. Всё очень вверно, хотя возможно и несколько преувеличено. Например у меня ноутбук 10-летней давности с 8 гигами оперативки прекрасно справляется с проектами объемом в десяток тысяч строк на верилоге. Только сейчас дозреваю до покупки нового. Самый главный это конечно пункт 1. И самое паршивое, что далеко не каждого можно этому обучить. Разраб FPGA-шник должен мыслить параллельными процессами, к чему человеческий мозг не очень хорошо приспособлен. У меня есть друг. На 12 лет моложе меня. Голова золотая. Я у него в своё время (конец 90-х) взлому учился. Однако FPGA так и не осилил. Даже под моим чутким руководством. Ну не пошло, и хоть тут тресни! Вот как-то так…

avf1906

18.12.2019 17:05+1да, действительно мышление ломается довольно жестко. Не специалист, но в свое время (лет 15 назад) делал специфический расширитель портов I2С на MAX (AHDL), и переход между си и ahdl ломал довольно сильно. В более сложном проекте (ЦОС на циклоне + VHDL) там еще печальнее, реально чувствовалось как мозги шевелятся переключаясь между параллельной и последовательной парадигмами разработки.

eugenk

19.12.2019 11:32Ага. Очень знакомо. Хотя дело привычки. У меня сейчас из всего домашнего зоопарка самая любимая зверюшка это iCE40-HX8K Breakout Board. Даже вторую такую хочу купить. Дико удобно!!! Там двухканальная FT232. По одному каналу шьётся FPGA. А по другому с ней можно общаться как с виртуальным COM-портом. По одному и тому же usb-кабелю! Плюс дикое количество ног, выведенных на разъёмы. Сейчас абсолютно все свои железные проекты делаю с участием этой платы. Причем пишу на смеси верилога и java. Java вообще мой самый любимый язык. И для неё есть библиотека для работы с COM-портом. Короче получается что-то типа программируемого логического анализатора с интерфейсом на яве. Когда только осваивал эту технологию тоже было несколько стрёмно переключаться с верилога на яву и обратно. Но сейчас привык. Главное же тут как я уже говорил выше. Прграммированию можно обучить любого психически полнценного человека, ибо это не выходит за рамки обыденного здравого смысла. Просто описание последовательности действий. А вот разработка для FPGA боюсь увы, удел уродов(ну хорошо, скажем мутантов), которых думается не более 1% популяции. Там способ мышления совершенно иной. Причем такой, к которому человеческий мозг не слишком хорошо приспособлен. Вот так примерно…

Mirn

19.12.2019 11:47схемотехники с опытом программирования и с опытом реализации на мелкой логики чего нибудь типа контроллера ISA шины вполне обучаемые, я обучал месяца за 1-2, нормально всё выходило.

eugenk

19.12.2019 13:09Вопрос какие объёмы кода… После тысячи строк на верилоге восприятие сильно меняется… Тот же мой друг о котором я писал выше. COM-порт (а я считаю что с этого должно начинаться вообще любое обучение, ибо COM-порт это глаза и руки в проекте) он написал с моей минимальной помощью. Причем не просто написал. Я ему ещё устроил(разумеется не предупреждая !) всякие гадости типа шума на линии, которые он успешно преодолел. Но когда речь зашла о моей выдиралке dvd-дисков, он сказал мол я просто не понимаю как всё это у тебя работает. Хотя говорили в реале, на кухне. При вклченном компе с кодом. И при осцилографе с времянкой. Ну НЕ ДАНО человеку!!! Поэтому если пишете для FPGA, помните, что Вы урод. Или мутант. Или любимец Бога. Это не всем даётся. Такие дела…

Mirn

19.12.2019 18:38я такое называю просто и без пафоса: «ну не твоё это, бывает, давай попробуем что нибудь другое»

VitalyNasennik

18.12.2019 05:21Ну у нас у всех очень разные представления о том, что такое «самое крутое»… Например, «самое крутое» для меня — это в крошечную мегу8 запихать вот это www.youtube.com/watch?v=sNCqrylNY-0

У меня фантазии не хватает, чем бы этот монструозный стратикс загрузить.

eugenk

18.12.2019 06:22У меня фантазии не хватает, чем бы этот монструозный стратикс загрузить.

Ага… Знакомо :)

Меня такое чувство впервые посетило когда делал проект для корейской LG Electronics. Причем там был не монстр какой-то, а скромная de0 nano c EP4CE22F17C6N на борту. 22320 ячеек всего-то навсего. Считать требовалось довольно сложные математические выражения. Причем с точностью не хуже одной тысячной процента по сравнению с тем, что даёт компьютер с плавающей точкой. Даже тут на хабре по итогам опубликовался habr.com/ru/post/469327. Так вот. Когда проект был загружен в FPGA (а нужны были пять (!!!) таких каналов !), выяснилось, что кристалл используется всего-то на 45%. Это меня тогда сильно удивило… Тем более что перед этим был проект на ICE40LP4K, где биться приходилось за каждую ячейку и за каждый такт. А вообще интересная жизнь у программиста-железячника. Не променяю её ни на какую другую :)

VitalyNasennik

18.12.2019 06:58Аналогично! habr.com/ru/post/27055

PS Я про свои коммерческие проекты обычно вообще ничего не пишу. А про некоммерческие лень…

PPS Логарифм по схеме АЦП последовательного приближения. Понравилось!

Dioxin

По-моему это офигенно.

AndrF

Только одна имеющаяся ESP32 будет намного мощней всех Z80…