Первоначальный замысел статьи состоял в описании Периферии Независимой от Ядра микроконтроллеров Microchip, но тема оказалась весьма обширной, поэтому в качестве первого шага расскажем о CLC – конфигурируемых логических ячейках (Configurable Logic Cell).

В статье (Использование конфигурируемых логических ячеек для управления светодиодной лентой WS2812 [1]) было рассмотрено как логические ячейки CLC PIC-контроллеров могут существенно упростить решение задачи формирования сигналов управления драйверами WS2812 и аппаратно реализовать функции, на программное решение которых может не хватать быстродействия простого микроконтроллера.

Цель представленной статьи заключается в более близком знакомстве с конфигурируемыми логическими ячейками в PIC микроконтроллерах Microchip, в демонстрации примеров реализаций и, по возможности, натолкнуть читателя на мысли по использованию CLC своих проектах.

Если очень кратко, то CLC это одна из частей ПНЯ.

Введение.

Описание. Варианты конфигурации. Что может быть входами и выходами

Конфигурируемые логические ячейки CLC являются частью ПНЯ – Периферии Независимой от Ядра (Core Independent Peripheral, CIP), т.е. функционирование такой периферии не зависит (почти) от тактовой частоты микроконтроллера и его состояния (RUN, IDLE, SLEEP).

Конечно же, подобная периферия конфигурируется программой микроконтроллера, но дальнейшее функционирование может быть независимым.

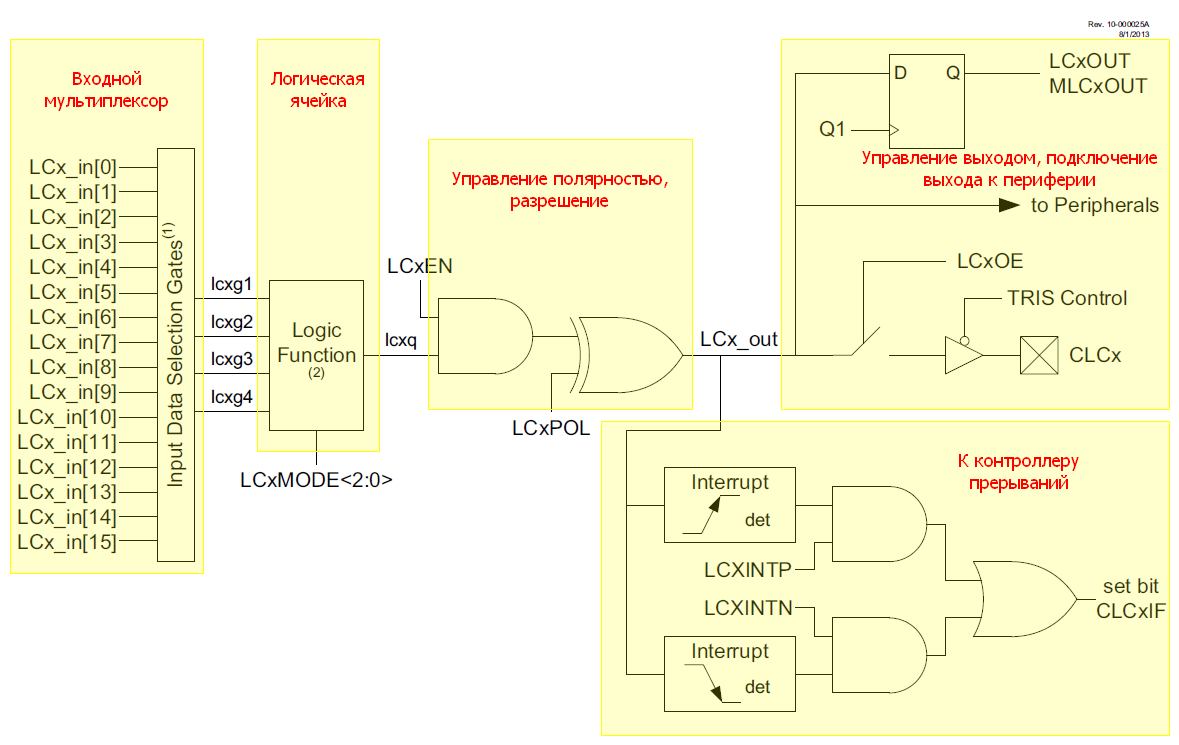

Каждая ячейка содержит входной мультиплексор, логическую функцию, управление выходом, подключение к контроллеру прерываний.

Общая схема одной логической ячейки приведена на рис.1.

Рис.1. Структура одной логической ячейки CLC

Каждая из логических ячеек имеет 4 входа, сигналы для которых выбираются входным мультиплексором, при этом каждый вход может быть прямым или инверсным. Часть входов может не использоваться и подключаться к уровню лог.0 или лог.1.

Входы для ячеек могут иметь внешние подключения (порты ввода/вывода) и внутренние (сигналы другой периферии: ШИМ, компараторы, таймеры и др. и выходы самих CLC).

Выход ячейки CLC имеет управляемую полярность, может подключаться на выходной порт микроконтроллера, к другой периферии, формировать запрос на прерывание по изменению состояния (по фронту и/или спаду).

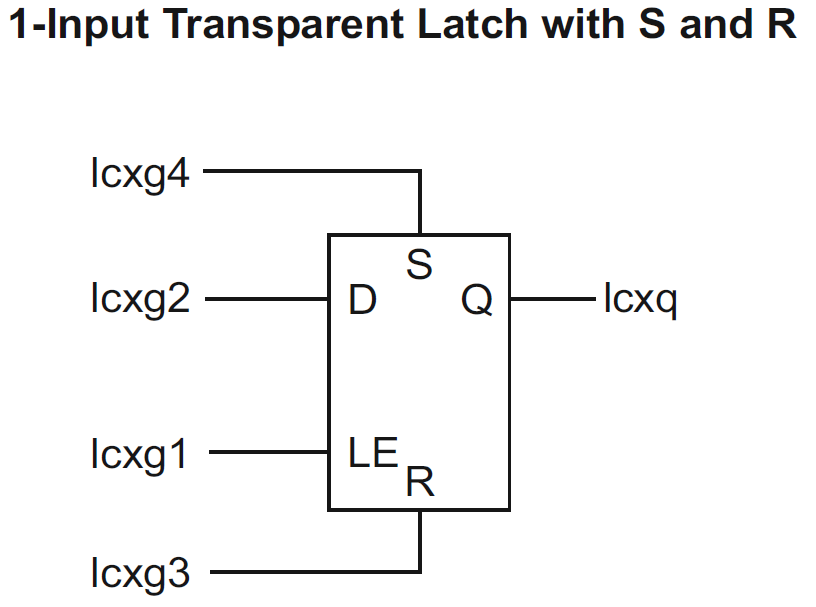

Логическая функция каждой ячейки выбирается из 8-и вариантов (см. табл.1)

| лог. ячейка | лог. ячейка |

|---|---|

|

|

|

|

|

|

|

|

Таблица 1. Варианты функций логических ячеек.

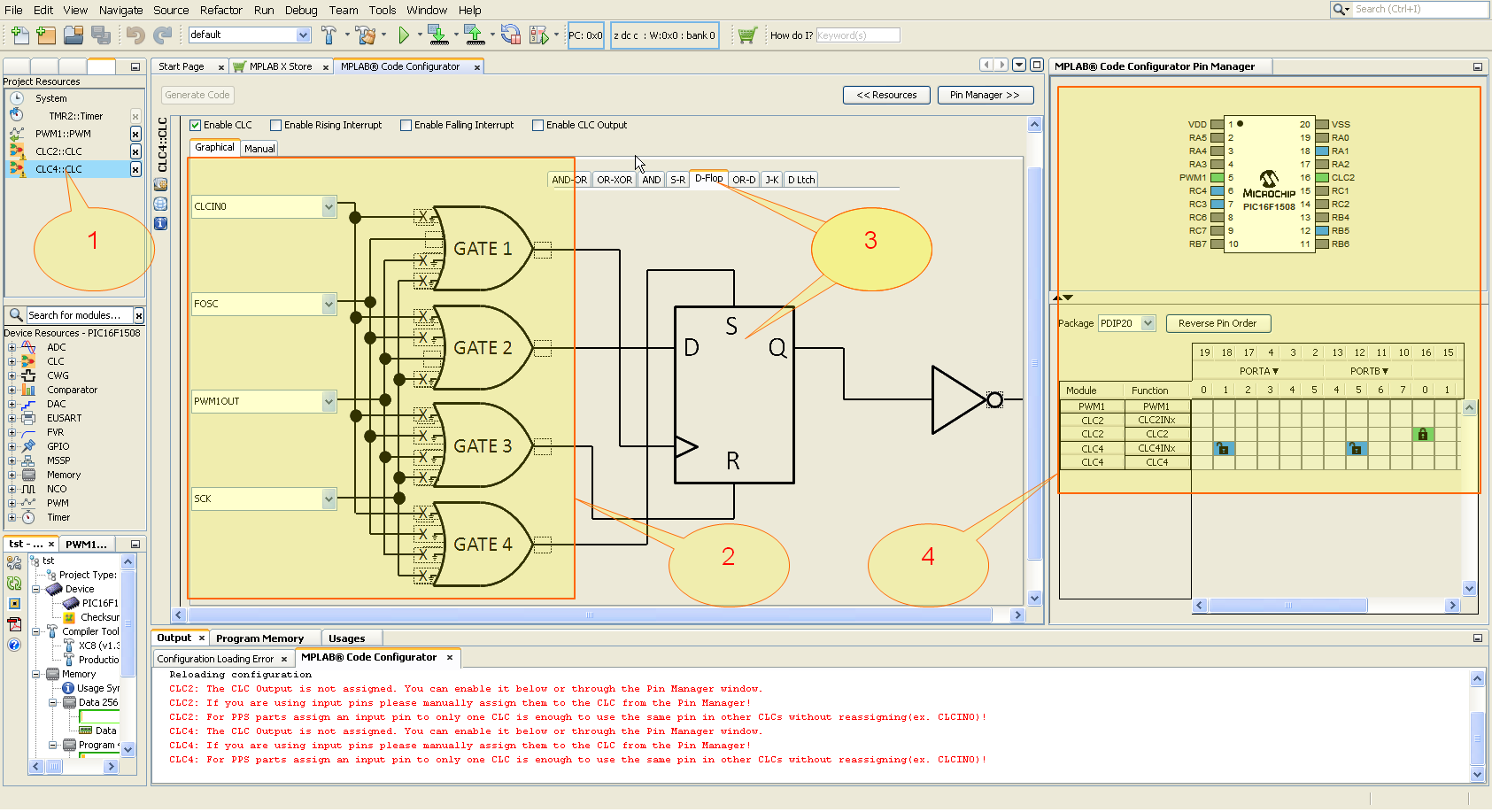

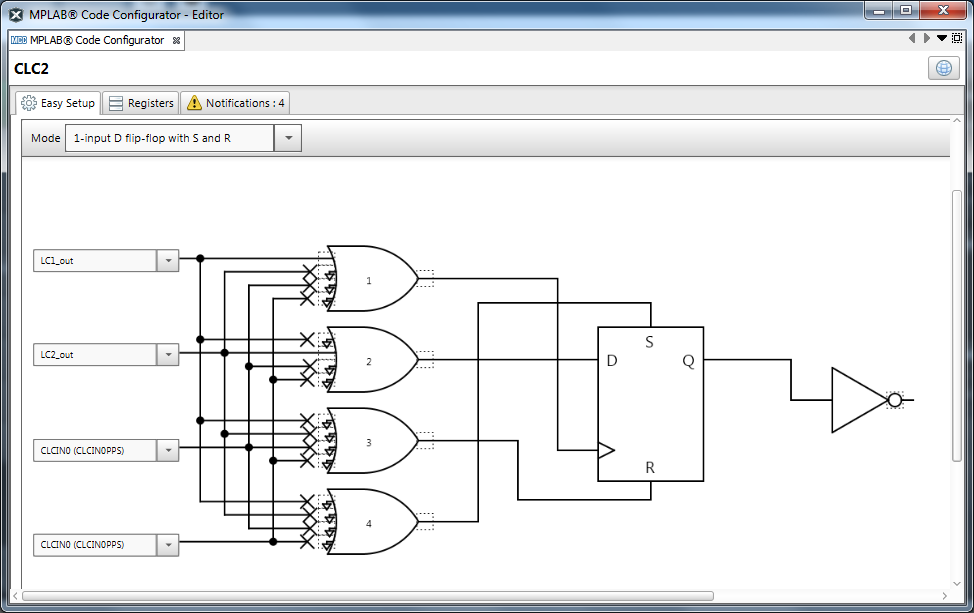

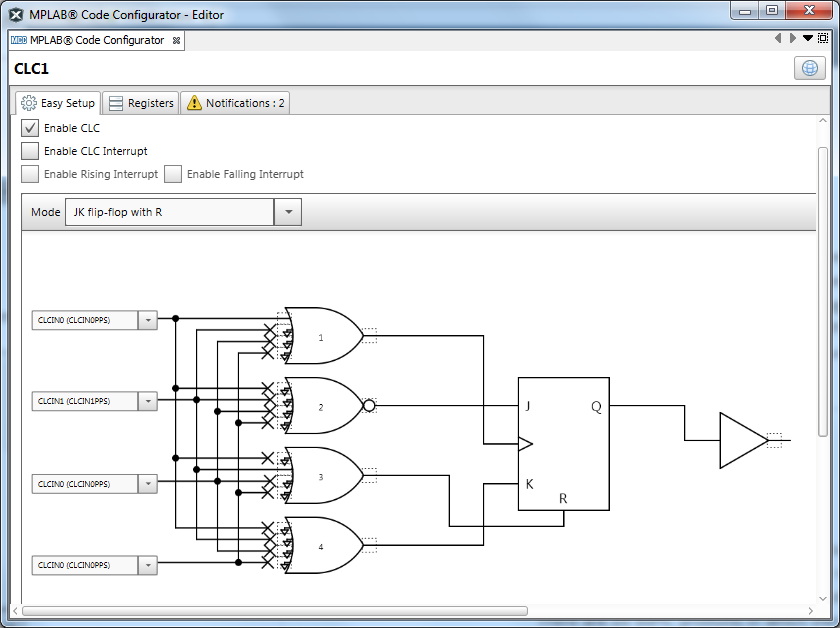

Так как логические ячейки имеют массу настроек, то проще всего конфигурировать CLC через плагин MPLAB Code Configurator в среде разработки MPLAB X, который создает Си файлы настроек задействованной периферии.

Рис. 2. Среда разработки Mplab X IDE с запущенным плагином Mplab Code Configurator (MCC)

где:

1 – редактируемая ячейка;

2 – настройка входного мультиплексора и полярности входов;

3 – функция логической ячейки;

4 – резервирование портов ввода/вывода.

Обратите внимание на входные гейты на входе CLC (рис.2, п.2), которые выполнены как элементы 4-ИЛИ.

При необходимости, в соответствии законам де Моргана, входные гейты можно преобразовать из базиса ИЛИ в И (см. Табл.2).

Таблица 2. Преобразование логических функций

| Логическая функция | Эквивалентное представление в CLC |

|---|---|

| 4-ИЛИ (OR) |  |

| 4-ИЛИ-НЕ (NOR) |  |

| 4-И-НЕ (NAND) |  |

| 4-И (AND) |  |

Примеры использования CLC

Плавное изменение яркости светодиода (мерцание)

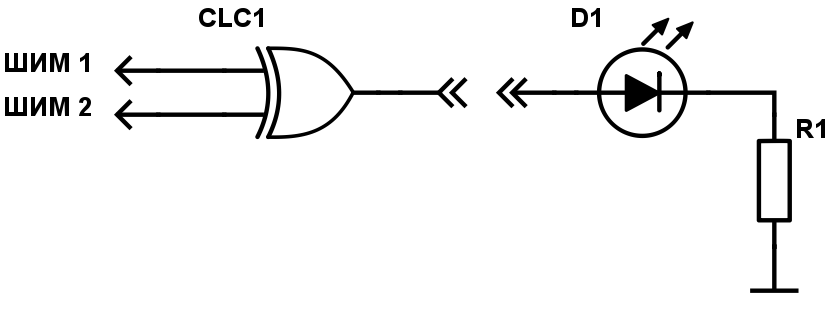

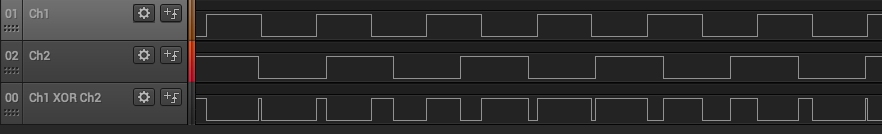

Если сигналы двух ШИМ с близкими частотами подключить к входам CLC сконфигурированной как элемент XOR (исключающее ИЛИ), то можно организовать «мерцание» светодиода (периодическое изменение скважности). При этом решение полностью аппаратное и не требует участия ядра МК (программы).

Рис. 3a. Схема «ШИМ модулятора»

Рис. 3b. Диаграммы демонстрирующие принцип изменения скважности

Если под такую простую задачу жалко использовать два ШИМ-модуля, то возможны варианты реализации без ШИМ:

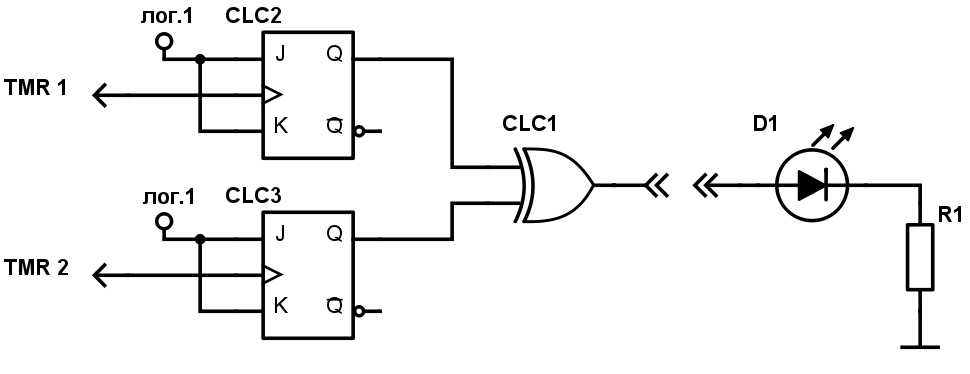

А) Используем сигналы переполнения двух таймеров (события), плюс три ячейки CLC.

На два JK- триггера в счетном режиме подаем сигналы с таймеров (postscaled out) – получаем на выходе меандры, которые затем подаем на элемент XOR.

Рис. 3c. Реализация ШИМ модулятора без входных ШИМ сигналов

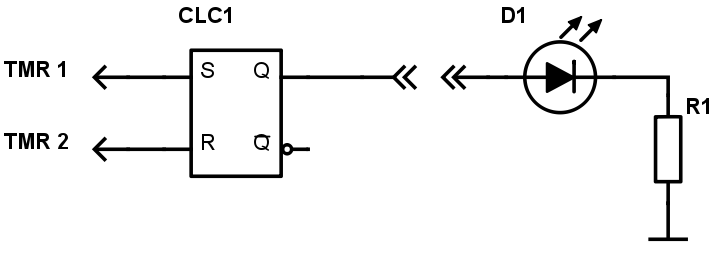

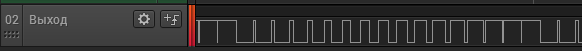

Б) Используем сигналы переполнения двух таймеров и одну CLC.

На входы RS триггера подаем сигналы с Таймера (postscaled out) – получаем на выходе «пилообразный ШИМ» (рис. 3e).

Рис. 3d.

Рис. 3e.

Делитель частоты

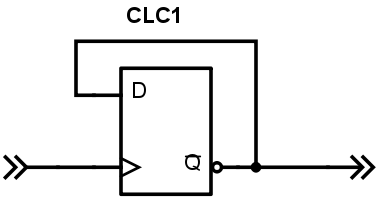

Схема делителя частоты на 2 приведена на рис. 4a. Используется один D-триггер в счетном режиме. Входной сигнал подается на вход тактирования, вход D соединен с инверсным выходом триггера. В момент поступления на вход тактирования фронта на входе D всегда будет инверсный сигнал относительно текущего состояния триггера, т.е. состояние триггера будет меняться только по фронту входного сигнала.

Рис.4а. Делитель на 2.

В плагине MPLAB Code Configurator подобная схема может выглядеть так:

Рис. 4b. Делитель на 2 в настройках MCC.

Рис.4c. Диаграмма на входе и выходе делителя.

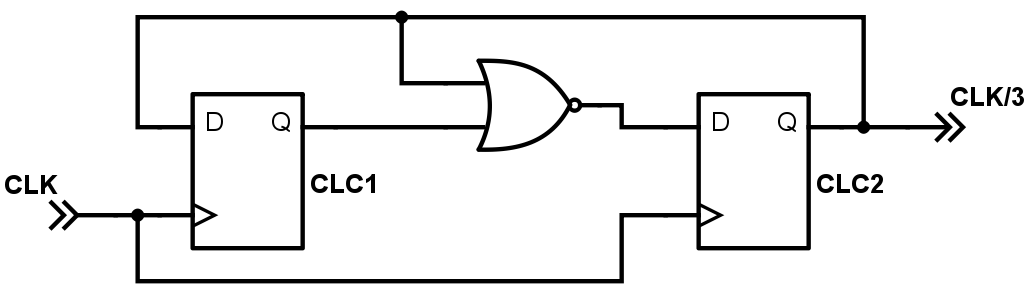

Делитель на 3 изображен на рис. 4d.

Рис. 4d. Делитель на 3.

Делитель на 4 это два последовательно включенных делителя на 2 ;-)

Где могут применяться делители? Там, где нужно поделить частоту.

Следующий пример использует делители частоты.

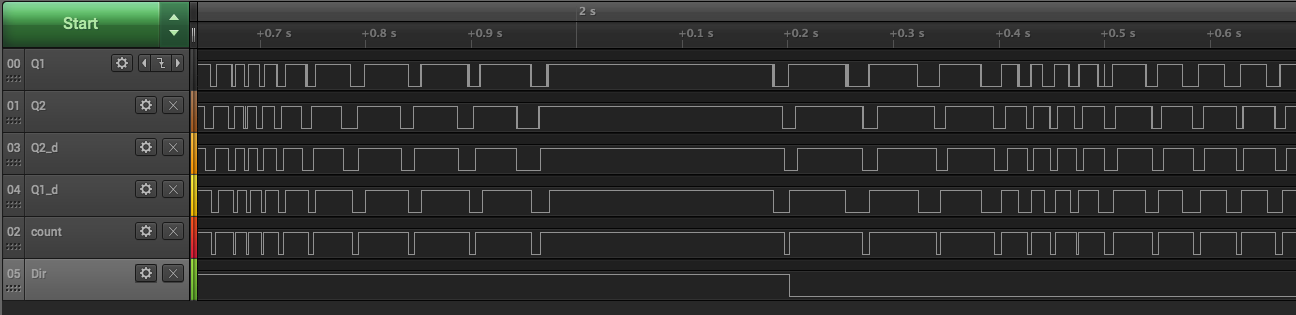

Драйвер шагового двигателя

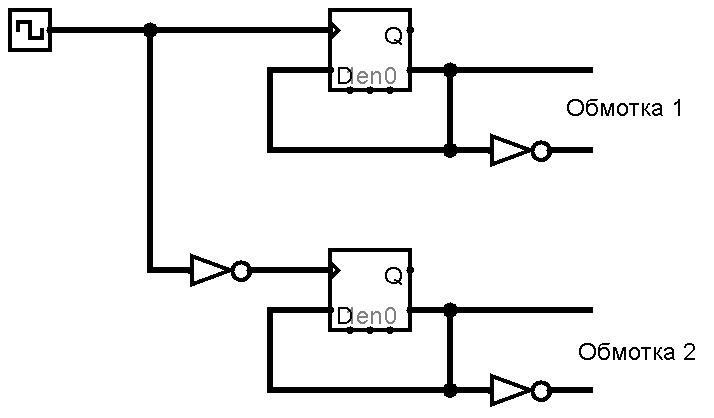

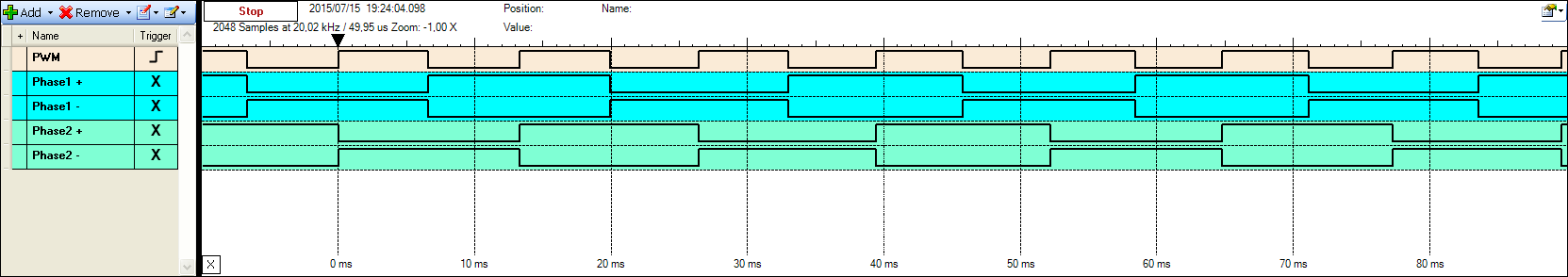

Один из самых простых вариантов управления Шаговым Двигателем (ШД) это полношаговое управление (full step). В этом варианте сигналы управления сдвинуты на 90°. Поэтому можно взять периодический сигнал, на один делитель частоты подать его в прямом виде, на другой – в инверсном.

Рис. 5a. Формирователь сигналов управления шаговым двигателем.

Рис. 5b. Диаграмма на выходе формирователя.

Изменение частоты на входе CLC будет изменять частоту управляющих сигналов шагового двигателя. Входную частоту можно брать с входа микроконтроллера (внешний сигнал), либо от внутреннего источника – ШИМ или NCO генератора.

При управлении ШИМ-ом нужно менять 2 параметра: регистр периода (частота) и регистр скважности, так как управляющий сигнал должен быть с 50% скважностью.

Применение NCO (Numerically Controlled Oscillator, управляемый генератор) выглядит более привлекательным, так как это генератор может автоматически формировать меандр, поэтому для изменения частоты нужно менять значения только в одном регистре.

Для смены направления нужно инвертировать сигналы на одной из фаз.

Задержка. Формирование импульса по фронту, спаду, изменениям

Для некоторых задач может понадобиться формирование задержанного импульса.

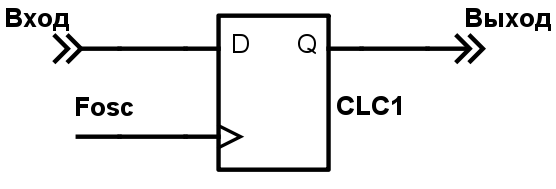

Для этого можно применить D-триггер. На счетный вход падаем входной сигнал, на вход тактирования – какой либо высокочастотный сигнал (например тактовой частоты Fosc). Таким образом, изменение выхода триггера будет происходить только по фронту тактового сигнала.

Данный метод будет сдвигать фронт и спад сигала на период Fosc (тактовой частоты) только если оба сигнала синхронны. Поэтому для гарантированного сдвига на 1 период Fosc сдвигаемый сигнал должен формироваться самим микроконтроллером (ШИМ, NCO и др.). Если входной сигнал асинхронный, то на входе можно поставить синхронизатор на точно таком же D-триггере (т.е. сперва сдвинуть асинхронный сигнал до первого тактового импульса, а затем сдвинуть на полный период тактового сигнала).

Рис. 6a. Формирователь задержанного сигнала.

Рис. 6b. Диаграммы на входе и выходе формирователя задержанного сигнала.

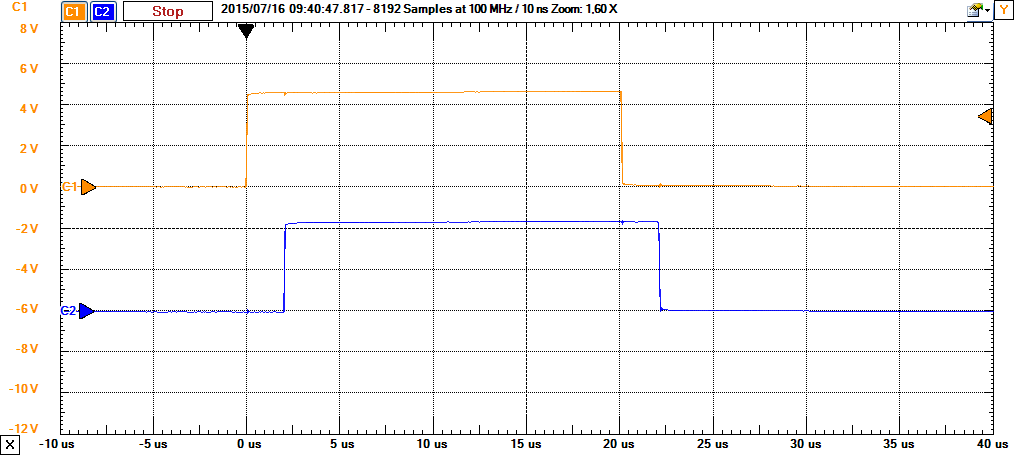

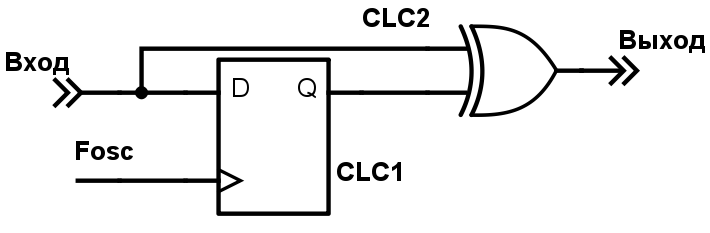

На основе этой схемы легко реализовать формирователь импульсов по изменению состояния входа, по фронту и по спаду.

Формирование импульсов по фронту и спаду

Рис. 7a. Формирователь импульсов по фронту и спаду

Рис. 7b. Диаграммы на входе и выходе формирователя импульсов по фронту и спаду

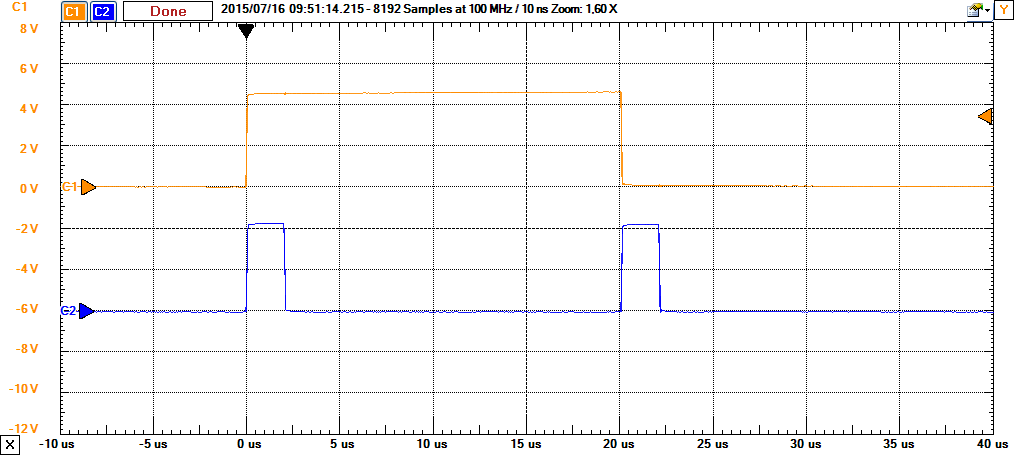

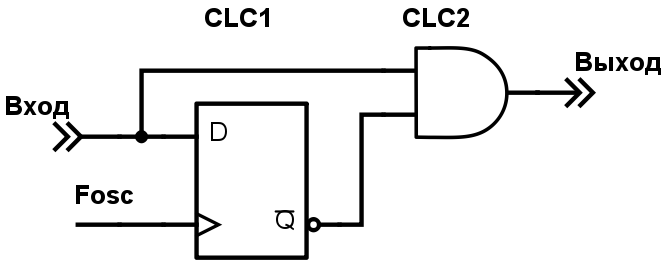

Формирование импульсов по фронту

Рис. 8a. Формирователь импульсов по фронту.

Рис. 8b. Диаграммы на входе и выходе формирователя импульсов по фронту

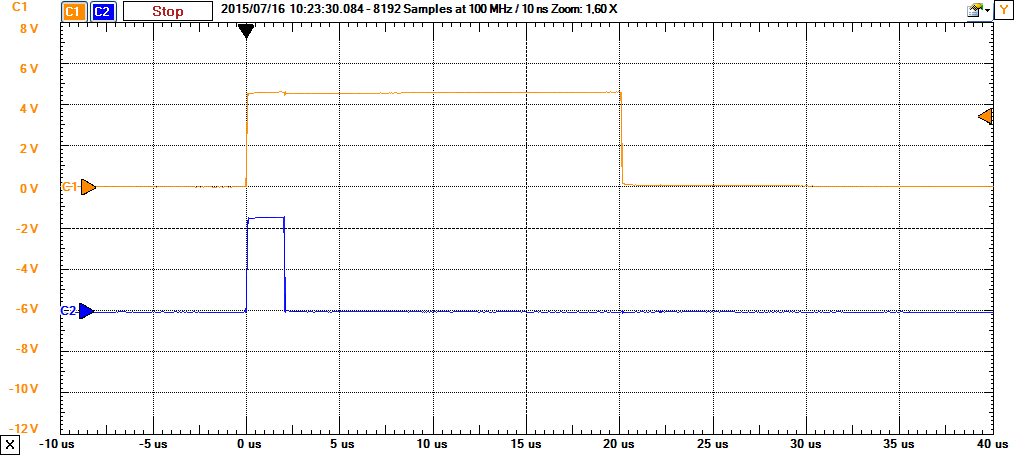

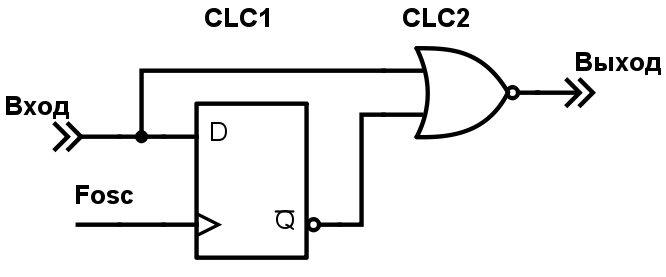

Формирование импульсов по спаду

Рис. 9a. Формирователь импульсов по спаду

Рис. 9b. Диаграммы на входе и выходе формирователя импульсов по спаду

Где могут применяться подобные схемы?

Можно использовать, например, при построении импульсного источника питания для бланкирования сигнала обратной связи от компаратора во время переключения силового ключа (подробнее см.ниже).

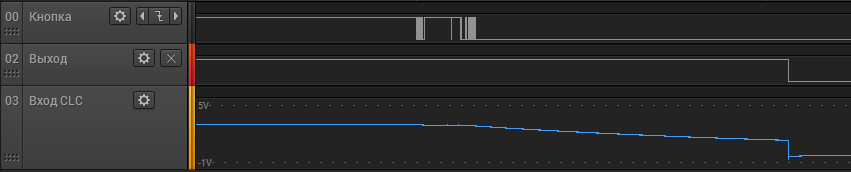

Подавление дребезга контакта

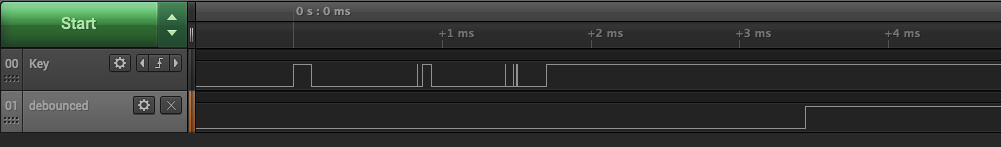

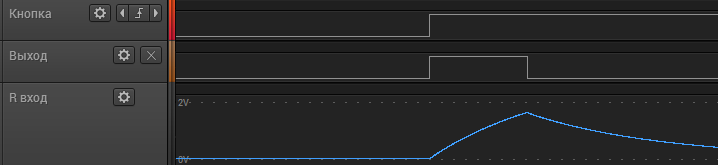

При замыкании и размыкании контактов наблюдается дребезг. Наверняка с этим явлением многие сталкивались при опросе состояния механических кнопок. Логические ячейки совместно с таймером могут решить задачу аппаратно.

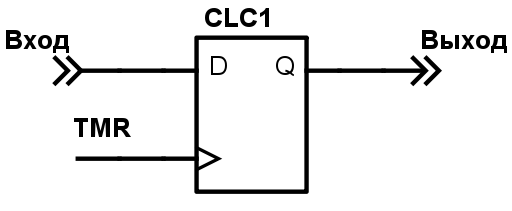

Схема реализации точно такая же как для формирования задержанного импульса, только период тактового сигнала нужно брать побольше. Суть метода заключается в том, что выход триггера не реагирует на вход если нет сигнала тактирования, поэтому схема не реагирует на каждое переключение входа.

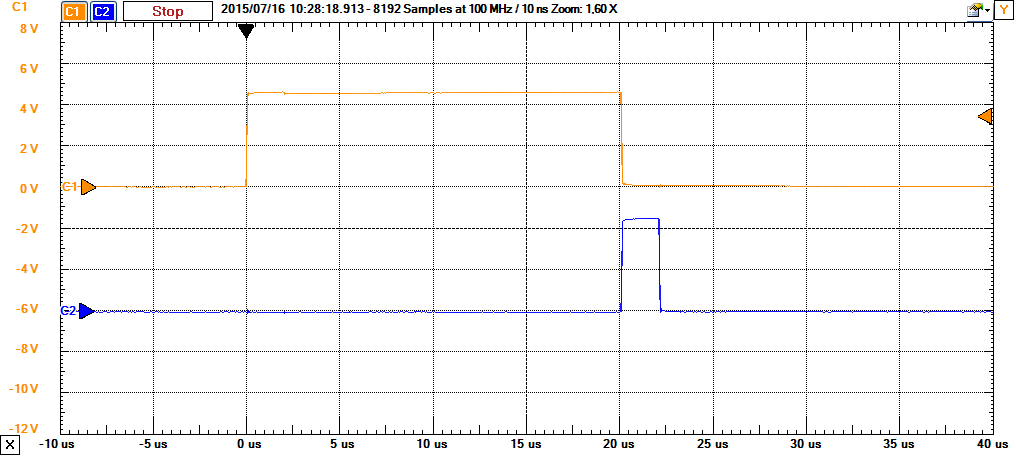

Рис.10a. подавление дребезга.

Рис.10b. Диаграммы сигналов на входе и выходе схемы подавления дребезга.

Где применяется?

Собственно опрос кнопок, предотвращение многократных ложных срабатываний.

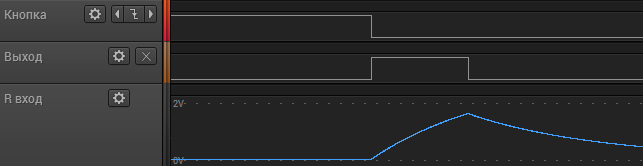

Еще варианты

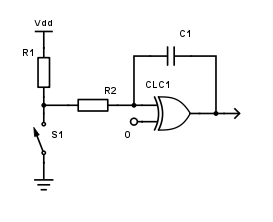

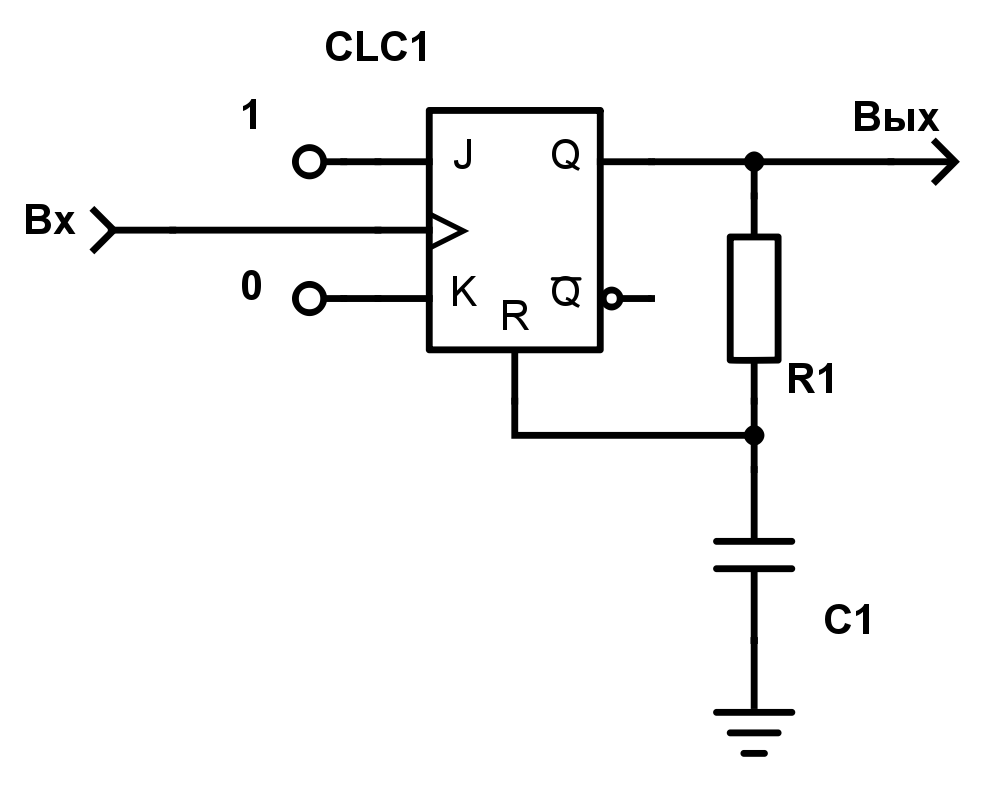

Рис.10c. Подавление дребезга с задержкой с RC-цепочкой

Рис.10d. подавление дребезга

В отличие от предыдущего примера задержка определяется параметрами RC цепи и не требует задействование таймера.

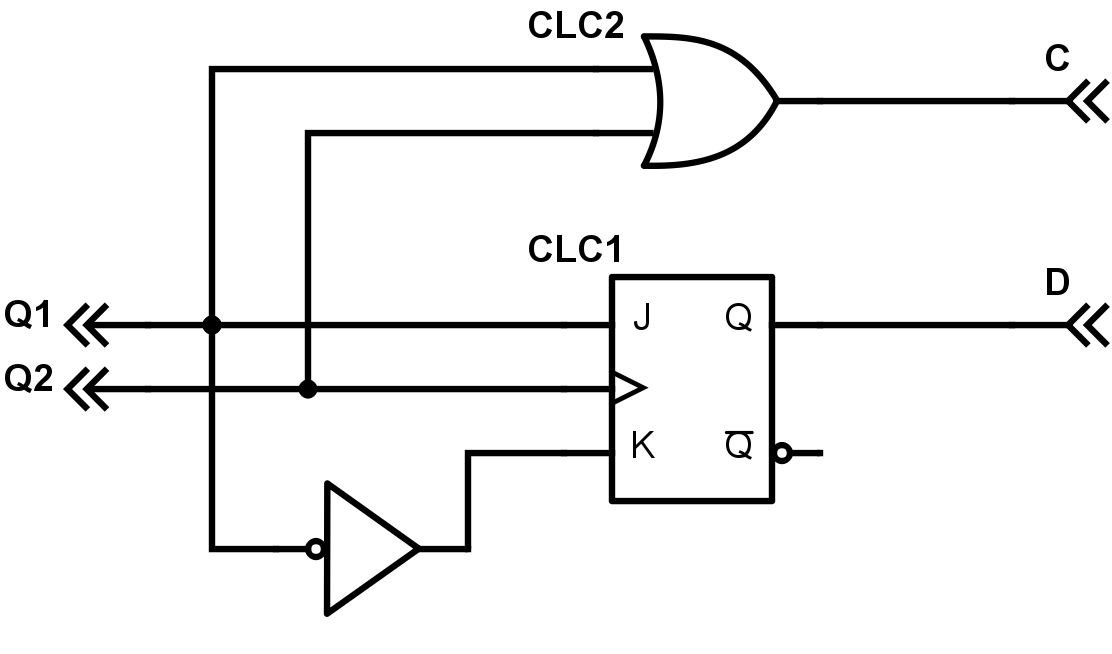

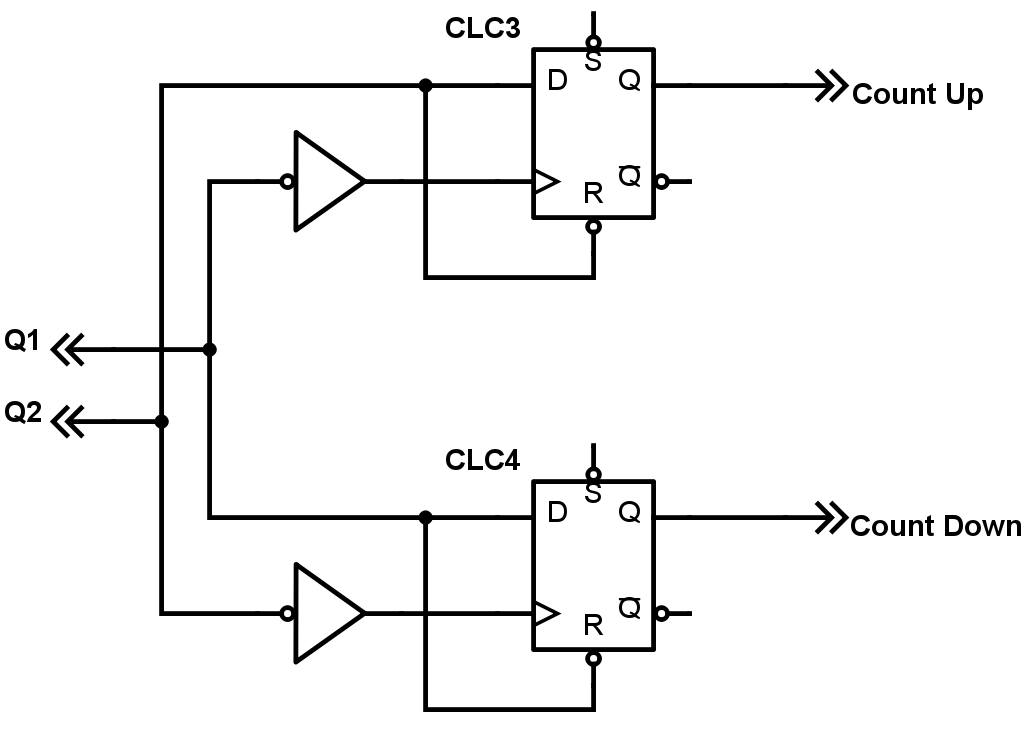

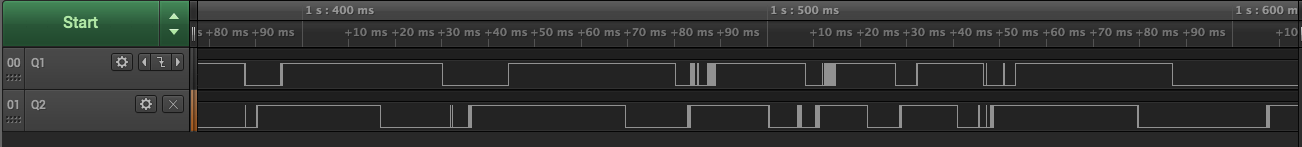

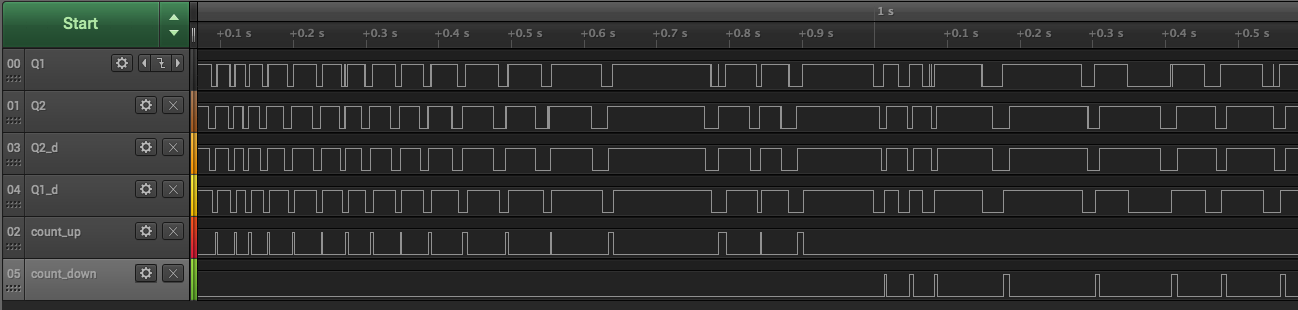

Квадратурный энкодер

Квадратурный энкодер это устройство, при вращении оси которого формируются два квадратурных сигнала (сдвинутых по фазе). Применяется в определении скорости (угла поворота или числа оборотов) и направления вращения/перемещения. Пожалуй, самое известное применение это колесо мышки.

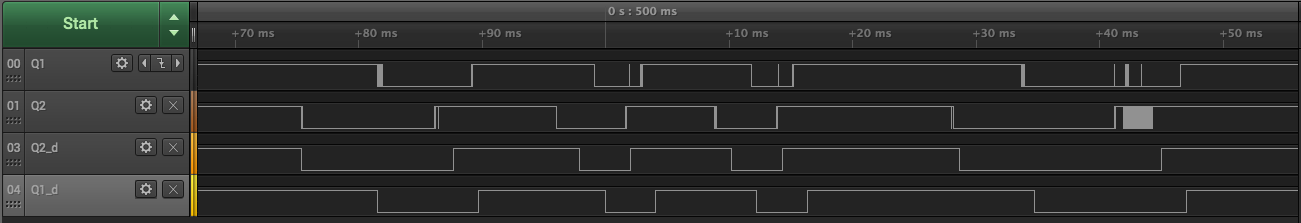

Ниже приведены две схемы декодирования сигналов квадратурного энкодера.

Рис. 11a. Квадратурный декодер со счетным выходом и сигналом направления.

Эта схема детектирует фазы входных сигналов (состояние выхода D показывает направление вращения энкодера) и выдает тактовые сигналы (выход С).

Рис 11b. Квадратурный декодер с двумя счетными выходами

Эта схема выдает импульсы. Один выход при вращении по часовой стрелке, второй выход – при обратном вращении.

При переключении контактов энкодер выдает множественные ложные срабатывания (дребезг контактов).

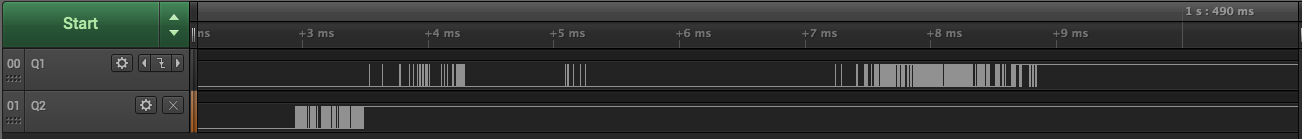

Рис. 11c. Сигналы с выходов механического квадратурного энкодера

Вот тут фрагмент покрупнее:

Рис. 11d. Сигналы с выходов механического квадратурного энкодера

Поэтому обе схемы нуждаются в очищенных от дребезга сигналов. Ранее мы уже рассматривали варианты подавления дребезга аппаратно на ячейках CLC.

Рис. 11e. Входные сигналы с энкодера и очищенные от дребезга.

Под обработку сигналов квадратурного энкодера понадобятся 4 ячейки CLC – две для подавления дребезга и две для детектирования.

Рис. 11f. Диаграммы сигналов обработки квадратурного энкодера для схемы с выходом направления

Рис. 11g. Диаграммы сигналов обработки квадратурного энкодера для схемы с двумя счетными выходами.

Входы и выходы логических ячеек могут подключаться к портам микроконтроллера, а могут иметь только внутренние соединения. Для данного примера необходимы только два входа, выходы декодера могут подключаться к внутренним счетчикам микроконтроллера, формировать прерывания, опрашиваться программой и пр… Но для задач тестирования можно все выходы CLC вывести наружу и проверить правильность работы схемы.

Где применяется?

Механические и оптические энкодеры, подсчет числа входящих и выходящих людей, закрытие турникета при прохождении в неположенном направлении ))

Манчестерский кодер

Манчестерское кодирование широко применяется при передаче сигналов. Каждый бит делится на два интервала, после первого интервала (в середине информационного бита) происходит смена уровня сигнала. Передача каждого информационного бита сопровождается изменением уровня, Нули и Единицы отличаются фазой (1 – перепад из 0 в 1, «0» — из 1 в 0). Таким образом, манчестерский код имеет следующие особенности:

- Самосинхронизирующийся – нет необходимости передачи специальных синхро сигналов, так как уровень передаваемого сигнала гарантировано меняется в середине информационного бита; высокая плотность информации

- Нет постоянной составляющей (сигнал меняется каждый такт)

Схема кодирования очень проста и использует один логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ.

На выходе получаем кодированный поток.

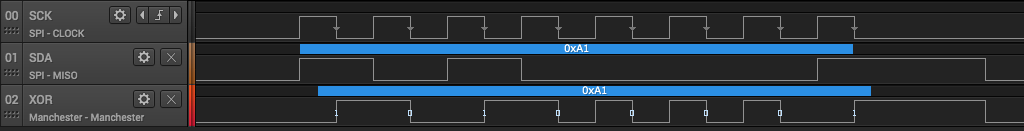

Рис. 12. Диаграммы формирователя Манчестерского кода

Декодер манчестерского кода

Схема манчестерского декодера гораздо сложнее. Её задача выделить синхро-импульсы и битовый поток.

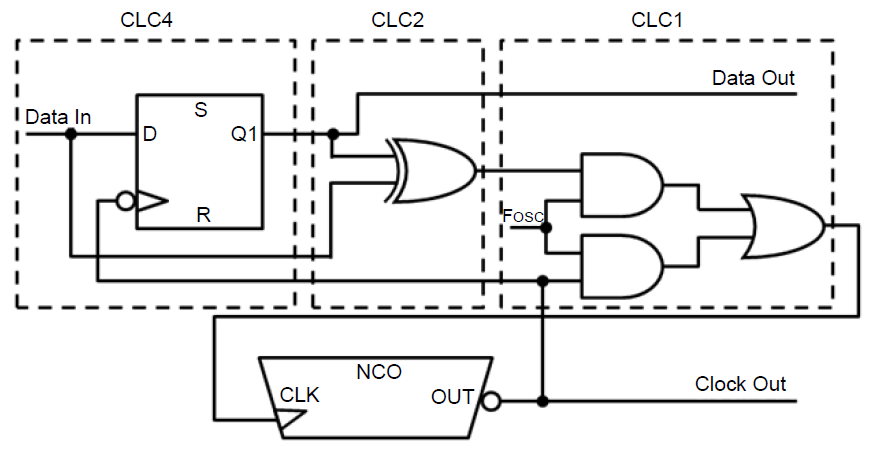

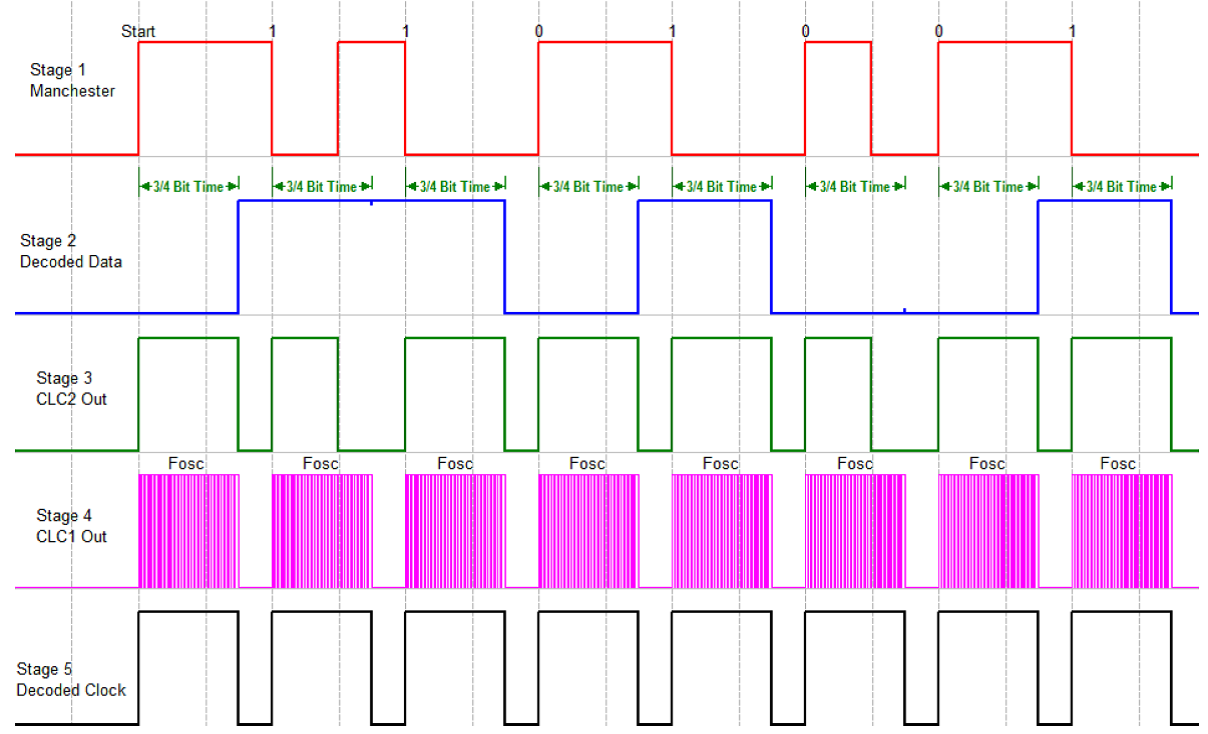

В примере применения AN1470 [2] предлагается следующая реализация аппаратного декодирования Минчестерского кода на основе CLC и NCO (управляемого генератора).

Рис.13a. Схема декодера Манчестерского кода

Рис. 13b. Диаграммы, поясняющие работу декодера

Стадия 1 – D-Триггер

Ячейка CLC4 (D-триггер) защелкивает входной поток по спаду сигнала синхронизации. Выход с этого триггера будет являться декодированными (восстановленными) данными из входного потока.

Стадия 2 – элемент XOR (CLC2)

Поскольку в Манчестерском кодировании изменение сигнала происходит в середине каждого информационного бита, то можно использовать элемент ИСКЛЮЧАЮЩЕЕ ИЛИ чтобы обеспечить нарастающий фронт на стадии 3 в середине каждого бита, т.е. мы синхронизируем декодер в середине каждого бита.

Стадия 3 – NCO + AND-OR (CLC1)

модуль NCO, используется для генерации ? битового интервала по завершении которого производится захват (фиксация) данных. NCO используется в режиме с активным низким состоянием. Длительность импульсов можно регулировать с помощью регистров. Модулю NCO необходим источник тактовых импульсов, которые поступают ему из CLC1.

Эти два блока являются наиболее важными в декодере. Они создают импульсы фиксированной длины после каждого нарастающего фронта сигнала, выходящего из «стадия 2». Выходной сигнал NCO подается обратно в элемент И-ИЛИ так, что если выход из «стадия 2» становится равным нулю, то NCO будет продолжать тактироваться до своего переполнения.

Выделенные сигналы синхронизации и данных можно завести на модуль SPI. Тогда, по приему кодовой посылки, в буфере SPI получим декодированные данные и прерывание по приему.

Ждущий мультивибратор

Для формирования одиночного импульса по фронту или спаду входного сигнала служат ждущие мультивибраторы.

Рис. 14a. Схема ждущего мультивибратора на JK-триггере.

Рис. 14b. Реализация ждущего мультивибратора на JK-триггере в PIC-контроллере.

Рис. 14c. Диаграммы поясняющие работу ждущего мультивибратора

Инвертирование сигнала на входе синхронизации реализует ждущий мультивибратор с запуском по спаду входного сигнала (Рис.14d).

Рис. 14d. Диаграммы ждущего мультивибратора с запуском по спаду.

В отличие от рассмотренных ранее формирователей импульса по фронту и спаду (см.рис 8а, 9а) у данной схемы длительность импульса задается не частотой сигнала на входе тактирования, а параметрами RC-цепочки.

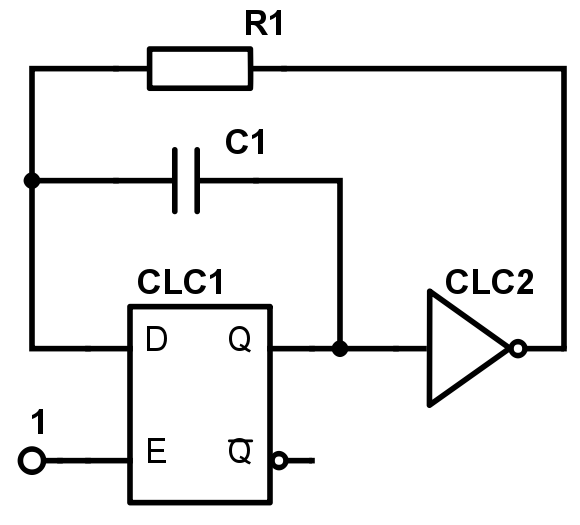

Мультивибратор

Простейший генератор можно сделать на двух CLC (D-триггер + инвертер).

Недостатком является низкая стабильность, так как пороги переключения зависят от уровней лог.0 и 1 конкретного типа микроконтроллера, которые могут «гулять» от температуры, напряжения питания и др. К тому же не очень правильно когда на цифровом входе уровень сигнала продолжительное время находится между 0 и 1.

Рис. 15a. Простейший мультивибратор на D-триггере.

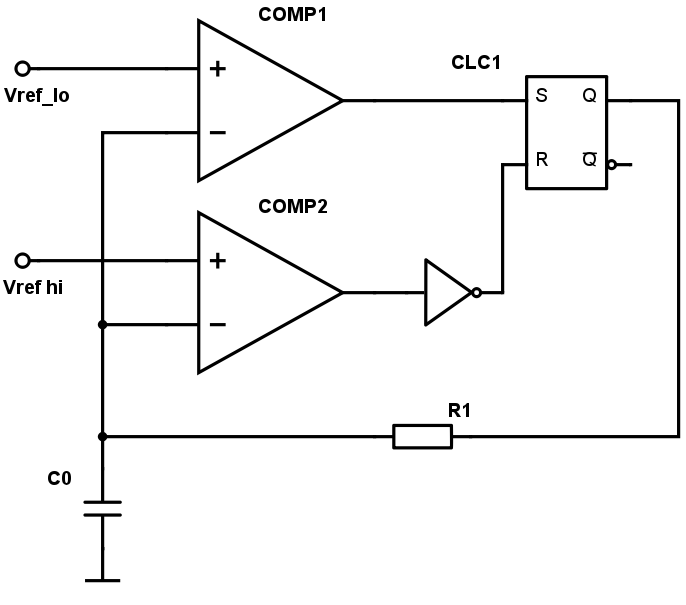

Следующая схема использует два встроенных компаратора и одну CLC. В этой схеме пороги срабатывания компараторов задаются источником опорного напряжения и внешним делителем (или встроенным ЦАП). Схема будет более стабильной и к тому же компараторы имеют аналоговые входы и позволяют любые напряжения на входе в пределах напряжения питания.

Рис.15b. Мультивибратор на двух компараторах и RS-триггере.

Для данного примера от ПНЯ помимо CLC нам понадобятся 2 компаратора, а так же источники опорного напряжения (внешние на делителе или внутренние).

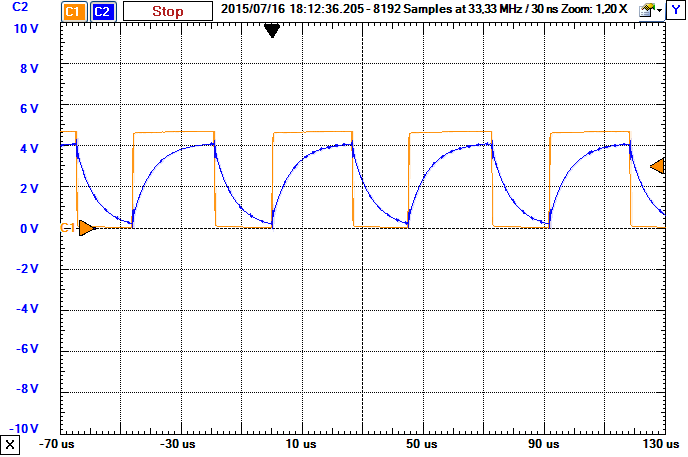

В начальном состоянии на выходе триггера установлен уровень лог.0, конденсатор разряжен, на компараторе COMP1 на выходе появляется лог.1, триггер устанавливается в 1, конденсатор заряжается через резистор до уровня напряжения верхнего порога (Vref hi), при достижении которого на входе R триггера появляется лог.1. Триггер перекидывается в противоположное состояние, конденсатор начинает разряжаться через резистор и т.д… Таким образом, мы получили полностью программно-независимый генератор. Но в данной схеме микроконтроллер может программно изменять частоту с помощью изменения порога срабатывания одного из компараторов (изменением опорного напряжения встроенным ЦАП или др.).

Рис.15c. Диаграммы сигналов мультивибратора

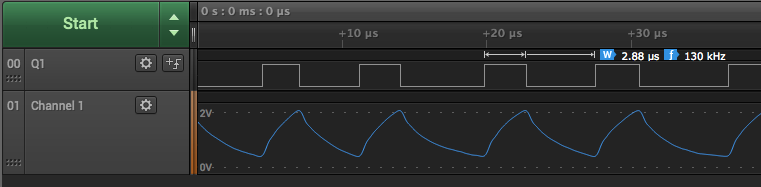

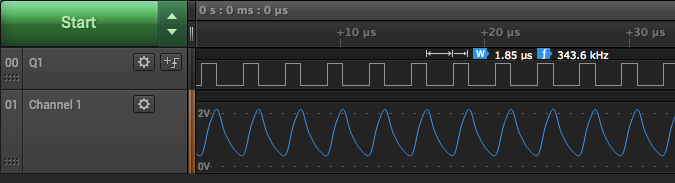

Измерение Емкости. Емкостной сенсор. Сенсорная кнопка

Частота мультивибратора (рис.15) зависит от значения емкости конденсатора и сопротивления резистора. Если один из параметров изменяется, то изменяется частота. Поэтому данная схема позволяет измерять сопротивление или емкость, например с помощью таймера микроконтроллера.

В качестве конденсатора может использоваться проводящая площадка, при касании которой мы будем вносить в схему дополнительную емкость, что приведет к уменьшению частоты генератора.

| сигналы | комментарий |

|---|---|

|

Осциллограммы без касания сенсора |

|

Осциллограмма при "нажатом" сенсоре |

Рис.16a. Диаграммы работы мультивибратора при изменении времязадающей емкости.

Подобным методом можно детектировать протечку воды или определять влажность почвы и использовать для автоматизации полива цветов ))

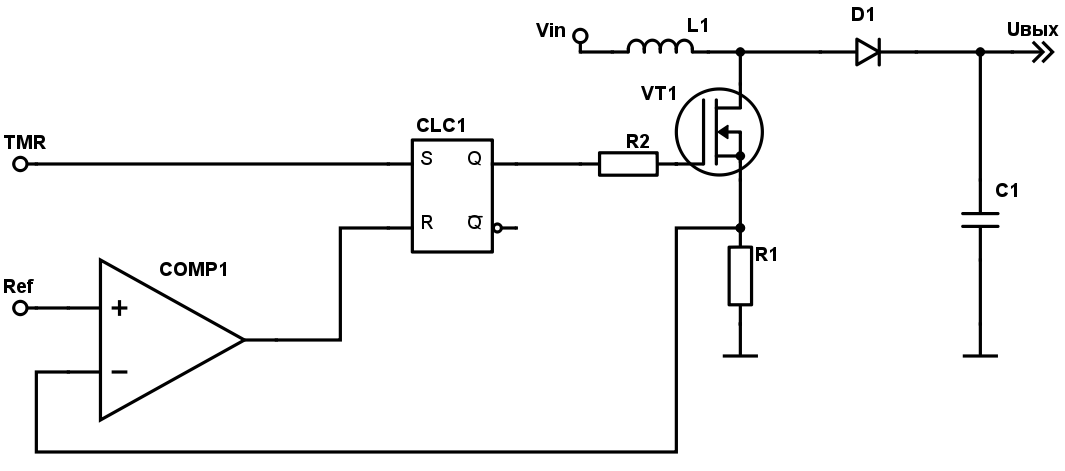

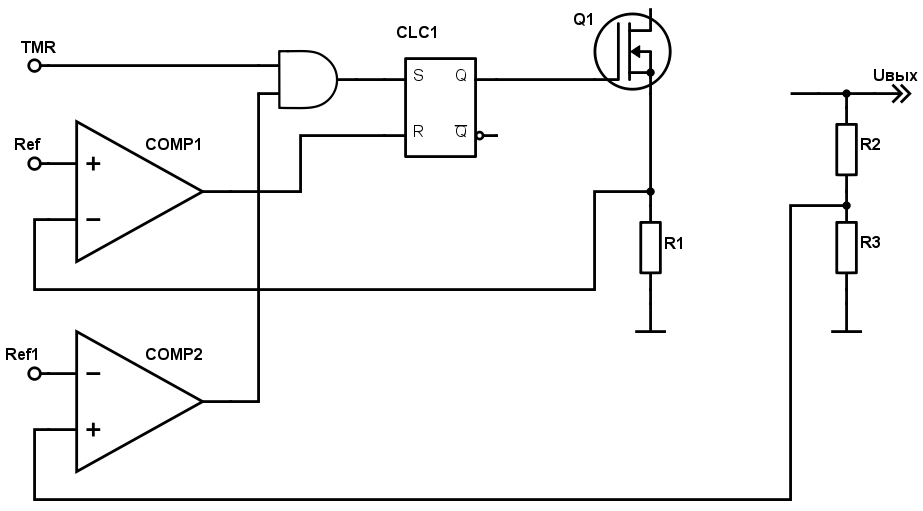

Импульсный источник питания

Еще один пример использования конфигурируемых логических ячеек совместно со встроенными компараторами.

Таймер TMR периодически устанавливает RS-триггер и открывает силовой транзистор. Ток начинает течь через индуктивность, напряжение на резисторе R1 линейно увеличивается. При достижении напряжения на R1 порогового значения срабатывает компаратор COMP1 и сбрасывает триггер, транзистор закрывается. Ток через индуктивность не может прерваться мгновенно, поэтому ток начинает течь через диод D1 и заряжает выходной конденсатор. По срабатыванию таймера триггер снова устанавливается и процесс повторяется.

Рис.17a. Простейший импульсный источник питания.

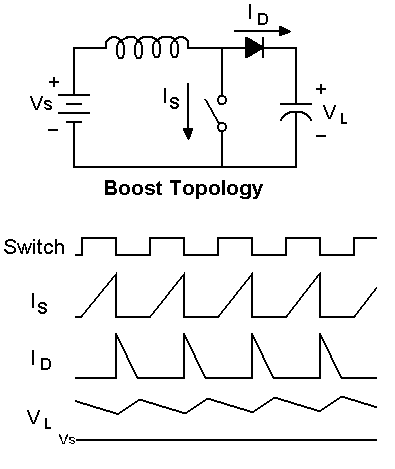

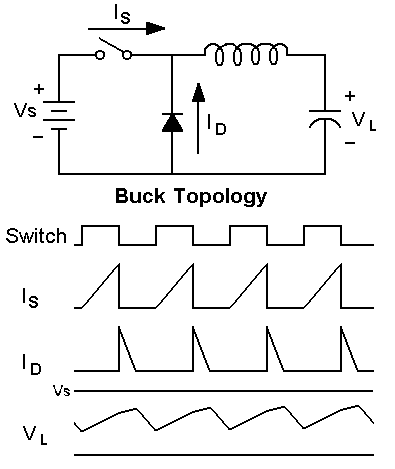

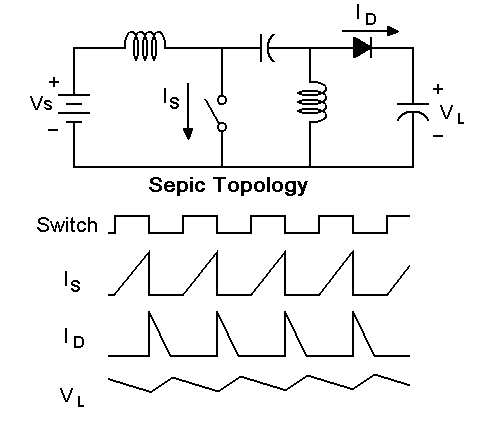

На рисунке приведена схема повышающего источника, но для других топологий (см. рис. 17b) работа схемы будет аналогичной, поэтому выходной каскад далее рисовать не буду.

| схема | описание |

|---|---|

|

повышающий |

|

понижающий |

|

Sepic |

Рис.17b. Различные топологии импульсных источников питания

Приведенная на рис. 17a схема выполняет функцию преобразования энергии и работает по пиковому значению тока в индуктивности. Можно ввести еще контур регулирования выходного напряжения. Наиболее просто сделать гистерезисное управление: когда напряжение на выходе ниже нормы – происходит накачка источника, когда напряжение выше – выдача управляющих импульсов на силовой транзистор блокируется.

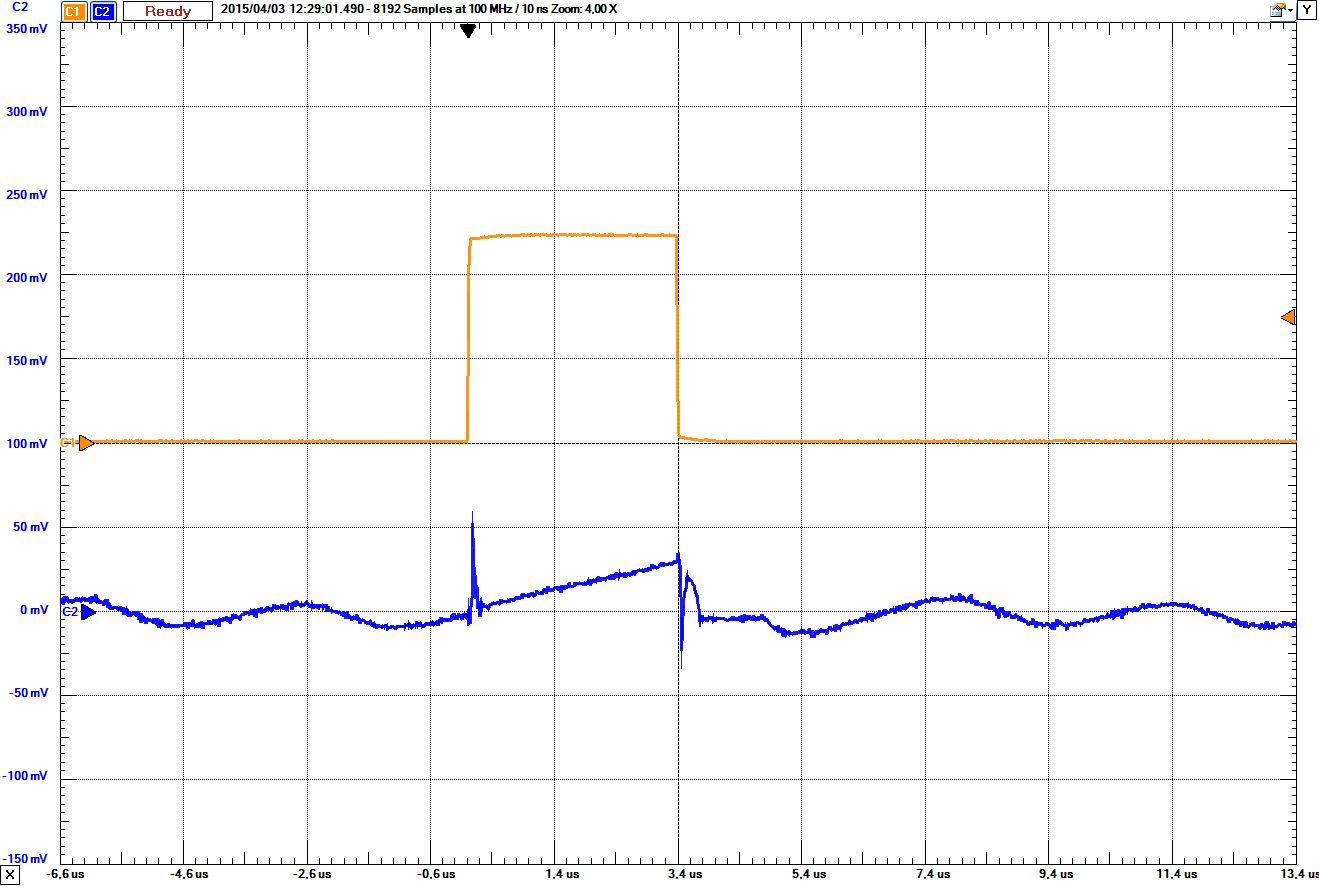

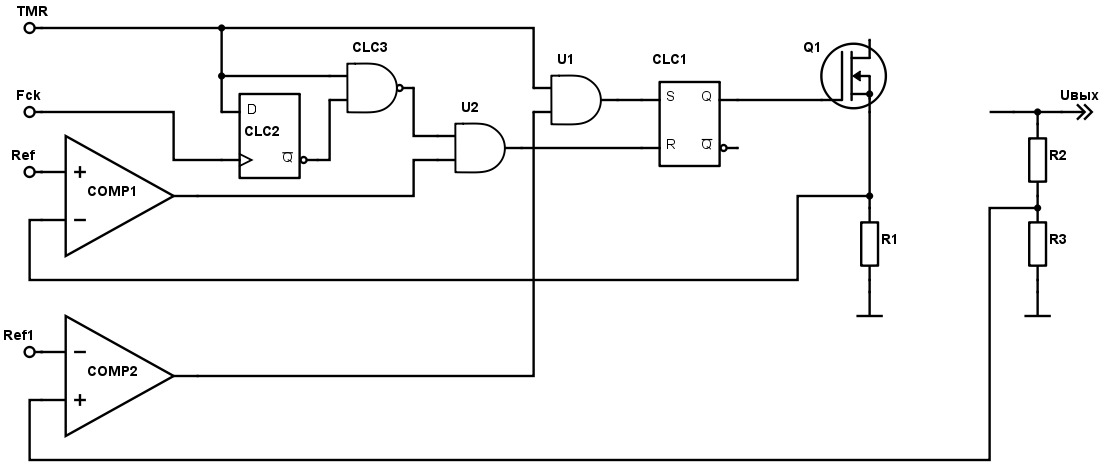

Рис.17c. ИИП с гистерезисным управлением

Включение силового транзистора будет генерировать помеху, которая может приводить к преждевременному срабатыванию компаратора COMP1. Для избавления от этого можно включить RC-фильтр в цепь между R1 и компаратором, а можно добавить рассматриваемый ранее блок бланкирования (формирование импульса по фронту, см. рис 8а, или рис. 14а), который после включения транзистора будет блокировать сброс триггера на короткий интервал времени.

Рис.17d. Помеха при коммутации силового ключа

Рис.17e. ИИП с гистерезисным управлением и бланкированием помехи переключения.

Элементы U1 и U2 можно привести к реализации на элементах ИЛИ и отнести к входу CLC1, тогда вся логическая часть схемы реализуется на трех ячейках CLC (обычно в микроконтроллерах Microchip имеется 4 ячейки).

Все что на схеме изображено левее силового ключа – находится внутри микроконтроллера, связи периферийных модулей так же осуществляются внутри кристалла микроконтроллера. Напряжения порогов Ref и Ref1 могут задаваться встроенными источниками опорного напряжения или ЦАП. Таким образом, импульсный источник питания с регулируемым выходным напряжением можно реализовать на периферийных модулях микроконтроллера. После первоначального конфигурирования схема будет работать полностью аппаратно без необходимости участия ядра в поддержании функции преобразователя. Ядро может заниматься интерфейсными задачами, индикации контроля и др.

Вообще, для построения импульсных источников питания в новых семействах PIC16F17xx микроконтроллеров Microchip есть дополнительные аналоговые (операционные усилители) и специализированные периферийные модули: модули пилообразной компенсации (Slope Compensation) и программируемый рамп-генератор (Programmable Ramp Generator, PRG), операционные усилители, модуль формирования комплементарных выходных сигналов (COG), HLT таймера. Но об этих частях ПНЯ постараемся рассказать в следующий раз.

Периферия независимая от ядра интересна сама по себе, но наибольшую пользу может принести возможность синтеза функциональных блоков, т.е. совместное использование нескольких периферийных модулей для решения конкретных задач. В этом случае тактовая частота, быстродействие и разрядность ядра уходят на второй план – аппаратная часть выполняет специализированные функции, а ядро занимается программной поддержкой работы изделия.

Литература

Комментарии (22)

Psychosynthesis

21.07.2016 21:37Блин это круто! Я даже сходу могу представить пару задач где это сильно бы мне пригодилось, но вот знаний работы логических элементов у меня лично не хватает чтобы вот так вот сходу начать это использовать.

А в каких популярных МК такое есть вообще? Я так понимаю это относительно новая технология в модельном ряде Микрочипа.

ariz0na

21.07.2016 22:47Для изучения рекомендую книгу Д. Харрис, С. Харрис. «Цифровая схемотехника и архитектура компьютера» (тут подробности http://habrahabr.ru/post/259505/)

Именно логические ячейки в PIC-ах у Microchip появились давно. Первые, если не ошибаюсь, в PIC10F3xx — это примерно 7 лет назад (первые PIC10 появились примерно в 2007)

Где есть… много где. Ниже ссылки на полезные документы, где в табличке приведены семейства и отмечено какая периферия у них есть — удобно для подбора нужного набора периферии

8-и битники (PIC10, PIC12, PIC16, PIC18): http://ww1.microchip.com/downloads/en/DeviceDoc/30010068D.pdf

16-и битники (PIC24) http://ww1.microchip.com/downloads/en/DeviceDoc/30010109B.pdf

32-х битные: недавно анонсированные PIC32MM получили немного CLC

ariz0na

21.07.2016 22:59Про Харрис и Харрис, Имею ввиду, что книга может быть полезна чтобы начать изучение логических элементов и синтез логических схем там подробно описан, тем более что книга есть на русском.

Книга, конечно, не совсем про это, но про «это» тоже есть ))

Carry

22.07.2016 01:01Классная штука!

Увеличили бы еще максимальный ток выходов CWG для управления мощными ключами напрямую — цены бы им не было!

ariz0na

22.07.2016 08:13Done ;)

см табличку по ссылке выше про 8-и битники. Там есть колонка HC I/O (mA), HC это High Current, есть МК с нагрузочной способностью 50 и 100мА (делают не все порты с такими функциями, но по паре присутствуют)

Eddy71

24.07.2016 13:05Спасибо большое за замечательное описание.

Интересно, а кроме плагина под MPLABX есть ещё способы конфигурирования CLC (кроме как ручками)?

ariz0na

24.07.2016 13:09Была отдельная утилита для конфигурирования CLC, но сейчас не знаю её актуальность (поддержка новых МК).

Вообще, плагин он же не только для CLC, он для конфигурации всей периферии, плюс еще есть библиотеки (бутлоадер, Ethernet, сенсорные кнопки)

Eddy71

24.07.2016 13:29Спасибо.

Последний раз я правда больше чем пол года назад пробовал свежую версию MPLABX — оставила удручающее впечатление. Очень медленно как-то и дискомфорт от работы. Юзаю до сих пор MPLAB 8.92 и PCWHD под ним. Потому и спросил про отдельную утилиту…

ariz0na

25.07.2016 13:50Попробуйте свежие версии MPLAB X. Читал в конф. что у людей магическим образом ускорилась работа.

dernuss

Интересно. Ждём от конкурентов микрочипа такой же периферии.

pitsakh

Иногда такого не хватало в AVR и STM32, чтобы не усложнять схему дискретной логикой.

Есть ли аналогичный функционал в недорогом сегменте у других производителей микроконтроллеров?

dernuss

С другой стороны довольно редко это надо, а если добавят, то увеличат стоимость микроконтроллеров.

А управлять WS2812b ресурсов хватает и у копеечного stm8.

ariz0na

… еще есть в SAM — М0+ кортексах от Atmel, называется CCL (Configurable Custom Logic), тоже на основе LUT (Lookup Table)

dernuss

выходит только в stm не добавили Custom Logic?

ariz0na

Подобное есть в XMEGA, называется XCL (XMEGA® Custom Logic).

Но оно работает с программируемой таблицей истинности, есть 2(3) входа и 1 выход.

Второй момент, что работает от тактовой частоты.

У PIC логические ячейки асинхронны от ядра и их быстродействие гораздо выше

pitsakh

Я как раз выбираю платформу с низким потреблением в спячке с WDT и остановкой тактирования для пары проектов (avr и stm не устроили) — соответственно между MSP430 и PIC 8 бит.

У MSP из интересного, бросившегося в глаза — WDT не с прескалером степени двойки, а со произвольным счетчиком. Как я понял у PIC такого нет, но выходит, что у PIC во первых есть программируемая логика и во вторых она в power down работает.

Похоже оба варианта надо на али заказывать и играться.

В целом спасибо за статью и комментарии, позволило взглянуть на вопрос под другим углом.

ariz0na

WDT он же для защитных функций и в «нормальной жизни» не должен срабатывать. У PIC Timer1 может работать в Sleep от внутреннего LowPower RC генератора (LPINTOSC), т.е. для такого таймера можно настроить пробуждение с желаемым временем/периодом (в разумных пределах).

pitsakh

Да, задача как раз иногда будить из спячки с отключенным основным генератором, причем с возможностью небольшой подстройки периодичности пробуждения. На AVR и STM выкручивался WDT, но он там в разы прожорливее, чем у PIC и MSP430. За Timer1 спасибо, посмотрю. Может MSP и не нужен будет.

ariz0na

например у PIC16LF1508 типовой ток WDT заявлен 0.44uA при 3.0В. Само ядро в спячке имеет типовой ток 0.025uA

На Таймер 1 в Sleep отдельно ток не прописан, но он работает от того же генератора, что и WDT. Т.е. при выключенном WDT ожидаемо что Таймер 1 потребляет примерно такой же ток.

Т.е. если WDT выключен, то потребление с работающим Таймером 1 должно быть где-то на таком же уровне 0.5мкА.

Если дойдут руки, то сделаю материал на тему микропотребления. У меня получался средний ток потребления приборчика (PIC + датчик температуры + ЖКИ) около 1.3мкА. Это при постоянном отображении данных на ЖКИ, периодическим просыпанием и измерением температуры.

nafikovr

в STM8S есть AWU, в STM8L и STM32 на сколько помню это же реализуется на RTC. это все работает в Halt (Standby) Mode. Честно говоря не знаю какое потребление у пиков в данном режиме (да даже у stm оно имеет неслабый разброс в зависимости от модели), но потребление в Standby мне показалось достаточно низким.

В любом случае WDT предназначен не для этого.

dernuss

микроконтроллеры silabs гляньте. Хорошо спят, у меня получалось 900 нА.

nafikovr

Посмотрите на Cypress PSoC