Вы хотите узнать, как получить работу по проектированию электроники космического корабля? Мне надавно пришло предложение поинтервьироваться на позицию FPGA designer для Blue Origin (см. выше). Лично мне такая позиция не нужна (у меня уже есть позиция ASIC designer-а в другой компании), но я отметил, что технические требования к претендентам в Blue Origin точно совпадают с содержанием семинара для школьников и младших студентов, который пройдет 15-17 сентября на выставке ChipEXPO в Сколково, с поддержкой от РОСНАНО. Хотя разумеется на семинаре мы коснемся технологий Verilog и FPGA только на самом начальном уровне: базовые концепции и простые, но уже интересные, примеры. Чтобы устроится после этого в Blue Origin, вам все-же потребуется несколько лет учебы и работы.

Из-за короновируса семинар будет удаленный, поэтому принять участие смогут не только школьники и студенты Москвы, но и всей России, Украины, Казахстана, Калифорнии и других стран и регионов. Физически проводить лекции и удаленно помогать участникам будут преподаватели и инженеры МИЭТ, ВШЭ МИЭМ, МФТИ, Черниговского Политеха, Самарского университета, IVA Technologies и fpga-systems.ru.

Для участия сначала, еще до семинара, нужно пройти три части теоретического курса от РОСНАНО, под общим названием «Как работают создатели умных наночипов»: «От транзистора до микросхемы», «Логическая сторона цифровой схемотехники», «Физическая сторона цифровой схемотехники». Этот курс необходим, чтобы вы понимали, что вы делаете, по время практического семинара. По получению сертификата окончания теоретического онлайн-курса, вы можете зайти в офис РОСНАНО в Москве и получить бесплатную плату для практического семинара (если они останутся, преимущество имеют школьники). С этой платой вы можете работать дома, до, во время и после семинара в Сколково.

Как получить плату, подготовится к семинару и что на нем будет:

Инструкция как получить плату есть на сайте STEMford. STEMford — это образовательные программы для школьников от eNano, дочернего предприятия Фонда инфраструктурных образовательных программ РОСНАНО. Вот их офис, куда нужно будет зайти:

До практического занития вам нужно будет установить на ваш компьютер среду Intel Quartus Prime Lite Edition. Инструкция как это сделать, есть в бесплатном фрагменте книги «Цифровой синтез: практический курс» под общей редакцией А. Ю. Романова, Ю. В. Панчула. ДМК Пресс, 2020.

Вообще «Цифровой синтез» — полезная книжка для семинара, там описываются упражнения, которые будут с некоторыми вариациями представлены и на семинаре, хотя например вместо учебного процессора schoolMIPS будет использоваться более новомодный schoolRISCV:

В конце книжки Цифровой синтез есть довольно занятное интервью пары молодоженов Владислава и Елены Шаршиных, который вместе с их коллегой Андреем Папушиным компания Intel привезла в Калифорнию за серебряную победу на конкурсе InnovateFPGA:

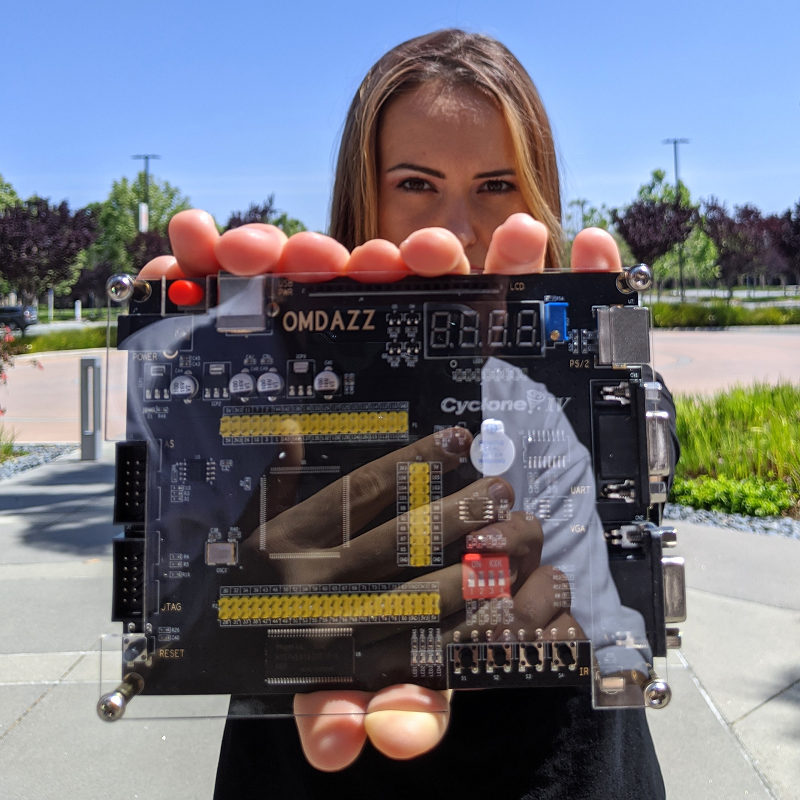

Вот одна из плат, которая будет использоваться на семинаре. Если плат на вас не хватит, или если вы не школьник, вы можете заказать плату на AliExpress и в других местах: 1, 2, 3, 4:

Что будет на семинаре? Вот части программы:

15 сентября. Из чего строится современная цифровая схема.

Модератор дня: Александр Михайлович Силантьев, преподаватель Национального исследовательского университета «Московский институт электронной техники» (МИЭТ).

15.00. Открытие мероприятия, приветствие от организаторов.

15.15-15.30. Мини-лекция: От Клода Шеннона до Apple iPhone: как появилось проектирование цифровых схем и как оно выглядит в современных компаниях.

Юрий Владимирович Панчул, проектировщик сетевых микросхем и микропроцессорных ядер. Саннивейл, Калифорния.

15.30-16.00. Лекция: Комбинационная логика и ее описание на языке Verilog. Теоретический материал переплетается с демонстрацией синтеза для ПЛИС/FPGA в среде Intel Quartus Prime Lite Edition. Александр Михайлович Силантьев.

16.00-16.30. Упражнение с логическими элементами

И/ИЛИ/НЕ/ИСКЛЮЧАЮЩЕЕ-ИЛИ, входы которых подсоединены к кнопкам, а выходы к светодиодам платы c ПЛИС.

16.30-17.00. Упражнение с выводом буквы на семисегментный индикатор.

17.00-17.30. Лекция: Последовательностная логика, которая вводит в схемы память и повторения.

17.30-18.00. Упражнение со сдвиговым регистром.

18.00-19.00. Упражнение для плат ZEOWAA и OMDAZZ с Intel FPGA Cyclone IV: Комбинируем сдвиговый регистр и вывод на семисегментный индикатор буквы: получаем вывод на многоразрядный динамический семисегментный индикатор слова (например имени ученика). Упражнение для платы Terasic DE10-Lite с Intel FPGA MAX10: Комбинируем сдвиговый регистр и вывод букв на статический семисегментный индикатор: получаем вывод бегущей строки (например имени ученика).

19.00-21.00. Дополнительные упражнения и индивидуальные проекты учеников, с помощью от студентов и аспирантов микроэлектроники от участвующих университетов: МИЭТ, ВШЭ МИЭМ, Черниговского НТУ,

Самарского Университета.

Первый день основан на опыте проведения прошлогоднего семинара в Москве, который описан в статье на Хабре:

Второй день основан на опыте проведения летней школы в Зеленограде в прошлом году и семинарах в Самаре:

16 сентября. Приемы и примеры цифрового проектирования на уровне регистровых передач.

Модератор дня: Сергей Анатольевич Иванец, декан факультета электронных и информационных технологий, Черниговский национальный технологический университет, Украина.

15.00-15.15. Мини-лекция: Как из простых схем строить сложные: параллельность, конвейерность и конечные автоматы.

Юрий Владимирович Панчул.

15.15-15.30. Предисловие к примеру игры: рассказ про генерацию графики на VGA.

Сергей Анатольевич Иванец.

15.30-16.00. Упражнение с рисованием на экране разноцветных квадратов и других статических изображений.

16.00-16.30. Презентация примера графической игры с параллельно вычисляемыми спрайтами и конечными автоматами для сценария игры. Демонстрация запуска игры на плате Digilent Basys3 с Xilinx FPGA Artix-7. Обсуждение модификации игры с помощью добавления новых спрайтов и изменения сценария.

Михаил Коробков, fpga-systems.ru.

16.30-17.00. Упражнение с запуском игры на платах ZEOWAA, OMDAZZ и Terasic DE10-Lite.

Сергей Анатольевич Иванец.

17.00-17.30. Лекция: Использование Linear Feedback Shift Registers (LFSR) для передачи данных и генераторов случайных чисел. Сравнение Verilog и VHDL на основе кода LFSR Фибоначчи и Галуа. Демонстрация использования LFSR для генерации изображения на экране VGA движущегося звездного неба из случайных звезд.

Илья Александрович Кудрявцев, декан Факультета электроники и приборостроения Самарского Университета.

17.30-18.00. Упражнение с запуском примера движущегося звездного неба на платах ZEOWAA, OMDAZZ и Terasic DE10-Lite.

Сергей Анатольевич Иванец.

18.00-19.00. Более подробная лекция про моделирование и использование генераторов случайных чисел для глубоко заинтересовавшихся.

Илья Александрович Кудрявцев.

18.00-21.00. Дополнительные упражнения и индивидуальные проекты учеников по изменению игры, в том числе с помощью добавления в нее фона из движущегося звездного неба. С помощью от студентов и аспирантов микроэлектроники от участвующих университетов.

Третий день будет основан на опыте ликбеза по процессорам от Станислава Жельнио и Александра Романова. Только раньше они разработали и использовали учебный процессор schoolMIPS, а теперь мы будем использовать schoolRISCV. Архитектура RISC-V очень похожа на MIPS и другие RISC-архитектуры (SPARC, ARM, POWER итд), но очищена от их костылей, которые имели смысл на простых процессорах, но мешают на сложных (регистровые окна в SPARC, которые обессмысливаются в софтвере с большим стеком; branch delay slots в MIPS до Rev6, которые хороши на простом статическом конвейере с последовательной выборкой инстркций, но превращаются в головную боль в динамическом конвейере итд).

Так как в России есть минимум три компании, которые проектируют процессоры на архитектуре RISC-V, и это хороший кандидат на будущий high-end российский встроеный и может быть даже десктопный и серверный процессор, и так как RISC-V уверенно заменяет MIPS в качестве рабочей лошадки для архитектурного и микроархитектурного экспериментирования в мировых университетах, то школьников лучше учить на нем.

17 сентября. Первый шаг в архитектуру и микроархитектуру современных процессоров.

Модератор дня — Александр Юрьевич Романов, к.т.н., доцент Московского института электроники и математики им. А.Н. Тихонова (МИЭМ), Национальный исследовательский университет «Высшая школа экономики» (НИУ ВШЭ).

15.00-15.15. Мини-лекция: От ENIAC и МЭСМ, через IBM/360 и Cray-1 до Intel, ARM и RISC-V: как появились, эволюционизировали и к чему пришли программируемые процессоры общего назначения.

Юрий Владимирович Панчул.

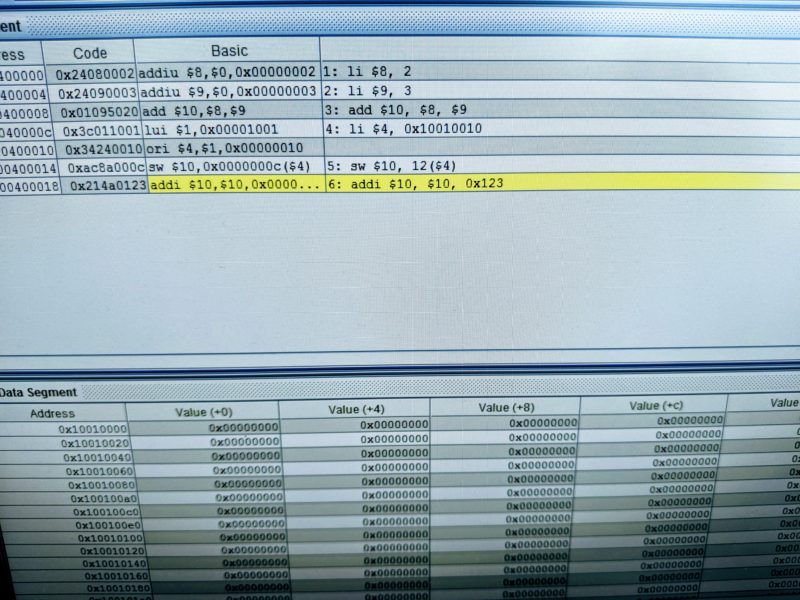

15.15-16.30. Архитектура: вид процессора с точки зрения программиста. Лекция об ассемблере RISC-V с одновременными упражнениями на симуляторе процессора на уровне инструкций.

Никита Поляков, проектировщик микропроцессоров и преподаватель Московского физико-технического института.

16.30-17.30. Микроархитектура: вид процессора с точки зрения схемотехника. Лекция по аппаратной организации процессора schoolRISCV, с вариантами одноцикловой и конвейерной микроархитектуры. Демонстрация синтеза процессора и запуск его на платах.

Станислав Жельнио, разработчик микросхем в IVA Technologies.

17.30-17.30. Упражнение по добавлению в процессор инструкции и верификации с помощью программного теста. Измерение максимальной тактовой частоты получившегося варианта процессора.

Станислав Жельнио.

17.30-18.00. Заключительная лекция: Следущие шаги в освоении проектирования цифровых схем, а также применение этих знаний для проектирования встроенных систем и ускорителей вычислений искуственного интеллекта.

Александр Юрьевич Романов.

18.00-21.00. Дополнительные упражнения и индивидуальные проекты учеников по изменению процессора и интеграции его с периферийными устройствами. С помощью от студентов и аспирантов микроэлектроники от участвующих университетов.

Вот Станислав Жельнио обучает школьников прошлым летом в Зеленограде:

До встречи на семинаре на виртуальном ChipEXPO в Сколково! Мы постараемся провести там часть мероприятия и вживую, силами преподавателей МИЭТ, ВШЭ МИЭМ и МФТИ, но если вирус не позволит, проведем распределенно.

sergey_zorin

Читаю твои статьи, и жалею, что не пошёл в микроэлектронику.

YuriPanchul Автор

Никогда не поздно, я вот в 49 лет на флейте решил научиться играть:

KeisN13

Ну все, отмазаться не получится xD

"16.00-16.30. Презентация примера графической игры с…

Михаил Коробков, fpga-systems.ru."

YuriPanchul Автор

:-)

amartology

Все хорошо в вакансии, кроме строчки про необходимость иметь гражданство США. И это в ней еще самый расслабленный вариант, в компаниях, работающих с госконтрактами (= всех остальных компаниях, занимающихся в США космической электроникой), требования к гражданству и security clearance еще строже.

YuriPanchul Автор

У меня есть знакомый, китаец Джонатан, так вот он ходил несколько месяцев назад интервьироваться в Локхид-Мартин, где делают ракеты. На позицию по SystemVerilog/верификацию/UVM. В свете нынешней анти-китайской истерии это необычно!

amartology

У меня есть знакомый россиянин, который очень хотел найти работу в американской аэроспейс индустрии вообще и в SpaceX в частности, но все, что он получил — несколько отказов в собеседованиях на основании того, что он россиянин, а не американец. И очень много проигнорированных CV.

BlackMokona

Ему требуется получить гражданство США, таковы требования правительства США.

amartology

Да, именно об этом я написал Юрию. Дополнительно наверное было бы интересно проходить проверки для security clearance, если успеть сначала поработать в российском аэроспейсе и, например, иметь в прошлом российскую форму допуска.

Так что завлекалка Юрия очень красивая, но совершенно утопическая.

YuriPanchul Автор

Бывшие россияне есть даже среди менеджеров DARPA, работников Mercury Systems (управляющие компьютеры для боевых вертолетов) и разумеется NASA.

amartology

С одной стороны да, а с другой — они все сначала получили гринкарты, а потом работу в такой отрасли. Да и времена нынче не те же самые что раньше.

Но наверное вы правы, для школьников и младших студентов перспектива уехать в США учиться и потом работать в аэроспейсе гораздо реальнее, чем для действующих специалистов.

YuriPanchul Автор

Я все же надеюсь, что в России увеличится рынок интересных работ (в том числе за счет улучшения образования), и им уезжать не прийдется.

amartology

Тогда и вакансию надо было брать в Элвисе или РКС)

YuriPanchul Автор

Такие вакансии подразумеваются. Согласно принципам зен-буддизма, а также японской эстетики ваби-саби, для совершенства заметки в ней должна быть недоговоренность. Как хлопок одной ладонью.

Pi-man

Извините за дилетантский вопрос: что я потеряю, если куплю вместо DE10-Lite дешевую плату на Cyclone IV? (Ту, что рекомендована в этой статье)

Насколько ее можно будет использовать в семинаре и при изучении книги «Цифровой синтез: практический курс»?

YuriPanchul Автор

Для этих упражнений — никакой разницы, разве что на de10-lite переключатели на ощупь приятнее. Разница появляется на более крупных проектах. Например на de10-lite можно засинтезировать промышленное процессорное ядро, подсоединить его на внешней по отношению к fpga памяти (она есть на плате) и запустить на этом Линукс. А вот на zeowaa и omdazz этого сделать нельзя, потому что 1) процессорное ядро с управлением страницами памяти (фича которая требуется для запуска линукса) на небольшие cyclone iv fpga просто не влезет и 2) памяти, которую можно синтезировать внутри fpga (килобайты) просто не хватит для поднятия линукса (мегабайты).

leniviy_ramvas

Интересненько. Хочу купить бумажную версию вашей книги, а также книги Харрисов, т. к. электронная не так удобна, как по мне, больше первый вариант нравится. Дома лежит одна китайская плис от Gowin, немного уже поковырял ее, но это были простые вещи, при помощи вашей (и не только) книги буду уже делать что-то посложнее. Как хорошо, что в интернете много информации по теме ПЛИС.

KeisN13

На эти книги есть промокод на скидку при покупке книг на сайте издательства.

В описании под этими видео подробнее написано

leniviy_ramvas

Спасибо!

chnav

Я купил бумажную версию. Всё бы хорошо, но «Введение» занимает целых 15 страниц (кто, зачем и почему решил написать книгу, благодарности и пр.), ещё 4 страницы как устанавливать Quartus со скриншотами Лицензионного Соглашения, в котором надо поставить галочку… Вообще очень много полноэкранных скриншотов, с одной стороны получается пошаговое руководство, а с другой — занимают кучу места в книге, только успевай перелистывать страницы. Если честно, я бы предпочел электронную версию.

leniviy_ramvas

Да, этот момент конечно плохой.