Логисторная логика это набор концепций, применение которых может позволить ускорить вычисления, сократить затраты энергии на вычисления и увеличить плотность транзисторов на кристалле без существенного изменения техпроцесса. Она находится в разработке и статья ниже является лишь первичным результатом. Мы надеемся что она вызовет интерес в научных кругах и среди энтузиастов и разработка будет продолжена.

Логисторная логика предполагает:

Параллельно - последовательное , а не последовательное как в CMOS, выполнение операций на уровне логических элементов (альтернатива CMOS)

Не стандартный метод кодирования 0 и 1

Использование Логисторов (тип транзисторов)

Использование двуполярного питания

Использование "grid array" расположения гейтов (вертикально и горизонтально на виде сверху)

В процессорах математические операции описываются логическими схемами, которые представлены последовательным подключением CMOS транзисторных сборок.

Время выполнения этих операций определяется суммой времен выполнения каждой из последовательно подключенных транзисторных CMOS сборок

Чтобы продемонстрировать задержки, возникающие при последовательном подключении CMOS сборок представим симуляцию, выполненную в LTSpice на основе реальных spice моделей 10нм FinFET:

На графике ниже виден исходный сигнал (зеленый) и задержки, возникающие после двух (синий) и после 4-х инверторов (красный)

Предлагается новый тип транзистора - логистор:

В логисторе выходной сигнал (между Source и Drain) "изолирован" от управляющего сигнала - между Gate и Base, соответственно логисторы могут также использоваться вместо оптронов

В comsol semiconductor была произведена симуляция логистора, которая показала возникновение канала между Source и Drain при подаче положительного напряжения на Gate и отрицательного на Base. Ниже показан канал при отсутствии и наличии напряжения между Source и Drain:

Расчетная Вольт-Амперная характеристика логистора:

Благодаря двуполярному питанию, которое будет описано ниже, не требуется обеспечивать полное "запирание" логистора при закороченных Gate и Base, благодаря чему возможен подбор профиля допинга при котором логистор "качественнее" запирается и позволяет пропускать втрое большие токи чем NMOS при прочих равных.

Входные значения в ALU, построенном на базе логисторной логики должны иметь ниже описанный метод кодирования 0 и 1:

Где выходное значение - это напряжение между выходами и землей. Как видно, каждый бит передается по двум проводам.

Единичные логические операции в логисторной логике принципиально описываются следующим образом:

Где "результат" - наличие (1) или отсутствие (0) пути

В логисторной логике логические цепи отличны от CMOS, TTL и других технологий. В случае отсутствия ограничения степени параллельности (в "полной" логисторной логике) цепи строятся таким образом, чтобы при выполнении операции не возникало "to Gate" операций. Другими словами в ALU запрещена подача сигнала с Drain на Gate.

В результате операции выполняются параллельно а не последовательно как у CMOS

Пример построения "полной" логисторной схемы для сумматора двух 4-х битных чисел

A1, A2, A3, A4; B1, B2, B3, B4 - биты первого и второго числа; outputs - результат

Инвертированные входы представлены как проводящие ключи, не инвертированные - не проводящие

В логисторной логике формат выхода не регламентирован и может не совпадать с форматом входа, поэтому правая часть (комплиментарная) не обязательна и приведена для понимания метода составления комплиментарных схем.

В полной логисторной логике каждый выход должен иметь независимую логическую схему.

Ниже представлена симуляция в Logisim без комплиментарной части. справа сверху - стандартная схема сумматора; справа снизу - схема необходимая для построения полных логисторных схем

Далее представлена симуляция логисторного сумматора двух 3-х битных чисел в falstad:

Для подтверждения работоспособности логической части логисторной логики была запроектирована в EasyEDA и изготовлена на JLCPcb плата:

Виду того что логисторы не существуют, были использованы оптроны. Плата работает и выдает ожидаемые значения, что неопровержимо доказывает верность логической части логисторной логики.

Для достижения высокой плотности размещения логисторов рекомендуется объединить Base всех логисторов и разместить Base на обратной стороне Substrate. Gates рекомендуется располагать горизонтально и вертикально. Source и Drain соседних Логисторов необходимо объединять, так что к одному Source / Drain будут присоединяться 4 Gate

Стоит обратить особое внимание на то что в статье описана логисторная логика без ограничения степени параллельности (полная), где степень параллельности - примерное количество Gates которое может запитываться с одного Drain. Для увеличения производительности обязательно использование ограничения степени параллельности. При этом исчезает требование - использовать независимую схему для каждого выходного бита. Использование каскадирования перед логисторной логикой для увеличения токов для насыщения большого количества Gates - является очевидным, но наихудшим решением

По техническим причинам коллектив далее не может продолжать работу над проектом и описать оптимальное решение внедрения ограничения степени параллельности, а также не обладает ресурсами для реализации чипа на базе логисторной логики, поэтому материал передается в доработку научному сообществу и энтузиастам

Разработано в ЛНМО; Авторы: Артем Родичкин, Анна Евсеева, Полина Маслова, Семен Архипов, Инна Миронова, Чечулин Михаил

Комментарии (16)

Flammmable

02.06.2022 12:28+3В книге " Цифровая схемотехника и архитектура компьютера" на стр.99 (стр.155 по pdf) рассказывается про проходной вентиль (аналоговый ключ), который, как говорится на стр.292-293 (стр.348-349 по pdf), применяется в защёлках/триггерах с целью сократить количество используемых транзисторов (по сравнению с защёлками/триггерами целиком состоящих из логических элементов).

Правильно ли я понимаю, что вы предлагаете, по сути, сделать всю логику на аналоговых ключах, а не только отдельные блоки?

И ещё. Чем отличается логистрон отличается от полевого транзистора с подложкой, выведенной на отдельный пин (MIC94030, к примеру)?

mozg4d Автор

02.06.2022 20:18+1Фактически да. Опишем на примере: допустим в логической схеме есть 2 элемента "И" выход первого элемента идет на один из входов второго. Можно пойти стандартным путем и собрать CMOS с 2-мя элементами "И", или можно "скомбинировать" их в 1 элемент "И" с тремя входами. Второй вариант требует меньше транзисторов, имеет меньшее энергопотребление и быстрее. Такой подход иногда используют в частных случаях. Логистронная логика "комбинирует" всю логическую цепь и это не частное а общее решение для любой логической цепи. Добавим к этому двуполярное питание, не обязательную комплиментарную часть и логистроны и будет "полная" логистронная логика. К сожалению это только часть решения которое не дает всей производительности на которую способна логистронная логика. Вторая часть - "ограничение степени параллельности" То-есть не вся схема "комбинируется" а частями и происходить это должно "по умному". Эта часть не описана и даже не придумана.

Что касается отличия логистрона от 4-х пинового транзистора N типа, то у последнего на базе - P+, а у логистрона - N, что мешает течь току между source и base вне зависимости от направления. Простые логические схемы возможно реализовать в логистронной логике без применения логистронов, используя обычные NMOS

И да, надо было назвать их логистронами, но уже поздно)

Flammmable

03.06.2022 09:58Во-первых. Ток через затвор 4-пинового полевого транзистора не течёт потому, что между контактом затвора и P находится диэлектрик. А через контакт подложки он способен течь потому, что этот контакт непосредственно примыкает к зоне P. Вы предлагаете сделать дополнительную зону N, но почему бы там не сделать тот же диэлектрик - как под затвором? Я не проверял, но не исключаю на 100%, что подобную конфигурацию можно сделать из готового 4-пинового полевого транзистора и конденсатора, установленного последовательно на контакте подложки.

Во-вторых. Вот здесь есть несколько абзацев про transmission gate (они же pass gate, они же аналоговые ключи). Они состоят из двух полевых транзисторов с выделенными пинами подложки и делают именно то, что и логистор.

Я понимаю, что это школьный проект и умение работать в соответствующих пакетах впечатляет. Однако по поводу непосредственно логисторной логики есть сомнения. С одной стороны промышленность и так способна создавать аналоговые ключи без некоего нового типа транзистора. С другой стороны, как указано выше, эти ключи и так эффективно применяются при создании защёлок и регистров в серийных цифровых микросхемах. Возникает закономерный вопрос, почему Texas Instruments, Intel, Microchip, Xilinx и прочие, ограниченно применяя аналоговые ключи не пошли дальше и не сделали на их основе вообще всю логику?

Думаю, проблема в следующем. Если я правильно понял ваш график, то при напряжениях на затворе и на стоке(?) по 1В, ток через транзистор составит чуть менее, чем 1мА. То есть сопротивление будет равно 1000 Ом. Но даже если мы возьмём, к примеру, полевой транзистор 2N7002K, то при напряжении 3В на затворе и 3В на стоке, ток сток-исток будет равен приблизительно 0,3А. То есть сопротивление канала будет равно 10 Омам. Восемь аналоговых реле (о которых говорят в комментариях ниже) с таким сопротивлением перехода дадут 80 Ом (чисто арифметически, понятно из-за нелинейности ВАХ "сток-исток" результат будет иной) - это, так скажем, весьма много. На выходе же блоков, созданных из обычных полевых транзисторов в большинстве случаев стоит инвертор, который предоставляет, скажем так, "свежее" напряжение, прошедшее только через один транзистор. Соответственно, из блоков обычной логики можно построить сколь угодно длинную цепочку, проводящую сигнал, которая будет работать исправно и закономерно (сопротивление её выхода не будет определяться её длиной). А из аналоговых реле - нет.

mozg4d Автор

03.06.2022 15:06Да, мы даже обсуждали такой вариант, вроде он не плох. Больше по нему можно сказать если произвести симуляцию в Comsol или visalTCAD (попробовать дают на месяц, мы не успели собрать в нем симуляцию), а в случае с отдельным конденсатором - в LTspice

Да, только больше/сложнее

График вольт амперной характеристики для транзистора с 5нм feature size, поэтому токи такие "маленькие". Меньше размеры - меньше гейты - меньше емкость гейтов, меньше требуются токи, это компенсирует большее сопротивление

Да, действительно, фишка CMOS - "свежее" напряжение после каждого блока, или высокая шумозащищенность. Существует предел размера схемы который можно "отлогисторить", выше которого шумы станут неприемлемые. Предполагаю этот предел выше размеров схем определяемых оптимальной степенью параллельности, которая оценочно около 4-х. Но это лишь предположение, исследований на эту тему не производилось, так же как и не определена оптимальная степень параллельности. Теоретически такие исследование возможно произвести используя доступный простым смертным cadence virtuoso

Flammmable

03.06.2022 15:52Да, мы даже обсуждали такой вариант, вроде он не плох

Более того! Есть ряд статей, описывающих Double-Gate MOSFET, где затворы расположены на противоположных от канала слоях (например, вот здесь более обзорно, а здесь более научно) .

Да, только больше/сложнее

Я несколько ошибся. По ссылке приведена схема аналогового ключа не с двумя 4-пиновыми транзисторами, а с двумя обычными MOSFET. Как я понял, вы предлагаете новый тип транзистора, который, по вашему мнению, в одиночку представляет из себя аналоговый ключ, так?

Вопрос, собственно, почему, на ваш взгляд, гранды полупроводниковой промышленности активно разрабатывая и производя MOS-структуры и будучи, весьма вероятно, в курсе работ по DG-MOSFET, а также активно используя аналоговые ключи в цифровых микросхемах в отдельных блоках не перешли целиком на логисторную логику?

Моё предположение заключается в том, что MOS-структуры с выводами на одной стороне (то есть обычные MOSFET) значительно дешевле в производстве, чем те же DG-MOSFET. И хотя формально, в одном случае на аналоговый ключ идёт два транзистора, а во втором - как знать - может удастся обойтись и одним, но стоимость этого одного транзистора будет выше чем у двух, а характеристики - хуже.

mozg4d Автор

03.06.2022 16:19Да, так.

В какой-то мере, в некоторых частных случаях, комбинируют логические элементы. Я не вижу причин по которым не перешли полностью на логисторную логику, но это не значит кто их нет.

Может тут объяснение не техническое, а в области психологии, например - "работает - не трогай", или "100% об этом думали и не используют, значит наверняка что-то не так"

А может просто не догадались. Решение очевидное после того как его увидишь

Логисторную логику можно делать и односторонней. Двусторонней ее рекомендуется делать только для увеличения плотности

Flammmable

03.06.2022 12:25Благодаря двуполярному питанию, которое будет описано ниже, не требуется обеспечивать полное "запирание" логистора при закороченных Gate и Base

Не совсем понял эту фразу, но в словосочетании про "неполное запирание" есть сходство с CML. Это когда два транзистора держатся приоткрытыми, а дифференциальным сигналом слегка закрывают один и приоткрывают ещё сильнее другой (либо наоборот), причём из этой пары транзисторов сигнал также будет выходить дифференциальный. На основе подобных пар, к примеру, Onsemi делает широкую номенклатуру логических элементов, работающих на бешенной частоте. Вот XOR (исключающее ИЛИ) MC100EP08, способный работать на 3ГГц. А у Analog Devices есть HMC721LP3E, XOR на CML, который работает на 13ГГц!

Разумеется, есть и проблема. CML жрёт ток как не в себя и дичайше греется. Поэтому процессор из него - так себе идея.

mozg4d Автор

03.06.2022 15:41Эта фраза не простая) Если не знать как устроен CMOS, то логично было бы предположить что NMOS транзисторы в нем открываются (превращаются в проводники) при подаче положительного напряжения на гейт и отрицательного на base, а запираются (превращаются в изоляторы) при подаче отрицательного напряжения на gate и положительного на base, но это не то что происходит.

В однополярном CMOS, NMOS запираются закорачиванием Gate и Base. В запертом состоянии они в идеале не должны пропускать ток, т.к. Если они будут его пропускать, то копмлиментарная и не комплиментарная части CMOS будут коротить. Чем хуже NMOS запирают, тем большие токи будут идти между комплементарной и не комплиментарной частью CMOS, и соответственно тем больше тепла будет выделяться / энергии потребляться. Соответственно необходимо подбирать такие профили допингов при которых обеспечивается достаточно качественное запирание.

Для обеспечения бошьших токов необходимы большие допинги, что при мелких размерах негативно влияет (в сторону увеличения) на проводимость канала при закороченном gate и base (в соответствии с тем что мы видели в comsol)

При использовании двуполярного питания, запирание происходит подачей отрицательного напряжения на gate и положительного на base. Можно в зависимости от техпроцесса и пр. условий подбирать уровни напряжений и профили допингов для обеспечения более оптимальных параметров. Мы увидели существенное улучшение параметров логистора при использовании двуполярного питания. Использование двуполярного питания также требует дополнительного исследования, в том числе в смысле влияния его на туннелирование

VertiBird

02.06.2022 12:41+4На одном из рисунков я насчитал 8 последовательных логисторов от входа до выхода, какое будет падение напряжения на выходе?

Есть какие-то оценки частоты с которой может работать такая схема и ее сравнение с аналогичной КМОП?

mozg4d Автор

02.06.2022 19:45+1Возможно предполагается что 8 последовательно подключенных логистора эквиваленты 8 последовательным диодам в смысле падения напряжения - примерно по .6 вольт на каждом, но в данном случае, если на гейты всех логисторов будет подано положительное напряжение то произойдет инвертирование поверхностного слоя, он станет "N", соответственно не будет depletion regions на пути от source первого логистора до drain последнего и не будет связанного с этим падения напряжения, фактически образуется единый проводящий канал с переменным сопротивлением, зависящим от количества и мобильности зарядов канала.

Taus

02.06.2022 17:15+3Предложенный тип транзистора схематически похож на много где используемые IGBT. Чем ваш вариант транзистора отличается от IGBT?

mozg4d Автор

02.06.2022 20:22+2Логистрон наиболее похож на NMOS. Единственное отличие в случае NLOG (логистрона N типа) - контакт идущий к базе идет не через P+, а через N или N+

Timka21213

03.06.2022 01:21+2Эта работа выполнена в школьном КБ и была впервые представлена на Балтийском научно-инженерном конкурсе baltkonkurs.ru

amartology

04.06.2022 16:33+3Проведенную работу стоит рассмотреть в двух отдельных частях: приборной и схемотехнической.

Приборная часть

Aвторы изобрели способ сделать из МОП-транзистора проходной ключ (“pass gate”). Необходимым условием работы МОП-транзистора является то, что стоковый pn-переход не должен быть прямо смещен. Соответственно, напряжение в p-легированной области n-канального транзистора не должно быть существенно выше, чем напряжение на стоке. Или, в случае с проходным ключом, не должно быть существенно выше, чем более низкое из напряжений на стоке и истоке. Соблюдение этого условия обеспечивает способность транзисторного ключа запираться в обоих направлениях.

Стоит заметить, что “p-легированная область n-канального транзистора” не имеет собственного названия в русском языке (и имеет собственное название “body” в английском языке), однако состояние этой области является важным для понимания работы транзистора в большинстве рабочих режимов. Пренебрежение значением этой области и распространенное заблуждение, что у МОП-транзистора три, а не четыре вывода - это колоссальная проблема русскоязычной научно-технической школы микроэлектроники.

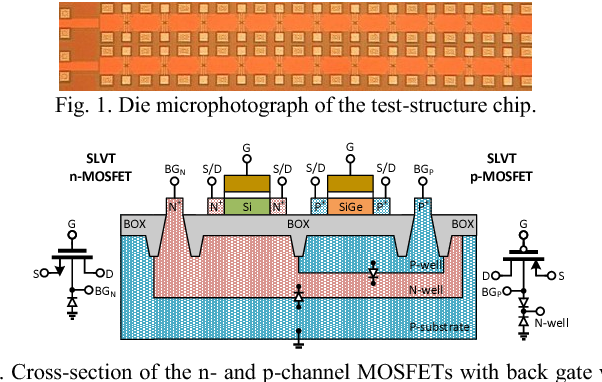

Авторы предлагают для обеспечения контроля потенциала в области “тела” транзистора применять непрямое управление через прямо смещенный диод. Эта мера работоспособна, однако потенциалом “тела” можно управлять и напрямую, подключив к нему источник напряжения (как это делается в интегральных МОП-транзисторах) или обеспечив полное обеднение этой области и используя второй затвор. Второй вариант реализован в технологии FDSOI с помощью второго затвора снизу.

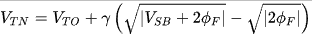

Разрез инвертора в FDSOI, с показанными возможностями управления областями body обоих транзисторов. Изменение потенциала “тела” транзистора приводит к модуляции порогового напряжения (так называемый “body effect”), которая считается по формуле:

Где Vt0 - порог без модуляции, Vtn - порог с модуляцией, Vsb - разница потенциалов между истоком и body.

На рисунке показаны ВАХ МОПТ с двумя вариантами смещения на body - прямой подачей напряжения (красные линии) и через предлагаемый авторами диод (зеленые линии). Видно, что прямая подача смещения позволяет модулировать пороговое напряжение в более широком диапазоне.

Логическая часть

Логика на проходных ключах действительно работоспособна и, более того, широко применяется в серийных микросхемах. Основным недостатком, не учтенным авторами, является то, что одиночный транзистор в качестве ключа не способен пропустить напряжение, более высокое, чем Vdd-Vth, вследствие чего становится невозможным напрямую подавать выход такого логического вентиля как вход следующего вентиля (потому что его выход составит Vdd/2*Vth).

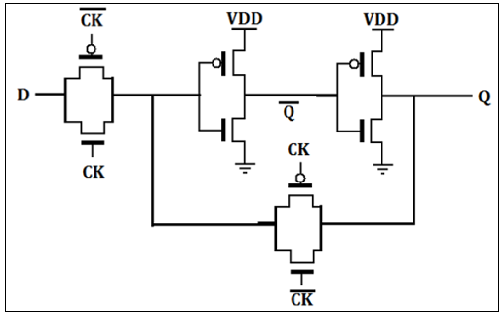

Пример симуляции проходного ключа. Видно, что напряжение на выходе ниже напряжения на входе Для преодоления этого недостатка в реальных схемах используются или проходные ключи в сочетании или с подтягивающими напряжение вверх буферами, или комплементарные проходные ключи из двух параллельно включенных транзисторов, n- и p-типа. Хорошие примеры использования проходных ключей - простой D-триггер и LUT в FPGA.

D-latch с двумя комплементарными проходными ключами

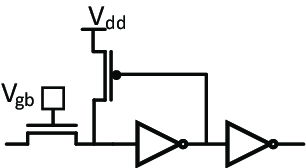

Проходной ключ с подтягивающим буфером (pmos должен быть длинноканальным, чтобы обеспечивать только достаточно маленький ток и не мешать переходу 1->0)

LUT в FPGA, выполненный на проходных ключах. Еще одна задача, в которой в промышленности широко применяется сочетание статической КМОП-логики с логикой на проходных ключах - это сумматоры, и представленный в статье образец сумматора достаточно похож на реальные схемы, применяемые в серийных микросхемах.

В целом хочется отметить, что логика на проходных ключах действительно работает и широко применяется, пусть и в сочетании с другими видами логики. Авторы статьи, самостоятельно придумавшие очень схожие с промышленными решения, большие молодцы.

dvserg

Было бы интересно Ваши наработки продвинуть в сторону оптических процессоров. Если удасться реализовать в кристалле управляемые

оптическиеЭМ каналы с вашей логикой - это будет следующий "большой шаг для человечества".Ну это так, идеи вслух.

Спасибо, очень интересно.