Судя по всему, процессоры на одном кристалле достигли своего предела. Законы физики и математики не позволяют дальше уменьшать транзисторы. Но это не значит, что развитие электроники остановится, а закону Мура конец. Ничего подобного.

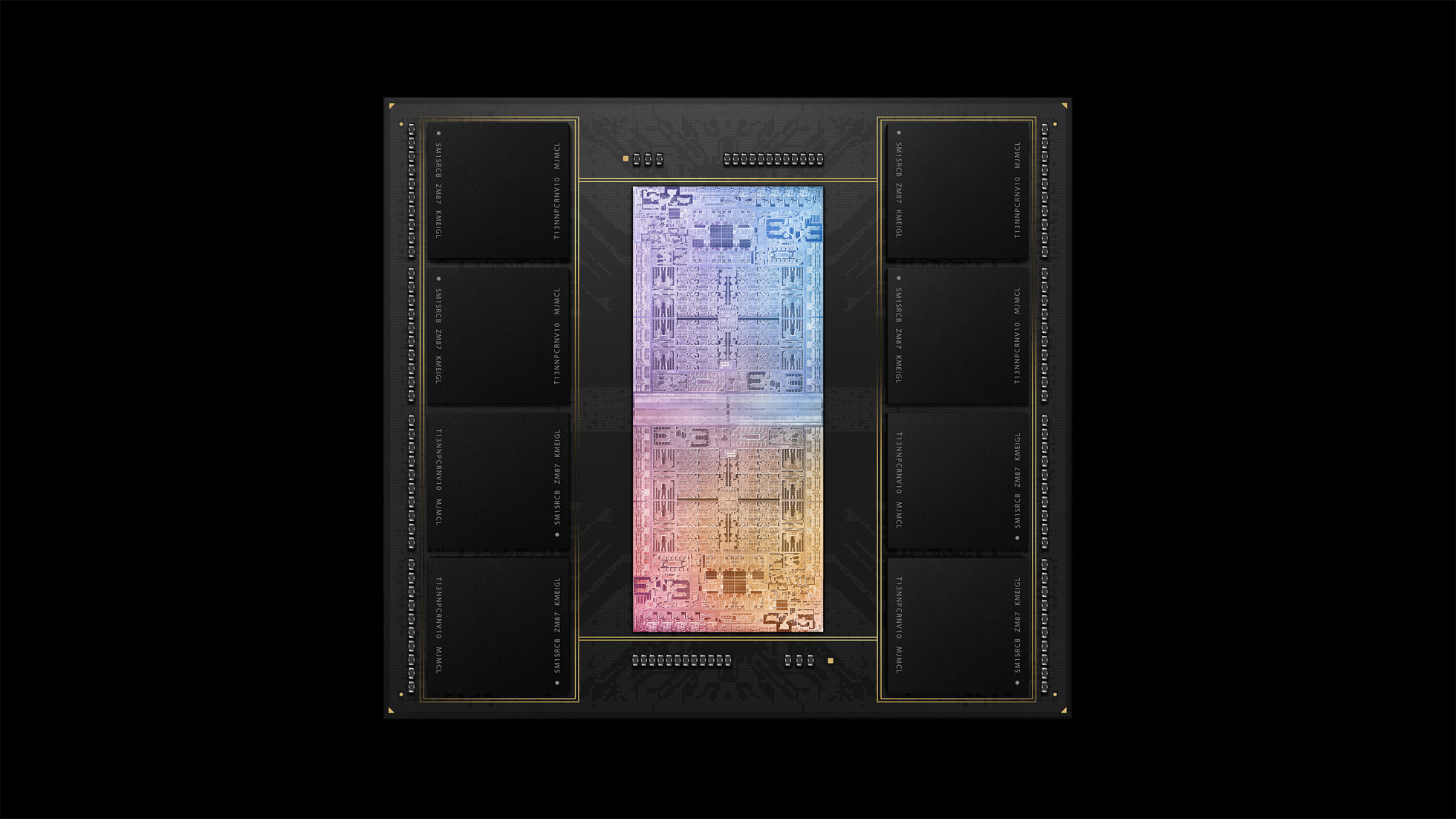

Последние новинки AMD, Apple и Nvidia показывают, что будущее CPU — за чиплетами, которые «склеиваются» из нескольких кристаллов. Например, новый процессор Apple M1 Ultra физически состоит из двух чипов (на фото вверху). То же самое мы видим в суперчипе Nvidia Grace CPU. Хотя и нацеленные на абсолютно разные рынки, но это вестники наступающего будущего.

▍ Чиплеты

Чиплет Nvidia Grace CPU — первый CPU, разработанный Nvidia для дата-центров. Он состоит из двух процессоров, соединённых высокоскоростной шиной NVLink-C2C.

Nvidia Grace CPU

По мнению инженеров IEEE Spectrum, межпроцессорный интерконнект является тем бутылочным горлышком, который будет определять максимальную производительность чиплетов. Можно почти до бесконечности масштабировать производительность, соединяя друг с другом большое количество вычислительных ядер или целых CPU, если решить проблему эффективного интерконнекта, а также распараллеливания задач и теплоотвода.

Соединение микросхем в чиплеты — не новая идея, но она получила широкое распространение в последние пять лет. Наверное, главным проповедником этой философии стала компания AMD, которая убедительно доказала её эффективность в конструкции процессоров Epyc и Ryzen. Потом её примеру последовали Apple, Nvidia и Intel.

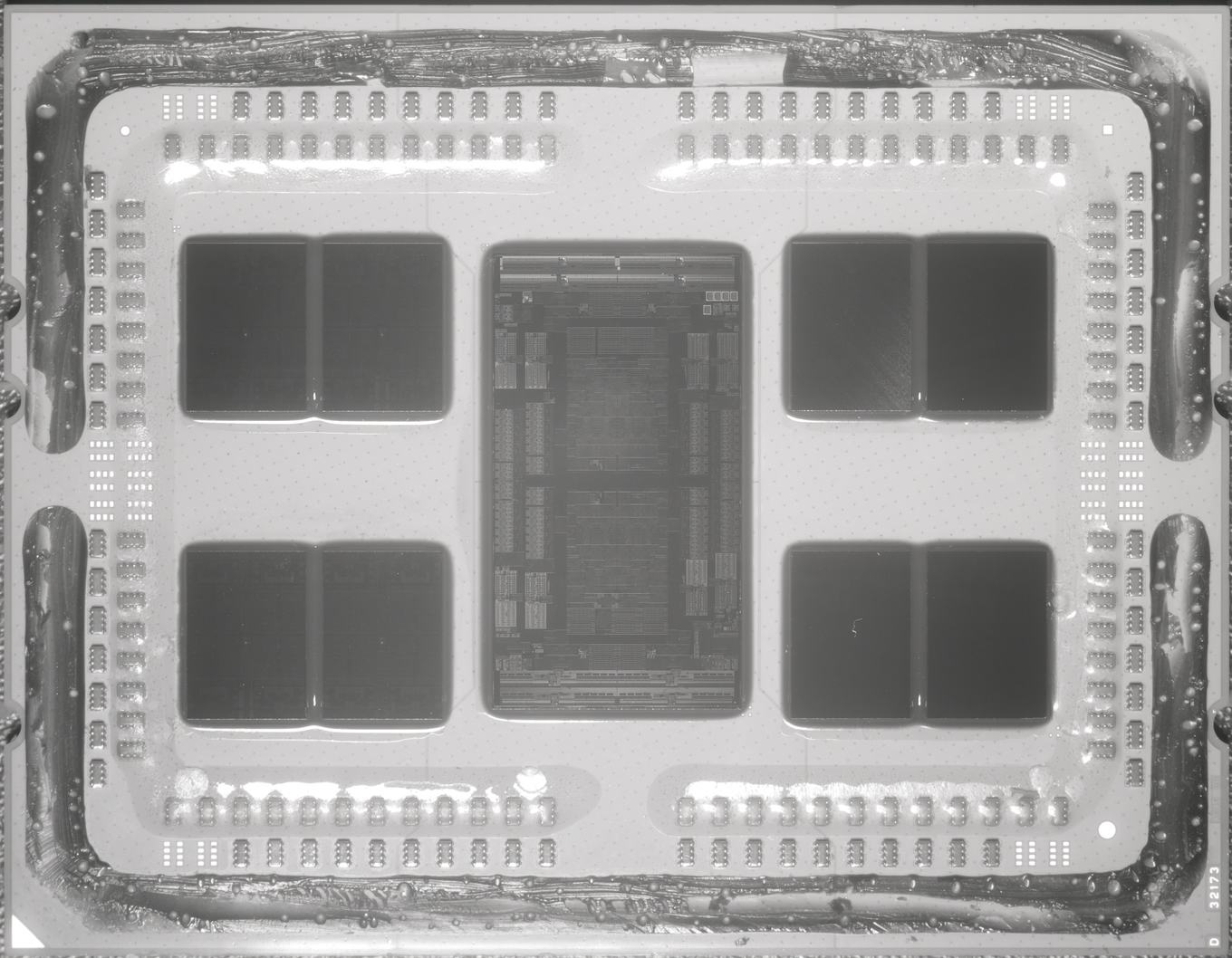

Что это даёт всей отрасли в целом? Самое главное, что таким образом мы гарантируем дальнейший экспоненциальный рост вычислений. Хотя миниатюризация транзисторов замедлилась, но количество транзисторов в новых процессорах растёт прежними темпами. В частности, в Apple M1 Ultra насчитывается 114 млрд транзисторов на рабочей области чиплета 860 мм², в то время как у чипа прошлого поколения M1 Max рабочая площадь равнялась 432 мм², и количество транзисторов было примерно вдвое меньше. На новом Nvidia Hopper H100 GPU (представлен одновременно с Nvidia Grace CPU— около 80 млрд транзисторов. Для сравнения, на флагманском 64-ядерном чиплете EPYC Rome образца 2019 года «всего лишь» 39,54 млрд транзисторов на площади 1008 мм².

64-ядерный чиплет EPYC Rome. Фото: HardwareLuxx

Как видим, закон Мура в силе, прогресс не останавливается. Производительность по-прежнему растёт в геометрической прогрессии, если считать и по количеству транзисторов на чиплете, и по стоимости вычислений, и по производительности на ватт.

В целом, переход на многочиповым модулям и чиплетам позволил производителям обеспечить лучшую энергоэффективность и производительность по сравнению с монолитными конструкциями, поскольку размер микросхем увеличивается, а процент брака неизбежно растёт.

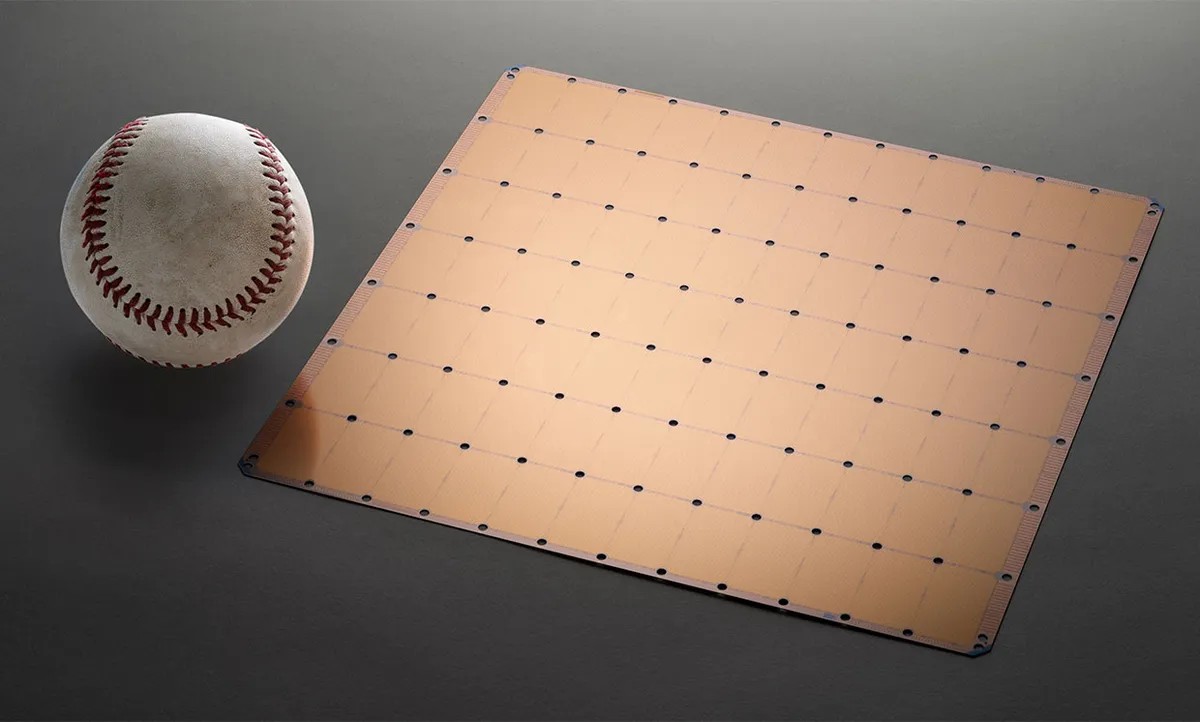

Если не считать Cerebras, которая пытается изготовить микросхемы размером с целую пластину, вся остальная индустрия вроде бы согласна с переходом на чиплеты, отказываясь от монолитного дизайна.

Cerebras, «самый большой в мире процессор»

Переход на чиплеты идёт при поддержке производителей. Например, TSMC предлагает продвинутую упаковку и корпусировку под названием 3DFabric, которую использует AMD в некоторых моделях процессоров Epyc и Ryzen и Apple в процессорах M1 Ultra.

▍ Новое поколение серверных ARM

За последние несколько лет накатило две волны серверных ARM-процессоров. Нельзя сказать, что эти модели произвели настоящую революцию на рынке и на голову разбили x86 по производительности. К сожалению, такого не произошло.

Первая волна процессоров от Calxeda, Applied Micro, AMD, Marvell, Nvidia и Samsung оказалась не очень убедительной. Вторая волна с Broadcom, Cavium, Qualcomm и Nuvia — тоже разочаровала.

Зато прямо сейчас на рынок накатывает третья волна серверных чипов ARM, которая может всё изменить. Речь идёт об Arm Neoverse.

Процессоры на новой архитектуре в сотрудничестве с Arm разрабатывает группа игроков, включая облачные компании (Amazon Web Services, Microsoft, Google, Alibaba и Tencent), а также несколько независимых разработчиков чипов (Ampere Computing, HiSilicon, Nvidia и SiPearl). Судя по всему, их планы могут повлиять на мировой рынок серверов, сама Arm Ltd. в этой связи даже собирается выйти на биржу.

В октябре 2018 года Arm Ltd. приняла решение разделить архитектуру серверных и клиентских CPU. Тогда и началась разработка с нуля платформы Neoverse, специально предназначенной для серверных задач. Серверный процессор — это высокая производительность, кэш L2 большего размера и быстрый интерконнект для соединения ядер и отдельных микросхем в чиплете.

При этом Arm Ltd. продаёт лицензии на архитектуру ARM, что позволяет клиентам создавать пользовательские ядра, производные от Neoverse.

В то время при создании эталонных платформ компания взяла обязательство выпускать новую серверную платформу каждый год и обеспечивать прирост производительности на 30% в каждом поколении.

В сентябре 2020 года дорожную карту Arm дополнила V-серия (кодовое название Zeus, с акцентом на вычисления с плавающей запятой), N-серия (высокая производительность целочисленных вычислений) и E-серия (энергоэффективность). В апреле 2021 года Arm Ltd. раскрыла некоторые подробности о трёх семействах серверных процессоров, в том числе на ядрах Neoverse V1 (Zeus) и N2 (Perseus).

И это не просто теоретические выкладки. Уже идёт проектирование реальных вычислительных систем на новых процессорах.

▍ Суперкомпьютер на процессорах Neoverse V1

Среди новых игроков на рынке ARM необычно выглядит European Processor Initiative — общеевропейская инициатива по разработке 29-ядерного ARM-процессора и суперкомпьютера на его основе. Довольно любопытно, что такие исследования идут не только среди коммерческих, но и практически на государственном уровне, то есть с государственной поддержкой. Проект объединяет 28 участников из 10 стран, а ведущим разработчиком выступает вышеупомянутая компания SiPearl, получившая грант Евросоюза на разработку. Разработчики уже успешно разработали «виртуальный прототип» процессора на архитектуре Neoverse V1 (Zeus) для высокопроизводительных ARM-процессоров (серверы, дата-центры).

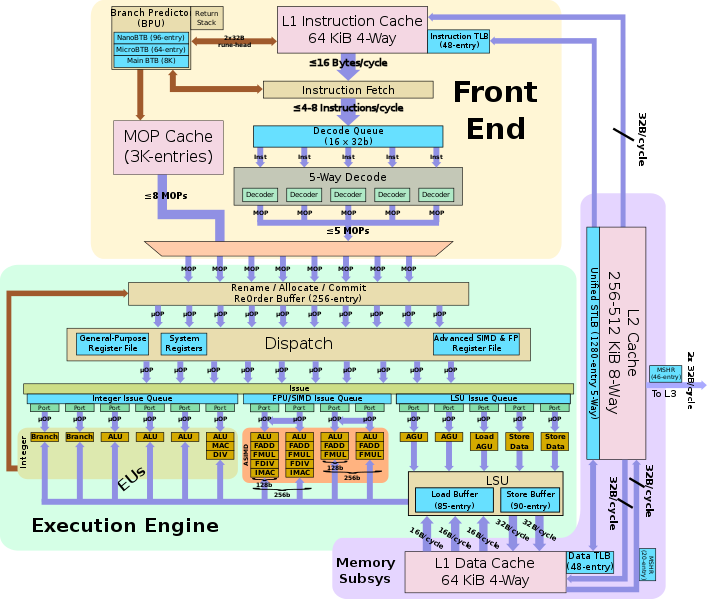

Пример архитектуры системы-на-чипе (SoC) ARM Neoverse V1, источник

Отдельное ядро Neoverse V1, источник

Это лишь один из примеров внедрения новых серверных ARM.

Дальше — больше. Появляется всё больше свидетельств, что разработки Arm Ltd. найдут применение в реальных дата-центрах. По крайней мере, сама компания в этом уже не сомневается — и поэтому дополнила дорожную карту Neoverse ещё несколькими вариантами ядер и официально объявила, что в разработке находятся последующие поколения.

Вот как сейчас выглядит актуальный план архитектуры Neoverse до 2023 года:

На каждой иллюстрации указан интерконнект CMN (Coherent Mesh Network), связывающий ядра и кэши L2.

Например, платформа V2 (Demeter) обладает следующими характеристиками:

- архитектура Armv9-A;

- память DDR5 (и LPDDR5);

- шина PCI-Express 5.0;

- протокол когерентной памяти CXL 2.0 для ускорителей (позволяет объединять память в пулы между серверами);

- векторная математика второго поколения Scalable Vector Extension (SVE2) из четырёх 128-битных векторов, поддерживает числа INT8 и BF16, вдобавок к стандартным числам с плавающей запятой одинарной точности FP32 и двойной точности FP64;

- адресация до 256 ТБ физической памяти.

Вопрос в том, кто первый сделает серверные ARM-процессоры на ядре V2 с поддержкой SVE2. Есть предположения, что это будет Nvidia или Amazon (c чипом Graviton4). Но рано или поздно серверные ARM появятся и на массовом рынке.

Ну, а уже в следующем году ожидается выпуск новой архитектуры Poseidon (V3) с поддержкой PCI-Express 6.0 и протокола CXL 3.0, что позволяет совместное использование памяти всеми процессорами, которые связаны коммутацией PCI-Express.

▍ Будущее микроэлектроники

C 80-х годов индустрия микроэлектроники представила множество инноваций, включая концепцию GPGPU, многопоточность, параллельные вычисления, продвинутое управление питанием, SIMD, NUMA, виртуализацию, предсказание ветвлений и т. д.

Будущее развитие процессоров связано с тем, что всё больше вычислений переходит в дата-центры. Отсюда и специализированное железо, и попытки довести среднюю утилизацию серверов до 90%. Уже есть первые попытки реализовать транзакционную память типа Hardware Lock Elision (HLE).

Можно ожидать появления более продвинутых интерконнектов между модулями в чиплете. Для унификации таких межсоединений создан отраслевой альянс Universal Chiplet Interconnection Express (UCIe). Предполагается, что в будущем производители получат возможность конструировать чиплеты из «универсальных» компонентов от разных поставщиков, и эти модули будут совместимы друг с другом.

Вот примеры корпусировки UCIe 2.D и 3D, по сравнению со стандартной упаковкой:

К сожалению, не все производители заинтересованы во вступлении в альянс. В частности, та же Nvidia ещё не вступила в него, а продвигает собственный стандарт интерконнекта NVLink-C2C, упомянутый выше.

Параллельно идёт разработка специализированных устройств для выполнения конкретных задач в дата-центрах: Microsoft разработала проприетарные FPGA для своих дата-центров Azure. Или специализированные ASIC для биохимических вычислений (ускорение расчётов в 100–1000 раз по сравнению с обычными GPU). Создаются и другие специализированные микросхемы для AI/ML и прочих вычислений.

Компания Intel развивается немного в стороне от всей индустрии (со своими техпроцессами и собственными фабриками). Но она тоже заверяет, что закон Мура сохраняет свою актуальность. Вот слайд с их презентации на последней конференции Hot Chips:

Если вкратце, будущее — за чиплетами и SOP (system on package). С их помощью закон Мура продолжает действие. Если всё пойдёт нормально, то к 2030 году мы увидим 1 триллион транзисторов в чиплете из нескольких микросхем.

RUVDS | Community в telegram и уютный чат

Комментарии (17)

phenik

10.10.2022 12:59+4Законы физики и математики не позволяют дальше уменьшать транзисторы.

Законы физики могут ограничивать, а как математики? S --> 0, где S — размер транзистора, интеграция 1/S --> ∞, какие тут могут возникнуть математические ограничения?

potan

10.10.2022 17:43Чиплеты могут в одном корпусе разместить и процессор, и приличный объем ОЗУ?

CrashLogger

10.10.2022 18:37+1В Raspberry Pi 3 гигабайт оперативки вместе с процессором в одном корпусе

Un_ka

10.10.2022 19:48+1А разве там не один чип припаян поверх другого? Эта технология называется PoP.

Arlekcangp

11.10.2022 10:29+2Ну ладно чипов с транзисторами напихают в корпус, а охлаждать их как ? С таким же успехом можно делать чип в несколько "этажей". Только эти "пирожки" будут сильно горячими. Уже сейчас 4000-я линейка GPU у NVIDIA потребляет какие-то мощности, сравнимые с чайником... C таким "прогрессом" в скором времени большую часть серверной стойки будет занимать криогенная система... Количество элементов в чипах можно наращивать, но для этого нужно уменьшить их потребление. А как это сделать не уменьшая их размеры ? Тут нужна новая элементная база (что-нибудь квантовое или оптическое)

А второй момент - это взаимодействие с памятью. Тут скажем кратко: классическая фон неймановская модель не вывезет. Память нужно пристыковать к самим вычислительным ядрам и всё это дело соединять быстрым и "толстым" интерконектом. Опять же нынешние способы не годятся, потому что слойность мат. плат до предела уже и так увеличена. Тут вижу замену только в оптике. Оптические трансиверы должны быть прямо к кристаллах CPU. Тем более что разработки были в этом направлении.

Что из этого могут предложить новые серверные CPU на ARM ? Ответ очевиден - ничего. Это пока что всего лишь разборки за кусок уже существующего рынка. Подсократить конкурентов, что бы влезть самим.

vadimbudnyaev

11.10.2022 10:35Одновременно опубликовали похожие мысли:) Только вот в одном кристалле "цифру" и фотонику вряд ли будут делать, т.к. для оптических трансиверов и волноводов не нужны тонкие техпроцессы и это экономически неэффективно. Уже были попытки сделать электронно-фотонные СнК, но то были 45/65/90 нм. Когда цифра изготавливается по нормам 3/5/7 нм, фотонные блоки становятся слишком дорогими.

Brak0del

11.10.2022 11:46+1Ну ладно чипов с транзисторами напихают в корпус, а охлаждать их как ? С таким же успехом можно делать чип в несколько "этажей". Только эти "пирожки" будут сильно горячими.

TSMC предлагали перемежать слои горячей логики холодными слоями Flash-памяти, например так:

Brak0del

11.10.2022 11:50А второй момент - это взаимодействие с памятью. Тут скажем кратко: классическая фон неймановская модель не вывезет. Память нужно пристыковать к самим вычислительным ядрам и всё это дело соединять быстрым и "толстым" интерконектом. Опять же нынешние способы не годятся,

Так-то уже лет 10 существует HBM, это уже давно нынешний способ и она примерно достигает того, что требуете, правда чутка дороговата.

vadimbudnyaev

11.10.2022 10:29Позволю себе понудить. Вроде слово "межсоединения" - вполне точный перевод interconnections. Почему его не использовать?

А если по теме, то мне представляется, что будущее чиплетов - это объединение микроэлектроники и фотоники в одном корпусе. Оптические межсоединения позволяют преодолеть основное узкое место такой "склейки" из нескольких кристаллов - пропускную способность. Кремниевая фотоника - это уже давно реальность, но именно в будущих чиплетах она может раскрыться по полной.

Brak0del

11.10.2022 11:39Microsoft разработала проприетарные FPGA для своих дата-центров Azure

Это не так. Microsoft не разрабатывала своих FPGA. Microsoft разработала для своих дата-центров Azure обычную плату-ускоритель (таких сейчас десятки), на которой стоит обычная плис от Intel (позже они перешли на Xilinx), а также есть пару сетевых интерфейсов, DDR, PCI-express. Кроме того, Microsoft разработала хороший слой софта над этими ускорителями, который может распределять задачи между ними, работая как с единой сетью, управлять коммуникацией, реконфигурацией, распределять нагрузку и т.д.

vadimr

Идея микросборок не нова, но это тактическое решение, связанное с временными технологическими трудностями. В прошлый раз это было во времена Pentium II под Slot 1.

aMster1