Все знают про язык программирования C, поменьше — про язык программирования F, кое‑кто про B, предшественник C, а вот знаете ли вы про язык «e»? Их кстати два — один с большой буквы «E», а другой с маленькой «e».

Вы наверное подумали, что это еще один безызвестный язык от какого‑нибудь аспиранта провинциального европейского университета. Однако интерпретатор маленького «e» под названием Specman продали в 2005 году большой компании Cadence Design Systems за $315 милионов долларов. Причем президента продающей компании Verisity звали Гаврилов. Также можно нагуглить, что этот язык использовали внутри компании Intel. Что же в нем такого, что вызвало интерес у толстых богатых корпораций?

От "e" и верилога к SystemVerilog

Язык «e» относится к так называемым языкам верификации аппаратуры — Hardware Verification Languages (HVL). «e» был первым успешным языком среди HVL, но потом его находки вобрал в себя появившийся после 2001 года SystemVerilog.

SystemVerilog стал гибридом из:

1. Языка описания аппаратуры Verilog (Hardware Description Language — HDL), который используется для логического синтеза схем — код на нем превращается в граф из логических элементов, а потом в дорожки и транзисторы микросхемы на фабрике;

2. Расширения верилога под названием Superlog (оттуда SV вобрал сложные типы — структуры итд);

3. HVL под названием Vera (откуда SV взял объектно‑ориентированность и некоторые аналоги черт из «e»);

4. Языка PSL (Property Specification Language), который возник чуть раньше и влиял на развитие SystemVerilog Assertions (SVA). PSL и SVA относятся к Hardware Assertion Languages, языкам высказываний темпоральной логики.

Главным драйвером развития SystemVerilog была компания Synopsys, которая купила и Superlog за ~$30 миллионов долларов и Vera за $26 миллионов.

Synopsys, вместе с Cadence, Mentor Graphics и представителями крупных электронных компаний занимались стандартами для всего этого хозяйства через комитет Accellera, на котором пришлось пару раз позаседать и автору этой заметки.

Помимо вышеперечисленных языков был еще HVL под названием Rave, который канул в Лету, а также Jeda — язык, который создали бывшие работники стартапа, с которым Synopsys купил Веру, по поводу чего Synopsys тревожил их с помощью юристов, после чего в Jeda боялись инвестировать и он тоже канул в Лету.

До HVL были HDL

В 1980 годы людям надоело рисовать схемы карандашом на бумаге или возить мышкой по экрану. В конце десятилетия случилась революция логического синтеза и схемы стали проектировать с помощью написания кода на языках описания аппаратуры Verilog и VHDL. Были еще PALASM, Abel и Cupl, а также iHDL — секретный внутренний HDL в Intel. Все эти языки быстро вымерли и середина 1990-х проходила под холиваром Verilog и VHDL.

В начале 1990-х ряд компаний пытался насадить VHDL, но инженеры сопротивлялись его противным фичам. Например если вам нужно сложить A+B, то в верилоге вы могли написать просто C=A+B. А в VHDL приходилось писать что‑нибудь типа:

с <= std_logic_vector (resize (signed (a), 9) + resize (signed (b), 9));Потом Verilog победил, но VHDL до сих пор остался в разных неочевидных местах, например графический процессор внутри Apple iPhone, который Apple изначально лицензировал у Imagination Technologies - был написан на VHDL.

Рост сложности, нудности и дороговизны ошибки

И у Verilog, и у VHDL не все было хорошо с тестированием получившихся схем. Пока схемы были маленькими, на уровне сложности советской игры 1985 года «Ну, погоди!» (она не была написана на HDL, я привожу ее просто как уровень сложности), с тестированием особой проблемы не было. Люди писали код в духе:

a = 2;

b = 2;

# 10 // Подождать 10 микросекунд

if (sum != 4)

begin

$display ("Сумматор не суммирует!");

$finish;

endТакие прямолинейные тесты так и называются: direct test («прямой тест»).

Однако в начале 1990-х годов размер микросхем быстро рос. Я до сих пор помню, с какими расширенными глазами мне маркетер из Mentor Graphics рассказывал про «гиганский ASIC на 100 тысяч вентилей» от его японского клиента, который «невозможно верифицировать» за разумное время. Сейчас счет вентилей в ASIC‑ах идет на миллиарды, и это никого так не пугает.

Дело в том, что помимо увеличения количества элементов увеличивалась и микроархитектурная сложность. Вместо микрокода 1970-х и простых конечных автоматов проектировщики стали конструировать конвейерные схемы, и были просто задавлены количеством частных случаев, которые им приходилось разгребать. Инженеры‑тестировщики (верификация в начале 1990-х стала оформляться как отдельная профессия) — очень страдали от нудности процесса и сбегали сначала в программирование GUI для виндоус, а потом в возникший в середине 1990-х веб‑дизайн.

Росла и стоимость ошибки — фиксированный платеж за re‑spin микросхемы на фабрике стал стоить сотни тысяч долларов, а потери выручки от задержки выпуска микросхемы стали исчисляться десятками миллионов (сейчас все выросло еще на порядок).

Решение ситуации, часть первая: повышаем уровень абстракции с сигналов до транзакций

И вот тогда возникло несколько идей для повышения производительности верификатора:

-

Повысить уровень абстракции - вместо проверки сигналов проверять так называемые транзакции. Примеры транзакции:

передаваемый за N тактов сетевой пакет;

запись строки из кэша процессора в память по заданному адресу и с заданным содержимым;

координаты и цвета вершин треугольника в GPU;

Проверять поведение блока, спроектированого на верилоге, против модели, которая работает на уровне последовательности транзакций и ничего не знает о тактовом сигнале.

Такую модель гораздо проще написать, чем потактовую модель - ее программист может вообще не знать, как организован конвейер и как проектируется хардвер на уровне регистровых передач. Более того, писание такой модели можно аутсорсить. Или купить готовую - скажем симулятор процессора на уровне инструкций.Для превращения транзакции в сигналы и сигналов в транзакции стали использовать особого вида программу под названием функциональная модель шины (Bus Functional Model - BFM). Опять же, писание BFM можно аутсорсить или вообще купить уже готовую модель - скажем шины AXI, SATA или PCI Express и приспособить под свои нужды.

Решение ситуации, часть вторая: делаем ограниченно-случайный генератор транзакций чтобы создавать сценарии, которые не приходили нам в голову

Использование транзакций в комбинации с BFM повышает производительность труда даже для написания прямых тестов, но все равно тысячи прямых тестов писать тягостно. Кроме этого, некоторые сценарии могут просто не приходить в голову.

Можно генерировать транзации, наполняя структуру транзакции (или класс транзакции) просто случайными числами, но тогда 99% транзакций могут быть просто внутренне противоречивыми, такими, которые никогда не увидит аппаратный блок в реальной жизни. Например запрос на чтение строки в кэш из памяти с атрибутом «атомарный».

Чтобы повысить качество генерации случайных транзакций, языки верификации аппаратуры ввели специальный механизм, который называется «решатель ограничений» (constraint solver). Он напоминает функциональные языки программирования: вы задаете отношения между объектами, и для вас автоматически генерируется транзакция, которая удовлетворяет этим ограничениям.

Причем (!) если у вас есть правило «если A находится в множестве { 1, 4, 8 } то B находится в диапазоне [5:10]» — то это правило будет работать в две стороны:

Если вы потом ограничите A == 4, то оно будет генерить только значения B, которые не вступают в конфликт с этим правилом, то есть генерить только B = 6, 7, 5, но не B = 13.

Но если вы ограничите B == 13, то оно будет генерить A = 10 или 0, но не такие A, чтобы B нарушало правила:

Вот как это выглядит на SystemVerilog:

class simple_transaction;

rand [7:0] a;

rand [7:0] b;

constraint a_versus_b

{

a inside { 1, 4, 8 }

-> b inside { [5:10] };

}

На тему ограниченно‑случайного генератора транзакций было последнее занятие на Школе Синтеза Цифровых Схем. Вот его видео, сайт и телеграм‑канал:

Решение ситуации, часть третья: проверяем, что известные нам интересные сценарии действительно случились во время симуляции - с помощью групп функционального покрытия

К сожалению, генерация ограниченно-случайных транзакций имеет ограниченную полезность, если мы не можем проверить, что известные нам сценарии из плана тестирования действительно произошли во время симуляции.

Да что там генератор случаных транзакций. Даже человек, который писал прямые тесты, может забыть или полениться реализовать часть тестового плана, а потом сказать "все сделано" и уехать в отпуск. Как проверить, что действительно все сделано?

Для этого в SystemVerilog есть два механизма: группы функционального покрытия (covergroups) и последовательности выражений темпоральной логики для функционального покрытия (cover properties).

И о первых, и о вторых мы поговорим на следущем занятии Школы Синтеза, которое состоится в эту субботу 25 марта. Занятие будет вести Сергей Чусов, Инженер по верификации аппаратного обеспечения лаборатории НИЛ-ЭСК МИЭТ

Идея cоvergroups: это структуры данных, которые состоят из так называемых точек функционального покрытия, coverpoints, которые соотвествуют переменным или выражениям. Для каждого из них есть группа "корзинок", cover bins. Когда симулятор видит какое-нибудь интересное значение, он увеличивает счетчик соотвествующей "корзинки":

В SystemVerilog есть подъязык описания этих корзинок и выглядит это так:

covergroup cvr @ (posedge clk iff ~ rst);

coverpoint push

{

// Мы видели такты с сигналом вталкивания в очередь (push)

bins push = { 1 };

// и видели такты без этого сигнала

bins no_push = { 0 };

}

// Мы видели все четыре комбинации сигналов вталкивания и выталкивания

cross push, pop;А вот как мы можем применять корзинки и группы корзинок для фиксации появления различных данных: индивидуальных значений, групп значений, диапазона данных или шаблона:

write_data_specific: coverpoint write_data

iff (push)

{

bins equal_12 = { 8'h12 };

bins equal_12_or_20 = { 8'h12 , 8'h20 };

bins from_12_till_20 = { [ 8'h12 : 8'h20 ] };

bins from_12_till_20_in_3_bins [3] = { [ 8'h12 : 8'h20 ] };

ignore_bins to_ignore = { [ 8'h17 : 8'h18 ] };

bins mixed = { [ 8'h12 : 8'h20 ] , 8'h30 };

wildcard bins binary_xx1x1x1x = { 8'b??1?1?1? };

wildcard bins hex_2X = { 8'h2? };

}Также мы можем создавать корзинки для последовательности изменений значений в нескольких тактах:

push_transitions: coverpoint push

{

bins push_010 = ( 0 => 1 => 0 );

bins push_101_or_1001 = ( 1 => 0 => 1 ), ( 1 => 0 => 0 => 1 );

bins push_10001 = ( 1 => 0 [* 3] => 1 );

}Еще можно средствами обычного кода на верилоге записывать номера тактов, в которых случились разные события и потом делать корзинки по разнице событий по времени (в смысле по тактам). Это полезный прием, который я часто использую.

Еще инструмент для верификатора: выражения темпоральной логики

Когда речь идет о последовательности событий, удобнгым инструментом для верификатора являются выражения темпоральной логики, которые можно использовать в трех ипостасях: для проверки ошибок во время симуляции (concurrent assertion), для функционального покрытия (cover property) и для анализа / реверс-инжиниринга кода с помощью методов формальной верификации (автоматическое доказательство утверждений с помощью assume / assert).

Мы не будем разбирать формальную верификацию в этом цикле Школы Синтеза, но на субботнем занятии concurrent assertions и cover properties будут.

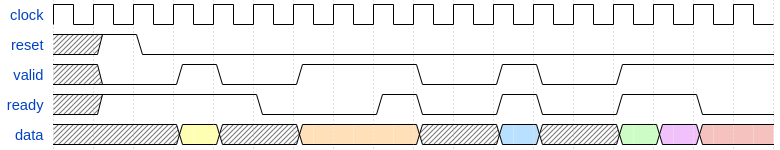

Пример concurrent assertions на тему протокола valid / ready, который мы разбирали во время одного из прошлых занятий Школы Синтеза:

keep_valid_high_until_ready: assert property

( @ (posedge clock) disable iff (reset)

valid & ~ ready |-> ##1 valid );Смысл этого выражения: симулятор считывает значения сигналов valid и ready на положительном фронте тактового сигнала clock, кроме случаев, когда мы находимся в сбросе (reset). При этом: если на фронте в текущем такте valid был выставлен в 1, но ready стояло 0, то в следующем такте valid должен продолжать стоять. А иначе симулятор выдаст ошибку.

Такое простое правило покрывает все случаи использования valid и ready: valid перед ready, valid после ready или одновременно:

Вот другой пример высказывания темпоральной логики, для очереди FIFO:

three_pushes_without_pops_result_in_cnt_3_and_non_empty:

assert property

(@ (posedge clk) disable iff (rst | depth < 3)

~ pop throughout (empty and push [*3]) |-> ##1 ~ empty & cnt == 3);Оно значит: если FIFO сначало было пустое, а потом мы сделали три вталкивания, и все это время не было ни одного выталкивания, то потом мы получим счетчик элементов FIFO равным трем и признак пустоты empty=0.

Такие же выражения можно использовать для проверки функционального покрытия, но в них нужно опустить следование / импликацию предикатов, то есть "|->":

observed_three_pushes_without_pops:

cover property

(@ (posedge clk) disable iff (rst | depth < 3)

(~ pop) throughout (empty and push [*3]));что означает: "во время симуляции видел три вталкивания подряд без выталкивания".

После симуляции можно сгенерировать информативный отчет о покрытии корзинок и последовательностей. Он выглядит так:

В субботу 25 марта на Школе Синтеза это все будет детально. Она сейчас проходит в офлайне на 12 площадках, но даже если вы до этого не ходили на Школу, но знаете основы верилога, вы можете получить инструкции по софтверу в телеграм-канале и потом смотреть все на ютюбе.

UPD: Трансляция занятия на YouTube в 12:00 в субботу 25 марта по московскому времени:

Краткое содержание:

Технология проверки функционального покрытия хорошо дополняет технологию генерации ограниченно-случайных транзакций, которую мы обсудили на предыдущем занятии Школы.

Такие методы, как "корзинки" покрытия (covergroups/coverpoints/cover bins), а также покрытие последовательностей, заданных выражениями темпоральной логики (cover properties) - позволяют проверить, что при симуляции со случайными транзакциями произошли все интересные сценарии, которые инженер-верификатор запланировал в плане тестирования.

Тандем "генерация ограниченно случайных транзакций + проверка покрытия плана тестирования" повышает качество, делает верификацию более предсказуемой, и одновременно менее нудной для разработчика, превращая создание таких сред в своего рода искусство.

Выражения темпоральной логики можно использовать не только для оценки покрытия. Если соединить их с импликацией предикатов ("если произошло A, а через N тактов B, то затем можно ожидать С") то такие выражения можно использовать для нахождения ошибок в схеме - как при симуляции, так и с помощью программ формальной верификации / автоматического доказательства утверждений. В SystemVerilog эта часть языка называется concurrent assertions - "параллельные утверждения". Это полезный инструмент как для инженера-верификатора, так и для проектировщика.

На занятии в субботу 25 марта мы разберем функциональное покрытие и параллельные утверждения, а на занятии 1 апреля - свяжем всю верификацию в законченную картину вместе с моделями интерфейсов шины (Bus Functional Model) - программ, которые связывают сигналы и транзакции.

Комментарии (45)

ReadOnlySadUser

00.00.0000 00:00+32Казалось бы, а причем тут язык "е") Статья-то хорошая, но заголовок вообще не соответствует содержанию

YuriPanchul Автор

00.00.0000 00:00-4Так в языке "e" начались все описываемые механизмы: constrained randomization, functional coverage, выражения темпоральной логики. И на 10 лет раньше, в 1992 году. SystemVerilog это просто инкорпорировал в себя в начале 2000-х.

Точно так же как скажем Паскаль не возник бы без Алгола.

ReadOnlySadUser

00.00.0000 00:00+23И сколько этой информации уделено места в тексте?) Одно предложение? Я понимаю бы ещё все примеры были на языке "е" или было бы сравнение "как было в е, и как стало в SV".

Но ведь нет) Статья о проблемах валидации железа. Убери из рассказа все упоминания "е" она хуже не станет)

YuriPanchul Автор

00.00.0000 00:00-5В принципе я могу для каждого примера на SystemVerilog его эквивалент на e. Но насколько это актуально? Лицензия на e стоит 50 тысяч долларов (стоила раньше по крайней мере). Его используют те, кто подсел на него в 1990-е / начале 2000-х и решил не переключаться на SystemVerilog, возможно некоторые группы в Интеле, или там военные, которые смешивали его с VHDL. Он открыл путь для SystemVerilog, а вот SystemVerilog можно скачать и с ним поиграть.

ReadOnlySadUser

00.00.0000 00:00+18Да проблема-то не содержании статьи) Проблема в заголовке) Заходишь почитать про язык, но читаешь целую статью о верификации железок) Кликбейт получается)

YuriPanchul Автор

00.00.0000 00:00-3Дык весь язык e - только про верификацию железок. Там все то же что в SystemVerilog, только в профиль + он не объектно-ориентированный, а аспектно-ориентированный:

Например вот его вариант constraints https://www.verilab.com/files/Specman_primer_systemverilog20180124.pdf

vvzvlad

00.00.0000 00:00+6Так проблема в том, что я узнаю это в комментариях, а в статье тема языка е просто заминается.

Fil

00.00.0000 00:00+3Сегодня в топе не менее кликбейтные "У животных есть личности. И это ставит науку в тупик", "ChatGPT провалил тест на ручник" (эта вообще не соответствует содержимому, просто мнение одного анонимуса). Конкурировать с такими по-честному невозможно. Если бы эта статья содержала в названии "SystemVerilog", ее бы прочитало 15 человек и она бы набрала +2.

Uint32

00.00.0000 00:00+4с <= std_logic_vector (resize (signed (a), 9) + resize (signed (b), 9));

Если a, b и c - integer, то на VHDL выглядит точно так же:

c <= a+b;

Хейт vhdl на пустом месте, имхо

YuriPanchul Автор

00.00.0000 00:00+1Никогда не видел, чтобы кто-либо использовал integer для сигналов (или variables) в VHDL. Он же вроде только 32-битный, а во всем синтезируемом коде нужно точно количество бит для каждого сигнала или переменной, которая превращается в D-триггер. Вы мне можете показать кодна VHDL в котором все на integer?

Стандартная практика - это std_logic_vector и numeric_std. Или это какое-то нововведение? (Я использовал VHDL много но давно)

Uint32

00.00.0000 00:00numeric_std

определяет арифметику.

YuriPanchul Автор

00.00.0000 00:00+1Да. А теперь два вопроса. 1) Как в numberic_std сложить два 8-битных числа с переносом в 9 разряд и присвоить их 9-разрядному числу? Со знаком и без знака. В верилоге это просто

logic [7:0] a, b;

wire [8:0] = a + b;

Перенос выясняется автоматически в контексте присваивания.

2) Пользуются ли типами signed и unsigned из numeric_std для портов entity?

nerudo

00.00.0000 00:00+1Все на integer не будет, т.к. интерфейсы рано или поздно потребуют явной спецификации разрядностей. Внутренняя математика — отчего бы нет? Начиная от тупого счетчика, который современные синтезаторы урежут до нужного числа бит. А если вспомнить что integer бывает с явным заданием диапазонов, так и вовсе можно любую арифметику писать. Заодно автоматически проверяя переполнение на моделировании.

YuriPanchul Автор

00.00.0000 00:00+1Я не видел синтезируемого кода на VHDL, который вот так бы полагался на то, что синтез все урежет из integer. Я также не встречал таких рекомендаций в литературе.

Насчет явного задания диапазонов - то же самое. Хотя я использовал VHDL в 1999-2003 и может потом кем-то стало принято писать integer c ranges вместо std_logic_vector / signed / unsigned.

nerudo

00.00.0000 00:00Лет 15-20 назад, когда математика еще писалась руками, я вполне писал себе ее на integer'ах и это синтезировалось ISE. Живого кода сейчас не найду за давностью лет

YuriPanchul Автор

00.00.0000 00:00+1Я понимаю что оно синтезировалось, но для ASIC-овых компаний это был бы неправильный стиль

yuklimov

00.00.0000 00:00+1Я использу ieee.std_logic_unsigned.all, и тогда std_logic_vector можно складывать без приведения.

Да, в VHDL нет расширения до размера результата, а только до максимальной ширины аргументов, но это спорный вопрос что лучше. Больший контроль за разрядностью - меньше ошибок, но чуть больше кода, когда надо разрядность изменить.P.S. Сразу скажу, что в моих ПЛИС и чипах нет знаковых чисел совсем (вот такие задачи ;)), да и расширения разрядности тоже не вспомню, чтобы требовались, кроме при выдачи в PCIe, где все регистры, видимые из процессора, 32 битные.

P.P.S. В листинге про 2+2 sum потерялось.

YuriPanchul Автор

00.00.0000 00:00+1Да, я в курсе про ieee.std_logic_unsigned.all но в 1998-2002 когда я пользовался VHDL, были дискуссии, что это плохо, что у VHDL есть разные несовместимые пакеты для арифметики (numeric_std и std_logic_signed/unsigned), std_logic_signed/unsigned считался менее стандартным (он вроде был связан с Synopsys) и предлагалось переходить на numeric_std. Собственно, это предлагается и сейчас - первая нагугленная ссылка:

https://nandland.com/vhdl-math-std_logic_arith-vs-numeric_std/

Have you ever tried to do math operations inside of an FPGA? If so, you probably have realized that you need to include a special package file to accomplish this task. If you are using std_logic_arith, you are using an unsupported package file. You should be using numeric_std.

Although it might appear that std_logic_arith is an IEEE supported package file, it is not. IEEE created the numeric_std package file and it is the official package file for performing mathematical operations in FPGAs. Std_logic_arith was created by Synopsis before IEEE created numeric_std. Since Synopsis had the first package file to do math, they gained a large user base. Unfortunately their package file is easy to use incorrectly, especially when doing unsigned and signed math. There are two main reasons for this:

Synopsis’ std_logic_arith file does not force you to be explicit in whether your signals are signed or unsigned.

When doing both signed and unsigned math in one file, you will have conflicts with overloaded operators.

yuklimov

00.00.0000 00:00Я начал лет на 15 позже, все успокоились, наверное, т.к. std_logic_unsigned нормально поддерживается всеми используемыми инструментами. Рекомендацию слышал, но писать как предлагает numeric_std вообще не захотелось. Явно это были голоса тех, то продвигали Verilog ;)

YuriPanchul Автор

00.00.0000 00:00+1P.P.S. В листинге про 2+2 sum потерялось.

Идея, что sum присваивается от инстанциации модуля сумматора вне этого кода

KeisN13

00.00.0000 00:00+6Я когда-то сделал вот такую картинку

YuriPanchul Автор

00.00.0000 00:00+1О, это хорошо. Не прошло и 20 лет, как я наконец понял отношение между eRM, RVM и uVC. Спасибо

AlexeyK77

00.00.0000 00:00+2При прочтении у меня случился промах кэша, пришлось лезть в медленное долговременное хранилище за значением;)

Коалесценция (от лат. coalesco — срастаюсь, соединяюсь) — слияние частиц (например, капель или пузырей) внутри подвижной среды (жидкости, газа) или на поверхности тела.

KeisN13

00.00.0000 00:00ну да, тут подразумевается соединение всех ранее придуманных методологий верификации в UVM

wormball

00.00.0000 00:00Это ещё что! Я как-то раз употребил слово "покоалесцирую" в значении "уподоблюсь коале". За что коала на меня обиделась.

В филогенетике, кстати говоря, коалесценция употребляется в обратном значении — где дерево ветвится, там и коалесценция. Ибо когда мы идём назад по времени (что делают коалесцентные методы построения деревьев), то кажется, что ветки коалесцируют, хотя на самом деле они расходятся.

PTM

00.00.0000 00:00+4интересный способ интегрированной рекламы, но мне лично больше нравится отдельным блоком в любом месте статьи, чем неочевидно и во многих местах. Спасибо за понимание.

YuriPanchul Автор

00.00.0000 00:00Я вас понимаю, но в принципе в данном случае речь идет не о платных тренингах, а о так сказать продолжении поста в виде бесплатной лекции на Школе Синтеза с упражнениями на симуляторе.

e-zig

00.00.0000 00:00+1А какие сейчас тенденции в использовании SystemVerilog как HDL?

На том же verilog очень неудобно описывать интерфейсы шин - их нельзя объединить в структуру. В том же VHDL можно - и это очень удобно. В SV можно использовать интерфейсы.

te3s

00.00.0000 00:00+2SV активно используется для разработки во многих компаниях именно из-за интерфейсов. Кроме того, использование SV для дизайна сильно упрощает использование UVM. В VHDL-2008 нет реализации интерфейсов как таковой, вместо этого можно упаковать порты в record, но без modport это все еще хуже, чем в SV. Интерфейсы добавили только в VHDL-2019, но должно пройти еще лет 10 пока вендоры начнут поддерживать этот стандарт. Т.е. в разработке большие компании скорее отходят от SV, если что-то написано на VHDL, то это скорее легаси, которое просто страшно/лень переписать.

shuhray

00.00.0000 00:00А что стало с Гавриловым?

YuriPanchul Автор

00.00.0000 00:00Стал членом совета директоров TSMC https://www.linkedin.com/in/moshe-gavrielov-401b28/

etherblade

00.00.0000 00:00+1Отличная статья, спасибо. Хотел бы добавить что еще очень важный coverpoint это то что мы наблюдали появление valid при отсутствующем в предыдущем такте ready.

DustCn

00.00.0000 00:00Вот ваш Гаврилов:

https://il.linkedin.com/in/yoav-hollander-aa565630?original_referer=https%3A%2F%2Fwww.google.com%2F

"I created the e verification language, and founded Verisity to commercialize the related tools and methodologies for HW verification. "

Не очень, как то на Гаврилова смахивает...

YuriPanchul Автор

00.00.0000 00:00По вашей ссылке сказано "президент Verisity?" Нет, по вашей ссылке сказано "founder & CTO" - в переводе с английского означает "основатель и CTO". А президент Гаврилов - здесь https://www.linkedin.com/in/moshe-gavrielov-401b28/

FSA

00.00.0000 00:00+1Забавно, что в повествовании забыли про язык D. А он, между прочим, в 2018 году был включен в состав GCC. Когда-то пробовал его, нашёл свой старый файл и скомпилировал с помощью gdc на своей системе.

datacompboy

Тема языка e плавно позабылась ;)

YuriPanchul Автор

Ну дык все его находки перенеслись в SystemVerilog. При этом SystemVerilog можно запустить и бесплатно попробовать вместе с Questa или Xilixn Vivado, а вот чтобы получить доступ к интерпретатору e/Specman, нужно или работать в электронной компании или заплатить $50,000 за лицензию https://www.design-reuse.com/news/3130/verisity-specman-elite-version-4.html

datacompboy

Для других поглащённых языков в статье упоминается куда именно они уплыли в SV, для e -- нет :)

datacompboy

поглОщённых, конечно же. и разумеется, заметил позже чем могу исправить.

mpaxepnepe

Dlang.org позволяeт забыть весь алфавит