Внутри каждого современного телефона несколько микросхем ASIС. Ими наполнены автомобили, стойки в центрах обработки данных, датчики «умного дома», и вообще все электронные устройства. Без чипов ASIC был бы невозможен быстрый интернет, трехмерные игры и ускорители машинного обучения.

Микросхемы ASIC, их родственники FPGA и выросшие с ними технологии проектирования позволили закладывать сложные алгоритмы прямо в «железо». Они разрушили стереотип, что вычислительная система — это только процессор, память и программирование. В статье я расскажу, как развивались ASIC, какую роль в этом процессе сыграли FPGA и каким может быть «железо» будущего.

Эволюция значения аббревиатуры ASIC

Аббревиатура ASIC расшифровывается как Application-Specific Integrated Circuit, или «интегрированная схема, специфичная для приложения». Сейчас это название может показаться странным, поскольку все современные микросхемы — интегрированные и у каждой есть какое-то приложение. Но термин ASIC распространился больше 40 лет назад, в начале 1980-х годов. Тогда он обозначал микросхемы, которые не были ни микропроцессорами, ни стандартными группами логических элементов — И, ИЛИ, D-триггеров.

Позже термин ASIC начали использовать для группы микросхем с определенным расположением логических элементов: рядами ячеек одинаковой высоты с каналами между ними. Эту группу противопоставляли микросхемам со свободным размещением логических элементов, приготовленных только для одного проекта. «Свободный» стиль назывался full-custom. Вплоть до середины 1990-х годов в нем проектировали продвинутые микропроцессоры, но потом их размеры увеличились, и подход full-custom стал излишне трудоемким. С тех пор даже процессоры стали проектировать в стиле ASIC.

Постепенно, начиная с 1980-х годов, внутри одной микросхемы начали размещать то, что раньше было в нескольких: к процессорным ядрам добавили кэши и математические сопроцессоры, встроенные блоки памяти, контроллеры периферийных устройств, ускорители графики и машинного обучения. Для такой организации микросхемы придумали название «система на кристалле», но и это значение смешалось с термином ASIC.

Особый смысл термин ASIC приобрел у разработчиков сетевых устройств во время взлета интернета в конце 1990-х и в среде майнеров криптовалют в конце 2010-х.

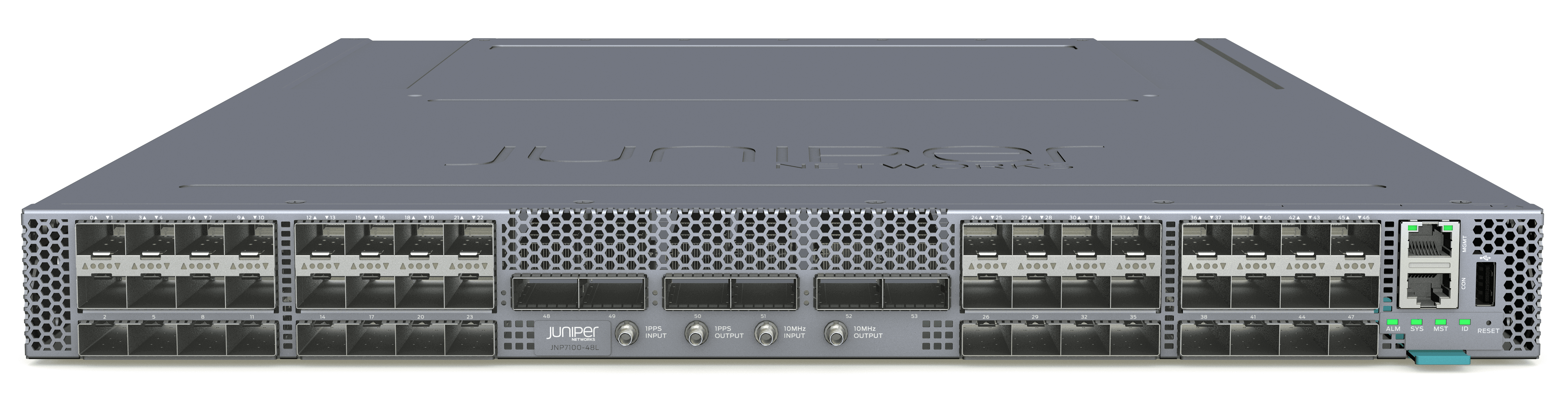

У сетевых инженеров ASIC — это микросхема для быстрой обработки пакетов данных в обход главного процессора. Большинство пакетов простые, их нужно принять из порта роутера, модифицировать заголовок и послать в другой порт. Программа на CPU делает это медленно, потому что байт за байтом изменяет содержимое сначала одного пакета, потом другого. А из ячеек ASIC можно построить так называемый конвейер — аппаратную структуру, которая для каждого порта и на каждом такте будет принимать трансфер пакета размером в десятки байт, и затем обрабатывать сразу много пакетов параллельно.

Конвейер обработки пакетов работает как сборочная линия автозавода, с которой раз в несколько минут выходит новый автомобиль. Сборка машины требует много перемещений конвейера. Внутри ASIC такие перемещения происходят по тактовому сигналу: миллиард раз в секунду для тактового сигнала с частотой 1 ГГц.

Внутри процессора общего назначения тоже есть конвейер, но это конвейер инструкций, а не пакетов. Поэтому обработка сетевых пакетов внешней по отношению к CPU микросхемой ASIC ускорила работу сетей в сотни и тысячи раз. Она позволила избежать коллапса интернета, который предсказывали в 1990-е годы.

Не меньший вклад ASIC внесли в компьютерную графику: для ее ускорения строят аппаратный конвейер обработки координат треугольников, из которых состоит изображение в трехмерной видеоигре, с последующим превращением треугольников в группы пикселей на экране.

В 2010-х аббревиатуру ASIC стали ассоциировать с майнингом криптовалют. Но современное ее значение не ограничивается даже перечисленными областями применения. Сегодня микросхемы ASIC стоят в компьютерах, сенсорах для интернета вещей и спутниках. Теперь они везде, и все стало ими.

Между цифровым лего и приложениями

В конце 1970-х — начале 1980-х годов компании в электронной промышленности делились на те, что выпускали чипы, и те, что строили из них электронные системы. Первые умели строить микропроцессоры, память и так называемую «рассыпуху» — микросхемы с группой однотипных логических элементов. Вторые знали нужды потребителей бытовой электроники и систем телекоммуникаций, имели в штате проектировщиков печатных плат, алгоритмистов по обработке звука и видео, разработчиков игр.

Бум в области персональных компьютеров породил компании нового типа — производителей ASIC. Основанные в 1979 и 1980 годах VLSI Technology и LSI Logic стали фаворитами венчурных капиталистов — Джон Нешейм привел их в пример в своей книге High Tech Start-Up. Эти компании производили специализированные микросхемы на заказ — для сетевых адаптеров, цифровых телевизоров и RISC-микропроцессоров.

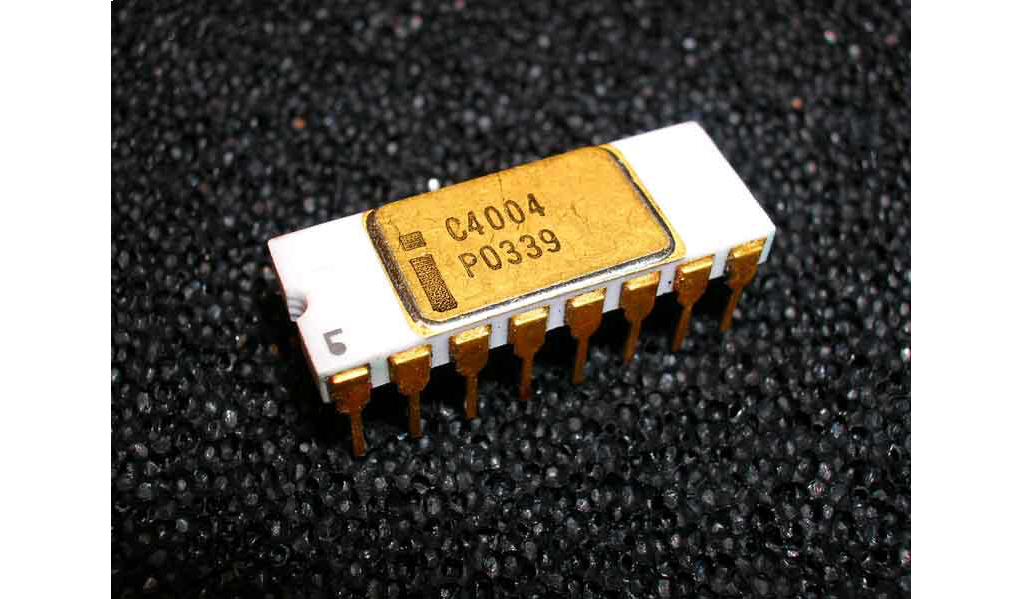

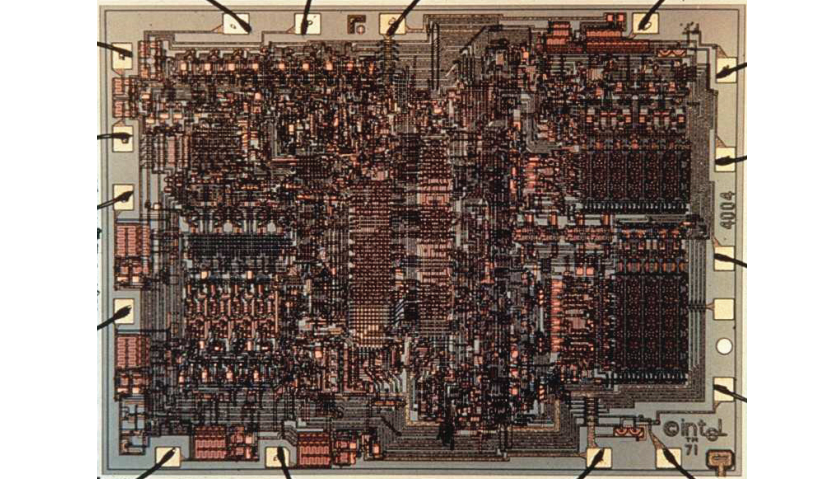

Размер первых микросхем ASIC составлял всего 200 логических элементов. В 1990-е счет уже шел на сотни тысяч, а в наше время — на миллиарды. Стандартным логическим элементом (the equivalent gate), по которому измеряют размеры схем, является схема И-НЕ. В технологиях CMOS она состоит из двух вводов, одного вывода и четырех транзисторов. По-английски простой логический элемент называется gate, и от этого слова, по-видимому, возникла русскоязычная калька «логический вентиль». Как и с понятием ASIC, c термином не обошлось без путаницы, поскольку слово gate также означает затворы у транзисторов.

Море вентилей, стандартные ячейки и их библиотеки

Сначала микросхемы ASIC строили на технологии gate array, которая у нас известна как «базовый матричный кристалл» (БМК). Одну из вариаций такого способа организации транзисторов на кристалле также называют sea of gates — «море вентилей». Основа технологии — в том, что на микросхеме строится «море» не соединенных между собой вентилей одного типа. Микросхемы с одним и тем же «морем» продаются разным клиентам, но для каждого заказчика вентили соединяются в схему дополнительными слоями металлизации. В 1980-х для этих целей использовали дорожки из алюминия, в 1990-х перешли на медь.

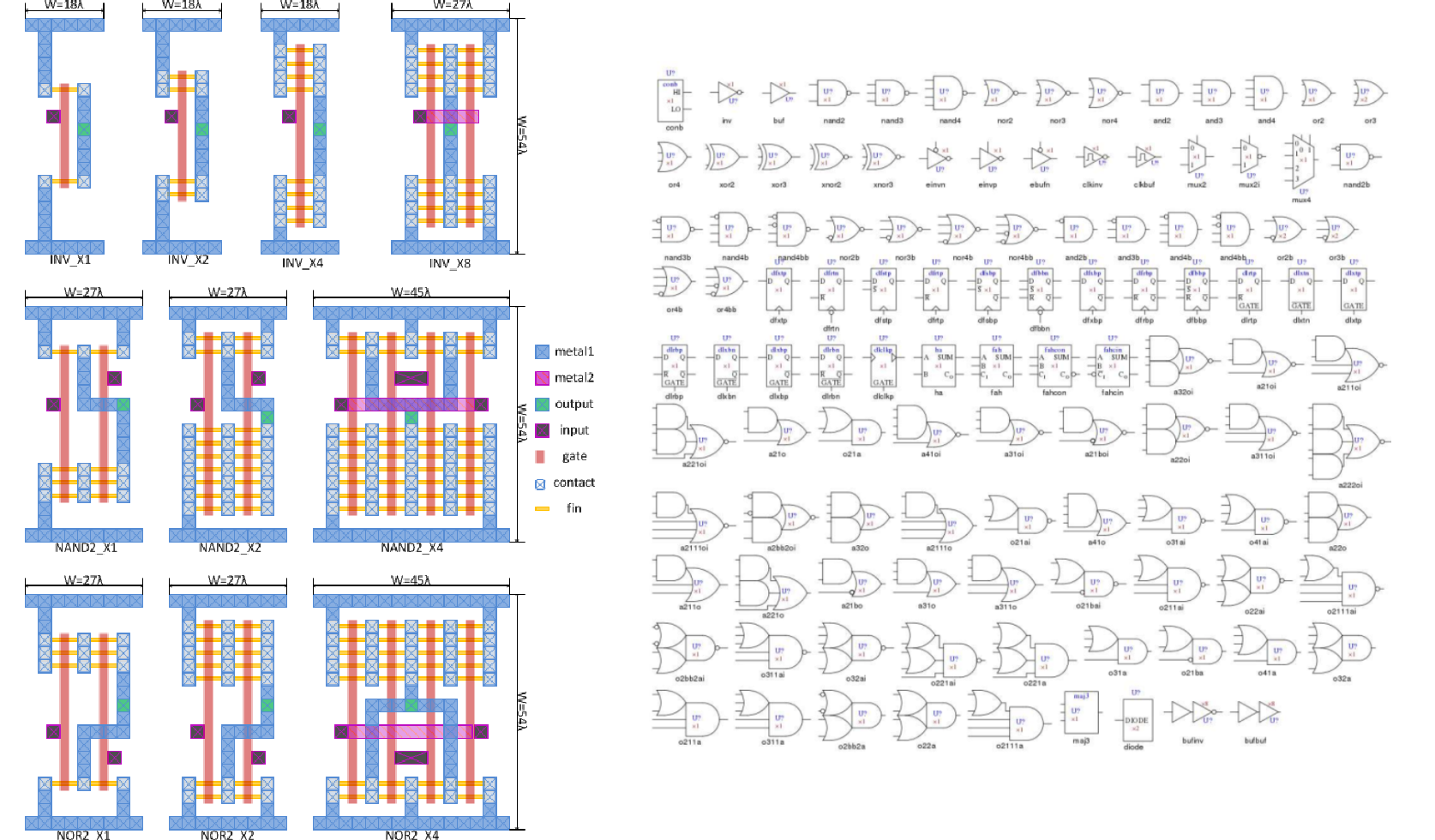

Через некоторое время БМК вытеснила технология стандартных ячеек, или ASIC standard cells. Слово «стандартный» здесь одновременно означает, что разные проекты используют один и тот же набор ячеек и что эти ячейки имеют стандартную высоту на изображении микросхемы, если смотреть сверху. Стандартные ячейки выстраиваются на поверхности микросхемы рядами, между ними находятся каналы — промежутки для соединений. У разных ячеек — разные функции. Помимо логических элементов И, ИЛИ, НЕ и их вариаций с разным количеством входов (2 или 3), в библиотеке ASIC могут быть:

комбинированные ячейки, например, И-ИЛИ-НЕ вместе,

разные вариации элементов состояния (D-триггеров),

элементы выбора — мультиплексоры,

блоки для простых арифметических схем, в частности сумматоров.

Библиотеку ASIC обычно разрабатывают под определенную технологию инженеры, связанные с конкретной фабрикой. Библиотека для технологии 3 нм отличается от созданной для 130 нм. Для каждой ячейки в базе данных библиотеки хранятся:

логическая функция,

физические размеры,

временные задержки в пикосекундах,

параметры, которые позволяют вычислять энергопотребление.

Коэволюция со средствами проектирования

Как показало время, компании-производители ASIC были первыми ласточками в разделении труда в электронной промышленности. В 1980-х годах произошло отделение проектирования от производства. Тогда появились:

компании без фабрик (fabless semiconductor companies),

производства, не проектирующие свои чипы (pure-play foundries),

компании по продажам программ для проектирования.

Способы организации логики на кристалле и структура библиотек ASIC развивались в тесной связке с программами для проектирования. В начале 1970-х годов, еще до появления ASIC, проектировщики рисовали схемы карандашом или строили образы дорожек и транзисторов из цветного картона. К концу десятилетия уже появились редакторы для соединения элементов на экране компьютера, в режиме текстовой псевдографики или на графическом дисплее. Тогда же стали доступны и ранние программы автоматического размещения и трассировки, связывания логических элементов проводниками.

Для программ трассировки оказалось удобно разбить проблему соединения на глобальную трассировку и трассировку внутри канала — так было проще составлять эффективные алгоритмы. Это повлияло на успех создания ASIC по технологии стандартных ячеек. Такие микросхемы стали компромиссом между эффективным использованием площади кристалла и эффективностью алгоритмов размещения с учетом задержек.

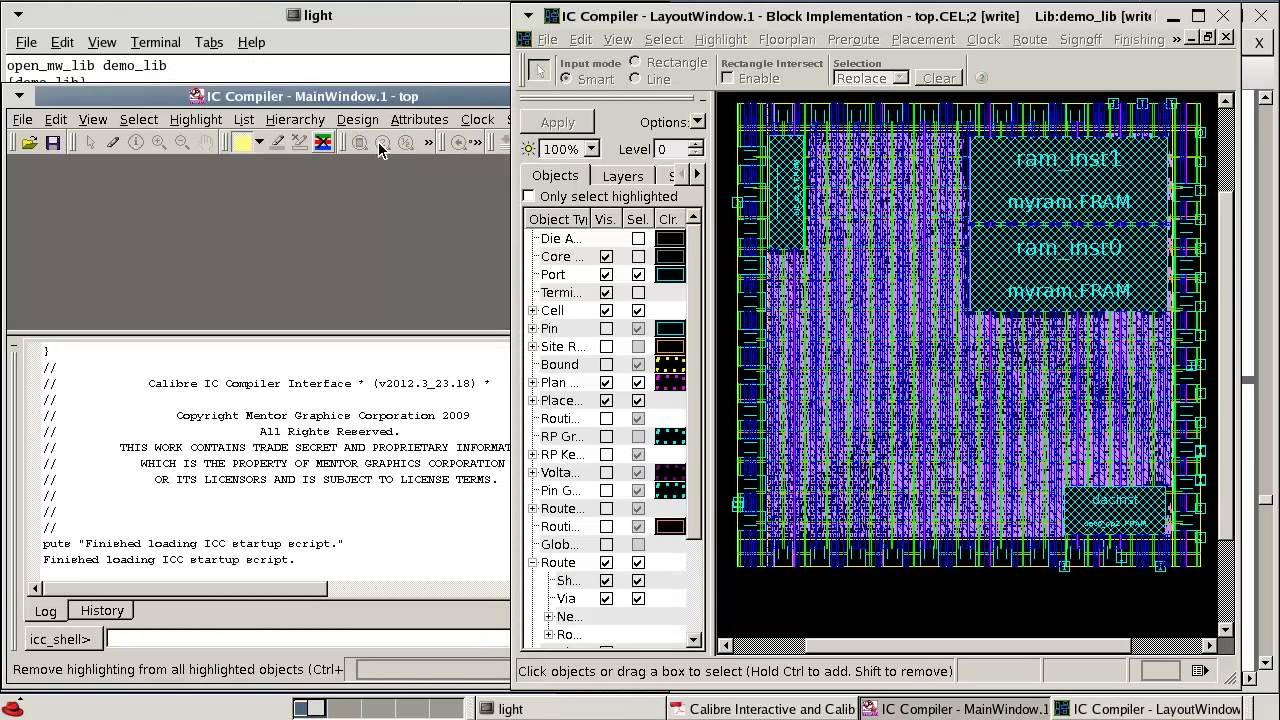

В начале 1980-х годов компании-разработчики программ для проектировщиков микросхем стали рассматривать как отдельную отрасль промышленности — Electronic Design Automation, или EDA. Стартапы в области EDA охотно финансировали венчурные капиталисты. Один из таких стартапов, Synopsys, в 1988 году коммерциализировал технологию логического синтеза и вырос в большую компанию. Synopsys вместе с Cadence Design Systems и Mentor Graphics (сейчас отделение Siemens EDA) стали лидерами отрасли EDA и по-прежнему сохраняют свои позиции.

Синтез логический, физический и поведенческий

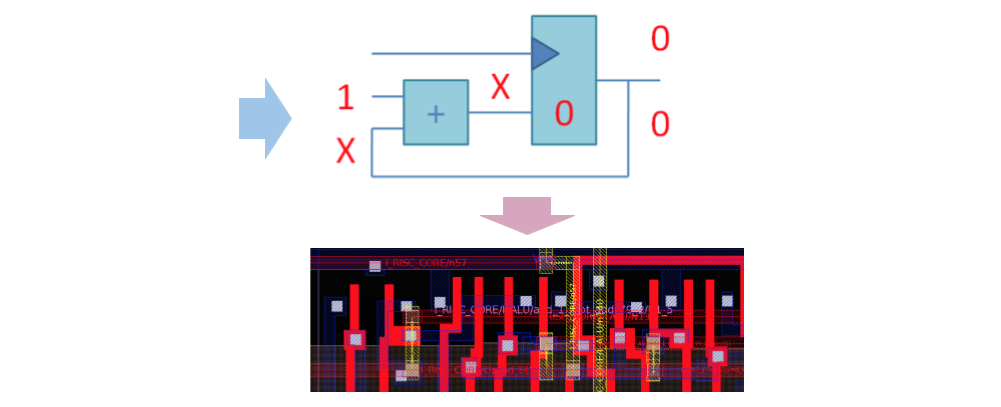

Согласно маршруту логического синтеза, проектировщик описывает поведение схемы кодом на языке Verilog или VHDL. Программа синтеза превращает код в граф из ячеек библиотеки ASIC. Затем программы размещения и трассировки превращают граф в образ слоев будущей микросхемы, файл в формате GDSII. Файл отправляют на фабрику, где на его основе специалисты готовят набор фотошаблонов, по которым потом печатают микросхемы.

module counter

(

input clock,

input reset,

output logic [1:0] n

);

always @(posedge clock)

begin

if (reset)

n <= 0;

else

n <= n +1;

end

endmodule

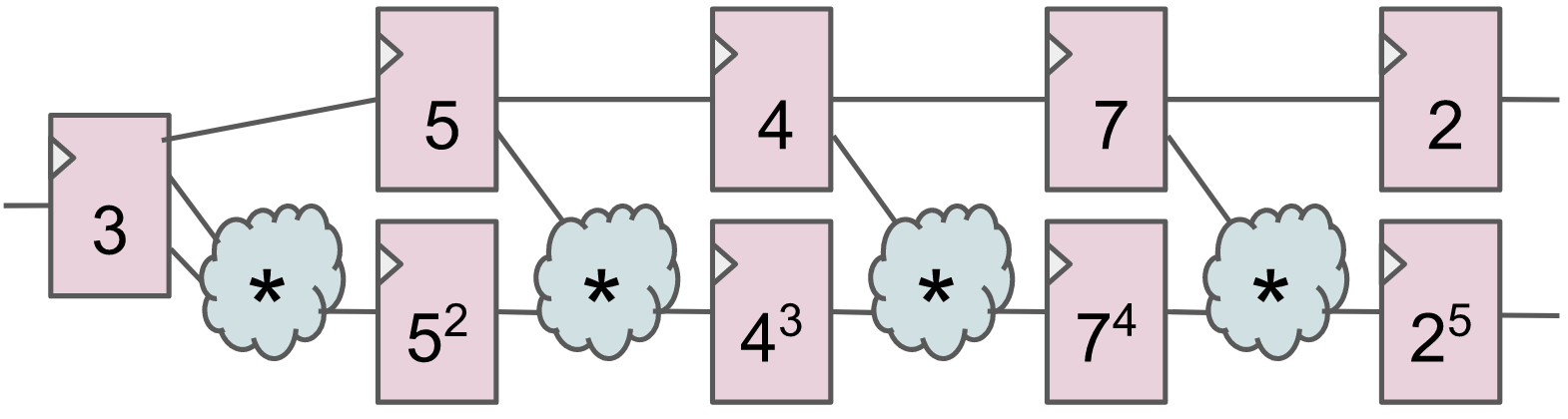

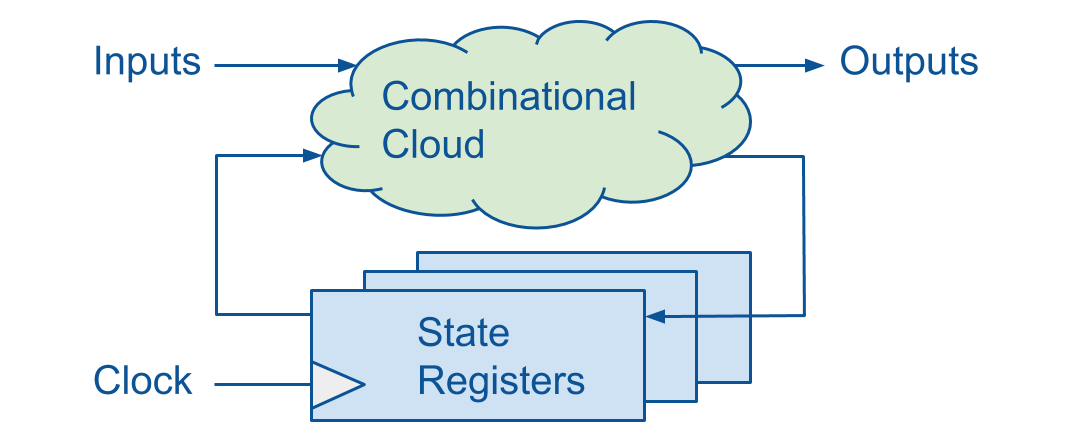

Код для синтеза на языке описания аппаратуры отличается от алгоритмов на языках программирования. Он говорит, что происходит со схемой внутри одного такта — от фронта до фронта тактового сигнала. В начале такта информация считывается из элементов памяти или элементов состояния, D-триггеров. Затем она проходит через несколько слоев логики «комбинационного облака» и в конце такта снова записывается в элементы состояния. Поскольку группы D-триггеров называются регистрами (не путать с регистрами, видимыми программисту в языке Ассемблер), подход получил название «проектирование на уровне регистровых передач». По-английски он называется Register Transfer Level (RTL).

Технология RTL-синтеза позволила сделать скачок из мира небольших процессоров в огромные системы на кристалле смартфонов и других современных чипов. Некоторые компании пробовали пойти дальше и синтезировать RTL из алгоритмов на языках программирования. Такая технология получила название behavioral synthesis, «поведенческий синтез». Однако выяснилось, что на ней неудобно строить конвейеры и другие параллельные структуры.

Большего успеха, чем в поведенческом синтезе, EDA-компании 1990-2000-х годов достигли в технологиях физического синтеза. Физический синтез — это более тесная интеграция логического синтеза с размещением и трассировкой.

Он стал необходим из-за уменьшения размеров транзисторов. Первые микросхемы ASIC начала 1980-х были на техпроцессах от 1 до 3 микрон или более 1000 нм. Задержка распространения сигнала в них определялась скоростью переключения транзистора. Однако с уменьшением техпроцесса до нанометров задержки на соединениях стали играть все большее значение. Теперь синтез может изменять синтезируемую логику после результатов размещения, чтобы вписаться в бюджетированную тактовую частоту. То есть процесс синтеза и размещения стал итеративным.

Если вы учитесь на технической специальности или в старших классах школы, приходите осваивать современные подходы к проектированию микросхем в Школу синтеза цифровых схем. Программа Школы построена на базе курса MIT и выверена годами. Кроме полезной теории вас ждет много практики с использованием отладочных плат, необходимого периферийного оборудования и инструментов разработки. Обучение бесплатное.

Стоимость разработки и производства ASIC

С уменьшением техпроцесса и взрывным ростом размеров чипов увеличивались и фиксированные расходы на их проектирование, верификацию и производство. Чтобы ASIC приносил компании прибыль, необходимо «размазать» фиксированные расходы на весь тираж, причем получившаяся цена должна оставаться конкурентоспособной. Однако расходы быстро повышаются вместе с прогрессом техпроцесса.

Вот примеры стоимости набора фотошаблонов для производства на техпроцессах разных лет:

1990-е — $100 000 и выше,

2000-е — более $1 000 000,

2020-е — более $10 000 000 для 5 нм, более $30 000 000 для 3 нм.

Общие фиксированные расходы на разработку и производство чипа на последнем техпроцессе 3 нм могут превысить полмиллиарда долларов. На такой технологии имеет смысл производить только дорогие устройства с большими тиражами — например, топовые смартфоны.

Как правило, период жизни массового ASIC на рынке ограничен парой лет. Задержка выпуска всего на несколько месяцев может сделать ASIC убыточным, так как за это время рынок заполнят микрочипы конкурента. Чтобы предотвратить задержки, компании еще в 1990-х стали инвестировать в сложные технологии тестирования с генерацией псевдослучайных транзакций и учетом появления запланированных сложных сценариев (functional coverage).

Сейчас в типичной электронной компании больше инженеров занимаются верификацией, написанием среды тестирования на языке SystemVerilog, чем написанием синтезируемого кода, который превращается в чип.

Конечно, не все современные ASIC сделаны на топовых технологиях. Микроконтроллеру, управляющему двигателем, или чипу IoT для производительности может быть достаточно 90 нм. Более того, чип на 3 нм рядом с горячим мотором выйдет из строя быстрее, чем чип на консервативном техпроцессе. При этом, как мы помним, фиксированные расходы для чипов на старых техпроцессах на порядок ниже.

Но можно создавать цифровые схемы и без заказа на фабрике. Такую возможность дают FPGA.

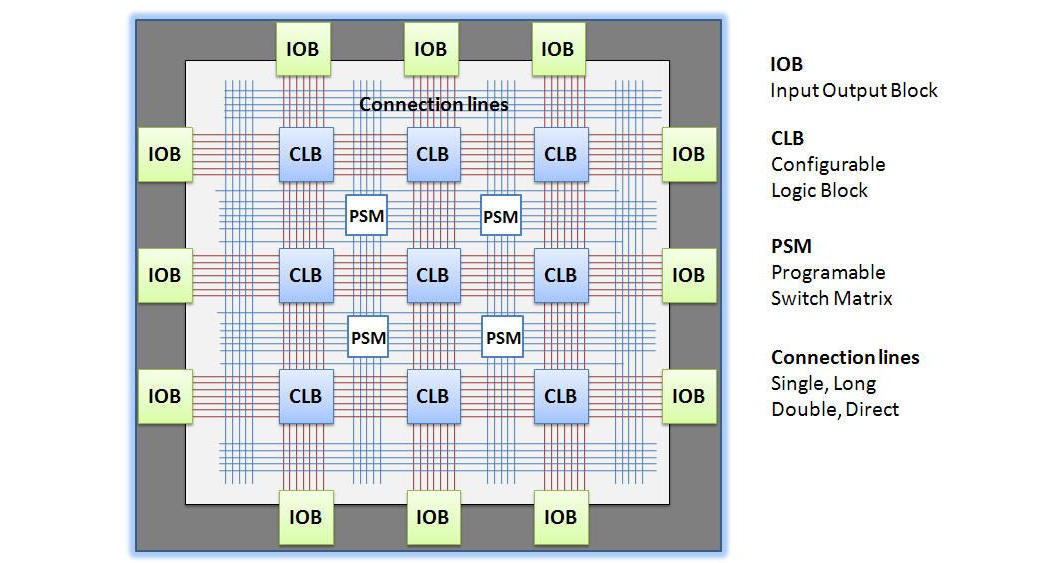

Идея изменяющегося железа

В середине 1980-х в противопоставление к ASIC появились FPGA, Field-Programmable Gate Arrays. На русском эти устройства называются ПЛИС, программируемые логические интегральные схемы. ПЛИС состоят из сложных ячеек, расположенных в виде матрицы. Логическую функцию каждой ячейки можно менять после производства через содержимое конфигурационной памяти.

Идея ПЛИС часто вызывает недоумение: как может меняться схема в уже произведенном чипе? Главную роль в этом играет элемент под названием LUT, или LookUp Table.

В простейшем случае у блока LUT есть шесть входных сигналов и один выходной. Из шести входных сигналов два рабочих (x1 и x0), а четыре — сигналы конфигурации (a, b, c, d).

Значения сигналов конфигурации можно устанавливать при прошивке микросхемы ПЛИС с помощью устройства под названием программатор. Сигналы идут в три мультиплексора, устройства выбора. При таком соединении, если abcd выставлены в 0001, то схема будет эквивалентна логическому элементу И с входами “x1” и “x2” и выходом “y”. А если abcd=0111, то схема будет эквивалентная логическому элементу ИЛИ.

Почему LUT называется справочной таблицей? Она фактически работает как ROM шириной один бит с адресом в два бита. Биты x0 и x1 образуют адрес, а биты abcd — это данные, результат операции для любой комбинации входов x0 и x1.

Если добавить к LUT элемент состояния с еще одним мультиплексором, то получится простейшая ячейка ПЛИС. С помощью мультиплексоров можно также определять связи между ячейками.

Скепсис и нереалистичные ожидания

У гибкости ПЛИС есть цена. Главная проблема в том, что для создания той же схемы, что и в ASIC, потребуется на порядок больше транзисторов. В схеме будут большие задержки, а значит, она сможет работать только на более низкой тактовой частоте. ПЛИС также проигрывает ASIC по энергопотреблению. Поэтому, когда компания Xilinx впервые представила свои FPGA в середине 1980-х годов, их встретили со скепсисом.

ПЛИС были не единственным вариантом изменяющихся микросхем. До них существовали микросхемы PAL компании Monolitic Memories. Внутри PAL выводы из несколько десятков логических элементов И шли в несколько элементов ИЛИ. Соединения входов микросхемы с входами в И можно было менять с помощью программатора у инженера на столе — правда, только один раз.

ПЛИС, построенные с помощью LUT и в форме матрицы ячеек, оказались более затратными, но и более гибкими. Спустя некоторое время рынок FPGA разделили компании Xilinx (сейчас часть AMD), Altera (сейчас часть Intel) и несколько производителей с меньшими долями.

В начале 1990-х годов у некоторых энтузиастов даже были ожидания, что ПЛИС вызовут переворот, сравнимый с революцией персональных компьютеров. В 1997 году в Scientific American появилась статья о реконфигурируемом компьютинге, согласно которой построенные на ПЛИС компьютеры открывали новую эру. Однако пользователи быстро обнаружили, что ПЛИС проигрывают ASIC практически по всем параметрам, кроме одного: чтобы построить схему на ПЛИС не нужно делать заказ на фабрике. Этого оказалось достаточно, чтобы FPGA твердо заняли несколько ниш.

Для чего хороши ПЛИС

Во-первых, ПЛИС оказались полезны для малосерийных устройств, где их объема логики и максимальной тактовой частоты достаточно, а возможность конвейерной обработки данных делает микросхему эффективнее программы на микропроцессоре. Среди примеров такого применения ПЛИС — ранние сетевые роутеры, ранние майнеры биткоинов, обработка сигнала с телескопа или с устройства для сейсморазведки.

ПЛИС применяются и для космоса. Современная система управления кораблем — это сеть из тысяч микроконтроллеров и ПЛИС, где последние используются как расширители ввода-вывода. Они помогают принимать сигналы с сенсоров и управлять движением крылышек.

Во-вторых, ПЛИС нашли применение в сфере образования. MIT еще в 1990-х годах внедрил лабораторные работы на FPGA вместо более ранних лабораторных на макетных платах с микросхемами малой степени интеграции. Для ПЛИС создали программы логического синтеза с языков описания аппаратуры Verilog и VHDL, поэтому ПЛИС стало удобно использовать для обучения будущих проектировщиков ASIC. Помимо базовых лабораторных работ с комбинационной логикой и конечными автоматами, студенты курса MIT 6.111 Introductory Digital Systems Laboratory делают на FPGA проекты по обработке звука и видео.

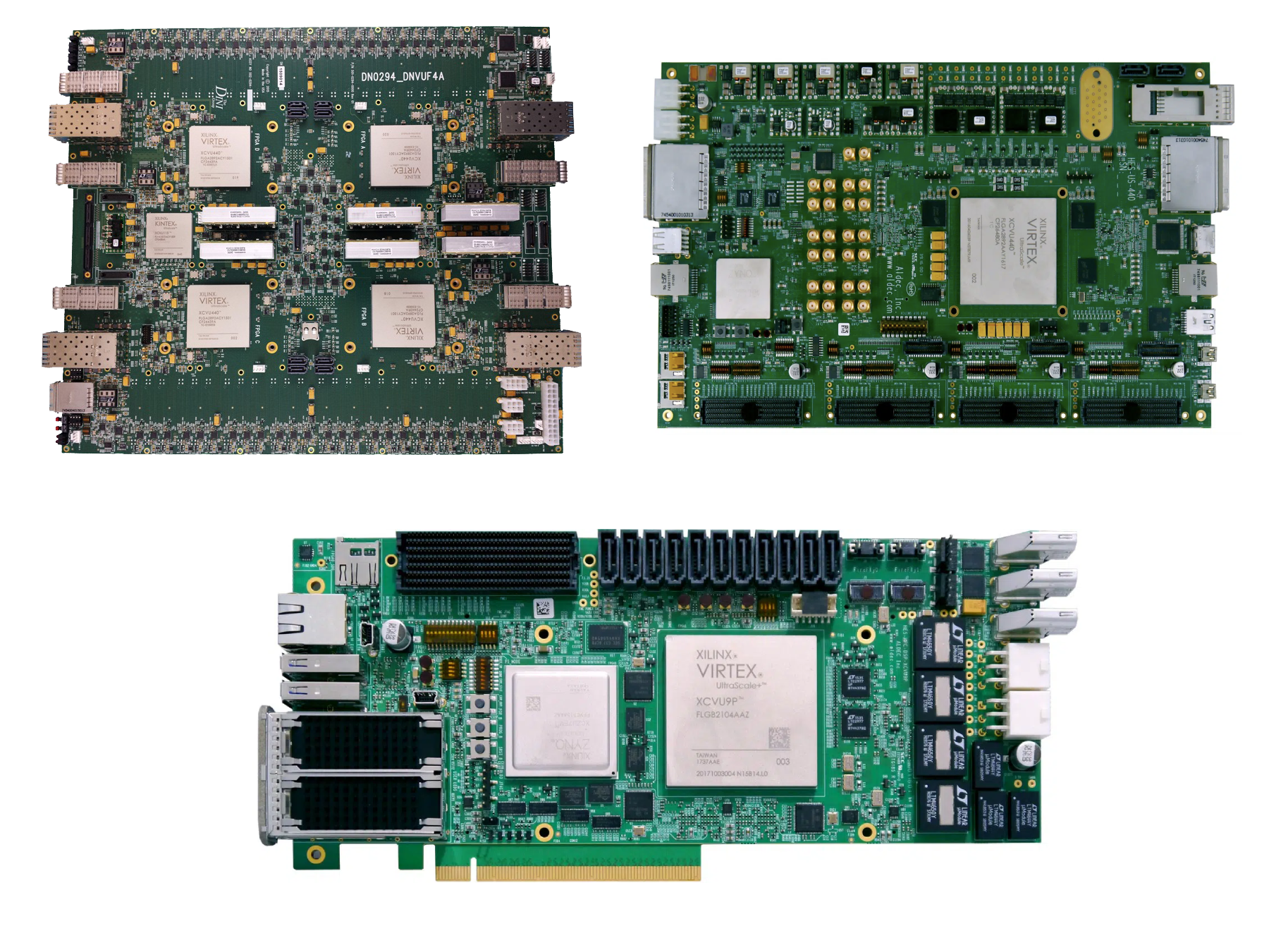

Не менее важным стало использование ПЛИС для прототипирования ASIC. Хотя задержки распространения сигнала внутри такта у ПЛИС другие, потактовое поведение у синтезированных из Verilog схем одинаковое на обоих типах плат. Поэтому процессорные компании стали отлаживать блоки для ASIC на платах ПЛИС. Не студенческих за сотни долларов, а на более дорогих платах с ценами порядка $30 000–$100 000.

Отладка процессора на ПЛИС менее удобна, чем в программном симуляторе на уровне регистровых передач — например, Cadence Xcelium. Но при этом тестовые программы исполняются на синтезированном в ПЛИС процессоре гораздо быстрее. Скажем, если Linux на реальном процессоре грузится за несколько секунд, а на синтезированном в ПЛИС — за пару часов, то на программном симуляторе на такую же операцию могут уйти дни.

После прототипирования процессора на ПЛИС его код заново синтезируется для ASIC. Специальная программа для статического анализа тайминга определит, вписывается ли процессор в бюджет тактовой частоты. Определить это для ASIC с помощью работы на ПЛИС нельзя.

Кроме типичных применений ПЛИС существуют и необычные:

Внутрь ASIC можно поместить встроенную ПЛИС для изменений частей схем на лету. Такую опцию предлагают несколько компаний, в частности французский стартап Menta.

Если проектировщики хотят перенести в ASIC проект с ПЛИС без повторного синтеза из исходников, существует технология HardCopy компании Altera (сейчас часть компании Intel).

Компании Xilinx (сейчас часть AMD) и Altera выпускают ПЛИС с ядрами процессоров ARM в одной микросхеме. Причем эти ядра не синтезированы как конфигурация ПЛИС, а просто расположены рядом с ней как часть ASIC. Такие гибридные устройства, например Zynq, совмещают сильные стороны процессоров и FPGA, но имеют проблему с «бутылочным горлышком» обмена информацией между ними. Как правило, гибриды не могут конкурировать с ASIC по производительности в решении специализированных задач. Зато могут конкурировать по гибкости и цене при малых тиражах устройств.

Если нужен малотиражный ASIC

Иногда исследователю или небольшому стартапу все-таки нужно произвести свой ASIC, потому что ни ПЛИС, ни программной симуляции недостаточно. Чтобы не платить полную коммерческую стоимость, существует более бюджетное решение — Multi Project Wafer (MPW), или шаттл (shuttle). Это вариант работы с фабрикой, при котором на одной пластине изготавливают по дюжине микросхем для нескольких исследователей. Недостатков у бюджетного решения два: ограничения на техпроцессы и сроки. Малотиражный ASIC приходится ждать несколько месяцев.

Сделать свой ASIC на консервативной технологии 180 нм с помощью MPW может стоить всего несколько тысяч долларов, а на технологии 28 нм — несколько десятков тысяч. В Европе возможность шаттлов для университетов предоставляет организация Europractice IC Service, а в США — MOSIS.

Пару лет назад Google в партнерстве с фабрикой Skywater сделали бесплатную программу по созданию MPW для проектов, которые прошли отбор на сайте Efabless. Для программы можно использовать бесплатные открытые средства проектирования Open Lane. Для сравнения, лицензии на средства проектирования от Synopsys и Cadence стоят сотни тысяч долларов. Кроме этого, в программе Google с Efabless используется платформа Caravel — базовая система на кристалле с процессором на архитектуре RISC-V, к которой студент или исследователь может добавить собственные блоки и получить спроектированный ASIC.

Можно надеяться, что аналоги такого сервиса сделают и в России на базе фабрики «Микрон» в Зеленограде. В таком случае российские исследователи и предприниматели (например, в области чипов для ускорения вычислений нейросетей) могли бы изготавливать прототипы устройств до поиска финансирования для массового производства.

Что впереди?

История развития ASIC далеко не закончена. Хотя уменьшать кремниевые транзисторы на технологии CMOS бесконечно нельзя, развитие может пойти по другому пути — например, в сторону трехмерных чипов.

Кроме этого, может быть создана методология проектирования с использованием асинхронных элементов вместо традиционной еще со времен ламповых компьютеров связки «логический вентиль + D-триггер с тактовым сигналом».

Не решена и задача превращения высокоуровневого описания поведения чипа в уровень регистровых передач. Все эти области ждут своих открывателей. Одним из них можете стать вы.

Комментарии (46)

ABRogov

15.12.2023 10:48Можно надеяться, что аналоги такого сервиса сделают и в России на базе...

Из каких соображений? к 2070му году? Не вижу повода для таких надежд.

YuriPanchul Автор

15.12.2023 10:48Готовы спорить со мной на деньги по поводу даты появления шаттл-сервиса для университетских чипов в России?

hogstaberg

15.12.2023 10:48Даты появления сервиса на бумаге? Нет. Даты появления реально работающего сервиса? Ну раз за добрый десяток лет под флагом технологического суверенитета не сделали сей достаточно базово-фундаментальный шаг, то есть все основания сомневаться в том, что теперь то сделают. Может даже технари из Микрона и рады бы, но менеджмент - далеко не факт. No offence, чистая экстраполяция многих прошлых лет в будущее.

RustamC

15.12.2023 10:48Аналог такого сервиса уже есть: https://mpw.miet.ru/

spqr_voldi

15.12.2023 10:48MPW-2023

Результаты первого запуска производства микросхем по системе MPW ожидаются

к концу 2023 года

Конец наступил, результаты есть?

YuriPanchul Автор

15.12.2023 10:48мне говорили месяц назад что в декабре первая пластина по этому сервису

RustamC

15.12.2023 10:48Судя по этой новости, микросхемы уже произведены и к концу года их передадут заказчикам.

А более подробные результаты по каждой из схем, как я понимаю, будут опубликованы в рецензируемых научных журналах, т.к. это одно из условий пользования сервисом

mpa4b

15.12.2023 10:48может быть создана методология проектирования с использованием асинхронных элементов вместо традиционной

Вроде уже создана какая-то, с названием что-то типа "delay-insensitive". Строб передаётся во 2ом проводе рядом с битом данных, активно используются асинхронные хендшейки и C-элементы (https://en.wikipedia.org/wiki/C-element). Даже целый процессор сделали: https://en.wikipedia.org/wiki/AMULET_(processor). Но не взлетело, я предполагаю потому что во-1 тулы не готовы для такой асинхронщины, во-2 оно без клока, зато логики физически больше получается, а следовательно утечки возрастают по сравнению с эквивалентной клоковой логикой (где клок и отключить можно). Хотя может у меня устаревшие сведения.

YuriPanchul Автор

15.12.2023 10:48Да, я работаю с одним из создателем Амулета. Эта тема поднималась много раз за 70 лет, примерно как ИИ. Может на какой-то итерации взлетит.

byman

15.12.2023 10:48В прошлом веке мне довелось делать сложный микропроцессор который работал без клока. Где-то внутри для передачи информации использовалась парафазность, т.е. два провода вместо одного. Вначале оба провода загоняются в 11, а потом по ним передается инфа. На конце детектируется разность. Некоторые модули (регистры , ALU) хорошо подходили под такой прием, но многое никак. В итоге приходилось делать то, о чем Вы писали. Чаще всего добавлялись банальные задержки, имитирующие наиболее критичный путь в логике. Особенно прикольно было с внешним интерфейсом. Предполагалось , что к внешнему контакту подключена какая-то емкость и вот по её разряду-заряду и бралось время :) Этот ужас так и не дошел до изготовления, хотя во всех симуляторах работал :)

Brak0del

15.12.2023 10:48Для чего хороши ПЛИС

Также ПЛИС хороши для применений, где спектр выполняемых задач не очень чётко сформулирован, не устоялся или быстро изменяется. Например, так FPGA-акселераторы заняли свою нишу в датацентрах. Там было много разнородных задач, которые требовалось ускорить, но непонятно в каких пропорциях (пропорции ещё и изменялись с течением времени, а также в зависимости от локации и т.д.). В некоторых случаях тиражи составляли миллионы таких акселераторов, а бюджет -- миллиарды долларов. Другим таким применением стали базовые станции 5G, где параметры обработки сигналов, алгоритмы предобработки и прочее меняются быстрее и чаще, чем есть возможность и экономическая целесообразность выпускать под это ASIC.

vyatkh1

15.12.2023 10:48А вот еще из опыта. ПЛИС прочно и надолго, судя по наблюдению, засели в медицине, конкретно я наблюдаю их в УЗИ аппаратах на формировании уз картинки ( как на формирование луча, так и на обработке эхо сигнала) на выходе платы имеем vga либо hdmi на который накладывается интрфейсная картинка с обычного пк и все это на дисплей. И я подозреваю тут коммерческий интерес. Опция типа эластографии стоит 2000 - 3000$. А делается прошивкой... А прошивка аппарата - это несколько файлов для ПЛИС как раз. Ну тут еще и мелкосерийка. Они бы и рады asic, да дорого.

aabzel

15.12.2023 10:481--Какой путь проходит verilog файл с момента написания до кристаллизации в микросхеме?

2--На фаб отправляют бинарный файл или текстовый?

3--Фаб сделает чип, если им просо verilog код послать?

YuriPanchul Автор

15.12.2023 10:481) порядка 20 шагов. Вот один из вариантов - Open Lane с открытыми тулами

2) Бинарный GDSII, но его можно представить и в текстовом виде - это типа язык описания полигонов, геометических фигур, соответсвующих разным слоям

3) Если с фабом связана сервисная компания которая предоставляет услуги по backend-design - можно сделать такой контракт. Скажем VeriSilicon

aabzel

15.12.2023 10:48Посоветуйте компактную FPGA плату, где есть аудиокодек.

YuriPanchul Автор

15.12.2023 10:48Практически любая плата больше нескольких тысяч лутов. К ней можно присоединить аудио-выход вот с такой дополнительной платой за полтора доллара

и вот такой микрофон

Например

Или скажем

или

https://www.aliexpress.us/item/3256804505446046.html

или

это только компактные, но вообще вариантов еще штук 50

aabzel

15.12.2023 10:48Есть ли в ToolChain(е) FPGA разработчиков утилита на примере Graphviz, которая бы по коду строила схему?

Чтобы пишешь код, запускаешь утилиту и получаешь pdf/svg со схемой электрической цепи / схемы, которые уже скомпонованы как планарный граф.

checkpoint

15.12.2023 10:48В Yosys тулчейне широко используется именно Graphviz.

aabzel

15.12.2023 10:48Graphviz так себе трассировщик.

Мало что можно настроить в Graphviz .

Даже повернуть узлы на произвольный угол нельзя.

checkpoint

15.12.2023 10:48Согласен. Но, как говориться, за неимением другого имеют то, что есть. :)

aabzel

15.12.2023 10:48Но ведь Altuim Designer как-то автоматически трассирует электронные платы?

Значит есть альтернатива.Системы на кристалле ведь тоже разводят автоматически. Так?

checkpoint

15.12.2023 10:48Я не совсем понял причем тут Altium и трассировка плат. Синтез и плэйсмент для ASIC и FPGA производятся автоматически, в то время как печатные платы в подавляющем большинстве случаев трассируются вручную. Если говорить об open source тулчейне - это Yosys и NextPNR. Graphviz используется для визуализации синтезированного нетлиста (схемы). Т.е. иногда дизайнеру хочется посмотреть, во что же на самом деле выродилось его творчество описанное на Verilog-е, он натравливает на синтезированный нетлист утилитки netlistsvg или graphviz и с умным видом смотрит на весь этот бардак. :)

aabzel

15.12.2023 10:48Синтез и плэйсмент для ASIC и FPGA производятся автоматически, в то время как печатные платы в подавляющем большинстве случаев трассируются вручную.

Это с каких пор проводники на кристалле стали разводить автоматически? Подозреваю что с 198x...

И почему тогда PCB всё еще разводят вручную?PCBшки они же проще чем SoC.

checkpoint

15.12.2023 10:48PCBшки они же проще чем SoC.

По этому разводятся вручну.

Топология кристаллов на финальной стадии тоже дорабатываетcя вручную, AFAIK.

YuriPanchul Автор

15.12.2023 10:48Визуализация графов на всех этапах синтеза, mapping-а и после place & route? Да, есть конечно, хотя ее редко используют. Причем на разных уровнять - абстрактном логическом графе, mapped на ячейки FPGA и после размещения:

Абстрактный граф:

После отбражения на конкретные ячейки FPGA:

После размещения (Altera Quartus Chip Planner)

aabzel

15.12.2023 10:48В ToolChain(не) для синтеза BitStream(ов) для FPGA тоже используют CMake?

YuriPanchul Автор

15.12.2023 10:48Все кишки современного Quartus, Vivado, Gowin IDE я не знаю, но раньше (во времена Synplify в 1990-х) не использовали. А почему это принципиально?

Gudd-Head

15.12.2023 10:48Внутри каждого современного телефона несколько микросхем ASIС.

Несколько микросхем ASIС что?

На такой технологии имеет смысл производить только дорогие устройства с большими тиражами — например, топовые смартфоны.

Наверное, на фабриках с технологиях производят не конечные устройства, а чипы для них?

YuriPanchul Автор

15.12.2023 10:48У меня специально для таких вопросов есть вот такая картинка, что делают различные ASIC-и внутри телефона. Картинка осталась от презентаций MIPS / Imagination Technologies:

Gudd-Head

15.12.2023 10:48Да я про то, что у вас первое же предложение без сказуемого.

Чипы вроде как есть, а работают они там или есть просто по фану - ?

dvb1

15.12.2023 10:48И что, до сих пор на Verilog пишут? Я лет 10 назад разговаривал с чуваком из Broadcom и он уже тогда утверждал что у них только System C, а Verilog слишком низкоуровневый.

YuriPanchul Автор

15.12.2023 10:48Я вас скажу даже больше. Я еще в 1996 году встретил на выставке Design Automation Conference продажника из Synopsys, который говорил "через пять лет

все будет телевидениемвсе будут писать на C++". Даже я лично потратил несколько миллионов долларов инвесторов в своем стартапе, в котором написал тул для трансляции из C в Verilog, причем этот тул использовали еще 25 лет назад Hitachi и Fujitsu, а потом стартап купил Synopsys.Так вот. Synopsys еще в 1998 году попытался надавить на RTL инженеров, чтобы те писали на SystemC. RTL инженеры матюкались, потому что они не хотели разбираться, когда вылезала какая-то непонятная ошибка в templated С++ классах для сигналов или bit-accurate types.

Далее выяснилось, что для типичного дизайнера проще написать код на верилоге для конвейера вручную, чем массажировать C++ код прагмами #pragma.

Также выяснилось что в части симуляции SystemC не быстрее, а медленнее, чем высокопроизводительные компилирующие симуляторы типа Synopsys VCS.

Тогда маркетологи Synopsys-а сделали ход конем и в начале 2000-х попробовали продавать SystemC европейским компаниям под соусом "а давайте делать на SystemC высокоуровневое транзакционное моделирование, так как C++ программистов больше, чем дизайнеров на Verilog, и кроме этого в C++ есть сложные структуры данных, а в Verilog их нет (не было в 2000 году)".

Ваш приятель в Broadcom возможно одна из жертв этих маркетеров. До сих пор есть куча компаний, в которых модели написаны на SystemC, хотя по части сложных структур данных начиная с 2002 года (покупки Synopsys-ом языка Superlog, который стал основой SystemVerilog) в SystemVerilog все стало хорошо.Короче: SystemC так и остался нишевым средством высокоуровневого моделирования (но не языком для синтезируемых дизайнов) и более того, после 2010 года его компании стали постепенно из разных мест удалять.

AlexanderS

15.12.2023 10:48Общемировой показатель VHDL 5 лет назад был более 50%. А вы говорите Verilog...

YuriPanchul Автор

15.12.2023 10:48Это странный показатель. Если приплюсовать все студенческие проекты, которые профессора дают в качестве курсовиков в Западной Европе и Южной Америке (в этих местах профессора любят VHDL), то так наверное и получится.

Но в индустрии крупные компании в основном используют верилог / SystemVerilog за некоторыми исключениями. Например Imagination Technologies использовала VHDL для PowerVR GPU, который стоял в первых четырех Apple iPhone, и в переписанном Appl-ом виде там до сих пор.

Даже американские военные и космические люди, которые изначально стандартизовались на VHDL, последние лет 10 все больше используют верилог. Некий контрактор на конференции DVCon в Сан-Хосе в 2010(?) году говорил что использует VHDL для RTL и SystemVerilog для тестбенчей (ранее использовал комбинацию из VHDL RTL и Specman e для верификации).

В общем моя позиция: на VHDL писать можно, но в большинстве крупных электронных компаний нынешние студенты будут писать на верилоге, поэтому для вводных курсов стоит учить его. Плюс в SystemVerilog быстрее водятся технологии верификации и лучше поддержка их тулами.

Учить два языка сразу - это имхо не очень эффективно, так как из-за нехватки времени получится, что студенты будут писать примитивные вещи и на одном, и на другом языках (типа мультиплексоры, FSM), но у них не хватит времени или внимание на освоение микроархитектурных задачек на конвейеры и FIFO, которые спрашивают на интервью.

AlexanderS

15.12.2023 10:48Вот, даже статью отыскал: https://habr.com/ru/articles/417953/

Вряд ли это странно, так как на VHDL очень много легаси тянется и всё же ещё много олдовых разрабов. Мне VHDL нравится за строгую типизацию, строгий контроль и стиль кода, хотя это уже вкусовщина, конечно. А молодежь, конечно, воротит нос от громоздких конструкций VHDL)

YuriPanchul Автор

15.12.2023 10:48В VHDL типизация немного бардачная. Зачем в std_logic столько значений? Почему есть не вполне совместимые пакеты numeric_std и std_logic_arith?

При этом в numeric_std, чтобы написать a = b + c и при этом сохранить перенос, нужно писать:

a <= std_logic_vector (resize (unsigned (b), 4) + resize (unsigned (c), 4))

AlexanderS

15.12.2023 10:48Даже спорить не буду в этом плане) Разрабы со стажем уже просто походили вдоволь по этим костыльным моментам и у выработали свои "шапочки" подключаемых библиотек "чтобы было всё нормально".

checkpoint

15.12.2023 10:48Вот тут есть кое-какие графики, правда на 2020 год.

YuriPanchul Автор

15.12.2023 10:48То что написано в этом тексте - это по моему персональному восприятию в Долине перекошенная картина, с желанием перетянуть одеяло на VHDL каким-то не вполне честным способом. Я подозреваю (я написал развернутый коммент выше) что в графиках от Siemens они приплюсовали все студенческие проекты, которые профессора дают в качестве курсовиков в Западной Европе и Южной Америке (в этих местах профессора любят VHDL). А смотреть нужно по дизайн-командам в электронных компаниях, особенно проектирующих массовые продукты, а также по стартапам.

checkpoint

15.12.2023 10:48Там на графиках Verilog и SystemVerilog представлены раздельно, если просуммировать, то Verilog явно в окажется в фаворитах. При чем последний в сторону роста популярности, в то время как у VHDL - спад. Где-то там же прочитал, что VHDL остался сейчас по большей части в военке и в космосе и то по причине норм и требований 20-30 летней давности, молодежь осваивает его с неохотой.

trawen

"В 1997 году в Scientific American появилась статья о реконфигурируемом компьютинге, согласно которой построенные на ПЛИС компьютеры открывали новую эру" - тут можно упомянуть и первый Российский компьютер на ПЛИС - Спринтер 1997

sappience

До, но и ПЛИС были не российские (Altera) и функциональность у них была вспомогательная, процессор был не ПЛИС, а вполне себе нативный Z84C15.