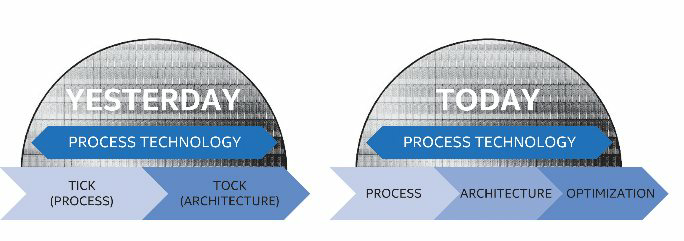

Теперь процессоры будут делать по циклу «процесс-архитектура-оптимизация»

Как публичная компания с более 10 млн $ в активах, акциями которой владеют более 500 акционеров, Intel предоставила Комиссии по ценным бумагам и биржам США ежегодный отчёт по форме 10-K. Особенный интерес в 150-страничном документе представляет страница 14, на которой Intel признаёт, что отказывается от стратегии «тик-так» в пользу новой концепции «процесс-архитектура-оптимизация».

Tick-Tock — модель развития микропроцессоров, которой Intel пользуется с 2007 года. В определённые промежутки времени технологии позволяют уменьшить размер элементов на плате, что позволяет снизить энергопотребление и уместить большее количество транзисторов на кристалле того же размера. Если можно уместить больше элементов, то возможна новая микроархитектура: добавляются новые команды, улучшается логика работы, увеличивается количество разных элементов.

Стратегия «тик-так» разделяет два процесса. За «тик» транзисторы становятся меньше. Изменения микроархитектуры есть, но они незначительны. «Так» означает создание новой микроархитектуры, то есть большие, иногда фундаментальные изменения в целях достижения больших приростов производительности.

Такими шажками Intel двигается уже почти 10 лет. Каждый из них занимает от года до полутора лет. Но в последнее время уменьшать техпроцесс становится всё сложнее. При переходе с 22 до 14 нанометров появились задержки в 6—9 месяцев. В это время приходилось повышать процент выхода работоспособных чипов с пластин до допустимого по себестоимости уровня. Закон Мура, который описывает удваивание количества транзисторов на кристалле каждые 24 месяца, приходится корректировать.

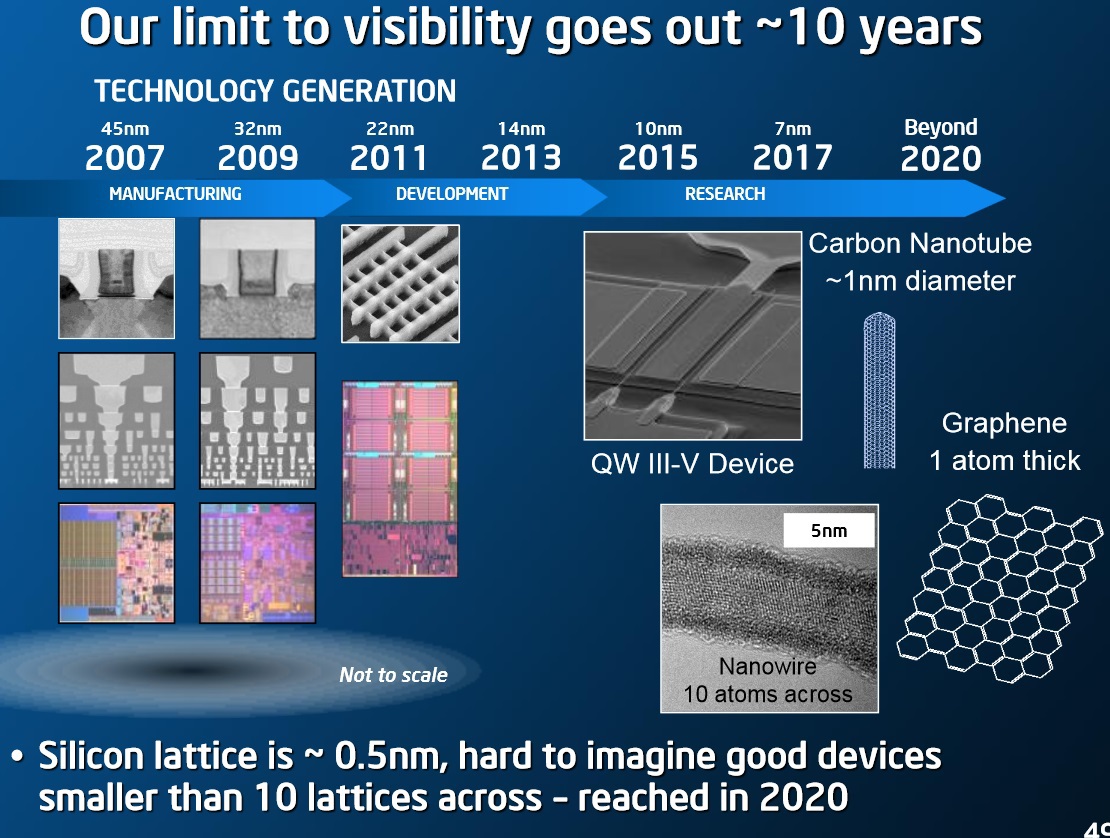

В дальнейшем планируется переход до 10, а затем и 7 и 5 нанометров. Достижение новых рубежей означает возможное использование литографии в глубоком ультрафиолете, Self-Aligned Quadruple Patterning (SAQP), отказ от кремния в пользу III-V полупроводников, карбоновых нанотрубок и графена.

Слайд из презентации год назад.

Документ для Комиссии по ценным бумагам и биржам затрагивает общий курс разработок Intel. Компания объясняет, что будет увеличено общее время использования продуктов на текущем техпроцессе в 14 нанометров и будущем в 10 нм. Но будет сохраняться рыночный темп выпуска новых продуктов. Как это будет достигнуто? Intel даёт изображение, которое в этом посте размещено до ката. В нём «тик-так» называется вчерашней технологией, а текущей реальностью объявлен цикл из трёх шагов «процесс-архитектура-оптимизация» (PAO).

14 нанометров помог отработать «тик» Broadwell, последователь 22-нм Haswell. Текущая микроархитектура Intel — это Skylake, шестое поколение Core, «так» 14-нанометрового техпроцесса. Его последователь, Kaby Lake, тоже будет 14-нанометровым, но будет предоставлять «значительные улучшения производительности по сравнению с семейством процессоров шестого поколения Core».

Достичь 10 нанометров может помочь упоминаемое в документе сотрудничество с ASML по исследованию фотолитографии в глубоком ультрафиолете, в том числе применимой к пластинам диаметров в 300 и 450 миллиметров. Intel пока что сохраняет лидерство: 14 нм были представлены в августе 2014 года, Samsung и TSMC подтянулись позже.

Ожидается, что 14-нанометровый Kaby Lake будет выпущен в этом году. Согласно текущим планам, продукты на 10-нанометровой микроархитектуре Cannonlake должны появиться в 2017 году. В трёхступенчатом цикле легко увидеть очевидные плюсы для конечного пользователя: одна и та же материнская плата может подойти для продуктов двух или более поколений.

pali

Samsung собирается делать 10 нм процесс на иммерсионной литографии, TSMC тоже, к 2017 году оба производителя будут массового производить пластины, Интел собирается к концу 2017 подключиться. Глубокий ультрафиолет эти компании собираются не раньше 7 нм внедрять, просто не на чем, EUV сканеров по миру есть не больше десятка, поправьте, если не прав.

Начиная с 90 нм где-то все используют 300 мм пластины, 200 мм экономически уже не выгодны. Я знаю про существование одного единственного 450 мм сканера от Никона, который стоит в университете штата Нью-Йорк (SUNY), это значит, что в скором будущем процесса на 450 мм пластины ещё не будет.

a5b

Да, однако год назад проходила информация о заказе на 15 NXE:3350B EUV (4-е поколение nxe):

http://www.kitguru.net/components/graphic-cards/anton-shilov/asml-sells-15-euv-lithography-scanners-possibly-to-intel/ ASML sells 15 EUV lithography scanners, possibly, to Intel — April 23rd, 2015; http://optics.org/news/6/4/31 22 Apr 2015

На октябрь 2015 — http://www.telegraaf.nl/dft/nieuws_dft/article24614198.ece/BINARY/Cijfers+derde+kwartaal+ASML.pdf — "NXE:3350B shipments — Target: 6 — First shipment of NXE:3350B in process with an additional 3 NXE:3350B systems on order with 2 shipments expected in Q4 2015 and 1 in 2016"

Несколько установок NXE:3300 (B) — 1 в Q1-Q2 2015 http://optics.org/news/6/10/10 в дополнение к 2+3+6 NXE:3300B https://staticwww.asml.com/doclib/misc/asml_20140306_EUV_lithography_-_NXE_platform_performance_overview.pdf#page=9 (часть из запланированных 3300 возможно обновили до 3350?) +6 NXE:3100.

В сентябре 2015 производитель EUV оценивал начало массового производства 7 нм с применением EUV в 2018 году:

http://www.semicontaiwan.org/zh/sites/semicontaiwan.org/files/data15/docs/3_20150825_semicon_taiwan_sept_3_web_site.pdf

pali

Если верить википедии, то по состоянию прошлого года было поставленио 16 систем: шесть 3100, восемь 3300 и две 3350.

Но NXE:3100 вряд ли будут использовать в массовом производстве, и кроме Интела ещё никто не купил достаточное количество сканнеров для тестирования процесса, к тому же 7 нм EUV будут сразу делать мультипаттернингом, если судить по результатам IBM/GloFo.

А так как 10 нм ожидается в 2017, то 7 нм, а значит и EUV, массово появится в 2019 или 2020. Причем производителей будет очень мало: Intel, TSMC, Samsung, и возможно GloFo с SK Hynix.