Британская корпорация ARM усовершенствовала гетерогенную вычислительную архитектуру ARM big.LITTLE, на которой основаны все ведущие микропроцессоры ARM начиная с Cortex-A7 (2011 год) — и вчера представила новую гетерогенную архитектуру DynamIQ big.LITTLE. На микросхемах выделено место для специальных аппаратных ускорителей приложений машинного обучения. Возможно, в будущем аппаратная поддержка нейросетей станет новым трендом среди разработчиков микропроцессоров и неотъемлемым качеством новых смартфонов.

Особенность архитектуры ARM big.LITTLE состоит в наличии процессорных ядер двух типов: относительно медленных, энергоэффективных (LITTLE) и относительно мощных и прожорливых (big). Обычно система активирует только один из двух типов ядер: только большие или только маленькие. Понятно, что фоновые задачи на смартфоне или другом устройстве удобно решать с маленькими ядрами, которые потребляют очень мало энергии. В случае необходимости процессор активирует мощные прожорливые ядра, которые в многопоточном режиме, работая сообща, демонстрируют особенно высокую производительность. В принципе, у всех ядер есть доступ к общей памяти, так что задачи можно ставить для выполнения на обоих типах ядер одновременно. То есть большие и маленькие будут переключаться на лету.

Подобная гетерогенная архитектура и переключение задач на лету с одного типа ядер на другой задуманы для создания динамического изменения мощности и энергопотребления процессора. Сама ARM заявляла, что в некоторых задачах та архитектура экономит до 75% энергии.

DynamIQ big.LITTLE — это эволюционный шаг вперёд. Новая архитектура позволяет задействовать разнообразные сочетания больших и малых ядер, которые раньше не были возможны. Например, 1+3, 2+4 или 1+7, или даже 2+4+2 (ядра трёх разных мощностей). Типичный смартфон будущего может иметь восьмиядерную систему на кристалле с двумя мощными ядрами, четырьмя средними и двумя низкопроизводительными ядрами для фонового режима.

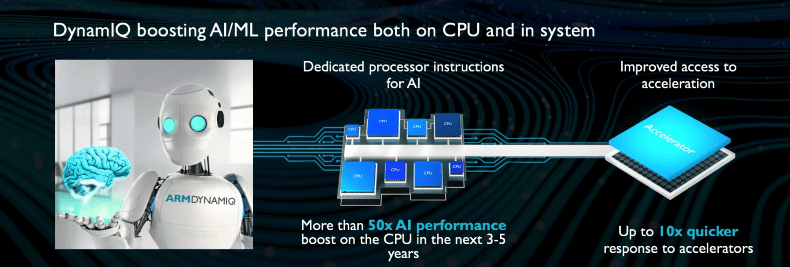

С аппаратной поддержкой машинного обучения и ИИ разработчикам станут доступны новые специальные процессорные инструкции (например, вычисления с ограниченной точностью). ARM обещает, что в следующие три-пять лет процессоры Cortex-A на новой архитектуре обеспечат до 50-кратной прибавки производительности в приложениях ИИ, в сравнении с нынешними системами на базе Cortex-A73 и ещё дополнительную прибавку за счёт встроенных ускорителей на микросхеме. Специальный порт доступа с низкой задержкой между ЦП и акселераторами имеет 10-кратную производительность.

Это означает, что на смартфонах будут гораздо лучше работать обученные нейросети, в том числе которые обсчитывают графику и видео, приложения компьютерного зрения и другие системы, которые обрабатывают большие потоки данных.

В каждом кластере может располагаться до восьми ядер разных характеристик. Это тоже можно использовать для ускорения приложений ИИ, по сравнению с нынешними системами. К тому же, переработанная подсистема памяти обеспечит более быстрый доступ к данным и улучшит энергоэффективность. Кстати, в кластеры ядер необязательно вообще включать ядра LITTLE со слабой производительностью, которые обычно используются в мобильных устройствах для сбережения заряда аккумулятора. Если вам нужна очень высокая производительность независимо от энергопотребления — никто не мешает делать кластеры из восьми больших ядер, и объединять их в особо мощные компьютерные системы. ARM считает, что это позволит расширить сферу применения процессоров ARM за пределы смартфонов.

Кластеры DynamIQ практически неограниченного масштаба с общей памятью — это предложение создавать мощнейшие вычислительные системы самого разного назначения.

Дополнительную гибкость в динамической подстройке мощности/энергопотребления даст функция индивидуального изменения тактовой частоты отдельных процессоров в кластере из множества процессоров ARM. Разработчики из Кембриджа считают, что это особенно важно в шлемах виртуальной реальности, которые длительные периоды времени находятся в состоянии низкого энергопотребления. Переходы процессора в одно из трёх энергетических состояний (ON, OFF, SLEEP) осуществляются гораздо быстрее, автоматически на аппаратном уровне.

В конце концов, продвинутая архитектура DynamIQ позволяет строить более надёжные системы с дублированием функций, что повышает уровень безопасности в автономных системах, которым нужно реагировать на сбои. Например, это системы компьютерного зрения в беспилотных автомобилях — Advanced Driver Assistance Systems (ADAS). Когда один кластер ядер выходит из строя или ускоритель сбоит — другой кластер автоматически берёт его функции на себя.

Процессорную архитектуру ARM применяют по лицензии в своих чипах многие производители, в том числе Samsung, Qualcomm, Nvidia, Intel и Apple (iPhone, iPad). Между 2013 и 2017 годами в мире было продано более 50 млрд микрочипов на архитектуре ARM, и английские разработчики надеются, что в ближайшие четыре года это число удвоится до более 100 млрд.

Большинство устройств на процессорах ARM не нуждаются в активном охлаждении. Компания уверена, что с увеличением мощности этих систем и переходе на архитектуру DynamIQ всё останется по-прежнему.

Комментарии (13)

HeavyRazzer

21.03.2017 17:58Многие современные SoC на архитектуре big.LITTLE страдают из-за не эффективного диспетчера задач (task sheduler) операционной системы, который должен решать на каком кластере и на каком ядре должен выполняться тот или иной поток. Так, либо что-то тяжелое случайно попадет на маломощный кластер, или ерундовая нагрузка застрянет на мощном.

Новая архитектура еще сложнее предполагается. Так что требования к качеству диспетчера задач будут еще выше. И зная, что производители устройств не первой категории часто ленятся оптимизировать прошивку под конкретное железо, с большой долей вероятности новая архитектура как минимум по первости будет работать весьма неэффективно. Даже более того, первые поколения, вполне вероятно, тоже могут работать не гладко, хуже уже вполне отточенному big.LITTLE…

К примеру, у Самсунга его первый двухкластерник (Эксинос 5420, если не ошибаюсь) в момент выхода по энергоэффективности проигрывал традиционной (на тот момент) архитектуре (Qualcomm Krait x4), не поражая при этом выдающейся производительностью.

Так что, новая архитектура в конечном итоге вполне может стать чем-то офигенным — идея-то хорошая.

wikipro

21.03.2017 20:08А архитектура VLIW (Эльбрус8/16C например) насколько лучше/хуже про сравнению с RISC для приложений машинного обучения? (при одинаковых тактовых частотах / разрядности)

Seven-ov

22.03.2017 08:52Я немного не понимаю, зачем этот огород из разных ядер (а то и из одинаковых ядер с разной частотой)

Неужели не проще и эфективнее сделать динамическое значение частоты процессора, динамическое число работающих ядер и отключаемые блоки этих ядер?

Sly_tom_cat

22.03.2017 10:58Мне кажется что как ни закручивай гайки многоконвейерной системе типа графического ускорителя, его все равно не заставишь работать с таким же потреблением как у одного простого конвейера.

Тут я думаю суть в том, что на большом можно работать с аппаратной поддержкой векторных операций, а на маленьком векторные операции будут эмулироваться циклами. Это конечно очень грубое описание сути, но что-то типа того там и реализовано (как я смог понять).

ilis

22.03.2017 10:16Что имелось в виду под «порт имеет десятикратную производительность». Поправьте пожалуйста.

А вообще правильный ход, именно что эволюционный.

Varfalomey

То-есть в текущей реализации нельзя больше двух кластеров? Как-же медиатек справился со своими 2+4+4?

maxzhurkin

В статье есть ответы на оба вопроса

Varfalomey

Еще раз перечитал. Вижу, что в текущей реализации три кластера быть не может, а заглянув на сайт ARM видно, что "In each of the combinations above, the big and LITTLE clusters can each have a maximum of four cores". То-есть больше восьмиядерника не получить. А в новой архитектуре предлагают то, что есть у mtk уже пару лет как.

maxzhurkin

Да. Прошу прощения, я имел в виду ту часть текста, в которой говорилось о будущих возможностях, восприняв её как текст о доступной реальности.

Возможно, это какой-то эксклюзив MediaTek, который перестанет быть таковым, возможно, вообще их разработка, переданная в ARM (разумеется, по соглашению).

HeavyRazzer

Больше двух выходит что можно (хотя название big.LITTLE и статьи от ARM намекают, что речь обычно идет как раз про 2 кластера). Впрочем, Медиатек как раз со своими тремя кластерами и не справился: батарею они едят с большим аппетитом, а плавностью и скоростью работы не отличаются (сужу по отзывам в сети и обзорам, сам я трехкластерник не щупал).