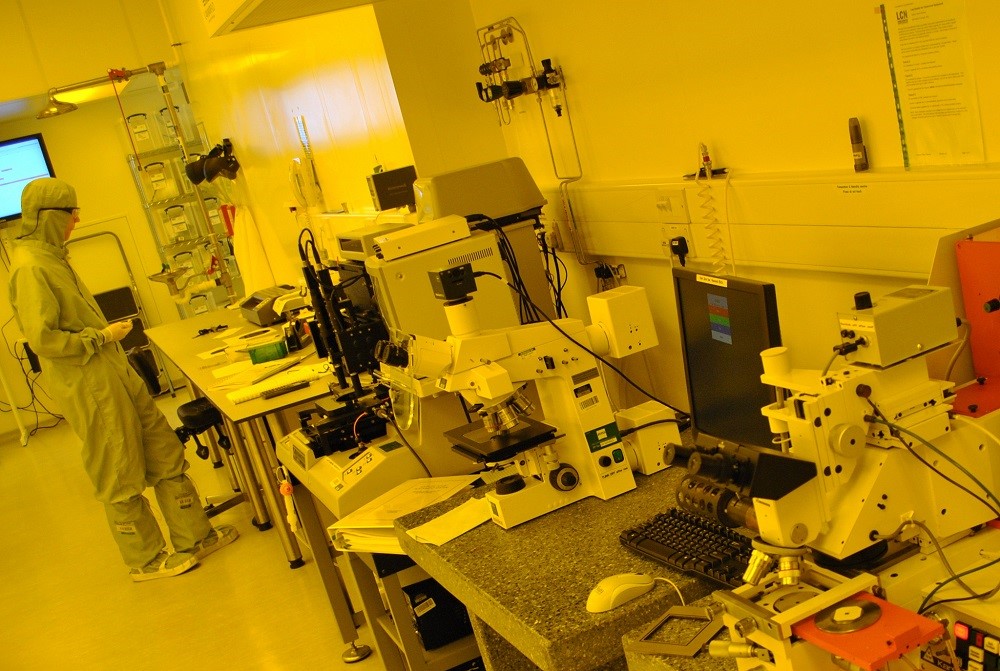

/ фото UCL CC

7-нм техпроцесс TSMC

Чип, напечатанный TSMC в начале месяца, выполнен по 7-нм техпроцессу второго поколения, который претерпел ряд изменений, по сравнению со своим предшественником.

В основе 7-нм техпроцесса первого поколения TSMC лежит DUV-литография с «глубоким» ультрафиолетовым излучением. При этом используется иммерсионная литография и сканеры с длиной волны 193 нм. Первый чип по этой технологии в компании напечатали еще в апреле этого года. А в мае TSMC начали производить 7-нм чипы для Apple. Новыми микросхемами снабдили систему на кристалле A12 Bionic. Она уже отвечает за работу последних смартфонов ИТ-гиганта: iPhone XR, XS и XS Max.

Всего же заказы поступают от двух десятков компаний, включая Bitmain, NVIDIA и Qualcomm. Крупным клиентом TSMC также является AMD — на основе 7-нм техпроцесса построены процессоры Vega 20 и серверный ЦП Epyc.

В начале этого месяца TSMC сообщили, что им удалось усовершенствовать свой 7-нм техпроцесс. Инженеры использовали для разработки чипов фотолитографию в «жестком» ультрафиолете (EUV). В этом случае длина волны оказывается в двадцать раз меньше и составляет 13,5 нм. Переход на EUV (совместно с развитием методов моделирования и обнаружения дефектов и других процессов) снизил энергопотребление производимых микросхем на 8% и увеличил плотность транзисторов на 20%, по сравнению с технологией первого поколения.

Пока с помощью EUV реализовывают только четыре некритичных слоя чипа. Сперва компания хочет освоить технологию, а потом уже использовать ее для изготовления больших объемов продукции (пока выход годных устройств довольно низок).

Кто стал первым клиентом, получившим новые чипы, компания-производитель не раскрывает, однако есть предположение, что им стала все та же Apple. Также компания разрабатывает специализированную версию обновленного техпроцесса для автоиндустрии.

Когда ждать 5-нм чип

В TSMC планируют начать рисковое производство 5-нм чипов уже в 2019 году. Для создания 5-нанометровых микросхем компания задействует EUV, но с помощью этого метода фотолитографии будут производиться четырнадцать слоев чипа, вместо четырех.

К тому времени тайваньская компания планирует обкатать технологию EUV и увеличить производственные мощности. Компания уже объявила о начале строительства новой фабрики, на которой будут создаваться чипы. Его возведут в Южном научном парке Тайваня.

У 5-нм чипов есть ряд преимуществ, по сравнению с 7-нм. При одинаковой сложности, плотность транзисторов в обновленных микросхемах будет в 1,8 раз выше, а тактовая частота увеличится на 15%. При этом 5-нм процессор будет потреблять на 20% меньше энергии, чем 7-нм. Однако перед запуском производства, компании нужно решить ряд трудностей.

Первая из них — нехватка инструментов для разработки. Необходимый пакет проектирования EDA для 5-нм техпроцесса подготовят в ноябре этого года. Однако библиотеки для блоков PCIe 4.0 и USB 3.1 окажутся готовы только летом будущего года.

Еще одна проблема — высокая стоимость разработки. По оценкам экспертов, разработка системы на кристалле по 7-нм технологии обходится где-то в 150 млн долларов. В случае с 5-нм техпроцессом стоимость увеличивается до 250 млн долларов. Это значит, что цена готовой продукции в итоге вырастет, и в использовании этих чипов будут заинтересовано меньше компаний-клиентов. Потому нет гарантий, что производство микросхем по 5-нм техпроцессу окупится.

Как дела у других компаний

В одном из прошлых постов мы говорили, что производитель интегральных микросхем GlobalFoundries остановил разработку своих 7-, 5- и 3-нм техпроцессов из-за финансовых трудностей. Вместо этого, организация переключилась на совершенствование 14-нм и создание встроенных запоминающих устройств.

/ фото Mr Seb CC / 22-нм кремниевая пластина Intel

Intel тоже проигрывают TSMC в скорости разработки новых техпроцессов. Компания опять перенесла релиз 10-нм микросхемы, а в сентябре и вовсе заявила, что возвращается к 22-нм (хотя и для реализации чипсетов), чтобы «разгрузить» производственные мощности. Однако здесь справедливо будет отметить, что 7-нм у TSMC и 10-нм у Intel считаются одинаковыми проектными нормами в контексте плотности и размеров транзисторов.

Единственным конкурентом TSMC на 7- и 5-нанометровом «поприще» пока видится Samsung. Запуск 7-нм чипов южнокорейский гигант запланировал на первую половину следующего года. Микросхемы по проектным нормам 5-нм Samsung начнут производить тоже в 2019, но когда стартуют их продажи, пока неизвестно.

P.S. О виртуальной инфраструктуре и работе с ПД — в нашем Telegram-канале:

Комментарии (41)

Andriy1218

21.10.2018 16:08А ведь размеры кристаллической решётки кремния 0.54307 нм. В школе, когда изучал физику, считал маленькие размеры атомов большой проблемой, из-за которой нам сложно понять всю эту физику. А теперь при производстве транзисторов мы почти подошли к минимальному пределу размеров и теперь атомы кажутся не такими и маленькими.

KonkovVladimir

21.10.2018 16:28+3Проектные нормы опосредованно связаны с линейными размерами, скорее с площадью ячейки статической памяти. habr.com/post/423575

Andriy1218

21.10.2018 19:12Я понимаю, в свое время читал эту статью.

Но все равно, некоторые расстояние в транзисторах из-за квантовых эффектов уже особо не уменьшишь. Понятно, что мы ещё какими-то хаками будем уменьшать техпроцесс, но предел уже близко.

KonkovVladimir

21.10.2018 20:11+2Это понятно. Я еще в 1989г читал прогноз, что к ~2012-2014г будет достигнут предел по длине канала в 20нм, меньше туннелирование не дает.

Garbus

22.10.2018 03:45Квантовые эффекты это одна сторона, но как дела с радиационной стойкостью? Ведь «капля никотина» меньше не становится, а лошадь до размеров хомячка почти уже уменьшили. :)

willyd

22.10.2018 05:20Там где нужна радиационная стойкость никто не будет вешать мессенджер на электроне.

Garbus

22.10.2018 10:12Это к тому что радиация на Земле есть везде. Любой державший в руках счетчик радиации неплохо представляет, что заряженные частицы не редкость. А так как речь идет о вполне себе «бытовых» чипах, то и стойкость какая-то должа обеспечиваться.

acmnu

22.10.2018 11:41Как-то на IBM мероприятии они хвастались, что на одном из марсоходов их Power толи 3 толи 4. А это уже были времена Power 7. Типа только они смогли предложить относительно мощный процессор общего назначачения на большом техпроссе и хорошо защищенный от космической радиации, как физически, так и схемотехнически. Говорят, что их системы отслеживания ошибок позволяют процессору повторить инструкцию прерваную из попадания высокоенергитической частицы извне (в разумных приделах, разумеется). Они даже статистику приводили по этому поводу, но я уже подзабыл цифры.

amartology

22.10.2018 14:24толи 3 толи 4. А это уже были времена Power 7

Это не проблема меньшей стойкости новых техпроцессов, это проблема сроков сертификации микросхем для ответственных применений. Сделать радстойкий (для космоса) процессор можно на вообще любой технологии 350 нм и ниже от любой фабрики.

Прямо сейчас уровень проектных норм космических процессоров — 65-45 нм, первые изделия по 28-20 нм появятся через пару лет.

Говорят, что их системы отслеживания ошибок позволяют процессору повторить инструкцию прерваную из попадания высокоенергитической частицы извне

Такое и на коммерческом процессоре можно сделать (и активно делается). Специально спроектированные процессоры могут не повторить инструкцию, а просто работать дальше, скорректировав ошибку за счет встроенного резервирования.

amartology

22.10.2018 14:19Для «земных» уровней радиации там все хорошо с радиационной стойкостью, можете не переживать.

Garbus

23.10.2018 07:24Тут не столько переживание, сколько общий интерес. Все же статьи про ускорители и детекторы попадаются порой, вот и возникают мысли на подобную тему.

amartology

23.10.2018 15:35На ускорители и детекторы cutting edge технологии не попадают, потому что во-первых, слишком дорого делать по ним мелкосерийные схемы, во-вторых, сроки разработки и эксплуатации чипов очень большие, и пересаживаться с однажды выобранной технологии никто не будет, а в-третьих, там, где действительно нужна высокая радстойкость — это аналоговые схемы, а не цифра, и там передовые проектные нормы натурально ни для чего не нужны.

А цифровая обработка данных идет на серийных серверах в безопасном месте.

Garbus

24.10.2018 12:55Как-то разошлись мы во мыслях, каждый о своём. ;)

Я вовсе не электронику сенсоров имел в виду, она может быть хоть ламповой, если в конкретном месте это наилучший вариант окажется.

Статьи же упомянул лишь к тому, что они наводят на мысли о частицах летающих как и когда им вздумается.

amartology

24.10.2018 13:22А, если так, то есть довольно хорошая статистика по сбоям в суперкомпьютерах, как правило построенных на самых современных процессорах (спойлер: сбои есть, и с ними борются, но в пересчете на персоналку там вероятность один сбой во много лет), и неплохая статистика по трансатлантическим авиаперелетам (несколько сбоев на самолет за рейс, там с ними тоже борются).

Главное — не ставить суперкомпьютер в метро и помнить о том, чтобы в материале корпуса микросхемы не было источников альфа-частиц.

amartology

22.10.2018 14:18Как там дела с радиационной стойкостью, мы вряд ли узнаем в обозримом будущем, потому что тратить 250 миллионов долларов на разработку чипа, которого потом будет нужна одна-две пластины, никто не станет, это неоправданно дорого.

Нынешние и переспективные разработки радстойких микропроцессоров — это уровень 28-20 нм, и там все с радиационной стойкостью довольно неплохо. Особенно если учесть, что в FDSOI технологии (на которой делается перспективный европейский процессор DAHLIA) нет тиристорного эффекта.

Ну и в целом, с радиационной стойкостью у маленьких проектных норм все обычно хорошо, хуже как раз со старыми нормами и с теми новыми процессами, где используются большие размеры (например, в высоковольных схемах).

sielover

21.10.2018 17:22Ну все-таки у кремния не простая кубическая решетка, а межатомное расстояние вдвое меньше, чем 0.543 нм.

Так что, скажем, 5 нм в затворе транзистора — это не 9-10 атомов, а 18-19. Еще есть куда двигаться!

kompas_3d

21.10.2018 20:38+2Вы не учитываете, что вероятность дефекта очень сильно вырастает.

springimport

22.10.2018 16:21Наверное поэтому теперь появились i9, из неудавшихся которых выйдут i7, i5, i3.

agat000

22.10.2018 12:39ИБМ ещё с алмазными полупроводниками экспериментирует, вроде бы. Там размер атомов ещё меньше.

Блин, ум за разум заходит, как представляю транзистор, размером в десяток атомов. Там же ещё легирующие элементы, их вообще считанные атомы получаются на элемент. Колдунство какое то.

amartology

22.10.2018 14:36Туннельный эффект говорит, что двигаться особенно некуда. Из-за него уже довольно давно пришлось заменить технологически удобный SiO2 в подзатворном диэлектрике на технологически неудобный, но более толстый оксид гафния.

Про фокусы с долегированием германием и прочими растянутые решетки для преодоления падения подвижности я даже начинать не хочу.

theschmidts

21.10.2018 17:10+1Про литографию, немного странно: 193 нм используют уже много лет, скорее бы стоило написать, что она иммерсионная и с четырехкратным экспонированием.

И, конечно, не переход к EUV позволил улучшить характеристики транзисторов, а просто набор performance knobs: различных приемов оптимизации структур, распределений стресса и примесей и тп.

EUV дает чисто финансовый плюс: можно вместо сложной многократной экспозиции сделать все за один раз. Но процесс крайне медленный и дорогой, так что пока не ясно, войдет ли он в технологию действительно, хотя и тайваньцы и корейцы и американцы делают на него ставку.

sim2q

21.10.2018 22:04А как решили поглощение столь жесткого УФ в материале?

Что там с «оптикой»? И наверное уже не в воздухе?

MikeVC

21.10.2018 18:39Тут уже писали что это размер «плавников» у транзисторов.

А сам транзистор далеко не 5нм и даже не 14…

Так что никакого прорыва нет.

theschmidts

22.10.2018 03:33Ну в той статье, неплохой кстати, это место было вообще не в тему: ширина фина к нормам производства и плотности транзисторов не имеет отношения (вернее имеет, но очень сложное): она определяется ограничениями, связанными с квантовой физикой (которая определяет распределения плотоности тока в канале в таким маленьких системах) и механическими свойствами: фин надо делать повыше, но если он слишком тонок, он просто сломается.

Nick_Shl

22.10.2018 04:29+1А где там 7 нм? Читаем википедию по ссылке из статьи:

EUV-литография делает возможной печать линий шириной до 30 нм и формирование элементов структуры электронных микросхем размером менее 45 нм

Т.е. 7 нм нет даже близко. Кроме того, было 7 нм, стало 7нм, но при этом "снизилось энергопотребление производимых микросхем на 8% и увеличилась плотность транзисторов на 20%". Как?

Видимо нынешние нанометры какие-то неправильные, подпорченные маркетологами.

willmore

22.10.2018 10:08Все правильно, подпорченные маркетологами. По сути показывают плотность упаковки ячейки памяти.

HexMaster

22.10.2018 11:19Вот вырасту большой, изобрету 3D-принтер, который будет печатать объёмные микросхемы, а не эти плоские «блины».

vodopad

Уже 5нм на подходе… Предел скоро наступит. Очень интересно, как дальше будут развиваться события.

mirwide

Скоро не наступит

Закон Мура из линейного превратится в асимптотический, каждое дальнейшее продвижение будет требовать бОльших вложений средств и времени. Со стремлением к пределу в бесконечности.

Будут поиски диэлектриков с меньшим размером кристаллической решетки, есть технологии изменения размера и вида кристаллической решетки под давлением, не обратимые. По принципу получения алмазов и металлического водорода. И даже изменения размера атома — переход валентных электронов на другую орбиту.

Iamkaant

Изменение размера атома? Ссылочку не дадите?

kalininmr

впринципе уже порядка нескольких ангстремов — невозможно.

mirwide

ФИЗИКА ВЫСОКИХ ДАВЛЕНИЙ ст.81

Iamkaant

Спасибо за ссылку, статья интересная. Но речь тут не о изменении размера атома, а о смене координации атомов, кристаллической решетки.

mirwide

AnthonyDS

Это к создателю)))

arantar

И в итоге приведет к удорожанию конечной продукции, но бесконечно нельзя цены поднимать.

SanekPlus

Ну это в Западном «рыночном» обществе как правило приводит к удорожанию цены. Китай несколько другая экономика. Он может субсидировать это производство различными путями, от прямых разовых «чеков» на закупку оборудования, до снижения пошлин на сырье для этой отрасли, а также налогов и даже ставку кредита, и при этом они продолжают резво занижать юань, так что цена в будущем может даже не измениться. И если запад делает подобное эпизодически, то Китай это делает постоянно и систематически обеспечивая конкурентное преимущество своим отраслям при первой же возможности ни с чем не считаясь.

Areso

Как говорил старик Эйнштейн, все в мире относительно.

www.xe.com/currencycharts/?from=USD&to=CNY&view=10Y

За десятилетний отрезок времени я вижу максимальные колебания аж в целых 15%. Такая «резкость» даже не снилась крупнейшему государству в мире) Можно только мечтать.

SanekPlus

Я сказал «резво», а не «резко» :). Китайцы молодцы снижают когда надо для экономики (например сейчас), а не просто когда вздумается. :)

p.s. Минус не я вам поставил. :)