В этой заметке я кратко опишу, что входит в СнК HR5000 и его процессорное ядро, покажу фотографии двух из ключевых разработчиков линеек MIPS 4K и 5K, а также расскажу, как вы можете поиграться дома на плате ПЛИС с «потомком младшего брата» этого компьютера — 32-битным ядром MIPS microAptiv UP, код которого на языке описания аппаратуры Verilog был основан на MIPS 4KEc.

Японское аэрокосмическое агентство JAXA лицензировало процессорное ядро MIPS 5Kf у американской компании MIPS Technologies. Это произошло еще в 2000-е годы. Группа, которая разработала это ядро, существует в разных конфигурациях уже 40 лет:

- Сначала в 1978-1984 MIPS был проектом в Стенфорде, под руководством Джона Хеннесси. На успехе от этого проекта Хеннесси стал автором самого известного учебника по компьютерной архитектуре и в некоторый момент — президентом Стенфорда.

- Затем, в 1984 году, MIPS стал коммерческой компанией — MIPS Computer Systems. В этом же году коммерциализировался и ARM. В 1991 году MIPS выпустил первый в мире 64-битный микропроцессор — MIPS R4000.

- После этого MIPS был поглощен Silicon Graphics и в 1990-х использовался внутри графических станций, на которых в Голливуде делали первые фильмы с реалистичной графикой («Парк Юрского Периода»).

- В 2000-е группа выделилась в компанию MIPS Technologies и в частности спроектировала процессор для JAXA. Штаб-квартира MIPS находилась в Калифорнии, часть разработчиков MIPS 5Kf сидела в европейском отделении MIPS в Копенгагене.

- В 2012 году MIPS Technologies купила британская компания Imagination Technologies, которая прославилась как разработчик GPU внутри ранних Apple iPhone.

- В 2017 году Apple кинула Imagination и после некоторых пертурбаций технологии и часть группы MIPS интегрировались в компанию Wave Computing, стартап, который разрабатывает чип для ускорения нейросетей.

- Чип Wave Computing является комбинацией из кластера 64-битных процессоров MIPS I6500, матричного умножителя на основе систолического массива а-ля Google TPU, а также процессора потоков данных (dataflow processor) на основе устройства с крупнозернистой реконфигурируемой архитектурой (Coarse-Grained Reconfigurable Architecture — CGRA). Классические процессоры в кластере I6500 загружают матричный умножитель и процессор потоков данных данными, матричный умножитель обеспечивает вычислительную плотность, а процессор потоков данных по задачам находится посередине между классическим процессоров и матричным умножителем — он более гибкий, чем умножитель, и более производителен, чем классический CPU.

Вот я сфотографировался с одним из двух ключевых разработчиков линейки MIPS 4K и 5K — Larry Hudepohl, Ларри Хьюдепол (справа в красной рубашке). Ларри начинал свою карьеру в Digital Equipment Corporation (DEC) как дизайнер процессоров для MicroVAX. Потом Ларри работал в небольшой компании Cyrix, которая в конце 1980-х бросила вызов Интелу и сделала FPU сопроцессор, который был совместим Intel 80387 и при этом был его на 50% быстрее. Потом Ларри проектировал чипы MIPS в Silicon Graphics. Когда MIPS Technologies отделилась от Silicon Graphics, Ларри вдвоем с Райаном Кинтером начали первый продукт независимого MIPS — MIPS 4K, который стал основой линейки, доминирующей в домашней электронике 2000-х (DVD-плееры, фотокамеры, цифровые телевизоры). Потом MIPS 5K полетел в космос — его использовало японское космическое агентство JAXA. Потом Ларри на должности VP Hardware Engineering руководил разработкой следующих линеек, а сейчас работает над новыми архитектурами Wave акселератора:

Теперь вернемся к процессору в Хаябусе-2 (в Хаябусе-1 он другой). Вот datasheet на процессорное ядро MIPS64 5Kf и страничка с данными системы на кристалле HR5000. Отметим несколько интересных моментов.

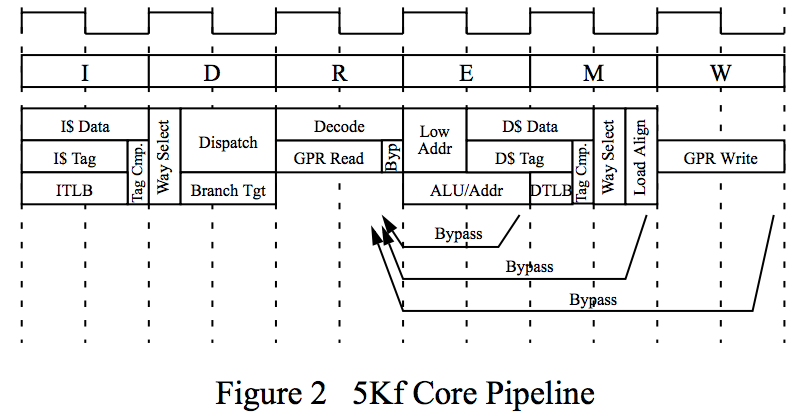

Прежде всего, MIPS 5Kf — конвейерный процессор. Если вы незнакомы, как это работает, то самый простой способ познакомиться — это проштудировать седьмую главу книжки «Цифровая схемотехника и архитектура компьютера» Дэвида М. Харрис и Сары Л. Харрис, последнюю версию перевода которой на русский язык которой можно скачать здесь или здесь). При этом конвейер в MIPS 5Kf отличается от классического конвейера MIPS из Харрис & Харрис. Те из вас, кто читали Х&Х, могут посмотреть на различия и догадаться почему:

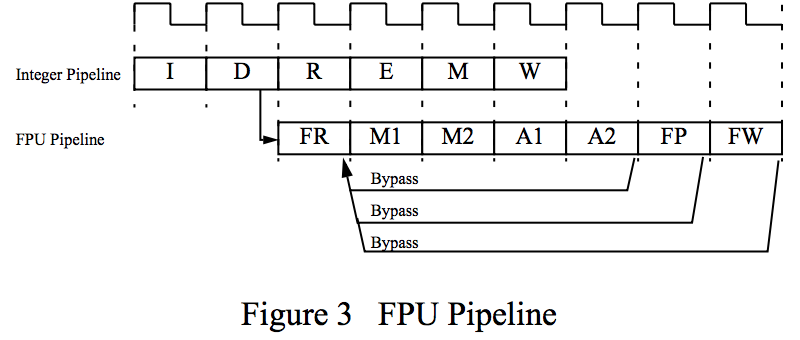

Конечно же — у MIPS 5Kf не пять стадий конвейера, а шесть, с дополнительной стадией Dispatch. Эта стадия нужна, чтобы сделать MIPS 5Kf ограниченно-суперскалярным. Он может выполнять не только операции одна за другой в конвейере, но еще и может выполнять операцию с плавающей точкой одновременно с целочисленной операцией или с операцией работы с памятью (загрузка или сохранение). Стадия Dispatch запускает сопроцессор с плавающей точкой, у которого есть собственный семи-стадийный конвейер:

А вот справа на фото — Даррен Джонс, Darren Jones, разработчик FPU в MIPS 5Kf. Буква «f» в «5Kf» означает именно то, что у него есть плавающая точка:

Вот в этой табличке вы можете увидеть, сколько циклов требуют разные операции в FPU и как часто (repeat rate) их можно запускать в конвейер. Например умножение одинарной точности требует четырех циклов, но при этом вы можете запускать в конвейер новое умножение каждый цикл. Так что FPU может одновременно обрабатывать четыре умножения одинарной точности на каждой стадии обработки. А вот умножение двойной точности требует пяти циклов, и запускать его можно только с паузой в цикл. Сложная операция взятия квадратного корня двойной точности требует аж 32 циклов, причем запустить новое взятие квадратного корня можно только через 29 циклов. Вот так оптимизируется вычисление координат корабля и формул его движения в космическом пространстве:

Хаябуса-2 использует конфигурацию MIPS 5Kf с раздельными 32-килобайтными кэшами инструкций и данных. При этом из краткого описания HR5000 непонятно, использует ли он четырехканальный кэш по 8 килобайт — или двухканальный кэш по 16 килобайт. Вы можете почитать, как работают эти кэши как в Х&Х, так и в моей старой презентации про кэши, а также в полезной книжке See MIPS Run Linux 2nd Edition by Dominic Sweetman:

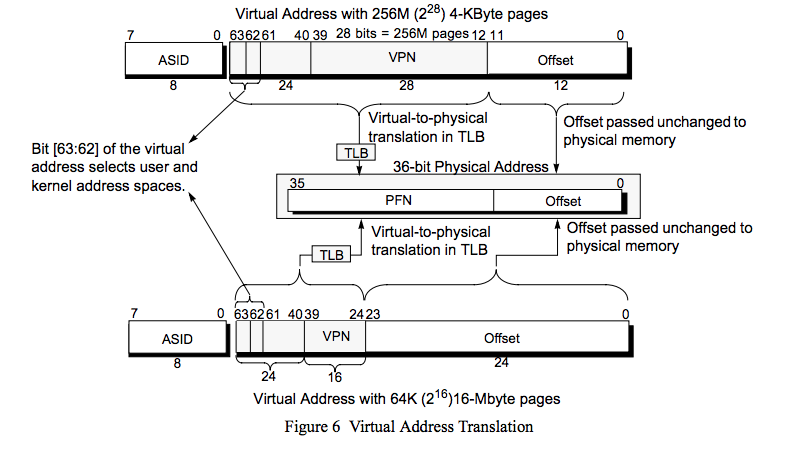

На Хаябусе-2 также стоит устройство управления памятью (Memory Management Unit — MMU), с буфером ассоциативной трансляции адресов (Translation Lookaside Buffer — TLB). TLB — это универсальное средство быстрого преобразования адресов из виртуального в физические. TLB позволяет:

Cкрывать память операционной системы от непривилегированного кода.

Защитить пользовательские программы друг от друга.

Предоставить доступ программы к объему виртуальной памяти, который превосходит объем физической оперативной памяти.

Адресовать бОльшую по размеру физическую память, чем доступно виртуальных адресов.

Разместить программу в любой части физической памяти.

Позволяет нескольким регионам памяти выглядеть как последовательный кусок.

Позволяет подгружать куски программы с внешнего устройства по необходимости.

TLB также ассоциирует с адресом разные атрибуты: запрета чтения, записи и исполнения, а также атрибуты кэшируемости и когерентности.

Атрибут кэшируемости нужен, чтобы показать процессору, где находится адресное пространство для следующего уровня кэша, а где — для решистров ввода-вывода, которые нельзя кэшировать.

Атрибуты когерентности нужны для совместной работы нескольких процессорных ядер, в каждом из которых свой кэш первого уровня, а все вместе они используют общий кэш второго уровня.

TLB может хранить индикатор, что на страницу с данным адресом происходила запись. Это помогает при своппировании, загрузке-выгрузке страниц памяти в системах с объемом физической памяти меньшей, чем нужно приложению для адресации всех кусков своего кода и данных виртуальными адресами.

Вот так выглядит трансляция 64-битного виртуального адреса в 36-битный физический на MIPS 5Kf. Зачем на Хаябусе-2 64-битный процессор с 36-битными физическими адресами? Я подозреваю, что Хаябуса-2 делает фотографии и должна обрабатывать изображения, для чего нужно много памяти. Возможно для некоторых алгоритмов 64-битная арифметика и 64-битные обмены с кэшем (или 64-битные некэшируемые обмены с памятью) что-то улучшают, и оно оказывается полезным в космосе. Но точно не знаю, наверное нужно спросить у Zelenyikot и amartology, которые знают про космос больше, чем я.

Вы можете почитать про TLB в Х&Х и See MIPS Run, но есть нюанс: обе книжки описывают, как выглядит TLB с точки зрения программиста. Но с точки зрения железячника проектировщики процессора обманывают программиста, показывая ему TLB как одну ассоциативную таблицу трансляций, при том, что на самом деле внутри TLB Хаябусы-2 таблиц три: микро-TLB инструкций, микро-TLB данных и общее (Joint TLB). Сначала устройство управления памятью ищет в ITLB и DTLB, и только если не находит, берет из JTLB. Это стоит процессору лишних 2 цикла. Также см. мою старую презентацию про TLB:

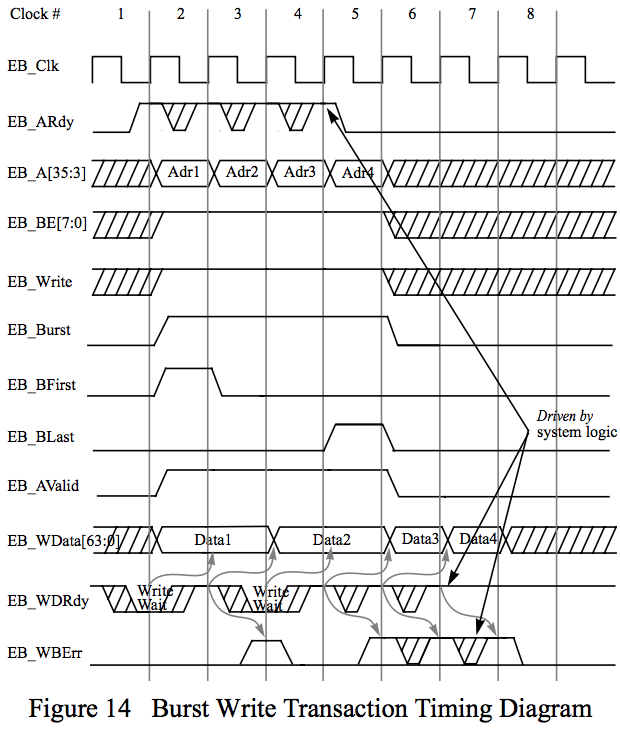

Интерфейс между кэшами первого уровня и контроллером памяти у MIPS 5Kf у Хаябусы-2 называется EB (произносится И-Би). Это сокращение от «External Bus». Он похож на AHB и AXI, и позволяет делать burst, выдавать из кэша или заливать в кэш из памяти целую строку, с помощью трансферов в последовательных циклах.

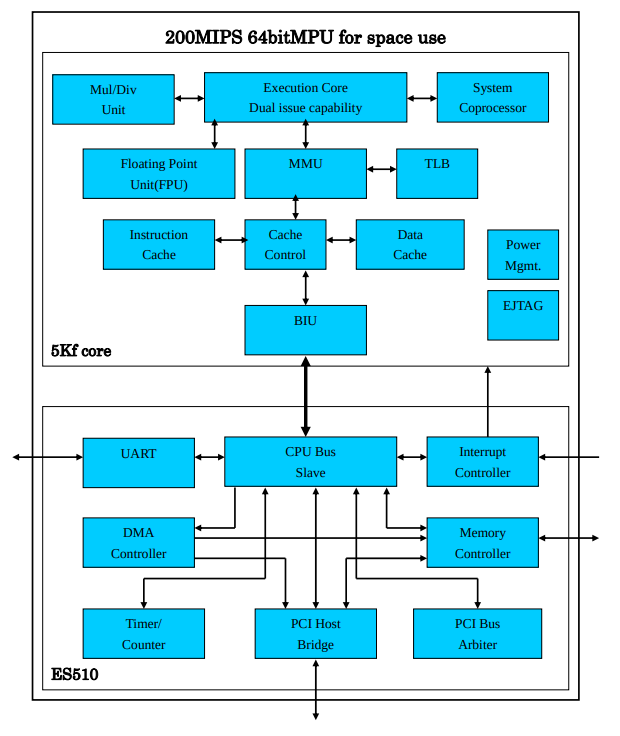

Вне процессорного ядра у HR5000 есть контроллер прерываний, модуль UART, контроллер прямого доступа к памяти, таймеры и контроллер PCI:

Для работы в космосе чип должен быть защищен от радиации. Я не специалист по радиационной защите, для этого на Хабре есть amartology, но знаю, что такая защита может делаться как на уровне физической технологии производства, так и на уровне разнообразных проверок ECC, и даже на уровне архитектуры, с троированием и т.д. Создатели системы на кристалле HR5000 решили применить обычный принятый в коммерческих применениях маршрус RTL2GDSII, синтез графа из логических элементов из кода на языке описания аппаратуры Verilog. Однако после получения такого графа (netlist), они модифицируют его с помощью специальной библиотеки примитивов hardness-by-design (HBD) (никогда такое не использовал, поэтому любое разъяснение в комментах приветствуется):

Так как MIPS 5Kf написан на Verilog, его можно превратить не только в нетлист, и не только в маску для производства чипа на фабрике, но и в конфигурацию ПЛИС. К сожалению исходники MIPS 5Kf не лежат в открытом доступе, но в открытом доступе лежат исходники потомка его «младшего брата», 32-битного процессора MIPS 4K. Этот «потомок» называется MIPS microAptiv UP, и его базовая конфигурация входит в пакет MIPSfpga. Код MIPS 4K/4KEc/microAptiv UP/M5150 (это все прогрессирующие версии линейки) тоже в свое время писали Ларри, Райан и Даррен.

Вы можете поиграться с конвейером, кэшами, устройством управления памятью и прерываний ядра MIPS microAptiv UP, запустить его на симуляторе или плате с ПЛИС/FPGA. Для этого достаточно загрузить пакет MIPS Open™ FPGA Getting Started Package, вместе с MIPS Open™ FPGA Labs, и (это важно!) дополнить его MIPSfpga+. В последнем есть лабы про конвейер, кэш и устройство управления памятью.

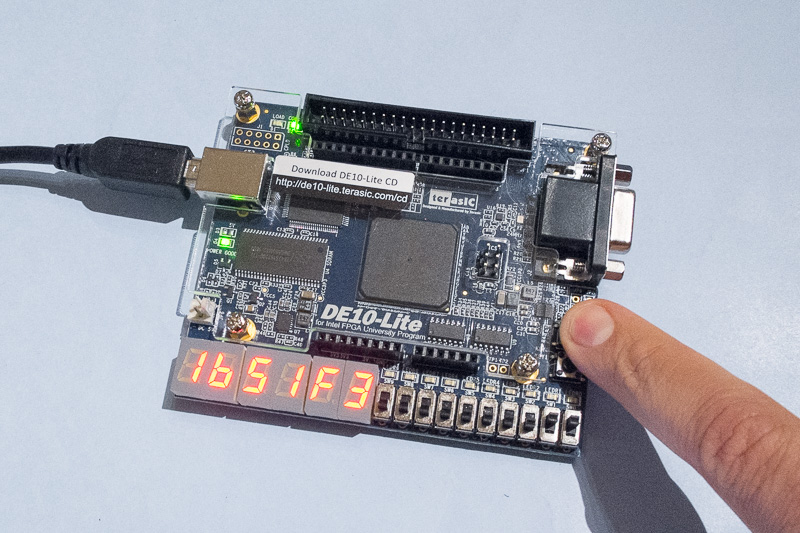

Синтезировать и запустить процессор MIPS microAptiv UP можно на недорогой плате за $85 (академическая цена $55):

Для работы с пакетом MIPSfpga/MIPSfpga+ нужно знание языка описания аппаратуры Verilog, принципов проектирования на уровне регистровых передач и умение писать на ассемблере MIPS.

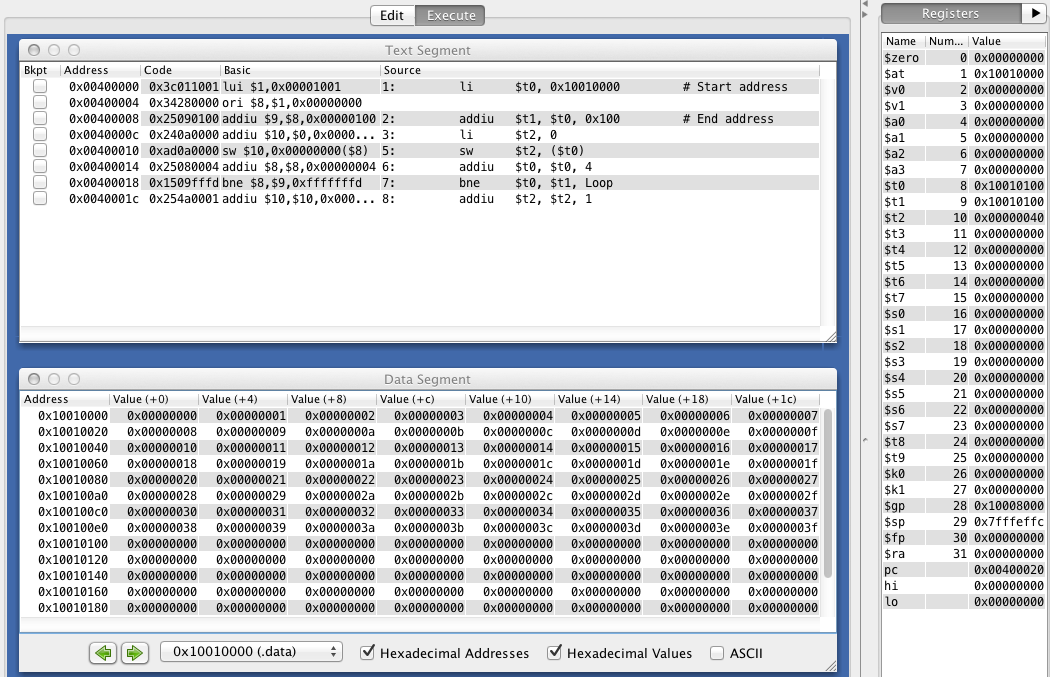

Ассемблер MIPS выучить проще всего. Для этого можно скачать симулятор MARS (MIPS Assembler and Runtime Simulator). Пользоваться им можно научиться за 5 минут, фактически в нем три кнопки — ассемблировать, запустить, запускать пошагово:

Потом можно провести день, упражняясь в писани на ассемблере по книжкам Харрис & Харрис и See MIPS Run Linux.

Если вы совсем ничего не знаете про разработку цифровых схем вообще и на языке описания аппаратуры в частности, вы можете начать с роснановского онлайнового курса для школьников, из трех частей: «От транзистора до микросхемы», «Логическая сторона цифровой схемотехники», «Физическая сторона цифровой схемотехники»). Потом можно изучить Verilog по Х&Х и понять что есть процессор по упрощенному процессору schoolMIPS.

Если вы заинтересовались этой темой и хотите участвовать в работе над MIPS Open (в рамках которого было открыто ядро MIPS microAptiv UP), напишите в комментариях. Роснановцы также проводят семинар для школьников по цифровому проектированию 17-19 апреля, где будет речь в том числе и об этом космическом процессоре. Хаябуса-2 бомбардировала Рюгу не зря — это в том числе повод для российских школьников и студентов узнать, что у нее внутри.

Комментарии (47)

amartology

09.04.2019 09:10+5С точки зрения радиационной стойкости, в этом чипе применены два основных приема:

1) специальная библиотека логических элементов. Код на верилоге при этом пишется абсолютно обычный, но когда он транслируется в нетлист (и потом в топологию) вместо обычных инверторов, ИНе, триггеров и т.д. ставятся специальные, защищённые от радиации. В таких эленметнтах может быть другая схемотехника (больше транзисторов для достижения внутреннего резервирования или компенсации каких-то эффектов) и другая топология (специальная форма затворов транзисторов, охранные кольца из легированных слоев). На уровне элементов обычно делается защита от полной поглощенной дозы и от тиристорного эффекта. Кроме того, рискну предположить, что в категорию «элементы» для простоты картинки могли быть засунуты, например, кэши со специальными радстойкими ячейками или даже с ECC.

2) У чипа более устойчивый к полной дозе радиации корпус. Это достигается за счёт тонких танталовых (не обязательно, но обычно это тантал) пластин вокруг чипа, которые задерживают излучение (это такой ответ на вопрос «а почему бы не сделать у спутника свинцовые стенки?» Но при этом такой корпус делает хуже стойкость к одиночным сбоям.

Существует также много других методов повышения стойкости к различным воздействующим факторам космической радиации, озвученный набор говорит о том, что разработчики чипа не очень переживали насчет одиночных сбоев и были больше озабочены полной дозой и тиристорным эффектом.

UPD из комментария ниже: судя по всему, процессор изготовлен по технологии «кремний на изоляторе». В ней все транзисторы изолированы друг от друга диэлектриком, что исключает возникновение катастрофического тиристорного эффекта, добавляя при этом хлопот с полной дозой и одиночными сбоями. Тем не менее, такая мера часто оправдана, потому что случайные отказы сложно парировать по-другому, тогда как для борьбы с негативными последствиями использования КНИ существует множество методов (которые, скорее всего, использованы в библиотеке элементов).

Необходимо, правда, заметить, что фраза «space processors are built on SOI» является мнением конкретного японского разработчика и не является универсальной истиной. На объемной технологии тоже можно сделать все, что нужно, и иногда это даже проще чем на КНИ, зависит от требований задачи и от специфики техпроцессов.

maxgorbunov

09.04.2019 09:15+2Вот тут намекают, что еще и технология SOI:

https://www.spaceflightinsider.com/missions/solar-system/mips-space-inside-jaxas-hayabusa-2-mission-asteroid-rendezvous/

vilgeforce

09.04.2019 10:26Почему обычно именно тантал, а не вольфрам, например или золото?

amartology

09.04.2019 11:03Точему именно тантал — не знаю. Вольфрам тоже применяют, и сплавы, и т.д.

Думаю, там смесь экономических соображений и легкости интеграции пластин (или напыления) с керамикой, а не только вопрос плотности металла. Плюс наверное стоит посмотреть, как различаются вероятности ядерных реакций с протонами для разных материалов и какие получаются продукты этих реакций.

И тантал, и вольфрам, и, например, платина — популярные материалы для мишеней в ускорителях заряженных частиц, а значит, при ядерном взаимодействии пуска протонов с ними получается много продуктов, то есть, в нашем случае, много одиночных сбоев.

da-nie

09.04.2019 12:41А не могли бы вы рассказать, почему именно тантал используется? Я что-то в поисковиках по запросу «тантал радиационная защита» ничего не нахожу.

Спасибо.

amartology

09.04.2019 13:01Не «именно тантал», а «обычно тантал». Принципиально: чем больше плотность — тем лучше. Топ-10 металлов по плотности:

Осмий (22,62 г/см3),

Иридий (22,53 г/см3),

Платина (21,44 г/см3),

Рений (21,01 г/см3),

Нептуний (20,48 г/см3),

Плутоний (19,85 г/см3),

Золото (19,85 г/см3)

Вольфрам (19,21 г/см3),

Уран (18,92 г/см3),

Тантал (16,64 г/см3).

Нептуний, уран и плутоний отсекаем по понятным причинам, а дальше начинаются частности в виде цены, технологичности, влияния на одиночные сбои и т.д.

Barafu_Albino_Cheetah

09.04.2019 13:24+2Почему уран отсекаем? Стабильный уран малоопасен и не дорог… Из него даже пули пытаются делать.

da-nie

09.04.2019 13:55+1Принципиально: чем больше плотность — тем лучше.

Это в космосе-то?

habr.com/ru/post/156049

Из-за всех этих проблем радиационную защиту из тяжелых элементов, как на земле — в космосе не используют. Используют защиту большей частью состоящую из алюминия, водорода (из различных полиэтиленов и проч), т.к. его разбить можно только на субатомные частицы — а это намного сложнее, и такая защита генерирует меньше вторичной радиации.

Но в любом случае, от ТЗЧ защиты нет, более того — чем больше защиты — тем больше вторичной радиации от высокоэнергетических частиц, оптимальная толщина получается порядка 2-3мм Алюминия. Самое сложное что есть — это комбинация защиты из водорода, и чуть более тяжелых элементов (т.н. Graded-Z) — но это не сильно лучше чисто «водородной» защиты. В целом, космическую радиацию можно ослабить примерно в 10 раз, и на этом все.

Мне для космоса и нужна защита компонентов изделия. Потому и спросит, зачем тантал? Может, он уникальный в чём-то в качестве защиты.

amartology

09.04.2019 14:26Да, в космосе. Для защиты от полной дозы излучения — чем больше плотность, тем лучше. Тантал ничем не уникален с точки зрения радиационной защиты, в реальности используются также многослойные структуры из разных металлов.

В приведенной вами цитате первый абзац полностью неверен, а второй говорит не про дозу, а про ТЗЧ. Про ТЗЧ я то же самое сказал выше: от танталового корпуса или любого другого экрана из плотного материала, уменьшающего дозу, ситуация по ТЗЧ становится хуже (причем намного).

da-nie

09.04.2019 15:26В приведенной вами цитате первый абзац полностью неверен,

А, ну-ну. Анекдот про филина и мышей помните? Стратегия мне не интересна. Мне реальное решение интересно. А реальное решение именно такое, как и описано в той статье. И проблемы те же, что там и описаны. Запустить десять метров свинца на стенке спутника мы не можем — ЦСКБ «Прогресс» не позволяет. С чего бы это, как думаете? :)

amartology

09.04.2019 15:58Реальное положение вещей таково, что японцы используют специальный корпус микросхемы, повышающий стойкость к полной поглощенной дозе. И что, например, «Тестприбор» предлагает такие корпуса. Вполне реальное решение:

При использовании электронного устройства на орбите МЕО, где преобладающими частицами являются протоны, корпуса с интегрированной радиационной защитой (ИРЗ) позволяют усилить защиту кристалла от жесткого космического излучения до 4х раз.

Так же использование корпусов с РЗЭ позволяет обеспечить защиту от рентгеновского излучения в пределах 1,3?1,5 раз.

Применение комбинаций технических решений с использованием радиационно-защищающих корпусов позволяет разработчикам интегральных микросхем с большей долей вероятности достичь необходимых результатов. Объединение в одной гетерогенной структуре веществ с малым и большим Z создает условия для многократного отражения частиц и – ?-квантов от поверхностей контакта слоев этих веществ и возвращение фотонов в слои, заполненные высокопоглащающим веществом, не выходя за внешние пределы структуры. Благодаря своему специфичному строению, такая структура является своеобразной ловушкой для фотонов.

Применить то же самое в большом масштабе, сделав свинцовый или вольфрамовый корпус целому блоку или всему спутнику, нельзя, потому что получится слишком тяжело, чтобы это куда-то долетело, но локально такие экраны для снижения дозовой нагрузки вполне себе используются — там, где прямо очень нужно поставить что-то, не укладывающееся в требования по дозе и при этом не боящееся ТЗЧ.

da-nie

09.04.2019 16:32Вполне реальное решение:

Всё это мне известно.

но локально такие экраны для снижения дозовой нагрузки вполне себе используются

Проблема в том, что обычно, электроника боится и того и другого.

amartology

09.04.2019 16:40Проблема в том, что обычно, электроника боится и того и другого.

А никто и не говорил, что такой экран — это универсальное решение. И даже что это хорошее решение. Я как разработчик радстойких микросхем вообще за то, чтобы мне заказывали побольше новых дизайнов вместо того, чтобы вот такими костылями повышать стойкость плохо подходящих для космоса микросхем.

Но такое решение может быть подходящим в некоторых случаях. Допустим (сферически в вакууме), что у вас есть микросхема на КНИ, но с плохой дозовой стойкостью.

lingvo

09.04.2019 15:38Возможно еще используются специальные IP ядра, проверяющие конфигурационную память на SEE. У Ксайлинксов есть неплохое описание в ихнем контроллере.

https://www.xilinx.com/products/intellectual-property/sem.html

Lev91gor

09.04.2019 18:59В качестве дополнения можно также уточнить, что популярным материалом для корпусов радиационно-стойких ИС в нашей микроэлектронной промышленности является Ковар (29НК, если не ошибаюсь) — железо (53%), кобальт (17%), никель (29%).

nerudo

09.04.2019 09:23+3Так и запишем: MIPS замешан в бомбардировках мирных астероидов.

amartology

09.04.2019 09:53В варварском освоении мирного космоса замешаны все популярные архитектуры микропроцессоров и микроконтроллеров, и ещё ряд специализированных. Разве что RISC-V пока не засветился, но это дело времени.

faoriu

09.04.2019 09:40Как код Verilog затем превращается в топологию? Насколько я слышал, высокопроизводительные процессоры до сих пор нужно разводить вручную, поскольку autolayout не даёт нужных результатов.

amartology

09.04.2019 09:50+1Неправильно слышали, такое количество транзисторов нельзя развести вручную человек может задать ограничения для программ, размещающих и разводящих элементы, но не более того.

Вручную реально сделать или небольшие по размерам, но критичные для производительности блоки (например, делитель и умножитель), или блоки из повторяющихся элементов (регистровый файл и кэш-память).

YuriPanchul Автор

09.04.2019 09:58+1Мы тут в компании недавно работали над нейроакселератором, который начинался как custom design, а потом был переписан на верилоге. Выяснилось, что получилось не намного медленнее. Конечно, в интеле и amd есть куски datapath роеализованные на custom logic, но бОльшая часть, как мне говорили и люди из AMD, и люди из Intel-а, делается на верилоге.

Код на верилоге превращается в топологию с помощью логического синтеза и последующего place & route + дополнительные шаги (static timing analysis, power grid synthesis, clock routing). Вы можете пролистать вот эту презентацию или пройти онлайн-курс с обзором RTL2GDSII.

xfaetas

09.04.2019 09:47Какие перспективы трудоустройства у школьников, которые заинтересуются проектированием процессоров и поступят на соответствующие факультеты, с учётом того, что с появлением 5G грядёт массовый переход на тонкие клиенты и облачные вычисления, а значит большинство современных семейств мобильных и десктопных процессоров исчезнут и на рынке останутся только топовые процессоры от производителей уровня IBM?

YuriPanchul Автор

09.04.2019 10:085G чипы тоже не на деревьях ростут и в них есть процессоры. Ядро MIPS I7200 (multithreaded in-order dual-issue superscalar) предназначено для использования в 5G чипах:

www.mips.com/press/new-mips-i7200-processor-core-delivers-unmatched-performance-and-efficiency-for-advanced-lte5g-communications-and-networking-ic-designs

New MIPS I7200 Processor Core Delivers Unmatched Performance and Efficiency For Advanced LTE/5G Communications And Networking IC Designs

Santa Clara, Calif. – May 1st, 2018 – MIPS, provider of the widely used MIPS processor architecture and IP cores for licensing, today announced the I7200 multi-threaded multi-core processor, a new high performance licensable IP core in their midrange 32-bit product lineup. Class-leading efficiency is essential to power sensitive applications such as the high bandwidth modem subsystems in Advanced LTE Pro and upcoming 5G smartphone SoCs, as well as networking ICs, and other applications. The I7200 delivers 50% higher performance in less than 20% area increase than the previous generation from MIPS.

old_bear

09.04.2019 10:09Процессоры никуда не денутся. Просто это будут процессоры для мобильных устройств или коммуникационного оборудования. И эти процессоры будут весьма сложными, как уже сейчас являются весьма сложными процессоры смартфонов, несмотря на то, что они большей частью анимированные смайлики обсчитывают и фотографии улучшают.

CrashLogger

09.04.2019 12:08В тонких клиентах тоже есть процессор. А еще сейчас активно развиваются разные специализированные вычислители, например майнеры биткоинов, ускорители нейросетей, графические процессоры. Так что школьникам работы хватит.

mistergrim

09.04.2019 21:00+4с появлением 5G грядёт массовый переход на тонкие клиенты и облачные вычисления

С 90-х это слышу.

mpa4b

09.04.2019 11:11Очень странно, целый 64-битный процессор да ещё и с защитой памяти! Зачем то и другое на космическом аппарате?

А ось, интересно, этот вот µITRON, умеет в виртуальную память?

amartology

09.04.2019 11:16Узкое место всех спутников дальнего космоса — очень медленный радиоканал до Земли. Это значит, что всю собранную информацию нужно обрабатывать и максимально сжимать на борту спутника — для этого и нужен мощный процессор.

Например, The New Horizons передавал фотографии Плутона, сделанные во время пролета (который занял несколько часов), в течение нескольких месяцев — и это были уже обработанные и сжатые фотографии.

mpa4b

09.04.2019 11:45+1ну 64-битность даёт только чуть более лёгкую работу с int64_t, и ВСЁ. Ясно, что 64-битное адресное пространство никуда не пригождается.

В целом ощущение, что японцы как купили на волне хайпа эту корку, так и пихают её без разбора везде уже почти 20 лет :)

amartology

09.04.2019 11:51Не «пихают без разбора», а «используют проверенное и хорошо себя зарекомендовавшее решение с серьезным flight heritage».

YuriPanchul Автор

09.04.2019 19:03*** ну 64-битность даёт только чуть более лёгкую работу с int64_t, и ВСЁ. ***

Еще некоторая оптимизация при load-store операциях из регистров общего назначения в память (через кэш или некэшируемым образом). Целый восьмибайтный кусок за один раз. Хотя на 32-битном процессоре это можно делать как load или store пары 32-битных регистров, но тем не менее.

zloe_morkoffko

10.04.2019 11:59ну 64-битность даёт только чуть более лёгкую работу с int64_t, и ВСЁ

и добавляет работы с виртуальной памятью, которая даже в mips32 сделана хм… неудобно

YuriPanchul Автор

10.04.2019 18:34Перечислите конкретные неудобства.

Я знаю только одно существенное — это двойной TLB entry, с двумя трансляциями для смежных страниц. У этого неудобства исторические причины, оно практически случайно просочилось в стандарт MIPS32 из-за некоей хохмы начала 1990-х, в которую были замешаны Silicon Graphics и Микрософт, которые портировали Windows NT на MIPS.

Другие нетривиальные вещи — например прерывание по ненахождению трансляции в TLB и подгрузка его из таблицы в памяти, а также более хитрый случай с подгрузкой трансляции по второму разу из таблицы в виртуальной памяти — это не bug, а feature, для эффективности процессора.

Кроме этого, в более новых MIPS, например в MIPS P5600 внутри российского процессора Байкал BE T1000, есть Hardware Page Table Walker, который автоматизирует этот механизм.

zloe_morkoffko

10.04.2019 19:17-пара регистров EntryLo0/1 — приходится ворочать сразу двумя страницами;

-двойной вызов TLB Refill после промаха по таблицам страниц;

-сегменты памяти — тут у нас кэш, тут не кэш, здесь через MMU, а тут сразу физика. Зачем?

-2 регистра Context и EntryHi — в обоих лежат адреса исключения TLB. Есть еще BadVaddr примерно с тем же содержимым. Это просто странно, зачем плодить столько сущностей.

Может есть какие-то трюки, что это все не вызывало такое отторжение, но мне они неизвестны.

off/ из трех процов, что у меня есть(комдив64\mips42kc\cortex-a8) — проще всего было отладить arm

YuriPanchul Автор

10.04.2019 19:47*** -пара регистров EntryLo0/1 — приходится ворочать сразу двумя страницами; ***

Это исторический инциндент. Трюк с двойными записями родился для экономии на компараторах. Согласно Майку Гупте, одного из дизайнеров MIPS R4000 (1991):

* Процессор с 64 одинарными записями TLB не влазил в floorplan

* Влез дизайн с 24 двойными записями (48 трансляций)

* Решение стало стандартным в начале 1990-х по требованию Микрософта

* Микрософт и MIPS были членами комитета Advanced Computing Environment (ACE)

* Микрософт портировал на MIPS Windows NT

* В 1999 году трюк с двойными записями просочился в стандарт MIPS32

www.panchul.com/dropbox/2013_11_23/imgtec_mips_microchip_masters_russia_2013.pdf

*** -двойной вызов TLB Refill после промаха по таблицам страниц; ***

Это имеет некую логику, описанную в See MIPS Run Linux.

*** -сегменты памяти — тут у нас кэш, тут не кэш, здесь через MMU, а тут сразу физика. Зачем? ***

А разве у ARM нет регионов памяти с разными атрибутами кэширования итд?

*** -2 регистра Context и EntryHi — в обоих лежат адреса исключения TLB. Есть еще BadVaddr примерно с тем же содержимым. Это просто странно, зачем плодить столько сущностей. ***

Логику этого я забыл, надо вспомнить по своим старым презентациям. Это есть в See MIPS Run Linux.

Но вообще спасибо за feedback.

mpa4b

10.04.2019 20:18А разве у ARM нет регионов памяти с разными атрибутами кэширования итд?

Насколько я знаю, у «больших» армов с MMU, типа armv7-a (cortex-a*) — нет, и все атрибуты задаются именно MMU. А вот у тех что без, «для контроллеров» — есть, например armv7-m (cortex-m*).

zloe_morkoffko

11.04.2019 11:15Это исторический инциндент.

Оправдалась ли экономия? Может быть стоило чуть ужаться в другом месте и сделать MMU на 64 entry?

А разве у ARM нет регионов памяти с разными атрибутами кэширования итд?

Есть, они прописаны в атрибутах страниц\секций. Как собственно и у MIPS в регистре EntryLo в поле С. Тут я про сегменты KSEG0\1\2.

See MIPS Run Linux.

Книга хорошая, подсматриваю туда.

Собственно, я не джедай по mips, и наверное просто не умею его готовить.

YuriPanchul Автор

11.04.2019 19:54*** Оправдалась ли экономия? Может быть стоило чуть ужаться в другом месте и сделать MMU на 64 entry? ***

Экономия конечно же не оправдалась, это было принятое в последний момент решение для одного чипа, чтобы его подогнать под бюджет площади, но изменение этого потом не делалось, так как меняло софтверную совместимость. Впрочем, возможно это и стоит сделать (у нас в MIPS сделали довольно сильные изменения при переходе от Revision 5 к Revision 6.

BoogieMan75

Фотки...facepalm

YuriPanchul Автор

А что, лучше пост без фоток? Или что вам не нравится?

BoogieMan75

лучше фотографии

YuriPanchul Автор

А, OK, поправил, спасибо