Необходимым качеством любой вычислительной машины является достоверность результатов её работы. Если отбросить умышленное искажение или уничтожение результатов посредством вирусов и другого вредоносного ПО (для середины 1960-х годов этот вопрос ещё не был актуален), главной причиной возможных проблем являются случайные сбои аппаратуры, ведь их последствия, в отличие от настоящих отказов, могут длительное время оставаться незамеченными. Например, если у процессора вышло из строя АЛУ, то последствия будут очевидны практически мгновенно: скорей всего, машина сразу же зависнет, чего человек не сможет не заметить. Однако если то же самое АЛУ даст неверный результат всего один раз за день непрерывной работы, такую ошибку, вполне возможно, вовремя не заметят, ведь она может повлиять, скажем, лишь на результат расчёта некоторой прикладной программы, не вызвав при этом явно ненормального поведения. Очевидно, что повысить достоверность результатов можно лишь с помощью тех или иных схем контроля, непрерывно проверяющих правильность функционирования основной аппаратуры.

В Системе 360, а соответственно, и в ЕС ЭВМ с самого начала предусматривалось широкое использование аппаратного контроля, причём некоторые аспекты реакции на возникновение ошибок были стандартизированы на уровне архитектуры — хотя самоочевидно, что в этой области стандартизировать можно немногое, ведь обработка ошибок тесно связана с особенностями реализации, которые могут кардинально различаться у разных моделей одной архитектуры.

На архитектурном уровне определены следующие принципы обработки аппаратных ошибок:

аппаратные ошибки не могут возникать из-за программных ошибок (исключение — использование команды ДИАГНОСТИКА, точные функции которой всецело зависят от конкретной модели, а неправильное её использование может приводить к непредсказуемым последствиям — однако эта команда является привилегированной, а соответственно, доступна только системному коду);

при обнаружении ошибки, не приводящей к немедленному останову, процессор пытается сохранить в определённых ячейках основной памяти всю возможную информацию на момент сбоя. Часть из этой информации общая для любых моделей (содержимое общих регистров, регистров с плавающей запятой и PSW), а часть зависит от реализации (состояние различных внутренних аппаратных регистров и т. п.);

в зависимости от тяжести сбоя, состояния бита маски прерываний от схем контроля в PSW и положения определённых переключателей на пульте управления процессор может либо (1) перейти в так называемый тяжёлый останов (hard stop; от обычного останова отличается тем, что из него невозможно выйти без предварительного сброса индикаторов ошибок; кроме того, в большинстве реализаций в тяжёлом останове отключается синхронизация, в то время как при обычном останове процессор, с технической точки зрения, продолжает работать, «крутясь» в своём внутреннем цикле, но не выполняя команды и не реагируя на запросы прерываний), либо (2) запомнить информацию о сбое в своей внутренней памяти и продолжить работу обычную работу (сохранённая информация может быть впоследствии записана в основную память), либо (3) выполнить прерывание от схем контроля, при котором записывается вся информация, отражающая состояние процессора на момент сбоя либо, возможно, сохранённая ранее. Обработчик прерывания от схем контроля, входящий в состав ядра операционной системы, выполняет дальнейшую обработку сбоя. В частности, он пытается сохранить информацию об ошибке в файле журнала, а затем либо аварийно завершает работу пострадавшей программы пользователя (или останавливает ОС, если дальнейшая работа невозможна), либо перезапускает её с контрольной точки.

Архитектура не накладывает каких-либо ограничений на степень охвата машины аппаратным контролем; в частности, ЭВМ может быть вообще лишена каких-либо средств контроля, хотя на практике такое если и встречалось, то крайне редко. ЕС-1020, как младшая и наиболее дешёвая модель, использует лишь простейшие способы контроля, не охватывающие всю её аппаратуру. Основным методом является контроль по чётности; кроме того, в некоторых случаях используется дублирование аппаратуры.

Формирование контрольных битов и обнаружение ошибок чётности и двухпроводных ошибок

Сама по себе идея контроля по чётности хорошо известна. При передаче или хранении контролируемого значения передаётся или хранится дополнительный контрольный разряд, который, в зависимости от реализации, дополняет количество единичных битов контролируемого значения либо до нечётного, либо до чётного. Для контроля правильности информации производится подсчёт числа единичных разрядов в контролируемом значении и полученный результат сравнивается с контрольным битом; несоответствие ожидаемого и вычисленного значений свидетельствует об ошибке.

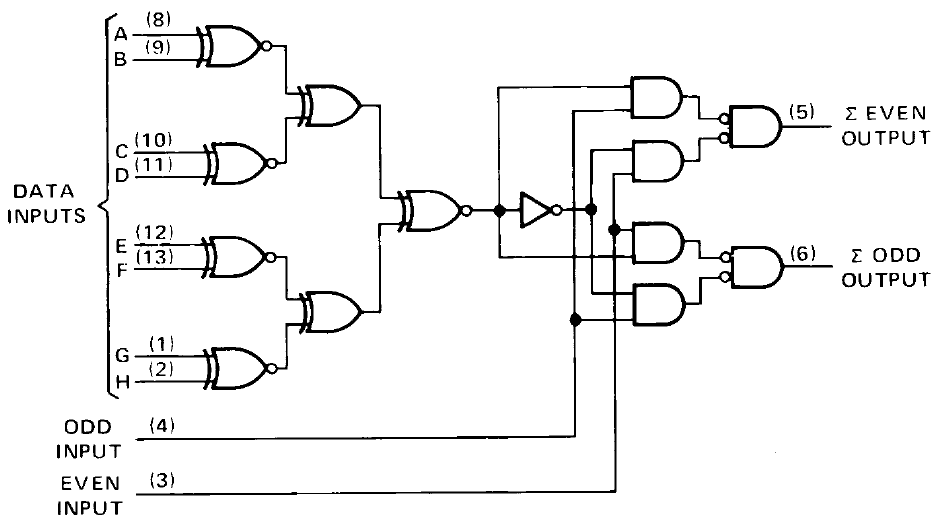

Подсчёт числа единичных битов производится так называемыми схемами свёртки (суммирования по модулю 2), с точки зрения двоичной логики построенными на элементах «исключающее ИЛИ». Если на вход такого элемента подать два бита информации, на его выходе будет логическая единица, если ровно один из двух исходных битов является единичным, и нуль в противном случае. Объединив несколько элементов, получаем многоразрядную схему контроля. Ниже в качестве иллюстрации показано внутреннее устройство классической микросхемы SN74180 (скопирована в СССР под обозначением К155ИП2), обеспечивающей формирование контрольных разрядов для 8-разрядного исходного значения и имеющей возможность наращивания разрядности.

На момент создания ЕС-1020, однако, готовых микросхем контроля чётности или хотя бы логических элементов «исключающее ИЛИ» (К155ЛП5, она же SN7486) наша промышленность ещё не выпускала, поэтому схемы контроля пришлось собирать из того, что было доступно, но не так прямолинейно, как можно было бы ожидать.

Для передачи информации между различными регистрами и блоками процессора ЕС-1020 используются так называемые парафазные сигналы. Этот в значительной мере забытый ныне термин означает передачу каждого бита информации сразу по двум проводникам: по одному передаётся его прямое значение, а по другому — инверсное. На первый взгляд, парафазный сигнал напоминает широко распространённые в наши дни дифференциальные сигналы, но сходство здесь чисто внешнее: если в дифференциальном сигнале его логическое значение определяется разностью напряжений между прямой и инверсной линиями, а сами по себе абсолютные значения напряжений на этих линиях безразличны (в разумных пределах, конечно), то в случае с парафазным сигналом каждая линия технически является самым обычным логическим сигналом с самым обычным логическим уровнем, просто значение на одной линии всегда является инверсным по отношению к другой.

Схемы свёртки, используемые в процессоре ЕС-1020, опираются на использование парафазных сигналов и не только формируют или проверяют контрольные разряды, но и обнаруживают так называемые двухпроводные ошибки, т. е. наличие одинакового логического уровня на парафазных линиях. Наиболее широко используется стандартная схема свёртки на восемь разрядов, функциональная схема которой показана на рисунке.

![Стандартная схема свёртки, скан из [1] Стандартная схема свёртки, скан из [1]](https://habrastorage.org/getpro/habr/upload_files/a55/9c7/474/a559c7474de616cb6199eb2eccc518e5.png)

Большую часть схемы (область «а») составляет собственно схема свёртки, основой которой является элемент, обозначенный М2, — на самом деле, это самый обычный элемент 2,2И-2ИЛИ-НЕ, который в количестве двух штук «обитает» внутри микросхемы К155ЛР1. Каждая пара битов исходной информации, для которой необходимо сформировать контрольный разряд (сигналы И(0-7) для прямых значений разрядов и –И(0-7) для инверсных), поступает на два элемента М2: на один из них попарно подаются либо два прямых, либо два инверсных значения, а на второй — один прямой, а другой инверсный или наоборот. Выходы элементов М2 первого уровня поступают на входы элементов второго уровня, а выходы последних — на входы элементов третьего уровня, с выходов которых снимается сформированный контрольный разряд в прямом и инверсном виде — сигналы И(К) и –И(К). Легко подсчитать, что в состав схемы свёртки входит 14 элементов, то есть семь микросхем К155ЛР1.

Две другие области схемы, «б» и «в», обеспечивают контроль информации. Сформированный в области «а» контрольный разряд сравнивается (область «б») с контрольным разрядом, полученным от источника информации; при несовпадении формируется сигнал ошибки «сбой по нечету». Область «в» контролирует наличие двухпроводного сбоя.

Контроль регистров

Общие и «полноценные» адресные регистры процессора, описанные в одной из предыдущих статей, — РФ, РЕ, РР, РИ, РТ, РУ, РЛ и РД — включают в свой состав восемь информационных разрядов и контрольный бит К. Информация в них заносится только с выхода БА, при этом она записывается сразу во все биты регистра, включая контрольный, где и хранится в ожидании дальнейшего использования.

При считывании любого из перечисленных регистров его содержимое, включая сохранённый контрольный бит, передаётся в регистр-приёмник, в роли которого может выступать один из входных регистров арифметико-логического блока РА и РВ либо один из двух младших байтов регистра адреса памяти РМН. На выходе каждого из этих трёх регистров расположены схемы свёртки, осуществляющие контроль правильности информации. В результате, используя лишь четыре байтовых схемы свёртки (по одной для РА и РВ и две для двух младших байтов РМН), обеспечивается контроль и этих регистров, и их регистров-источников, и путей передачи информации от БА в регистры блока регистров и из них обратно в БА и в РМН.

Недостатком такого подхода является некоторая несвоевременность обнаружения сбоя: скажем, если регистр РФ неисправен, это обнаружится только при попытке использования сохранённой в нём информации, а не в момент занесения в него нового значения. Это несколько усложняет поиск возникшей неисправности, однако не сказывается на реальной надёжности обнаружения ошибок: с точки зрения пользователя, нет разницы, при выполнении какой именно микрокоманды ошибка была обнаружена, главное — обнаружить её и прекратить выполнение пострадавшей от сбоя программы, оповестив об этом пользователя (или, на худой конец, остановить процессор с индикацией возникновения машинной ошибки). Для максимально удешевлённой машины, без сомнения, это является правильным решением.

Хуже обстоит дело с тремя «неполноценными» адресными регистрами — РМ, РП и РГ. Они не имеют контрольного разряда, поэтому при их считывании он формируется сокращённой схемой свёртки (на два бита для передачи в старший, неполный байт РМН и на три бита для передачи на вход БА). Соответственно, занесение в них некорректной информации с выхода БА или неисправность самих этих регистров аппаратурой не обнаруживается и проявляется лишь косвенно — скажем, ОС может «упасть» из-за порчи содержимого памяти по адресу, искажённому вышедшим из строя регистром. Хотя на отсутствии контрольного бита достигнута некоторая экономия аппаратуры, представляется, что в данном случае это не было оправдано: надёжность обнаружения ошибок снизилась, а экономия очень невелика — особенно с учётом того, что специально для этих регистров можно было бы предусмотреть отдельную схему свёртки на три бита на выходе БА, а не реализовывать такую схему индивидуально для каждого регистра.

![Контроль адресных и общих регистров, скан из [1] Контроль адресных и общих регистров, скан из [1]](https://habrastorage.org/getpro/habr/upload_files/966/8f4/7ce/9668f47ce3c151642c44f5893b16b3e4.png)

Служебные регистры — РБС, РБР, РБК и РБД, а также регистр ошибок РО, о котором речь пойдёт ниже, — не имеют никаких средств собственного контроля, и лишь для проверки правильности их передачи на вход БА они снабжаются формируемыми «на лету» контрольными разрядами, как это сделано для РМ, РП и РГ (с поправкой на разрядность регистров). Несмотря на схожесть ситуации, в данном случае экономия является, скорее, оправданной: контролировать эти регистры можно лишь дублированием аппаратуры (многие их биты изменяются аппаратно независимо от других битов, что делает невозможным банальное сохранение контрольного разряда), а это весьма дорого — как минимум, нужен двойной комплект триггеров плюс схемы их сравнения. В то же время, выход этих регистров из строя почти никогда не может привести к порче результатов выполнения команд и при этом остаться незамеченным. Скажем, если «сдохнет» триггер запроса прерывания от какого-либо из каналов ввода-вывода, это проявится либо в непрерывном потоке ложных прерываний, либо, наоборот, к потере реальных запросов и, как итог, к зависанию операций ввода-вывода. В обоих случаях неверных результатов как таковых не будет, зато система перестанет функционировать нормальным образом, что быстро будет обнаружено оператором.

![Контроль служебных регистров, скан из [1] Контроль служебных регистров, скан из [1]](https://habrastorage.org/getpro/habr/upload_files/25e/156/f2d/25e156f2d16f57d38641f19e13bc55ba.png)

Контроль арифметико-логического блока

Как уже говорилось, принимаемая во входные регистры РА и РВ информация контролируется на нечётность и на двухпроводную ошибку с помощью стандартных схем свёртки, обеспечивая попутно контроль регистров-источников информации и путей передачи. По результатам проверки формируются сигналы сбоев СБРАН, СБРВН (сбой по нечету РА и РВ), СБРАД и СБРВД (двухпроводной сбой РА и РВ).

Правильность выработки сигналов управления узлом управляющих сигналов контролируется, как было сказано в предыдущей статье, с помощью специально вырабатываемого сигнала И, уравнивающего чётность количества активных управляющих сигналов с чётностью кода выполняемой прямой или косвенной функции. Код функции и сформированные управляющие сигналы поступают на схему контроля, формирующую сигналы сбоев СБУАН (сбой по нечету) и СБУАД (двухпроводной сбой). При подаче кода функции 0001, который может быть задан только как косвенная функция, специально формируется неверное значение сигнала И, что позволяет проверить работу самой схемы контроля.

![Контроль узла управляющих сигналов, скан из [1] Контроль узла управляющих сигналов, скан из [1]](https://habrastorage.org/getpro/habr/upload_files/f0c/6f9/899/f0c6f989988d3092df84c4b97c634040.png)

Для контроля обрабатывающих блоков БА они продублированы, причём основной комплект оборудования выполняет операцию и формирует результат в прямом виде, а дублирующий — в инверсном. Соответственно, совпадение хотя бы одного бита результата для прямого и инверсного трактов обработки свидетельствует о неисправности. Контроль осуществляется обычной схемой свёртки, которая, помимо проверки правильности результата (по сути, двухпроводного сбоя), формирует значение контрольного разряда С(К), выдаваемого на выход БА вместе с результатом. Для проверки работоспособности самой схемы контроля предусмотрена микрооперация НКР поля УСТАНОВ: если она задана, при подаче на вход схемы свёртки производится инвертирование младшего разряда результата, что должно вызвать появление сигнала сбоя СБСД.

![Контроль результата БА, скан из [1] Контроль результата БА, скан из [1]](https://habrastorage.org/getpro/habr/upload_files/45c/cc3/5ca/45ccc35ca5b21fdf06812b58ddd257f5.png)

Работа байта состояния БА (ББА) никак не контролируется. Как и в случае со служебными регистрами, его контроль возможен только методом дублирования, что слишком дорого. Правда, в отличие от служебных регистров, сбой ББА обычно приводит к получению неверного результата операции, поэтому оправданность отсутствия его контроля — вопрос спорный.

Контроль блока микропрограммного управления

В блоке микропрограммного управления контролируется чётность регистра адреса постоянной памяти РАПП и регистра микрокоманды РМК.

![Контроль блока микропрограммного управления, скан из [1] Контроль блока микропрограммного управления, скан из [1]](https://habrastorage.org/getpro/habr/upload_files/d4c/45f/a5d/d4c45fa5dacf7bb81529b190d6b80ce1.png)

После приёма микрокоманды, считанной из постоянной памяти, в РМК схемой ЛСВ2 производится свёртка его разрядов 0:62 и сравнение результата со значением разряда 63; при обнаружении несоответствия формируется сигнал СБРМК. Заметим, что этот контроль распространяется не только на сам РМК, но и на содержимое постоянной памяти, т. е. обнаружение ошибки говорит о проблемах либо в РМК, либо в ПП, либо в тракте передачи информации из ПП в РМК, либо, наконец, в самой схеме контроля. Подробности устройства ЛСВ2 отсутствуют, но, по всей вероятности, это девять рассмотренных выше схем свёртки: восемь из них свёртывают значения каждого из восьми байтов микрокоманды, а девятая объединяет их результаты.

РАПП контролируется несколько необычным образом. Его 13 разрядов свёртываются схемой ЛСВ1 и сравниваются с битом РМК[62] микрокоманды: последний дополняет до нечётного количество единичных разрядов в адресе микрокоманды, за счёт чего и достигается проверка.

На схеме показан также триггер, сохраняющий признак ошибки РАПП, однако для признака ошибки РМК подобный триггер отсутствует. Здесь дело в том, что сигналы ошибок поступают далее в регистр ошибок, однако сигнал ошибки РАПП не «доживает» до момента его приёма в РО, поскольку по тактовому импульсу ТИ2 или ХИ2 в РАПП уже заносится следующий адрес. Данный триггер является «промежуточным звеном» на пути признака сбоя РАПП в РО; в роли сигнала занесения в него выступает, судя по временной диаграмме, объединение задержанных тактовых импульсов ТИ4З и ХИ4З. Содержимое РМК изменяется лишь в самом конце такта, поэтому сигнал его сбоя остаётся стабильным до приёма в РО и не нуждается во временном сохранении.

![Временная диаграмма контроля блока микропрограммного управления, скан из [1] Временная диаграмма контроля блока микропрограммного управления, скан из [1]](https://habrastorage.org/getpro/habr/upload_files/59b/934/98d/59b93498d9e8e78dc972f887f0e018f0.png)

Дешифраторы полей микрокоманд никак не контролируются.

Контроль памяти и блока защиты

Контроль регистра адреса памяти РМН выполняется двумя стандартными однобайтовыми схемами контроля и дополнительной схемой на два разряда, контролирующей старшие два бита адреса. При обнаружении ошибки выдаётся сигнал СБРМН.

Контроль двух младших байтов адреса фактически проверяет работоспособность и соответствующих порций РМН, и линий передачи информации в них, и адресных регистров, из которых в последний раз информация передавалась в РМН — аналогично тому, как это происходит при передаче содержимого регистров на вход БА. Контроль неполного старшего байта адреса не столь всеобъемлющ, поскольку «неполноценные» адресные регистры (РМ, РП, РГ) не имеют контрольного разряда, и для передачи в РМН он формируется «на лету» — опять-таки, аналогично тому, как содержимое этих регистров передаётся в БА (с той лишь разницей, что контрольный разряд вырабатывается лишь для двух битов, а старший, «уплотнённый» разряд никак не контролируется — при обращении к памяти он используется лишь для обнаружения выхода за пределы ОП, а не для адресации как таковой, поэтому на его контроле решили сэкономить). Соответственно, правильность работы собственно РМН и линий передачи контролируется, а вот правильность занесения и хранения информации в РМ, РП и РГ — нет.

Регистр данных памяти РНЗ контролируется двумя стандартными байтовыми схемами, однако сформированный ими сигнал ошибки может быть заблокирован специальной схемой, приведённой на рисунке.

![Схема выработки сигнала сбоя регистра РНЗ, скан из [1] Схема выработки сигнала сбоя регистра РНЗ, скан из [1]](https://habrastorage.org/getpro/habr/upload_files/778/1cc/073/7781cc073659bdd03cbe4f335099c3b4.png)

Со схемы контроля регистра РН поступают сигналы сбоев СБРНН и СБРНД (для сбоя по нечету и двухпроводного сбоя), со схемы контроля регистра РЗ — аналогичные сигналы СБРЗН и СБРЗД. Из них схемой ИЛИ формируется общий сигнал сбоя СБРНЗ, однако, как видим, прохождение исходных сигналов блокируется с помощью элементов И. Верхняя пара элементов управляется показанным на рисунке триггером РАЗР СБОЯ РН, у нижней пары имеется такой же триггер, который на рисунке опущен (показан лишь приходящий с него сигнал РАЗР СБОЯ РЗ). Эти триггеры сбрасываются сигналом гашения, т. е. аппаратным сбросом процессора, а также по ХИ2 при установленном триггере контроля машины ТКТРМ, что имеет место в случае обнаружения сбоя (об этом будет подробнее сказано позже). Цель этого сброса — заблокировать возможность выдачи сигнала ошибки РНЗ сразу после сброса процессора или если аппаратный сбой уже был обнаружен. В первом случае это необходимо из-за того, что после включения питания и связанного с ним сброса регистр находится в неопределённом состоянии и может вызывать ложную индикацию ошибки, во втором — чтобы не допустить повторной регистрации уже обнаруженного сбоя.

Триггеры блокировки сбоя устанавливаются по ТИ4 в такте, в котором производится занесение информации в РНЗ или любую из его половин либо с выхода БА (сигнал РН:=С или РЗ:=С), либо из оперативной памяти (сигналы ПОДКЛ ПО ЧТ и ПОДКЛ ПО СТ): в этих случаях в РНЗ принимается новая информация, и её нужно проконтролировать.

Поскольку с памятью работает не только процессор, но и селекторные каналы, при обнаружении сбоя во время работы канала сигнал будет выдан в него, а не в регистр ошибок процессора (точнее говоря, сам сигнал сбоя поступает и туда, и туда, но при работе процессора активны синхросигналы серии ТИ или ХИ, а при работе селекторного канала — СИ, поэтому индикатор ошибки будет занесён в триггер того устройства, активность которого привела к ошибке).

В блоке защиты контролируются только старшие пять разрядов его информационного регистра РБЗ, что обеспечивает также контроль правильности работы памяти ключей.

![Контроль блока защиты, скан из [1] Контроль блока защиты, скан из [1]](https://habrastorage.org/getpro/habr/upload_files/a86/1bf/981/a861bf9814c63d521a721c1d61b9c21f.png)

При считывании из памяти ключей значения ключа в РБЗ[0:4] одновременно считывается и его контрольный бит, попадающий в разряд РБЗ[К]. С помощью схемы свёртки ЛСВ1 выполняется контроль соответствия ключа и его контрольного бита и при обнаружении ошибки выдаётся сигнал СБРБЗ. Этот контроль выполняется только в такте, в котором производится либо явное считывание памяти ключей, либо считывание/стирание ячейки ОП: последнее должно проверяться механизмом защиты, для чего требуется прочитать ключ.

Для передачи информации из РБЗ в БА требуется сформировать для него правильный контрольный разряд. Как было описано в статье, посвящённой памяти, РБЗ — самый «извращённый» регистр процессора, поэтому формирование его контрольного бита не столь прямолинейно: из-за наличия двух четвёртых разрядов требуется мультиплексор для выдачи одного из них в БА и на схему свёртки ЛСВ2, формирующую контрольный бит. Очевидно, что формирование контрольного бита «на лету» не позволяет обеспечить стопроцентный контроль работоспособности РБЗ: правильность хранения информации в битах 4':7 вообще никак не контролируется, а работоспособность битов 0:4 проверяется лишь при явном или неявном считывании ключа памяти, но не при передаче в БА.

За пределами приведённой схемы осталось формирование контрольного бита в самом РБЗ, когда в него записывается информация с выхода БА, чтобы потом выполнить запись ключа в память ключей. Содержимое бита РБЗ[К] в этом случае формируется из битов РБЗ[0:4], принятых с выхода БА, а контрольный разряд, формируемый в БА, игнорируется: он определён для всего байта, а в память ключей будет записана лишь его часть, а соответственно, и контрольный бит будет другим.

Регистр ошибок

Регистр ошибок РО предназначен для фиксации сигналов сбоев различных узлов процессора. Его упрощённая схема приведена на рисунке. Как это нередко бывает, она содержит ряд небольших ошибок. Кроме того, на ней не показаны цепи для занесения информации в РО с выхода БА (это используется, как минимум, для обнуления содержимого РО в процессе обработки сбоя, о чём говорилось выше; возможно, занесение информации в него выполняется и в микропрограммах проверки работоспособности процессора, чтобы проконтролировать сам РО) и для передачи его содержимого на вход БА.

![Регистр ошибок, скан из [1] Регистр ошибок, скан из [1]](https://habrastorage.org/getpro/habr/upload_files/216/617/8ad/2166178ad996c5899a3580288322f237.png)

Если не считать упомянутой возможности загрузки содержимого РО с выхода БА, все триггеры этого регистра сбрасываются специальным сигналом ГАШ. СБОЯ, подаваемым при нажатии одноимённой кнопки пульта управления. Устанавливаются эти триггеры индивидуально при возникновении соответствующих ошибок.

Первые пять триггеров могут быть установлены только при выполнении микрокоманды во время действия тактового сигнала ТИ3.

Бит РО[0] (ТСБРБЗ) устанавливается при наличии сигналов СБРБЗ и ТБЗ. Первый из этих сигналов является, как было сказано выше, признаком сбоя регистра блока защиты РБЗ, выдаваемом при чтении ключа защиты памяти, если чётность разрядов РБЗ[0:4] не соответствует значению контрольного бита РБЗ[К]. Что касается второго из этих сигналов, ТБЗ, то он является признаком наличия блока защиты: конструкторы ЕС-1020 предусмотрели упрощённый вариант машины, не имеющий такового. Выпускались ли в СССР такие машины серийно, я не знаю; у IBM такие машины были, но быстро сошли со сцены: защита памяти быстро стала рассматриваться как необходимое качество любой ЭВМ, кроме самых простых и дешёвых.

Биты РО[1:2] (ТСБРА и ТСБРВ) устанавливаются при обнаружении ошибки во входных регистрах БА РА и РВ соответственно, а они, как уже говорилось, используются для контроля содержимого почти всех остальных регистров процессора. Для обоих этих разрядов предусмотрены сигналы, блокирующие их установку; на схеме они ошибочно показаны в прямом, а не инверсном виде. Сигнал блокировки сбоя РА устанавливается, если информация в РА в данном такте не принимается, т. е. если он хранит своё старое содержимое, что имеет место при нулевом значении поля А микрокоманды. Сигнал блокировки сбоя РВ устанавливается в трёх случаях: (1) если поле В содержит нуль, т. е. в данном такте приём новой информации не выполняется; (2) при установленном триггере ТГС, о котором будет сказано позже; и (3) если в РВ принимается байт состояния БА (ББА) — последний не имеет контрольного разряда. В последнем случае разработчики машины предпочли не формировать контрольный разряд искусственно схемой свёртки, а просто отключать в этот момент контроль, чем ББА отличается от ряда других регистров, например, РБС; вероятно, такое решение объясняется тем, что ББА, в отличие от других регистров, является частью БА и физически расположен неподалёку от РВ — надо полагать, на той же панели; соответственно, сигналам от ББА до РВ приходится проходить значительно меньшее расстояние, что уменьшает вероятность их искажения помехами или физической порчи проводников.

Бит РО[3] (ТСБРМН) устанавливается при обнаружении ошибки в регистре адреса памяти РМН. Установка выполняется, если микрокоманда задаёт обращение к памяти (поле РЕЖИМ содержит любой код, кроме 00). Заметим, что при обращении к памяти со стороны селекторных каналов содержимое РМН тоже контролируется, но сигнал сбоя фиксируется не в РО, а в соответствующем триггере канала; такой сбой будет рассматриваться как ошибка канала, а не процессора.

Бит РО[4] (ТСБРНЗ) устанавливается при обнаружении ошибки в регистре данных памяти РНЗ, если его установка не блокируется установленным триггером ТГС или сигналом поступления данных от канала. Оба блокирующих сигнала ошибочно показаны прямыми — в действительности они должны быть инверсными.

Установка РО[4], хотя кажется практически такой же простой, как и предыдущих разрядов, требует некоторого пояснения. Приём информации в РМН производится по разным тактовым импульсам в зависимости от того, какой узел служит источником данных. Так, при записи в него результата операции БА занесение выполняется по ТИ4, однако РО[4] устанавливается по ТИ3 — а это означает, что ошибка, возникшая при приёме информации в этот регистр из БА, будет обнаружена не в такте записи в РНЗ, а в следующем за ним.

При выполнении считывания информации с устройства, подключённого к мультиплексному каналу, передача данных выполняется микропрограммными средствами, однако каждый байт передаётся не через БА, как это имеет место при выполнении любых операций собственно процессора, а напрямую из буферного регистра мультиплексного канала в РНЗ, причём в этом случае приём информации выполняется по ТИ3 — т. е. одновременно с фиксацией сбоя в РО[4]. Очевидно, что схема контроля не гарантирует формирование правильного результата в таких условиях, поэтому приём признака сбоя в том же такте должен блокироваться, что и делает сигнал ДАН ИЗ КАН (сбой будет зафиксирован в следующем такте).

При обмене данными с селекторным каналом приём в РНЗ выполняется по тактовому импульсу СИ2З, при этом исходное содержимое РНЗ временно сохраняется в регистре-дублёре РН1З1, а возможная ошибка РМН фиксируется в соответствующем триггере канала. К моменту возобновления синхросерии ТИ содержимое РН1З1 возвращается в РНЗ; если это было сделано с ошибкой (например, из-за неисправности РН1З1), она будет зафиксирована по ТИ3.

Таким образом, установка РО[4] даёт знать о сбое или неисправности тракта обмена данными с памятью, но обнаружение реальной причины сбоя может быть весьма затруднено, поскольку точный момент его возникновения остаётся неизвестен.

Остальные три бита РО изменяют своё состояние по тактовому импульсу ТИ2 или ХИ2.

Бит РО[5] (ТСБРМК) устанавливается при обнаружении ошибки чётности регистра микрокоманды РМК, а бит РО[6] (ТСБРАПП) — при обнаружении ошибки в содержимом регистра адреса постоянной памяти РАПП. Приём сигналов сбоев выполняется либо по ТИ2, либо по ХИ2, поскольку адрес микрокоманды и сама микрокоманда изменяются как в тактах ТИ, так и в тактах ХИ. Установка этих триггеров блокируется сигналом гашения системы (ошибочно показан как прямой, а не инверсный): завершением гашения является занесение в РАПП адреса 0001, с которого начинается микропрограмма гашения, и выборка в РМК из постоянной памяти первой микрокоманды. Пока эти процессы, выполняемые по тактовым сигналам серии ХИ, не завершены, в этих регистрах может находиться «мусор», а соответственно, схемы контроля могут вырабатывать ложные сигналы ошибок; их приём и блокируется этим сигналом.

Бит РО[7] (ТСББА) устанавливается при обнаружении сбоя в работе БА (нарушение чётности набора управляющих сигналов либо совпадение битов прямого и инверсного результатов). Информация о сбое принимается в следующем за операцией такте — именно поэтому требуется фиксировать её не только по импульсу серии ТИ, но и по импульсу серии ХИ, поскольку ещё до обнаружения сбоя обычное выполнение микропрограммы может быть прервано, например, для обслуживания одного из каналов, что повлечёт выполнение такта ХИ сразу за «сбойным» тактом ТИ. Неясно лишь, почему сбой БА не фиксируется в самом конце такта, по ТИ4: именно по этому импульсу в регистры процессора записывается результат работы БА, и сигналы ошибок в работе последнего к этому времени уже гарантированно сформированы. В качестве гипотезы предположу, что проектирование различных узлов машины велось одновременно, и на момент начала работ разработчики не были уверены в том, что БА и его схемы контроля будут достаточно быстры, и предпочли перестраховаться.

Выходы всех триггеров РО подаются на схему формирования сигнала СБОЙ МАШ, устанавливаемого, когда установлен хотя бы один из этих триггеров. Некоторое недоумение может вызвать, почему на схеме показана подача инверсных значений триггеров и повторное инвертирование их на входе элемента ИЛИ вместо подачи прямых выходов без дополнительной инверсии. Думается, это стало следствием неполноценной переделки принципиальной схемы в функциональную. Дело в том, что в реальном «железе» сборку восьми сигналов с выходов триггеров в один общий сигнал ошибки выполняет не восьмивходовый элемент ИЛИ — таких в природе не существует, и собирать его из доступных на тот момент элементов малоэффективно, — а элемент 8И-НЕ, представленный микросхемой К155ЛА2. Как известно, элемент И-НЕ — это то же самое, что элемент НЕ-ИЛИ, поэтому, чтобы собрать сигналы триггеров РО по «или», необходимо на входы элемента И-НЕ подать инверсные, а не прямые выходы триггеров — и тогда на выходе И-НЕ будет получен прямой сигнал СБОЙ МАШ.

Обработка ошибок

Общая последовательность действий при обнаружении любой машинной ошибки заключается в следующем.

Устанавливается триггер регистра ошибок РО, соответствующий обнаруженному сбою.

Факт установки любого из триггеров РО вызывает установку триггера контроля машины ТКТРМ, а за ним и триггера первого сбоя ТПСБ, являющихся разрядами 6 и 7 регистра РБД, описанного в одной из предыдущих статей. Установка ТКТРМ приводит к приостановке формирования тактовых импульсов серии ТИ и запуску серии ХИ. Во время выполнения такта ХИ происходит загрузка в РАПП адреса начала микропрограммы обработки ошибок (фиксированный адрес 8), после чего из постоянной памяти в РМК считывается первая микрокоманда этой микропрограммы.

Возобновляется выработка тактовых импульсов ТИ и начинается выполнение микропрограммы обработки ошибки. Первый же импульс ТИ1 сбрасывает триггер ТКТРМ, однако триггер ТПСБ остаётся установленным.

Микропрограмма обработки ошибки сначала проверяет, возникла ли ошибка при выполнении микропрограммы процессора или микропрограммы обслуживания одного из каналов (путём анализа состояния триггера ТЦП, он же бит РБД[0]). Если сбой возник во время работы канала, управление передаётся микропрограмме обработки сбоя канала, иначе выполняется микропрограмма обработки сбоя процессора.

Любая из этих микропрограмм сохраняет в фиксированных ячейках основной памяти содержимое ряда регистров процессора или каналов, включая регистр РО, и другую информацию, потенциально полезную для поиска причины сбоя. Регистр РО после сохранения его содержимого очищается.

-

Выполняется исправление битов чётности аппаратных регистров процессора и ячеек локальной памяти. Технически это осуществляется путём подачи содержимого одного регистра за другим на вход В БА, передачи его на выход БА (операция ТРАНЗИТ В) и записи результата обратно в исходный регистр. Поскольку контрольный разряд на выходе БА формируется, исходя из значения результата, т. е. в соответствии со значением информационных разрядов регистра, прошедших через БА в неизменном виде, в регистр поступит его исходное содержимое с правильным контрольным битом.

Содержимое ЛП исправляется таким же образом, но более длинным путём: каждая двухбайтовая ячейка ЛП считывается в регистр РНЗ, а затем побайтово пропускается через БА, после чего обновлённое содержимое РНЗ сохраняется в ЛП.

-

Происходит переход на микропрограмму смены слова состояния процессора PSW. Эта микропрограмма «собирает» PSW из регистров процессора и ячеек ЛП, записывает его в указанную область основной памяти, а затем считывает из другой области ОП новое значение PSW и «раскладывает» его по регистрам процессора и ячейкам ЛП. Несколько подробнее этот процесс будет описан в следующей статье, поскольку он является общим для всех видов прерываний; в данном конкретном случае запись значения PSW на момент возникновения сбоя происходит в область старого PSW прерываний от схем контроля, а выборка нового значения — из области нового PSW прерываний от схем контроля.

В последней микрокоманде микропрограммы загрузки PSW производится сброс триггера первого сбоя ТПСБ, что указывает на окончание обработки возникшей ошибки со стороны микропрограммы и возобновление нормальной работы аппаратуры.

Возобновляется выполнение программы с адреса, заданного в только что загруженном новом PSW, — это будет обработчик прерываний от схем контроля машины, входящий в состав операционной системы.

Пока выполняется микропрограммная обработка сбоя, т. е. от момента установки триггера ТПСБ одновременно с переходом на микропрограмму обработки сбоя и до его сброса в последней микрокоманде этой микропрограммы (технически — в последней микрокоманде микропрограммы загрузки нового PSW) возникновение нового сбоя недопустимо: оно приводит к переходу процессора в состояние тяжёлого останова путём установки триггера ТТО, что вызовет полный останов синхронизации.

Очевидно, что занесение в РВ содержимого регистра с неправильной чётностью вызовет обнаружение ошибки — однако именно такую подачу необходимо делать для сохранения содержимого регистров в памяти и для восстановления правильных значений их контрольных разрядов. Аналогичным образом, для восстановления правильных контрольных разрядов в ячейках памяти необходимо сначала загрузить их содержимое в РНЗ — но это тоже вызовет обнаружение ошибки. Чтобы избежать в процессе выполнения этих действий возникновения тяжёлого останова, перед началом процедуры сохранения и коррекции информации микропрограмма устанавливает упоминавшийся при описании регистра РО триггер гашения системы ТГС — как мы видели, он блокирует занесение в РО признаков сбоев РВ и РНЗ, не препятствуя фиксации других возможных ошибок. Сброс этого триггера производится по окончании процедуры коррекции регистров и памяти. «Гашение системы», давшее название этому триггеру, означает сброс оборудования и в процессоре ЕС-1020 выполняется почти исключительно микропрограммными средствами. Микропрограмма гашения, подобно обработчику сбоев, тоже обеспечивает правильность контрольных разрядов во всех регистрах процессора и во всех ячейках всех видов памяти — в ЛП, МП, ОП и памяти ключей, поскольку на момент сброса (в частности, сразу после включения питания машины) там может находиться любой «мусор». Сам триггер ТГС назван, на мой взгляд, неудачно, лучше было бы назвать его, например, триггером блокировки сбоев.

Следующая далее схема показывает (как водится, с ошибками) связь между триггерами ТКТРМ, ТПСБ и ТТО.

![Схема обработки сбоев, скан из [1] Схема обработки сбоев, скан из [1]](https://habrastorage.org/getpro/habr/upload_files/64d/cae/d14/64dcaed147a1374e23b77cd75e59140c.png)

Находящийся слева вверху элемент И формирует сигнал КТРМ («контроль машины»). По сути, это сигнал СБОЙ МАШ, т. е. признак наличия в РО хотя бы одного установленного разряда, но блокируемый следующими сигналами.

-

ТМКТРМ, он же бит РБР[5] — маска контроля машины, являющаяся 13-м битом PSW. Когда этот бит установлен, прерывания от схем контроля разрешены, когда сброшен — запрещены. Соответственно, если операционная система запретила прерывания от схем контроля, сбросив этот бит PSW, любые машинные ошибки процессором просто игнорируются.

Такое поведение аппаратуры является не совсем правильным: при возникновении сбоя, делающего невозможным корректное продолжение функционирования (а в ЕС-1020 все обнаруживаемые сбои собственно процессора именно такие, лишь сбои каналов не влияют напрямую на выполняемую программу), процессор должен либо вызвать обработчик прерывания, что невозможно из-за состояния маски в PSW, либо перейти в тяжёлый останов, но не продолжать работать, как будто ничего не произошло. По сути, маска контроля предназначена для того, чтобы остановить процессор, если новый сбой происходит во время выполнения обработчика прерывания от схем контроля, а также для блокирования сравнительно неважных прерываний от схем контроля (скажем, индикации отказа системы охлаждения — но в ЕС-1020 подобные неисправности не обнаруживаются) на время выполнения критического кода ОС.

БЛК СБ (показан прямым, но должен быть инверсным) — сигнал блокировки сбоя от переключателя на пульте управления. Режим блокировки сбоев может использоваться либо в процессе наладки процессора, либо когда достоверно известно, что вышла из строя сама система контроля, а останавливать машину для её ремонта в данное время нежелательно.

ТБЛПРВ — выход триггера блокировки прерываний. Этот триггер устанавливается на время выполнения пультовых процедур — например, считывания и записи содержимого памяти машины по нажатию соответствующих кнопок. Сами пультовые процедуры реализованы, по большей части, микропрограммно, и во время их выполнения, естественно, могут возникать сбои — но они не должны препятствовать, насколько это вообще возможно, выполнению этих процедур (предполагается, что человек, работающий с пультом, заметит загорание одного из индикаторов ошибок, если что-то пошло не так).

ТПСБ — на схеме ошибочно показана подача прямого выхода триггера; на самом деле на эту схему И подаётся инверсный выход, а прямой поступает вниз, к ТТО, о чём речь впереди. Когда ТПСБ установлен, т. е. когда выполняется обработка возникшего сбоя, сигнал КТРМ должен быть заблокирован, поскольку он вызывает установку одноимённого триггера, а это, в свою очередь, прерывает выполнение микропрограммы и вызывает переход к обработчику ошибок — а он и так выполняется.

Сигнал КТРМ по любому из тактовых импульсов ТИ4 и ХИ4 (ошибки могут возникать и при выполнении микрокоманд, т. е. в тактах ТИ, и в процессе вызова микропрограмм обслуживания каналов, т. е. в тактах ХИ, поэтому их возникновение должно обрабатываться и там, и там) устанавливает триггер ТКТРМ. Этот триггер, кстати, изображён с ошибкой: его прямой выход должен быть расположен сверху, а инверсный — снизу, причём последний не используется, а первый используется для установки ТПСБ и подаётся на схему синхронизации и схему формирования адреса следующей микрокоманды: установка этого триггера, как уже говорилось, приводит к приостановке серии ТИ и запуску серии ХИ, во время которой произойдёт переход на микропрограмму обработки ошибок.

Сброс ТКТРМ выполняется либо сигналом ГАШ СБОЯ, либо тактовым импульсом ТИ1. Первый из этих сигналов вырабатывается при нажатии соответствующей кнопки на пульте управления, что, вообще говоря, применяется только в процессе ремонта машины. Сброс импульсом ТИ1 происходит в начале выполнения первой микрокоманды обработчика ошибок.

Заметим, что ТКТРМ является шестым разрядом регистра РБД, о чём говорилось в соответствующей статье, но, судя по всему, он не может быть изменён микропрограммно (прямо скажем, это лишено смысла) и не может быть считан микропрограммой — точней, может, но всегда будет равен нулю, поскольку сбрасывается по ТИ1. Зачем понадобилось делать его частью РБД, мне непонятно; возможно, это пережиток раннего этапа разработки машины, который просто не стали менять, чтобы не затягивать запуск в серийное производство (другой вариант — с этим триггером не всё так просто, а доступная литература просто не даёт увидеть полную картину).

Установленный ТКТРМ устанавливает ТПСБ (его прямой и инверсный выходы тоже перепутаны) по ХИ3 такта, в котором производится выборка первой микрокоманды обработчика ошибок, — сам ТКТРМ устанавливается в конце предыдущего такта, в котором ошибка была зафиксирована в РО. ТПСБ сбрасывается сигналом гашения сбоя от кнопки на пульте. Кроме того, возможна микропрограммная установка или сброс ТПСБ путём записи в регистр РБД, седьмым битом которого он является. На схеме не показано, по какому тактовому импульсу происходит изменение ТПСБ микропрограммой, но, поскольку это изменение выполняется путём приёма информации с выхода БА, наверняка этим импульсом является ТИ4.

Инверсный выход ТПСБ, как уже говорилось, поступает на вход схемы И, блокирующей сигнал КТРМ, а прямой идёт далее, на вход элемента И, отвечающего за установку триггера тяжёлого останова ТТО (у этого триггера тоже перепутаны выходы: сверху должен быть прямой выход, а инверсный не используется). Установка ТТО при установленном ТПСБ происходит при появлении сигнала СБОЙ — он является сборкой всех сигналов установки триггеров РО (но не сборкой выходов этих триггеров, как СБОЙ МАШ).

Помимо тяжёлого останова при возникновении повторного сбоя, ТТО устанавливается ещё в трёх случаях:

при возникновении сбоя, если имеется сигнал ОСТ ПО СБОЮ — он формируется переключателем на пульте управления, что используется в процессе наладки для немедленного останова процессора при обнаружении сбоя вместо вызова микропрограммы его обработки;

по соответствующей микрооперацией поля УСТАНОВ — это происходит в определённых ситуациях при выполнении диагностических микропрограмм (установка ТТО в этом случае происходит по ТИ3, а не по ГИ3, как показано на схеме: последний сигнал — это сборка сигналов ТИ3, ХИ3 и СИ3, а останов должен происходить именно при выполнении микрокоманды, т. е. только в такте ТИ);

при обнаружении неисправности питания по ГИ3, если при этом триггер конца цикла памяти ТКЦП сброшен. Этот триггер уже упоминался в статье про регистры процессора: он устанавливается в начале обращения к памяти (в такте считывания или стирания) и сбрасывается в такте записи/регенерации. Назначение этого триггера — блокировать микропрограммную приостановку для обслуживания каналов или, как в данном случае, останов процессора при отключении питания в момент, когда идёт обращение к памяти, — чтобы не допустить её разрушения (напомню, что при считывании содержимое ячейки ферритовой памяти разрушается, поэтому за считыванием всегда записывается либо старое, либо новое значение, и данный триггер даёт возможность процессору выполнить эту запись).

Сброс ТТО возможен только по сигналу гашения сбоя, т.е. при нажатии соответствующей кнопки на пульте.

Заключение

Весьма обширные средства аппаратного контроля являются непременным атрибутом почти любой модели Системы 360 или ЕС ЭВМ, хотя архитектура и не требует их наличия. Благодаря наличию этой аппаратуры значительно возрастает достоверность получаемых при расчётах результатов. С другой стороны, наличие схем контроля значительно увеличивает объём аппаратуры — это одна из основных причин высокой сложности и стоимости процессоров мэйнфреймов по сравнению с процессорами мини-ЭВМ, выполненными на том же технологическом уровне.

В ЕС-1020 средства аппаратного контроля, как видим, не охватывают весь процессор, оставляя ошибкам и сбоям некоторые «лазейки». В более сложных моделях контроль становится полнее, а несколько позже появляются и средства коррекции ошибок (например, в ЕС-1033 при возникновении сбоя при выполнении команды производится попытка выполнить эту команду заново; в ЕС-1035 повторение реализовано уже на уровне отдельных микрокоманд, а для контроля памяти используется не обычная проверка чётности, а код Хэмминга, позволяющий «на лету» исправлять одиночные ошибки). В совокупности с соответствующей поддержкой со стороны операционной системы и при надлежащем оформлении прикладных программ всё это даёт возможность минимизировать последствия сбоев и отказов — например, перезапустить пострадавшие задания с контрольной точки, а не с самого начала, сэкономив иногда часы работы.

Литература

В. В. Пржиялковский и др. Процессор ЭВМ ЕС-1020. Под общей редакцией А. М. Ларионова. — М., "Статистика", 1975.