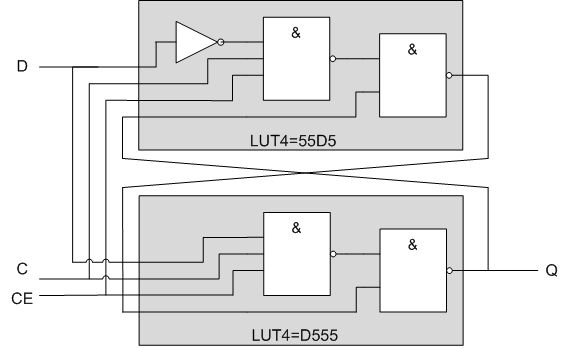

Однажды случилось так, что плата с кристаллом XC5VSX95T не заработала. Было известно, что это новая партия кристаллов. Для проверки проблемы был написан тест, тестирующий подряд все слайсы FPGA. Тестирование кристаллов показало наличие неисправных модулей LUT, входящих по 4 элемента в состав одного слайса. Оказалось, что триггеры в этих слайсах в порядке, и тогда был создан блок памяти на триггерах, которые в свою очередь созданы на LUT. См. рис. 1. Здесь показан пример триггера на LUT4. Каждая ячейка(бит) в тесте отвечает за один слайс. Триггерная ячейка задействует все четыре LUT слайса. Кристалл был разбит на 5 областей (и в другом тесте 9 областей), которые тестировались отдельно, каждый своей прошивкой. Правильное размещение используемых слайсов регламентировалось атрибутами LOC. Неисправность характеризуется невозможностью изменить состояние тестируемого триггера. Выход такого триггера может читаться 0 или 1, но всегда одинаково. Поэтому сначала память заполнялась 1, и проверялась, потом 0, и проверялась. Полный диапазон слайсов такой: X0Y0 – X91Y159. (14720 слайсов)

Рис.1

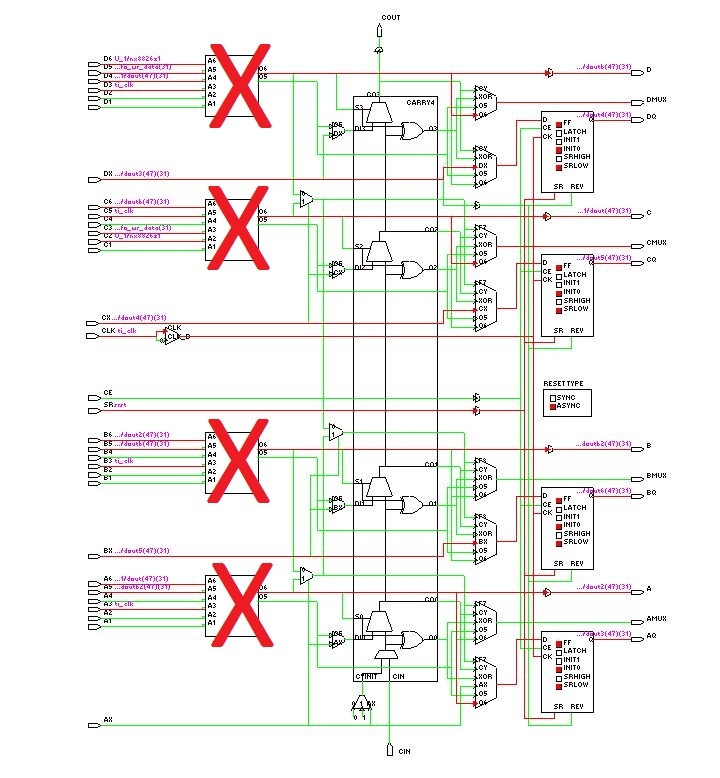

На рисунке 2 проиллюстрирована структура слайса ПЛИС Virtex5 и отмечены неисправные компоненты. Именно LUT5 оказались неисправными. Полный код проекта по известным причинам не размещается. Однако в архиве можно найти VHDL код реализации ячеек памяти на триггерах и на LUT.

Рис.2

Тестирование 3 плат показало:

BOARD #2 18 BAD SLICES:

SLICE_X26Y120 – SLICE_X26 Y128

SLICE_X27Y120 – SLICE_X27 Y128

BOARD #3 19 BAD SLICES:

SLICE_X26Y120 – SLICE_X26 Y128

SLICE_X27Y120 – SLICE_X27 Y128

SLICE_X26Y129

BOARD #4 19 BAD SLICES:

SLICE_X26Y120 – SLICE_X26 Y128

SLICE_X27Y120 – SLICE_X27 Y128

SLICE_X26Y131

Вывод:

при использовании плат требуется исключать из разработки плохие слайсы командой

CONFIG PROHIBIT=SLICE_X26Y120:SLICE_X27Y128;

CONFIG PROHIBIT=SLICE_X26Y129;

CONFIG PROHIBIT=SLICE_X26Y131;

Или лучше исключить сразу возможные все с запасом:

CONFIG PROHIBIT=SLICE_X26Y120:SLICE_X27Y131;

При нехватке ресурсов возможно организовать симуляцию использования дефектных LUT, чтобы иметь возможность использовать остальные исправные элементы этих слайсов.

Комментарии (10)

jok40

08.12.2017 11:09Вот это номер… Напомнило начало 90-х, когда дохлые ячейки в ОЗУ компа «Правец» пришлось изолировать резидентной ничего не делающей утилиткой, загружаемой прямо на них. Но сейчас то на дворе 2017-й! Причина таких странных выводов в конце статьи, я так полагаю, заключается в цене чипов?

Maksimuzz Автор

08.12.2017 12:57Да. скорее всего таки и есть. Вообще, бывали случаи поставки например микросхем FIFO с правильной надписью, но с абсолютно другим, неизвестным содержимым. А стоят они дорого, более $100 за шт.

old_bear

08.12.2017 16:37А каким софтом собирали тесты — ISE или Vivado?

Maksimuzz Автор

08.12.2017 23:26Софт ISE, это был проект с Virtex 5. Однако позже с незначительными изменениями был применен и для Kintex 7 в комплекте с Vivado. В ближайшие дни будет опубликован сезон 2 (: там будет готовый проекты для Vivado целиком, причем с встроенным UART и автоматом тестирования, потребуется только внешний клок и пин на выход для UART. Ну и переходник USB-RS232.

Cobolorum

08.12.2017 19:01Возникло 2 вопроса

1 Действительно ли тест «на триггер» закрывает все возможные сбои-ошибки в FPGA? Или он закрывает ваши риски в вашем проекте?

2 Можно ли что то сказать более конкретно об этой ошибке, написав дополнительные тесты?

Типа вывод 1 оборван или вывод 1 замкнут на земле?

Maksimuzz Автор

08.12.2017 23:30Гарантий, что тестируется все что можно конечно нет, однако отделить триггеры от LUT удалось. Кроме того, после исключения неисправных слайсов проект заработал как обычно. На тот момент это было решение. Но конечно, не самое хорошее. Поэтому почти сразу отказались от применения дефектных кристаллов.

nerudo

Отделу закупок отрубить одну руку и сказать что так можно сэкономить — на рукаве и перчатке. Происхождение партии известно?

Maksimuzz Автор

Да, с этим разобрались. Но когда столкнулись впервые, были мягко говоря обескуражены. Сколько раз наверное мы как разработчики пытались обвинить ПЛИС в плохой работе, выдумывали метастабильные состояния, но в конечном итоге оказывались виноваты сами.

Mirn

экономить часто приходится потому, что в России делают, например, как в моей бывшей компании:

Руководство решает что систему видеонаблюдения можно продать по 10тр за канал и точка — обсуждению не подлежит, закупаются самые дрюшлые айпивидеокамеры без обогрева, компы на атоме и устаревшем HDD и тд, а потом все удивляются куче рекломаций и фин жопе. Попытки продать например за 15тр или уговорить начальство что маркетинг тоже должен быть а не для галочки эффекта не взымели. В итоге даже у разработчиков ПЛИС вместо того чтоб сменить сгоревший кристал или целую отладку — судорожно покупается на авито подержанная отладка и удивляются чего она не работает или сколот чип. Естественно в продакшен ПЛИС часто покупается чуть ли не в разы дешевле чем офиц цена на сайте производителя — удивлению тоже нет предела — фишка в том это приходится делать, иначе маржа станет отрицательной такого "бизнеса".

В Японии сейчас делается так:

если ТЗ требует поднять цену FPGA с 1000 баксов до 3000 баксов то задача руководства:

В итоге стало работается очень спокойно и стабильно.

??