Сезон 2: Плата содержит 4 кристалла XC7K160T, которые не работают больше 2-3 недель. В чем причина отказа? Разбираемся

1.Программное обеспечение.

Была проведена проверка количества элементов LUT между триггерами. Она показала, что это

количество достигает 12, однако это не приводит к большим временным задержкам и легко

укладывается в 4 нс, и даже почти всегда в 3 нс. В процессе получения результата комбинаторных операций (сложение и сравнение многоразрядных чисел) есть опасность повышенного потребления тока и локальных разогревов из-за значительного разброса времен распространения импульсов, и как следствие появление предельных частот переключения до 1ГГц. На рисунке 1 ниже видно, что на каждый такт происходит не одно переключение, а несколько.

Рис.1

Поэтому была предпринята попытка применения конвейера для вычислений и оценка с

использованием симуляции на GATE уровне. Переключений оказалось не слишком много, и

конвейеризация привела только к повышению тока потребления, поэтому больше не применялась. Оценка кода показала, что он написан настолько оптимально насколько возможно. Любые изменения в частности и алгоритма (например, аппроксимация умножением, которое применимо при делении на фиксированную константу) могут привести лишь к увеличению используемых ресурсов. Поэтому дальнейшее касалось в основном поиска причин выхода из строя чипов.

2.Проверка температурного режима.

Одна из причин выхода кристалла из строя может быть перегрев. Критической температурой кристалла можно считать температуру более 80 градусов. По словам эксперта (Novomar) наступает “деградация” кремния. Обычно именно так проводят испытания на отказ кристаллов, за короткое время удается оценить, сколько проработает кристалл в нормальных условиях. Температурные измерения показали, что при самых плохих условиях и длительной работе температура выше 70 градусов не поднимается. (См. Рис.2) Из чего следует, что даже при тактовой частоте 300 МГц вряд ли может сократиться срок службы кристалла. На рисунке виден график, когда вычисление длится не долго. Было проверено, что в длительном режиме так же температура выше 70 градусов не поднимается.

Рис.2

3.Ток потребления ядра и переходные отверстия.

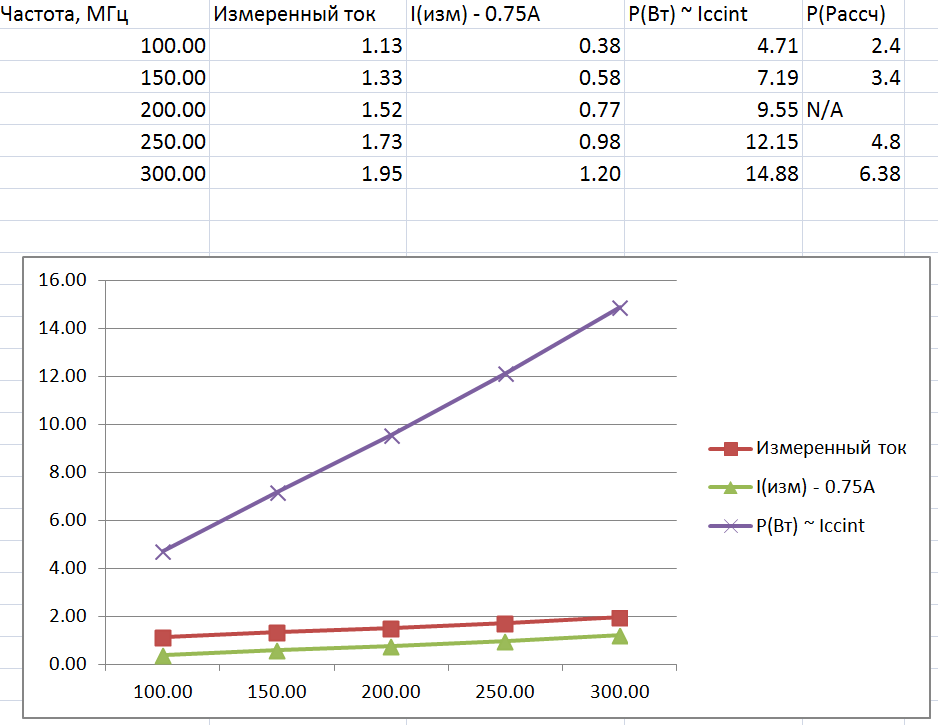

Был измерен ток потребления ядра (VCCINT и VCCBRAM) FPGA. Напряжение питания 1.0В.

На рисунке 3 приведен график тока потребления ядра от тактовой частоты блока обработки

данных. Реальный и расчетный. Расчетный меньше, поскольку режим отсутствия вычислений и

режим вычислений усредняется. Тут видно, что ток может достигать значения до 15 А, при этом

контактов питания у FPGA 21 шт. т.о. ток каждого пина примерно составит 0.7 А. В печати есть 2 места (M14, N13 и L13, K12), где на одно переходное отверстие приходиться 2 пина. Т.о. ток

составит 1.4 А. Расчетное значение на переходное отверстие 1.5 А, рекомендуемое разработчиками – 1 А. Было проведено испытание этих отверстий на разрушение от тока.

Длительное испытание током 4 А (несколько часов) никак не повлияло на переходное отверстие. Сопротивление его составило несколько mOhm. Кроме того, на плате со снятыми FPGA все отверстия были проверены на обрывы, которые не обнаружены. Вывод таков, что по этой причине плата в переразводке не нуждается. Причина выхода кристаллов из строя не в этом. На рис 3 приведен график мощности потребления ядром, но поскольку напряжение

питания ядра 1 В, то ток численно равен мощности.

Рис.3

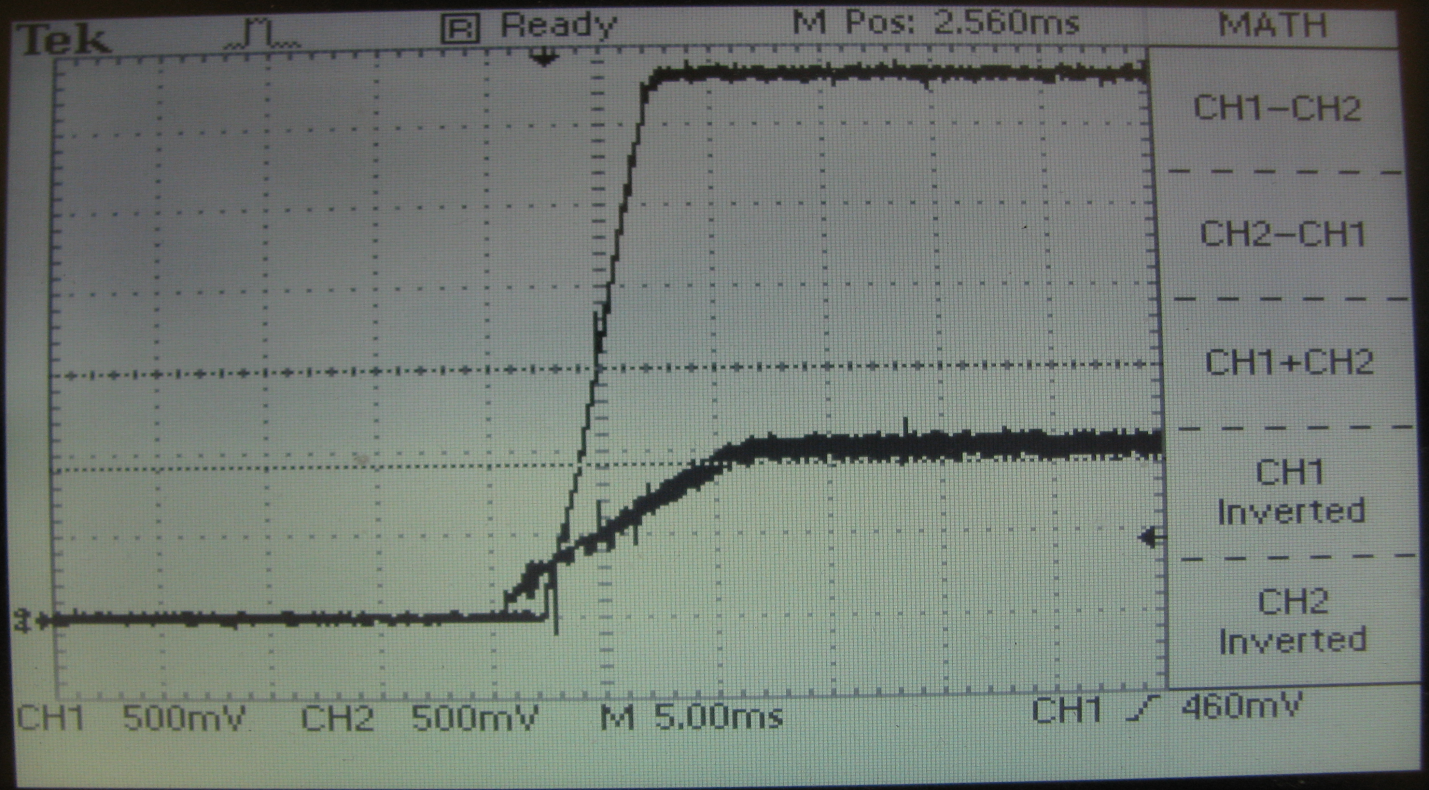

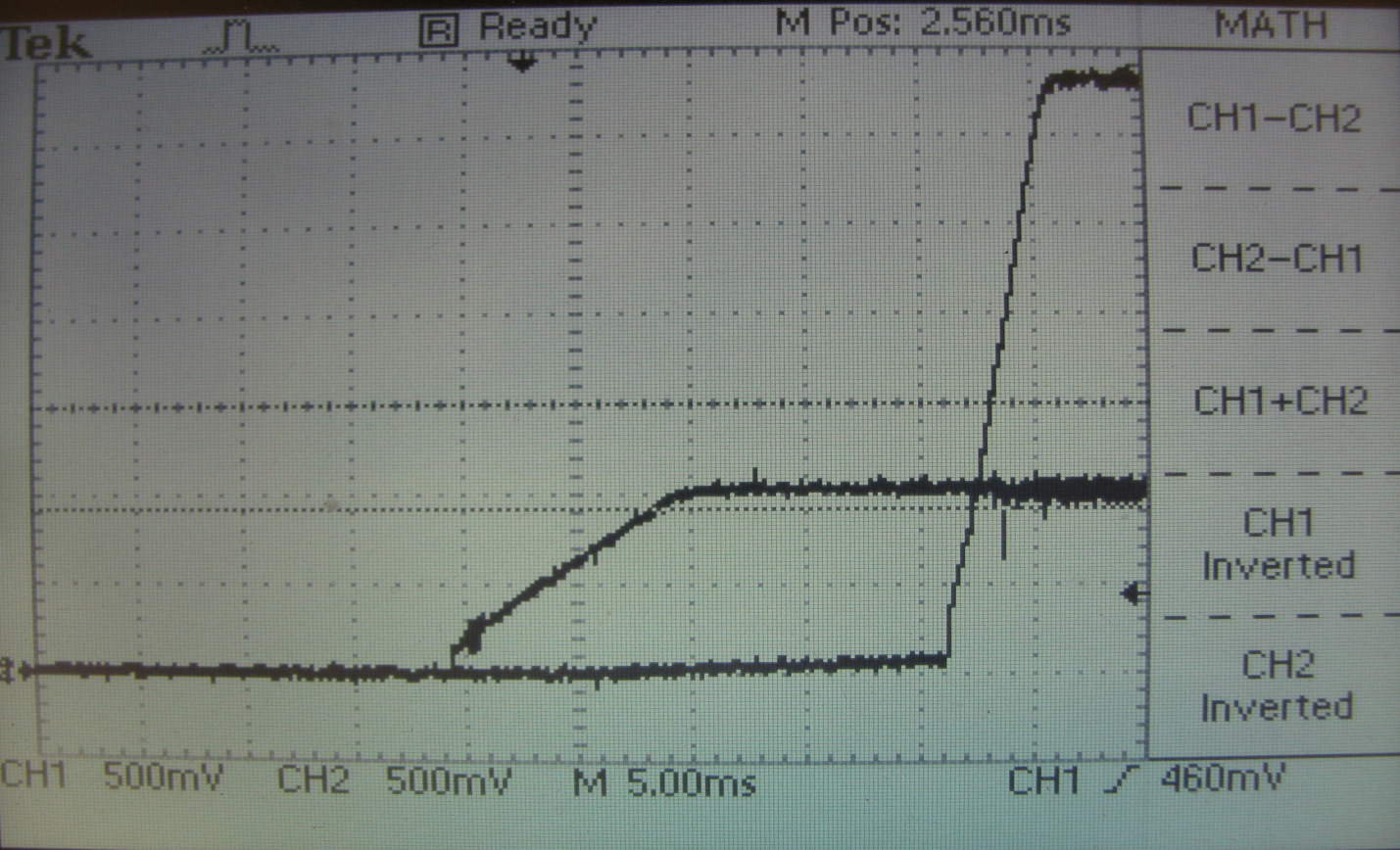

4. Последовательность подачи питания на кристалл.

Последовательность подачи питания на кристалл такова: VCCINT-> VCCBRAM->VCCAUX&

VCCO; VCCINT и VCCBRAM допускается подавать одновременно. В данном проекте последовательность нарушена. Это видно на осциллограмме на рисунке 4. В течение 5 мс

напряжение VCCO 3.3 В превышает 1.5 В, а VCCINT еще не вышел на номинальное значение. Это

не рекомендуется производителем.

Рис.4

Однако в такой ситуации выход из строя возможен в момент включения питания. А реально

кристалл выходит из строя во время длительной работы. Тем не менее, рекомендуется на

контакты INHIBIT стабилизаторов 3.3 В и 1.8 В установить конденсаторы 1.0 мкФ на GND. Это

позволит задержать их запуск на несколько миллисекунд, и обеспечить выполнение требования

последовательности включения питания. См. рис. 5.

Рис.5

5.Принципиальная схема

Изучение схемы показало, что на пин M12 VCCADC подается питание 3.3 В. Это нарушает

предельно допустимые значения для кристалла, которое составляет для этого пина 2.0 В, номинал 1.8 В. Необходимо либо переразвести плату и подключить этот пин к 1.8 В, либо уменьшить питание 3.3 В до 1.8 В. Но тогда требуется переключить сигнал CFGBVS_0 подключить на GND. Также это может изменить другие режимы, поэтому, кажется, лучше переразвести.

6. Изучение состояния неисправных кристаллов.

На исправном устройстве обнаружена проблема с ресетом. Т.е. при включении все светодиоды горят и устройство не выходит в рабочий режим. Проблему удалось обойти, убрав внешний ресет, и генерируя его внутри кристалла. Однако, на неисправном образце проблема на 3 чипах из четырех. На двух из них внутренний сигнал RST никак не реагирует на изменение состояния пина (J26), на одном — реагирует только если его замыкать на землю, а так у него состояние 1, хотя должно быть 0. И только на одном корректно работает. Это наводит на мысль, что-либо это результат воздействия на пин статического электричества, (хотя, мне сказано, что пин не используется), либо проблема тоже связана с неправильным питанием пина ADCVCC(M12), или с неправильным порядком включения питания.

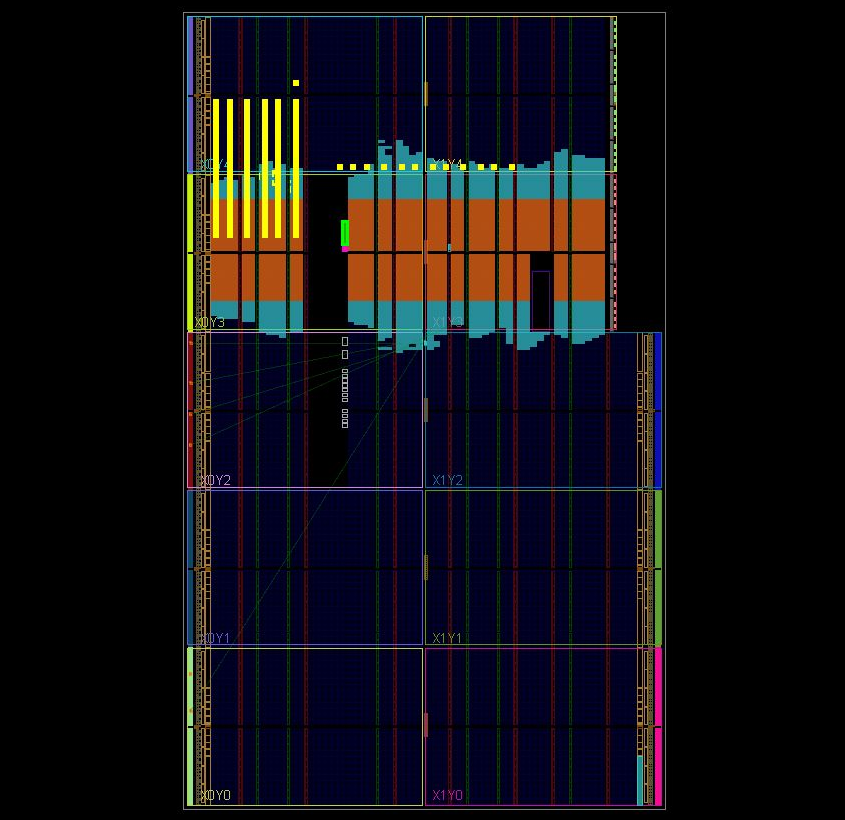

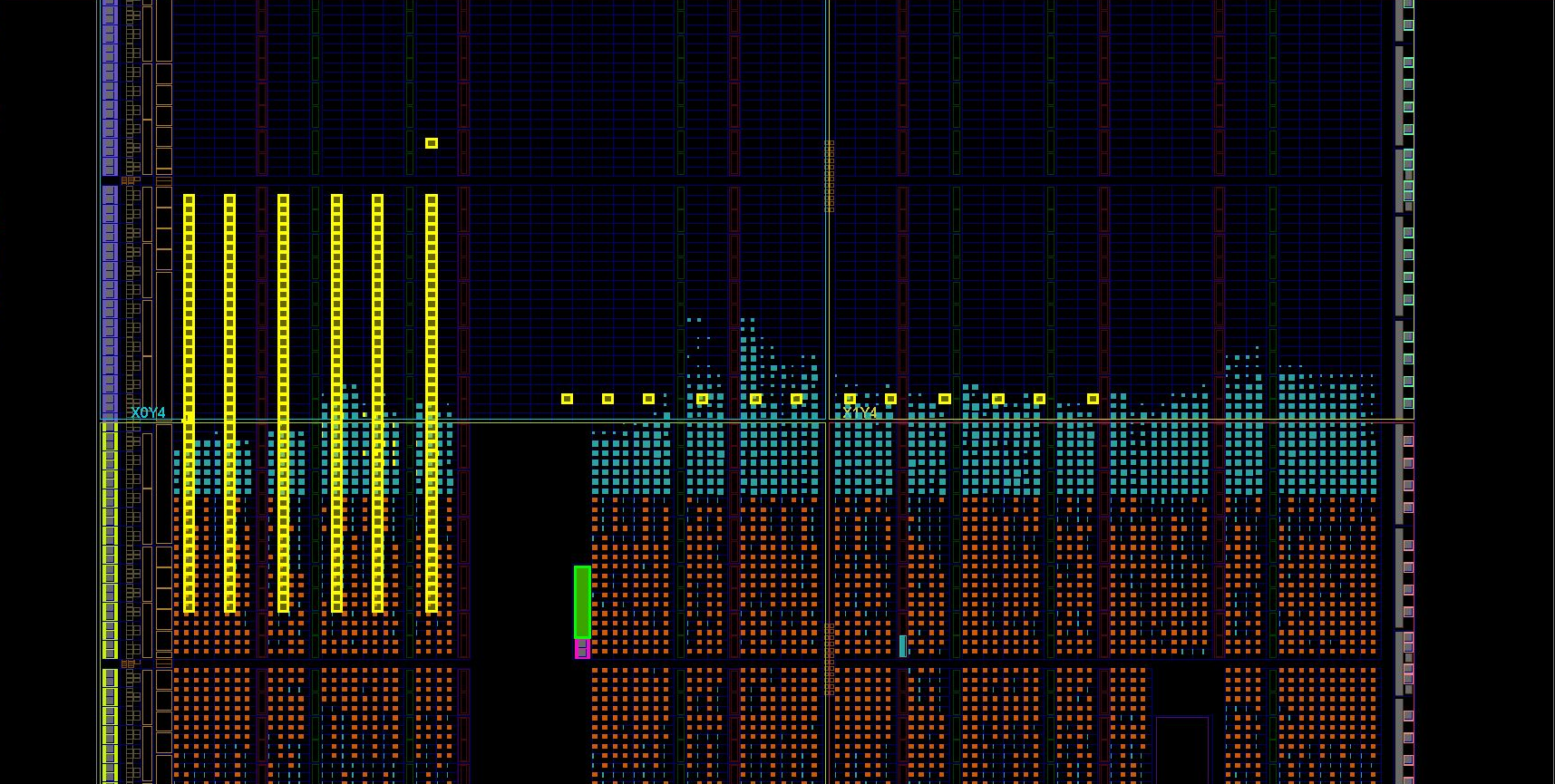

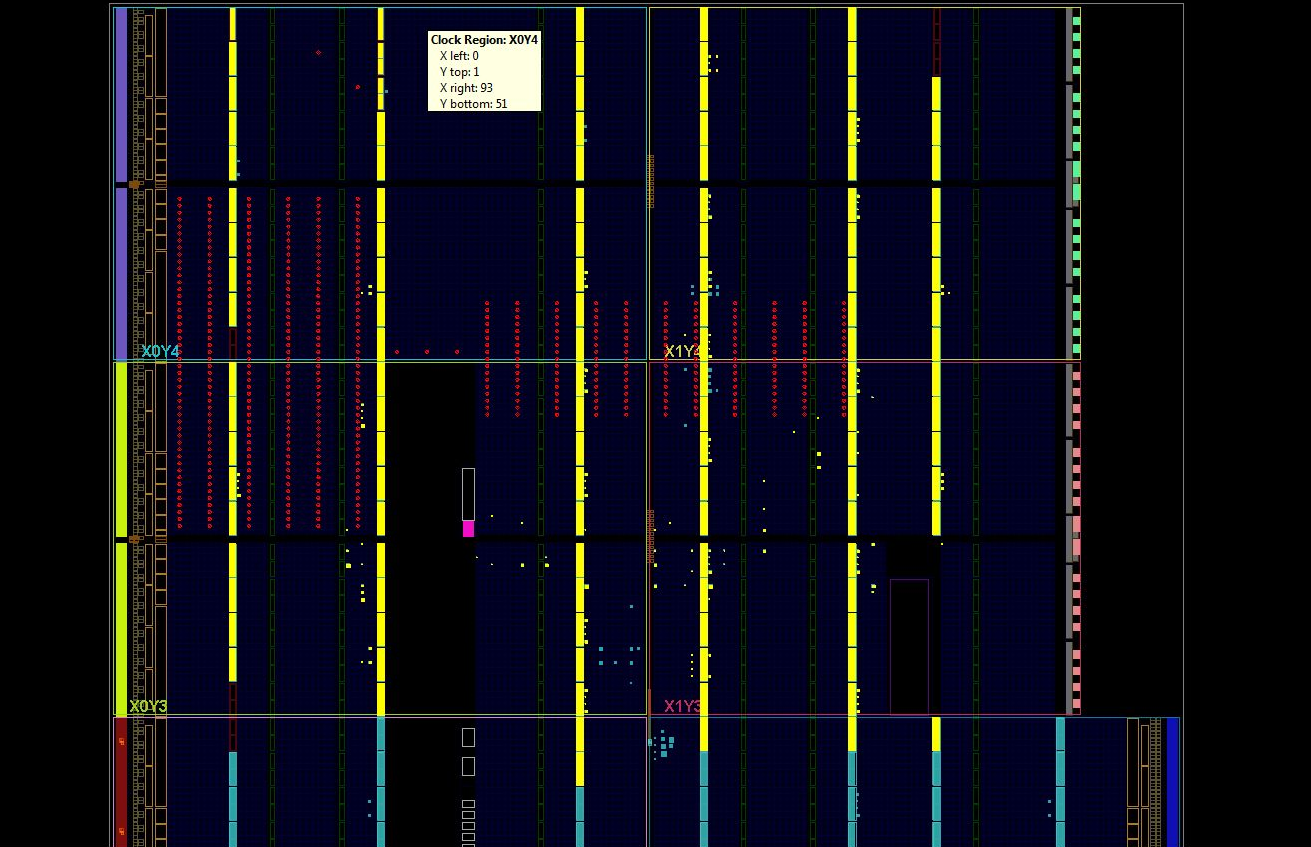

6.1 SLICES

Теперь самое интересное. Была написана программа, заполняющая по очереди слайсы

(элементарные ячейки) триггерами, и организована память на них. Сканирование кристалла

показало наличие неисправных элементов. На рис. 6 показаны эти элементы желтым. (Кроме

бледно-желтой полоски по левому краю). На рис.7 более подробно.

Рис.6

Рис.7

Результат тестирования можно посмотреть в лог файлах. Расчет неисправного элемента выглядит так: Например, файл: test_X0-108Y160-191_Dev1(com5).txt

ERROR AT A:000D

WR:55555555

RD:43555555

Адрес 0xD, 13: Позиция слайса: X = 13, Y = 160 + (позиция неправильных битов) = 160 + 25 = 185 и остальные: 186, 188. Итак, X=13, Y = 185, 186,188

Так были получены позиции неисправных слайсов. Сам тест с исходниками в архиве TEST_SLICES (27'07'2016). В папке Versions лежат и bit файлы для запуска. Они рассчитаны на кварц 125 МГц, скорость порта 115200. На рисунках видно еще зеленый прямоугольник, это блок XADC, тот у которого неправильное питание, 3.3 В вместо 1.8В. Если XILINX близко к действительности показывает расположение элементов, то видно, что предположение о порче кристалла по этой причине может быть правдой. Исключить битые слайсы из системы и запретить разводчику их использовать можно командами:

set_property PROHIBIT 1 [get_sites SLICE_X17Y243] — запрещает отдельные слайсы.

set_property PROHIBIT 1 [get_sites -range SLICE_X1Y176:SLICE_X25Y223]

— запрещает набор слайсов.

Полный набор таких команд можно найти в фале main1.xdc в проекте архиве BRAM_TEST.

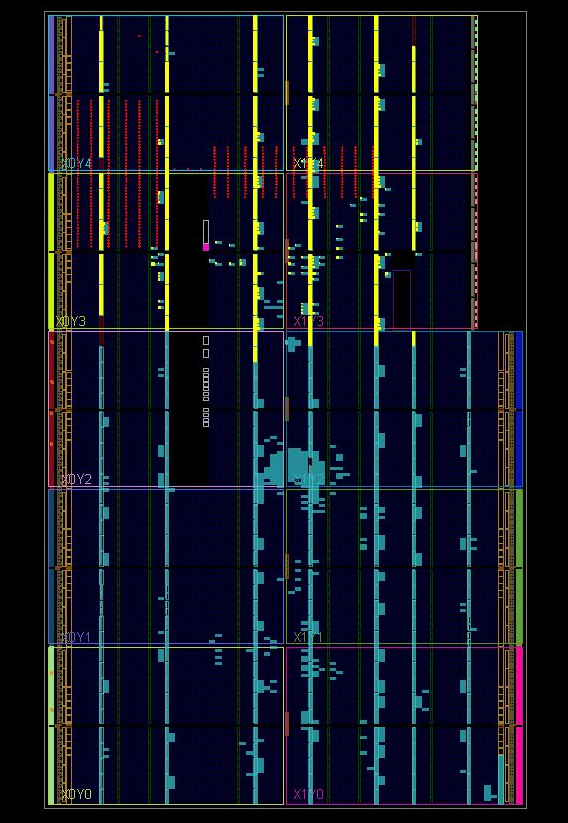

6.2 BRAM

Используя данные о битых слайсах был построен тест с использованием 98% блоков

памяти. Результат тестирования на рис. 8.

Рис.8

Более подробно на рис.9. Красными точками помечены неисправные слайсы, не используемые

для работы теста.

Рис.9

Можно видеть, что почти половина памяти BRAM повреждена. Причем поврежденная область так

же находиться ближе к модулю ADC, на который подается неправильное питание. Возможно это

не случайность. Если учесть, что тест слайсов показывает не все неисправности, а только по

одному триггеру и несколько LUT на слайс, считаю использовать кристалл с ограничением

количества ядер для проекта не эффективно. Его работа будет непредсказуема, и может не

показывать надежных результатов. К тому же, слишком велики повреждения BRAM. И также

нужно учитывать, что на некоторых других чипах могут быть другие повреждения и не совпадать с уже найденными.

Заключение:

1. Плата нуждается в переразводке с исправлением питания на ADC_VCC(M12) и установке

дополнительных конденсаторов на выводы INHIBIT стабилизаторов +3.3В и +1.8В. Также, если

сигнал RST выводиться за пределы платы с помощью длинных проводов (не считая платы со

светодиодами), желательно предусмотреть защиту от статического электричества.

2.При большой необходимости можно попробовать собрать проект, например, на 80-90

ядер, внеся ограничения на использование BRAM и SLICES, без использования внешнего пина RST, применив внутренний сгенерированный ресет.

PS: После выполнения рекомендации 1 проблемы пропали.

М. Е. Генералов, 2018

Комментарии (22)

dernuss

15.01.2018 08:06Ну хорошо что XC7K160T не очень дорогие

Тем не менее, рекомендуется на

контакты INHIBIT стабилизаторов 3.3 В и 1.8 В установить конденсаторы 1.0 мкФ на GND.

Помоему лучше использовать сигнал POWERGOOD для последовательного включения питания

Maksimuzz Автор

15.01.2018 08:26Согласен. Хотя иногда сложные проблемы имеют простые, легкие для понимания неправильные решения:)

Maksimuzz Автор

15.01.2018 08:241. Неисправные ПЛИС больше не использовались.

2. Это интересно, сказать честно, я не знал о возможности контролировать состояние SRAM, в которой хранится конфигурация. Этот проект завершен, но в будущих проектах возможно это будет полезно. Спасибо.

3. Питание было проконтролировано осциллографом и проблем замечено не было, думается что этого достаточно. К тому же, характер повреждений такой, что после повреждения уже ничего не восстанавливается. А в описанном случае скорее всего случались бы ошибки одноразовые и восстанавливающиеся.

Goron_Dekar

15.01.2018 13:08+1Изучение схемы показало, что на пин M12 VCCADC подается питание 3.3 В. Это нарушает предельно допустимые значения для кристалла, которое составляет для этого пина 2.0 В, номинал 1.8 В. Необходимо либо переразвести плату и подключить этот пин к 1.8 В, либо уменьшить питание 3.3 В до 1.8 В. Но тогда требуется переключить сигнал CFGBVS_0 подключить на GND. Также это может изменить другие режимы, поэтому, кажется, лучше переразвести.

Хм. Действительно, вы подали в 2 раза большее напряжение на пин. Возникает вопрос: почему вы после этого продолжили искать другие ошибки и тестировать память? Часто ли у вас такие вот грубые нарушения рекомендуемых условий эксплуатации, что называтеся, «прокатывают»? Спрашиваю не троллинга ради, мне действительно интересно, насколько свято надо бдить графу max в Voltage characteristics

Maksimuzz Автор

15.01.2018 13:17Я не являюсь разработчиком схемы, меня попросили как эксперта найти и исправить проблему. Изначально правильность схемы считалась фактом, поэтому я начал не с этого. Самое на мой взгляд интересное тут, вот что: Вот Вы часто наблюдали, как ведут себя FPGA с неправильным питанием? Я впервые. На моей практике FPGA одни из самых надежных компонентов и выходят из строя в последнюю очередь. И то, что выходят из строя компоненты FPGA вокруг места с неправильным питанием для меня удивительно и очень интересно. Когда я понял, что питание неправильное, как раз и стало интересно проверить, что именно внутри не работает. А как проверить, если просто не работает и все. FPGA не имеет дисплея, не может сама сообщить, где проблема. Получилось интересное исследование.

Goron_Dekar

15.01.2018 18:28+1Исследование, конечно, интересное. Даже иногда завидно, что у людей хватает времени и внимания довести такое исследование до конца. Большое спасибо за статью.

amartology

15.01.2018 15:06Это зависит от того, какие транзисторы стоят в схеме в уязвимом месте. Типовые напряжения, на которые рассчитываются транзисторы разных типов, содержащиеся в кристалле — это 1.2, 1.8, 3.3, 5 В. При этом запас по напряжению обычно не очень большой. Например, для семейства техпроцессов 180 нм одной из популярных фабрик на транзисторы, имеющие номинальное питание 1.8 В, запрещено подавать больше, чем 1.98 В (+10%), в противном случае фабрика не гарантирует ресурс микросхем. Опыт говорит, что на коротких дистанциях такие транзисторы пробиваются где-то на 2.5 В, не позже. И чипов я на испытаниях пожег довольно много, в том числе выясняя, при каких напряжениях и посему именно они ломаются.

Так как проблем на длинных временах работы вы тоже скорее всего не хотите, то могу, как разработчик микросхем, порекомендовать вам бдить цифры, записанные в absolute maximum ratings, максимально свято.

С другой стороны, схемы ввода-вывода, рассчитанные на питание 3.3 В, часто делают на пятивольтовых транзисторах, и там бывает можно подать побольше без вреда для транзисторов. Но так как пользователь не может знать, как именно устроен чип, смотрите рекомендацию выше.

nckma

15.01.2018 15:47Что-то у меня такие статьи вызывают только скепсис.

Что значит поиск «внутренних деффектов ПЛИС»? Какие еще такие деффекты?

Далее по статье читаю, что схема платы имела деффект по питанию — и что это? Разве это деффект ПЛИС?

Думаю ксилинкс на вас может в суд подать за нанесение урона имиджу.

Shpakov

15.01.2018 16:24+1Да вроде всё логично — схемотехнические ошибки привели к возникновению дефекта внутри ПЛИС и автор статьи выяснил, какой именно дефект появился.

nckma

15.01.2018 16:26-1Ну так статью тогда назвать «Поиск деффектов платы с ПЛИС».

Maksimuzz Автор

15.01.2018 17:20Все очень просто, первый сезон был действительно про дефект в плис. А тут меня пригласили как эксперта найти в чем дело. Плисы уже дефектные, нужно было выяснить постфактум, что произошло. Это как исследование катастроф.

amartology

15.01.2018 18:43ПЛИСы не были дефектными ни в какой момент времени, они работали точно так, как должны были. Дефектными были разработчики платы, которые подали на микросхемы недопустимое напряжение и спалили их. Срок службы 2-3 недели вместо 15 лет — это типичная картина пробоя подзатворного диэлектрика при длительном перенапряжении.

Maksimuzz Автор

15.01.2018 18:48Не ошибается тот кто ничего не делает.

amartology

15.01.2018 18:51Это, разумеется, так. Но валить вину с больной головы разработчиков, допустивших ошибку, на здоровую голову производителя микросхемы — это неправильно.

old_bear

15.01.2018 23:15Не обязательно все читали «первый сезон». IMHO, вам имеет смысл превозмочь себя, и добавить в начало этой статьи несколько человеческих слов, а не начинать как бы минуту назад прерванный разговор узких специалистов.

Maksimuzz Автор

16.01.2018 08:35Спасибо. Вы правы. Действительно каждый пост должен быть законченным и независимым. Учту это в будущем.

lingvo

15.01.2018 19:12Хмм, интересно. У нас были подозрения на неисправную память BRAM в Virtex-7, но Xilinx нам сказали — либо ПЛИС работает, либо нет. На этом мы успокоились и по-моему в конце концов нашли причину в неправильно подключенном клоке где-то в прошивке.

А Вы можете поделиться исходниками тестов BRAM — насколько с помощью них делать прошивки и легко ли портируются они под другие чипы?

Maksimuzz Автор

15.01.2018 21:02Конечно, для этого и пишу. В тексте есть две ссылки на проекты для SLICE и для BRAM, написанные в Vivado на VHDL.

Inanity

1. После переразводки платы «неисправные» ПЛИСы были перепаяны на новую плату? Нельзя исключать то, что всё могло заработать и ПЛИСы не были убиты/неисправны и т.д.

2. Такое ощущение, что у вас SRAM память конфигурации бьётся в процессе работы. Уверен, вы в курсе, что такое SEU (Single event upset), но заряжённая частица из космоса — не ваш случай. Тем не менее в 7-ой серии Xilinx есть внутренний контроллер Soft Error Mitigation Controller, который следит за контрольной суммой конфигурационной SRAM в процессе работы ПЛИС. Было бы очень интересно на проблемной плате вставить этот блок в дизайн и проследить за его поведением. Если проблема в изменении памяти SRAM, то он это отловит. Если инвертируется битик конфигурации, отвечающий за таблицу истиности LUT, получится логический сбой, то же самое и со всем остальным.

3. Вы уверены, что мощности источника питания VCCINT и VCCBRAM хватает на всех режимах работы? Пиковое потребление может быть и выше озвученных 15А в переходных режимах. Чтобы это отловить нужен чувствительный токовый пробник, а не медленный амперметр.