Приветствую, Хабр! Меня зовут Даниил Смирнов, я учусь в аспирантуре Университета ИТМО, где в лаборатории программирования и моделирования наш коллектив занимается программируемой электроникой для проектов, связанных с волоконно-оптическими датчиками. В качестве аппаратной базы для датчиков используются FPGA – Field Programmable Gate Array. Пару лет назад мы узнали о том, что производители FPGA проводят конкурсы среди студентов по разработке. С тех пор каждый год от нас формируется команда для участия в этом мероприятии, а поскольку в этом году оно получилось особенным, мы решили поделиться как все было изнутри.

Шел октябрь 2017 года, я делал еженедельную рутинную проверку: анализ проходящих конференций по темам, которые реализуются на нашей кафедре. В один момент мне приходит рассылка от Terasic: стартует новый конкурс по разработке проектов с использованием отладочных плат на FPGA, теперь всемирный. В голове проносится и вспоминается опыт этого же конкурса прошлого года: откладывание до последних двух недель месяца, долгая отладка и настройка алгоритмов и выдачи всех каналов на монитор и обещание больше не откладывать это на последний день.

Это был крутой опыт, в ходе которого мы узнали много нового о такой платформе как SoC FPGA – единение между собой огромного массива логических элементов и процессора Cortex-A9, а так же их взаимодействие между собой и с периферией на отладочной плате.

Новый конкурс – новые правила, новые требования, новый уровень. Теперь конкурс проводится в несколько этапов: сначала проводятся региональные этапы, а затем финал в Сан-Хосе; плату всем участникам высылают одинаковую, DE10-Nano, а в дополнение теперь можно выбрать не только базовые три модуля, но и большой вариант плат от Analog Devices! Однако, в отличие от конкурсов в предыдущие годы в этот раз необходимо подписать гарантию выполнения проекта, а в случае невыполнения – участники должны отправить платы обратно. Вполне справедливо с учетом статистики прошлых лет:

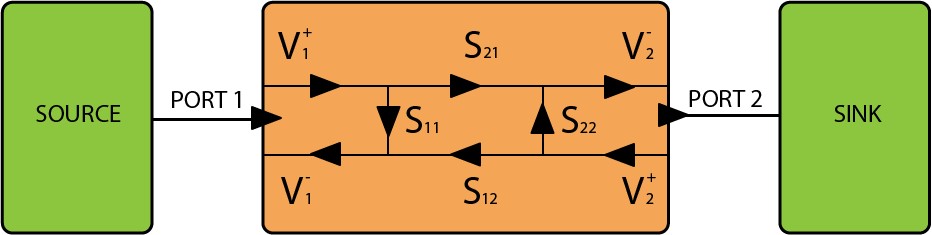

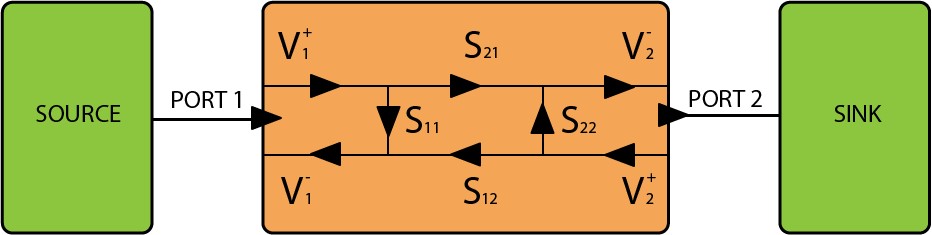

Чтобы проект не остался в стороне, решено было реализовать полезное для кафедры устройство, которое потом можно будет несложно дорабатывать и улучшать. Исходя из областей деятельности кафедры были различные варианты: оптический рефлектометр, стробоскопический осциллограф и др. Быстро просмотрев уже существующие заявки и доступные дополнительные платы выявлено, что рефлектометр уже заявили, а стробоскопический осциллограф на таких элементах не собрать. Единственная идея осталась живучей – векторный анализатор цепей. На днях в лабораторию принесли пару связных катушек, на которые отсутствовала какая-либо документация. Задачей было определить хотя бы приблизительные характеристики этих катушек. Известно было, что в них собран колебательный контур, поэтому главной задачей было выяснить резонансную частоту. В подобных задачах как раз и может найти применение векторный анализатор цепей (ВАЦ или VNA – Vector Network Analyzer). VNA позволяет определить матрицу рассеивания, известную также как матрица S-параметров. В таком методе исследуемый элемент рассматривается как черный ящик, у которого проводят анализ падающих и отраженных сигналов от портов этого устройства. Так, для двухпортовой системы матрица выглядит следующим образом:

Где V1+ V2+ – электромагнитные волны, поступающие на порты;

V1- V2- –электромагнитные волны, выходящие из портов;

Sij – элементы матрицы рассеяния многополюсника. [2]

Схема измерения S-параметров многополюсника

Рентгеном рассмотреть компоненты и схему не удалось (по крайне мере рентгеном метрополитена), поэтому на коленках было собрана следующая схема: через циркулятор на вход катушки с использованием генератора поочередно подавались частоты с выставленным шагом, второй порт циркулятора подключался на вход катушки, а третий вход – на осциллограф, имеющий в своем ПО режим амплитудно-частотного анализа. Такая схема позволяет измерить параметр S11, т.е. отражение. В конечном итоге после долгих мучений и калибровок снять данную характеристику удалось – но какой ценой? На кафедре давно ожидалось приобретение векторного анализатора цепей для подобных задач (измерения АФЧХ радиоэлектронных устройств), но эта закупка всегда каким-то образом откладывалась.

После возни с катушками было решено собрать свой собственный анализатор цепей с визуализацией и комфортной настройкой. Найти азарт и желание узнать что-то новое для себя у студентов и аспирантов, работающих на кафедре, несложно, поэтому команда была быстро собрана из электронщика, программиста-разработчика систем на кристалле, меня и двух наставников.

Сказано – сделано! После многочисленных обсуждений о полосе частот, алгоритмах обработки и других параметрах проекта заявка содержала следующее:

Для прохождения в следующий этап необходимо было чтобы страница проекта набрала достаточное количество «лайков» от зарегистрировавшихся на сайте пользователей. Первое время всё шло неплохо, однако затем некоторые сомнительные проекты начали набирать нереалистичные и контрастные по сравнению с остальными проектами значения лайков и просмотров. Оказалось, сайт конкурса был слишком уязвим к накрутке.

Через некоторое время организаторы оповестили, что финалистов все равно будет выбирать коллегия судей, поэтому лайки от пользователей, по сути, потеряли свой вес. 31 января в списках прошедших в следующий этап появилась и наша команда и мы начали детальнее продумывать наш проект в ожидании отладок.

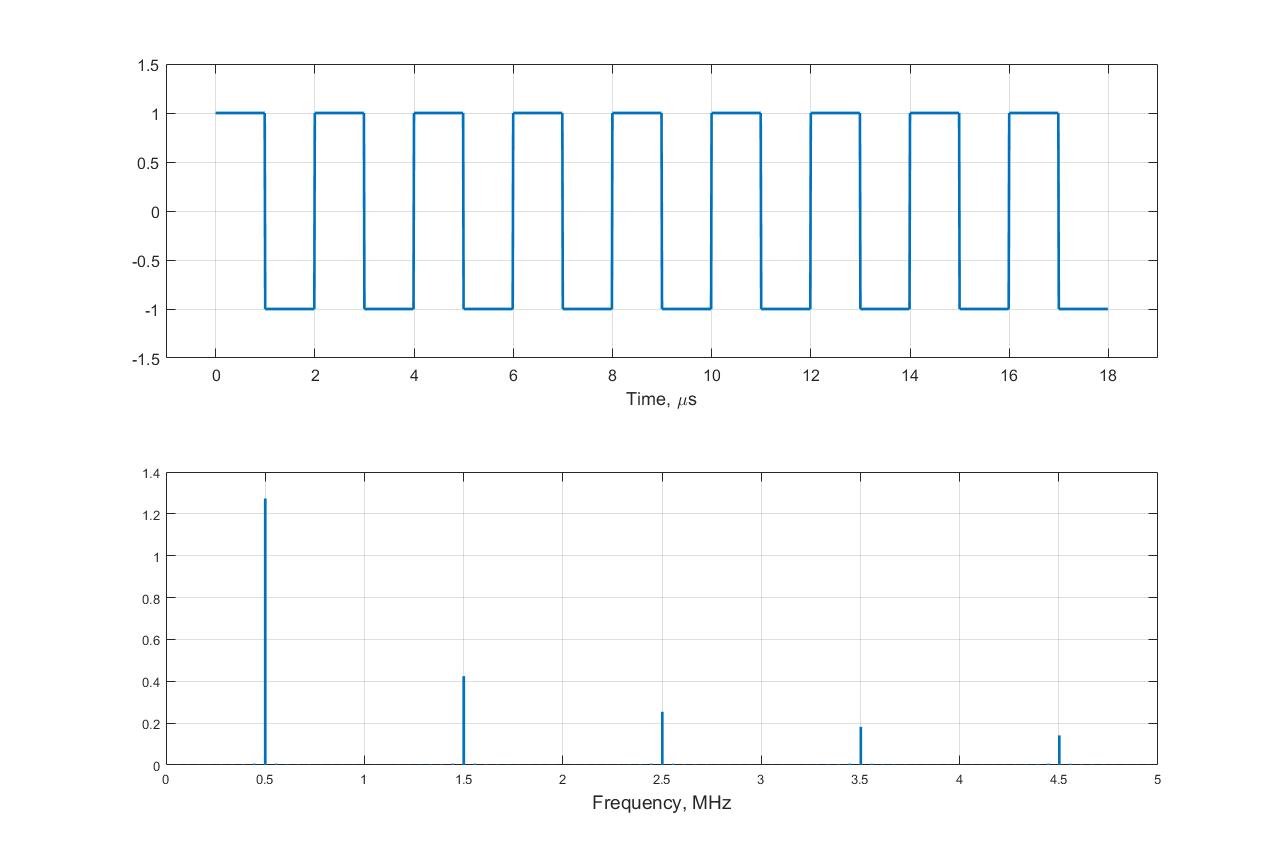

Первой пришла плата DE10-Nano. Приятно, но немного странно: ожидали, что платы придут все вместе. Спустя несколько дней поступает звонок с таможни: пришли платы, они все вместе превышают порог по цене, поэтому необходимо заплатить за растаможку сумму примерно равную стоимости этих плат. Такой расклад нас огорчил, но не устроил: от плат мы отказались. В наличии миксеров и генераторов у нас не было, необходимо найти новые решения. Что же делать? Первым в голову пришло не самое точное, но довольно необычное решение: использовать обычную ножку GPIO и с неё генерировать меандр. На выходе этой ножки устанавливается аналоговый ФНЧ с полосой среза чуть больше максимальной частоты меандра. Включать анализ для начала предлагалось с 1МГц (к примеру): тогда после фильтра мы получили бы более-менее чистый синус (старшие гармоники отрезались бы фильтром), и так далее до тех пор пока частота не опустится до той, на которой в сигнале после фильтра будет две гармоники. Меандр – это сумма нечетных гармоник, причем пропорциональный вклад каждой гармоники заранее известен [3].

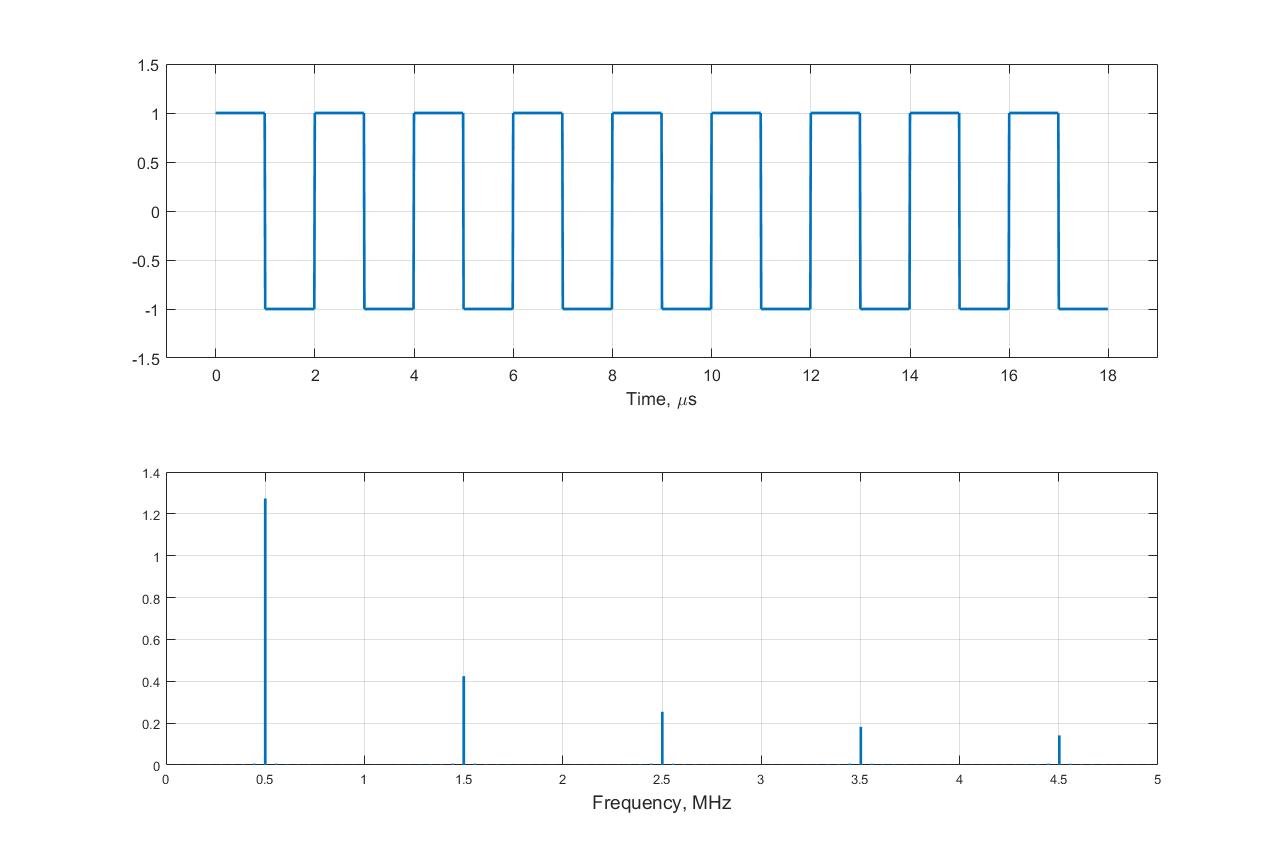

Пример меандра во временной и частотной областях: на спектре видны составляющие сигнал гармоники на 500кГц, 1.5МГц и др.

С фильтром с частотой среза 1 МГц можно спускаться до 33.(3) кГц. После этой частоты за фильтром мы должны получить сумму двух синусов. Пропорциональное соотношение их амплитуд известно (sinc-функция), отклик измеряемого устройства на частоту 1 МГц (первая нечетная гармоника) тоже, значит нам остается составить уравнение с одной неизвестной и вычислить характеристику отклика на частоту 33,(3) кГц! Сначала это решение показалось слишком простым, поэтому для начала оно рассказано было всем в надежде что кто-нибудь найдет ошибку. Ошибки не нашлось, но по мере обсуждения был обнаружен ряд ограничений:

Допустим мы все проблемы по аналоговой части решили; программно возникают две других:

И, наконец, последнее по порядку, но не по значению. Описанная схема может использоваться если измеряемый элемент можно описать линейной передаточной функцией. Однако если мы будем измерять черную коробку с нелинейными характеристиками – от идеи больше проблем, чем пользы. Времени оставалось немного (Первый результат надо показать уже через два месяца после прихода платы), поэтому после непродолжительных размышлений мы решили перепроверить наши запасы по уже имеющимся отладочным платам – и нашли 14-битный ЦАП на 125 Msps! Не самое элегантное решение, но выбирать не приходится, используем его в качестве генератора выходного сигнала.

Выбранный ЦАП в качестве генератора принимает на вход параллельной шины данные и защелкивает его тактовым сигналом, идущим с ПЛИС. Такая схема идеальна для синхронизации в нашей схеме. Однако с детектированием оставались вопросы.

Да, на этой же плате есть 14-битный АЦП на 65 Msps. Но вот только возможности генератора потенциально выше, а по теореме Котельникова данный АЦП уже не подойдет на максимальных частотах.

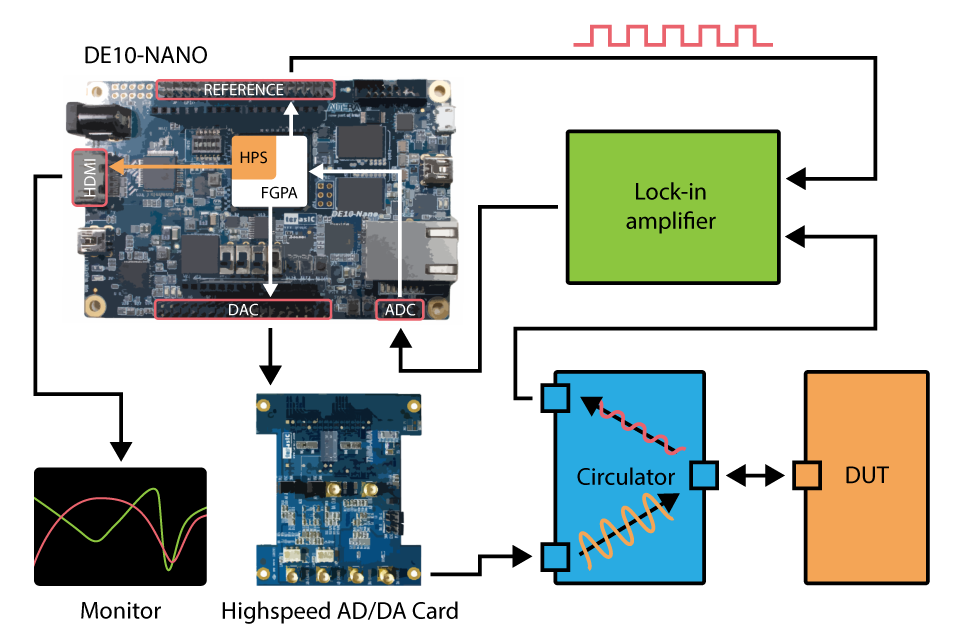

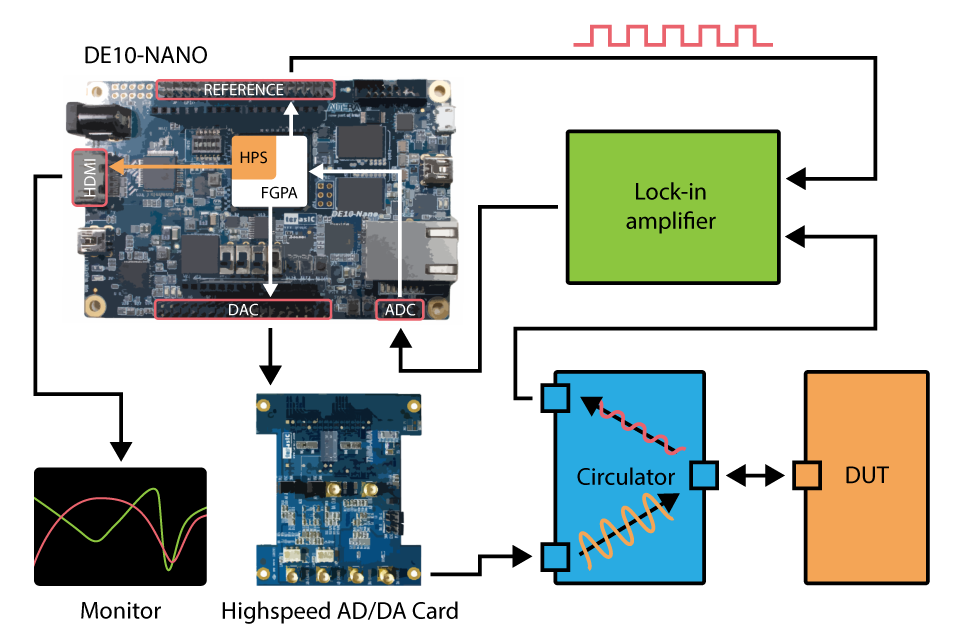

Решение было найдено в ходе обсуждения этой задачи с опытными электронщиками. Оказалось, что для нашей задачи мы можем воспользоваться схемой синхронного детектора (lock-in amplifier): выходом такого детектора являются две постоянных величины, фазовая и квадратурная составляющие, из которых можно получить амплитуду и фазу сигнала, а так как они постоянны, их можно детектировать даже с помощью медленной АЦП, установленной на DE10-Nano! Решено было сначала отмоделировать схему в LTSpice, а уже потом подбирать компоненты и собирать схему, с учетом того, что входом детектора является сигнал с циркулятора, а выходы подключаются к АЦП на плате DE10-Nano.

Обновленная концепция проекта

Синусоидальные сигналы с частотой от 1 Гц до 1 МГц с выставленным шагов в несколько Гц поступали на первый порт циркулятора. Ко второму порту подключалось исследуемое устройство, в зависимости от частотной характеристики которого происходило изменение коэффициента отражения сигнала. Отраженный сигнал поступал на 3 порт, где для определения частотной и фазовой характеристик была собрана схема синхронного детектора. Для корректной работы было осуществлено согласование портов циркулятора под импеданс 100 Ом, что было связано с выходным сопротивлением ЦАП и выбором исследуемых устройств.

До сдачи проекта оставалось меньше месяца, а к концу срока необходимо было ещё и подготовить отчетные материалы: подробное описание проекта на странице конкурса, проект, выложенный на GitHub в открытом доступе и видеоотчет о проделанной работе.

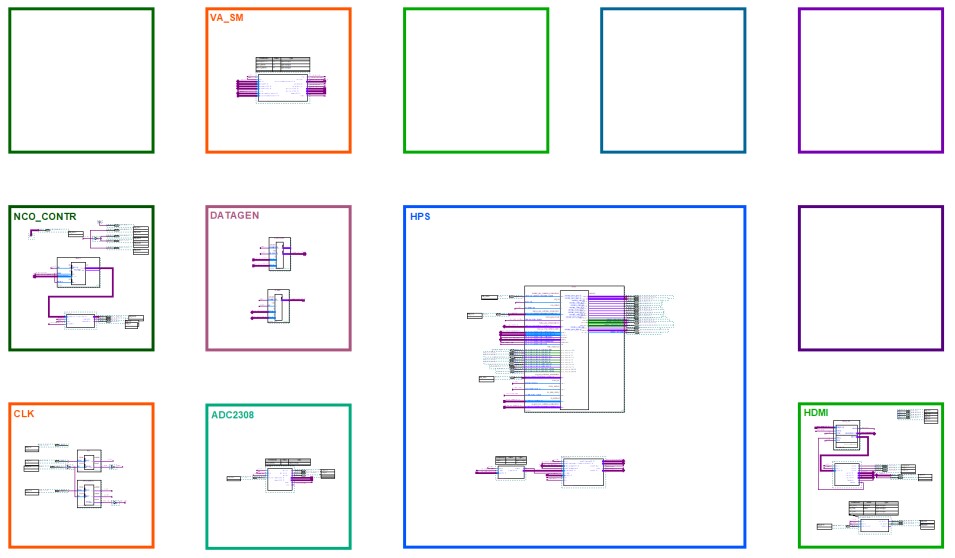

Поскольку теперь мы понимали, какие данные будут поступать на входы и выходы, мы начали работу над проектом для SoC FPGA. Реализуемый проект нам виделся следующим образом: пользователь задаёт частотный диапазон, в котором планируется проведение измерения, ПЛИС начинает генерировать по очереди гармоники в указанном промежутке с помощью ЦАПа, АЦП принимает на вход квадратурную и фазовую составляющие, преобразуя их в значение амплитуды и фазы на текущей частоте, полученные значения отображаются в реальном времени на мониторе, подключённому к отладочной плате. Наработки по отображению информации на монитор уже до этого были, поэтому основная часть заключалась в корректной отрисовке данных в реальном времени и выдаче картинки на HDMI. Мы разгруппировались. Первая группа занялась задачами по программе для процессора, разбираться подробнее с необходимыми инициализациями, вопросами по визуализации данных. Также мы попросили их поднять разрешение экрана до 1024х768 [6]. За второй группой остались детали по реализации части на FPGA, которые затем должны быть подведены в процессор через шину интерфейса lightweight_h2f, а также проверка работоспособности первого прототипа синхронного детектора. После устранения недочетов и удачного измерения характеристик нескольких элементов оставалось немного времени, поэтому следующие два дня были посвящены соединению систем вместе, дописыванию отчетности и монтированию видео.

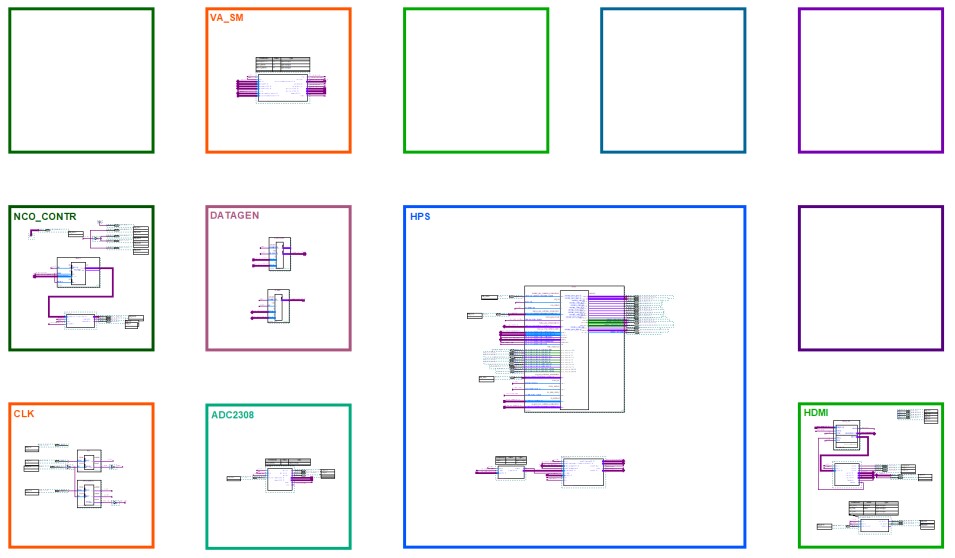

Внешний вид файла верхнего уровня в программе Quartus II

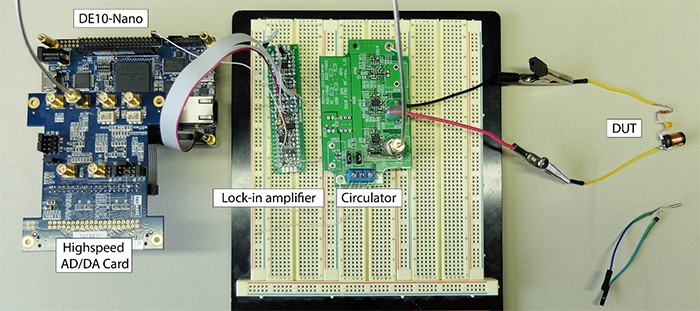

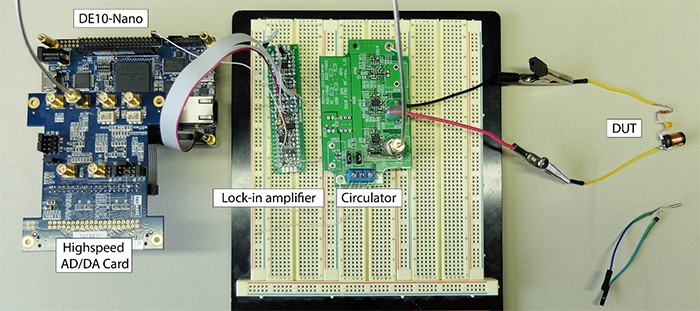

Проведя не одну пару выходных в лаборатории, мы собрали всю систему. Она работала не на весь потенциальный частотный диапазон, измеряла только параметр S11 и на мониторе отражала измеряемые фазовую и амплитудную характеристики подключаемого устройства. Внешне собранное устройство ещё пока выглядело не слишком привлекательно – три отдельных платы соединяемых между собой одножильными проводками, однако это рабочий прототип, а уж навести марафет можно в следующем этапе. Мы написали текст, проиллюстрировали этапы реализации, сняли видео, все загрузили на сайт и стали ждать.

Конечно же мы разослали некоторым знакомым ссылки на эти материалы чтобы слегка добавить просмотров. Однако в один день просмотры начали сами расти, будто кто-то слил это на раскрутку. Проведя небольшой анализ выяснилось: наш проект заметили на hackaday.io [7] и подавляющая часть просмотров была именно оттуда. Было интересно увидеть первые отклики на наш проект. Воодушевившись, мы стали ждать результаты.

Это не первый год нашего участия в конкурсе. Данный проект был для нас самым продуманным среди ранее реализованных нами студенческих работ. Но не срослось: мы не прошли в следующую стадию. Быть может это из-за непонимания между нами и судьями. Быть может просто проект не входит в область текущих трендов для FPGA в полной мере (криптография, параллельные вычисления, нейронные сети и пр.). Но для нас это большой шаг в разработке на SoC FPGA, новая ветвь развития и, главное, опыт.

Поздравляем российских представителей, занявших второе место в финале конкурса!

Благодарю своих коллег по проекту Данилу Никифоровского и Евгения Вострикова и руководителей Ивана Дейнеку, Филиппа Шуклина и Артема Алейника за активное участие и поддержку.

[1] Innovate Europe 2015 Contest www.innovateeurope.org/eu/2015winner.html

[2] An Engineer’s Guide To Automated Testing Of High-Speed Interface, Jose Moreira, Hubert Wekmann, 2010, приложение F стр. 503

[3] Спектр периодической последовательности прямоугольных импульсов, ru.dsplib.org/content/fourier_series_pimp/fourier_series_pimp.html

[4] Principles of lock-in detection and the state of the art, Zurich Instruments www.zhinst.com/applications/principles-of-lock-in-detection

[5] Низкочастотный циркулятор/изолятор без феррита и магнита www.cqham.ru/oth9.htm

[6] проект ВАЦ для платы DE10-Nano github.com/tvShushtov/em078_vector_analyzer

[7] Статья про ВАЦ на Hackaday hackaday.com/2018/05/09/vector-network-analyzer-uses-soc-fpga

Вступление

Шел октябрь 2017 года, я делал еженедельную рутинную проверку: анализ проходящих конференций по темам, которые реализуются на нашей кафедре. В один момент мне приходит рассылка от Terasic: стартует новый конкурс по разработке проектов с использованием отладочных плат на FPGA, теперь всемирный. В голове проносится и вспоминается опыт этого же конкурса прошлого года: откладывание до последних двух недель месяца, долгая отладка и настройка алгоритмов и выдачи всех каналов на монитор и обещание больше не откладывать это на последний день.

Это был крутой опыт, в ходе которого мы узнали много нового о такой платформе как SoC FPGA – единение между собой огромного массива логических элементов и процессора Cortex-A9, а так же их взаимодействие между собой и с периферией на отладочной плате.

Новый конкурс – новые правила, новые требования, новый уровень. Теперь конкурс проводится в несколько этапов: сначала проводятся региональные этапы, а затем финал в Сан-Хосе; плату всем участникам высылают одинаковую, DE10-Nano, а в дополнение теперь можно выбрать не только базовые три модуля, но и большой вариант плат от Analog Devices! Однако, в отличие от конкурсов в предыдущие годы в этот раз необходимо подписать гарантию выполнения проекта, а в случае невыполнения – участники должны отправить платы обратно. Вполне справедливо с учетом статистики прошлых лет:

<…>71 teams from 20 European countries registered the contest <…> 25 judges from Industry (ALTERA) and Academia (CNFM) in France reviewed the 32 projects [1].Научный руководитель как и ребята-студенты, которых хотелось привлечь в эту работу, были и без того под большой нагрузкой по различным проектам, но сам азарт в ходе конкурса и мотивация узнать много нового стали весомыми аргументами вновь поучаствовать в конкурсе. Оставалось придумать проект, с которым можно заявляться.

Идея для проекта

Чтобы проект не остался в стороне, решено было реализовать полезное для кафедры устройство, которое потом можно будет несложно дорабатывать и улучшать. Исходя из областей деятельности кафедры были различные варианты: оптический рефлектометр, стробоскопический осциллограф и др. Быстро просмотрев уже существующие заявки и доступные дополнительные платы выявлено, что рефлектометр уже заявили, а стробоскопический осциллограф на таких элементах не собрать. Единственная идея осталась живучей – векторный анализатор цепей. На днях в лабораторию принесли пару связных катушек, на которые отсутствовала какая-либо документация. Задачей было определить хотя бы приблизительные характеристики этих катушек. Известно было, что в них собран колебательный контур, поэтому главной задачей было выяснить резонансную частоту. В подобных задачах как раз и может найти применение векторный анализатор цепей (ВАЦ или VNA – Vector Network Analyzer). VNA позволяет определить матрицу рассеивания, известную также как матрица S-параметров. В таком методе исследуемый элемент рассматривается как черный ящик, у которого проводят анализ падающих и отраженных сигналов от портов этого устройства. Так, для двухпортовой системы матрица выглядит следующим образом:

Где V1+ V2+ – электромагнитные волны, поступающие на порты;

V1- V2- –электромагнитные волны, выходящие из портов;

Sij – элементы матрицы рассеяния многополюсника. [2]

Схема измерения S-параметров многополюсника

Рентгеном рассмотреть компоненты и схему не удалось (по крайне мере рентгеном метрополитена), поэтому на коленках было собрана следующая схема: через циркулятор на вход катушки с использованием генератора поочередно подавались частоты с выставленным шагом, второй порт циркулятора подключался на вход катушки, а третий вход – на осциллограф, имеющий в своем ПО режим амплитудно-частотного анализа. Такая схема позволяет измерить параметр S11, т.е. отражение. В конечном итоге после долгих мучений и калибровок снять данную характеристику удалось – но какой ценой? На кафедре давно ожидалось приобретение векторного анализатора цепей для подобных задач (измерения АФЧХ радиоэлектронных устройств), но эта закупка всегда каким-то образом откладывалась.

После возни с катушками было решено собрать свой собственный анализатор цепей с визуализацией и комфортной настройкой. Найти азарт и желание узнать что-то новое для себя у студентов и аспирантов, работающих на кафедре, несложно, поэтому команда была быстро собрана из электронщика, программиста-разработчика систем на кристалле, меня и двух наставников.

Сказано – сделано! После многочисленных обсуждений о полосе частот, алгоритмах обработки и других параметрах проекта заявка содержала следующее:

- Заявляемый проект – Векторный анализатор цепей на базе SoC FPGA на плате DE10-Nano;

- Запрашиваемые дополнительные платы: плата с программируемым генератором частот, высокочастотный миксер и плата с АЦП;

- Рабочий диапазон частот: согласно представленным параметрам дополнительных плат;

- Возможности быстрого расширения количества подключаемых портов;

- Вывод амплитудной и фазовой составляющей на экран;

- Другие базовые функции ввода/вывода для векторного анализатора цепей.

Для прохождения в следующий этап необходимо было чтобы страница проекта набрала достаточное количество «лайков» от зарегистрировавшихся на сайте пользователей. Первое время всё шло неплохо, однако затем некоторые сомнительные проекты начали набирать нереалистичные и контрастные по сравнению с остальными проектами значения лайков и просмотров. Оказалось, сайт конкурса был слишком уязвим к накрутке.

Через некоторое время организаторы оповестили, что финалистов все равно будет выбирать коллегия судей, поэтому лайки от пользователей, по сути, потеряли свой вес. 31 января в списках прошедших в следующий этап появилась и наша команда и мы начали детальнее продумывать наш проект в ожидании отладок.

Суровая реальность

Первой пришла плата DE10-Nano. Приятно, но немного странно: ожидали, что платы придут все вместе. Спустя несколько дней поступает звонок с таможни: пришли платы, они все вместе превышают порог по цене, поэтому необходимо заплатить за растаможку сумму примерно равную стоимости этих плат. Такой расклад нас огорчил, но не устроил: от плат мы отказались. В наличии миксеров и генераторов у нас не было, необходимо найти новые решения. Что же делать? Первым в голову пришло не самое точное, но довольно необычное решение: использовать обычную ножку GPIO и с неё генерировать меандр. На выходе этой ножки устанавливается аналоговый ФНЧ с полосой среза чуть больше максимальной частоты меандра. Включать анализ для начала предлагалось с 1МГц (к примеру): тогда после фильтра мы получили бы более-менее чистый синус (старшие гармоники отрезались бы фильтром), и так далее до тех пор пока частота не опустится до той, на которой в сигнале после фильтра будет две гармоники. Меандр – это сумма нечетных гармоник, причем пропорциональный вклад каждой гармоники заранее известен [3].

Пример меандра во временной и частотной областях: на спектре видны составляющие сигнал гармоники на 500кГц, 1.5МГц и др.

С фильтром с частотой среза 1 МГц можно спускаться до 33.(3) кГц. После этой частоты за фильтром мы должны получить сумму двух синусов. Пропорциональное соотношение их амплитуд известно (sinc-функция), отклик измеряемого устройства на частоту 1 МГц (первая нечетная гармоника) тоже, значит нам остается составить уравнение с одной неизвестной и вычислить характеристику отклика на частоту 33,(3) кГц! Сначала это решение показалось слишком простым, поэтому для начала оно рассказано было всем в надежде что кто-нибудь найдет ошибку. Ошибки не нашлось, но по мере обсуждения был обнаружен ряд ограничений:

- Ножка GPIO – не самый лучший источник меандра особенно с ростом частоты;

- Спаять компактный фильтр на доступных компонентах будет нетривиальной задачей;

- Даже если эти ограничения можно будет обойти – возникает проблема синхронизации для детектирования фазы.

Допустим мы все проблемы по аналоговой части решили; программно возникают две других:

- С понижением частоты погрешность каждого предыдущего детектирования и вычисления будет вносить свой вклад в последующее измерение;

- С понижением частоты время на вычисление характеристик будет значительно расти.

И, наконец, последнее по порядку, но не по значению. Описанная схема может использоваться если измеряемый элемент можно описать линейной передаточной функцией. Однако если мы будем измерять черную коробку с нелинейными характеристиками – от идеи больше проблем, чем пользы. Времени оставалось немного (Первый результат надо показать уже через два месяца после прихода платы), поэтому после непродолжительных размышлений мы решили перепроверить наши запасы по уже имеющимся отладочным платам – и нашли 14-битный ЦАП на 125 Msps! Не самое элегантное решение, но выбирать не приходится, используем его в качестве генератора выходного сигнала.

Первый концепт

Выбранный ЦАП в качестве генератора принимает на вход параллельной шины данные и защелкивает его тактовым сигналом, идущим с ПЛИС. Такая схема идеальна для синхронизации в нашей схеме. Однако с детектированием оставались вопросы.

Да, на этой же плате есть 14-битный АЦП на 65 Msps. Но вот только возможности генератора потенциально выше, а по теореме Котельникова данный АЦП уже не подойдет на максимальных частотах.

Решение было найдено в ходе обсуждения этой задачи с опытными электронщиками. Оказалось, что для нашей задачи мы можем воспользоваться схемой синхронного детектора (lock-in amplifier): выходом такого детектора являются две постоянных величины, фазовая и квадратурная составляющие, из которых можно получить амплитуду и фазу сигнала, а так как они постоянны, их можно детектировать даже с помощью медленной АЦП, установленной на DE10-Nano! Решено было сначала отмоделировать схему в LTSpice, а уже потом подбирать компоненты и собирать схему, с учетом того, что входом детектора является сигнал с циркулятора, а выходы подключаются к АЦП на плате DE10-Nano.

О синхронном детекторе и циркуляторе

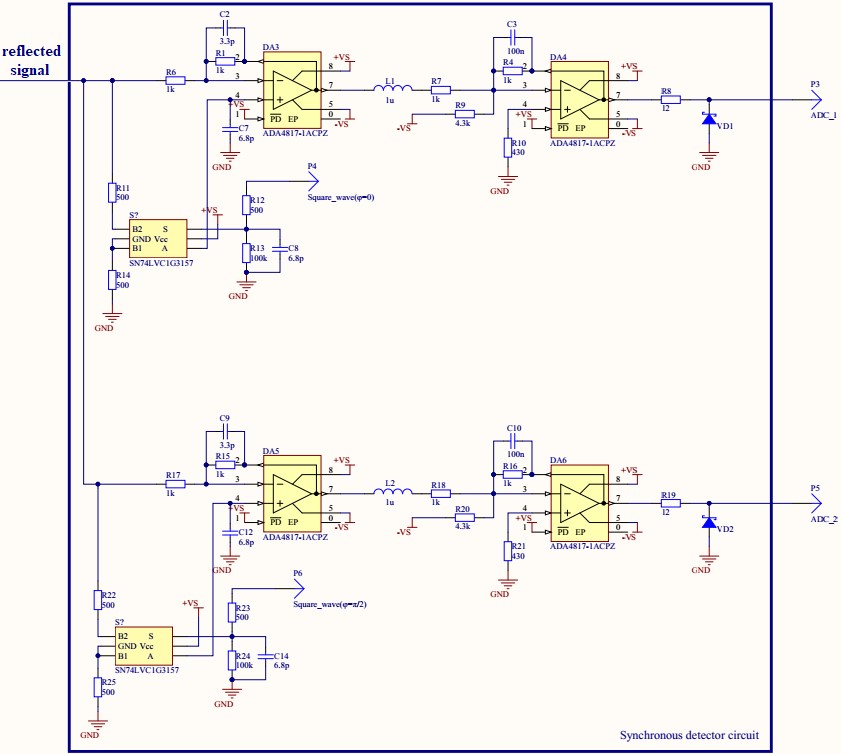

Синхронный детектор применяется и в цифровой обработке сигналов для детектирования различных сигналов на фоне шумов. Хорошее описание есть у Zurich Instruments [4], в нашем случае детектирование производится следующим образом: отраженный сигнал известной частоты умножается на меандр с использованием высокочастотного переключателя и операционного усилителя:

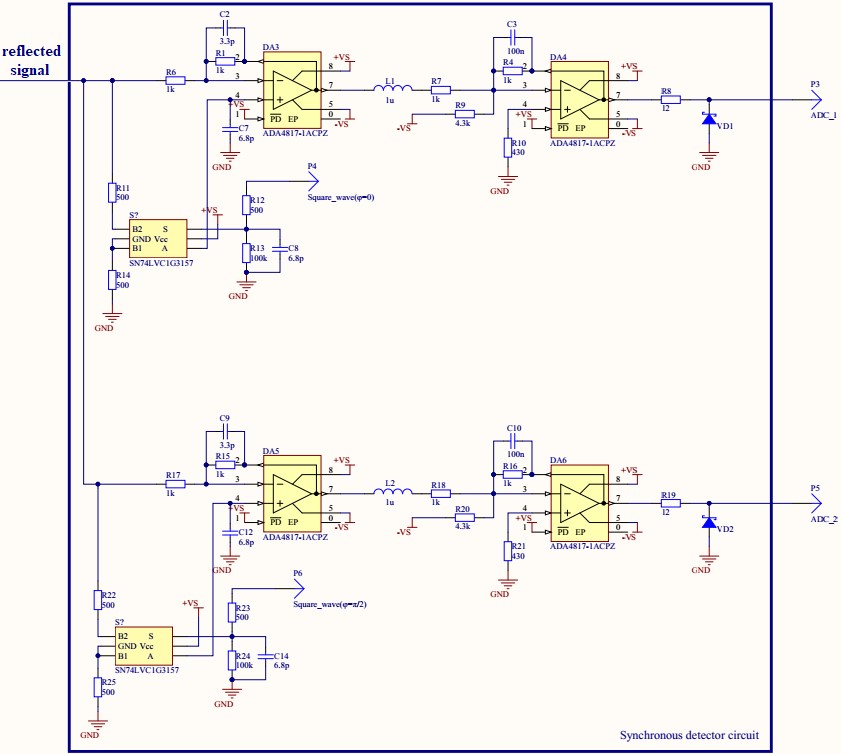

Схема детектирования отраженного сигнала

На деле умножение реализовано как переключение режима работы операционного усилителя, а переключение управляется двумя меандрами, поступающих с платы DE10-Nano: один из них в фазе с исходным сигналом (поступающим на вход устройства), а другой с задержкой по фазе на 90 градусов.

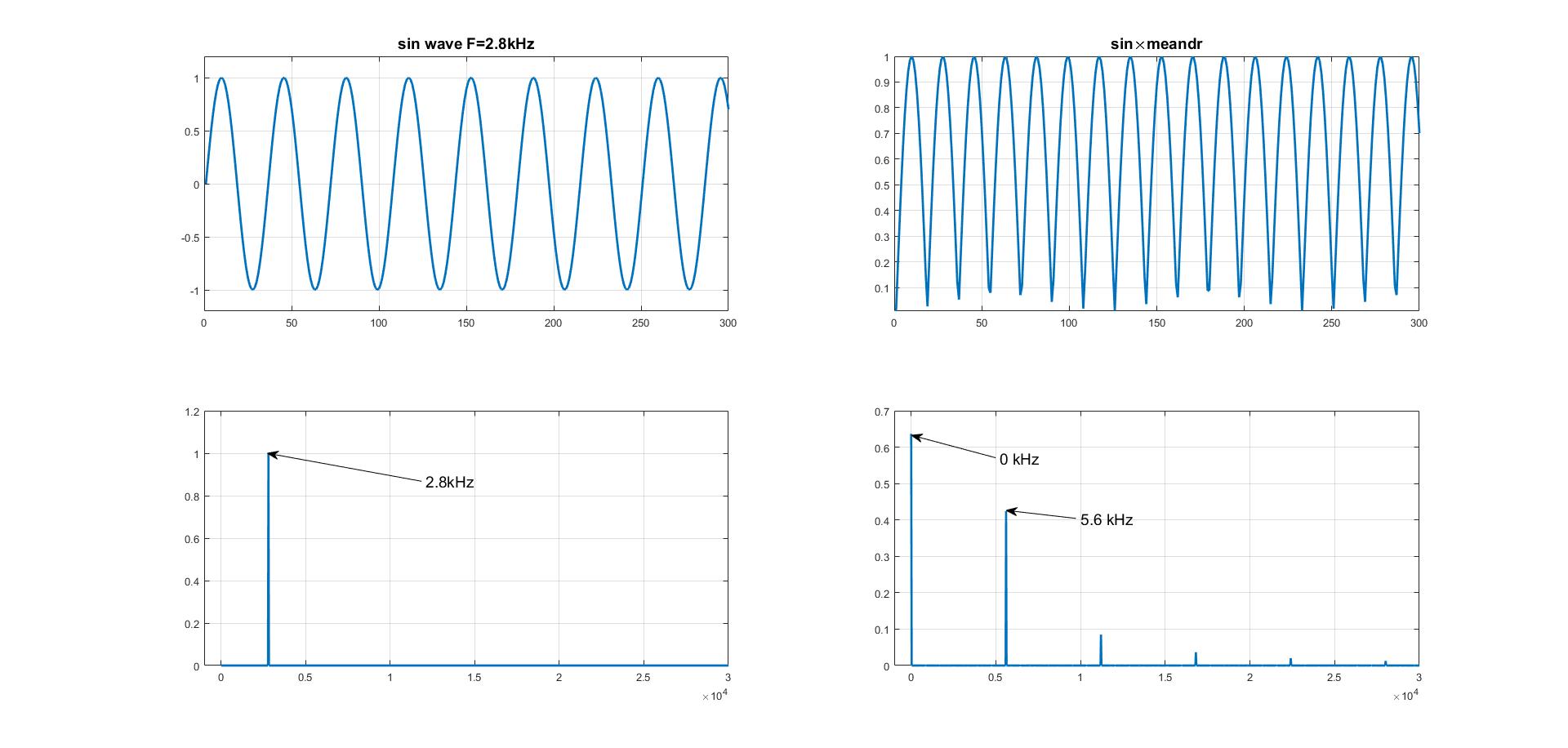

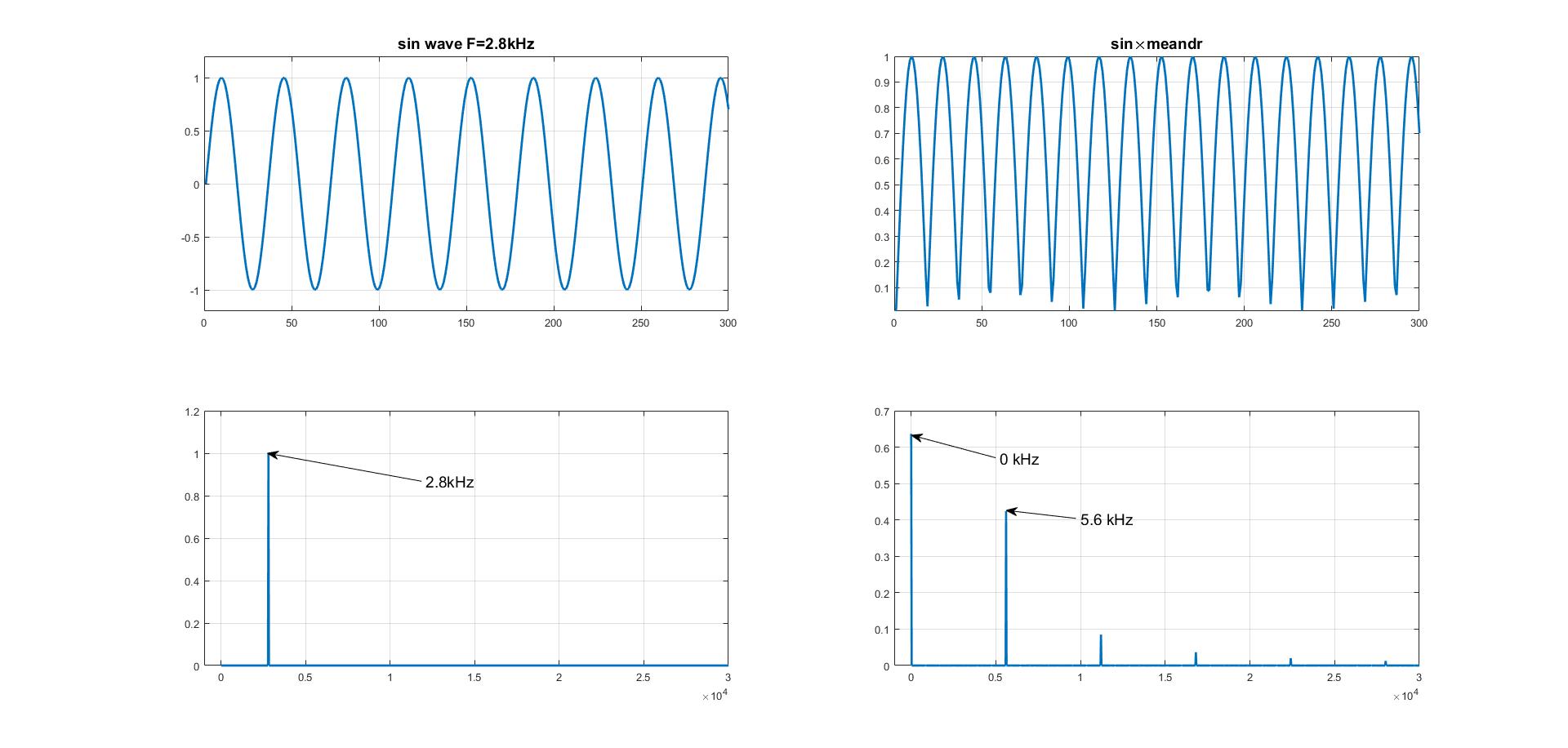

Результатом умножения становится перенос полезного сигнала в постоянную составляющую, а все частоты выше уже не интересны и поэтому могут быть отфильтрованы:

Спектр сигнала до и после умножения: на выходе операционного усилителя можно собрать простой ФНЧ для выделения только постоянной составляющей

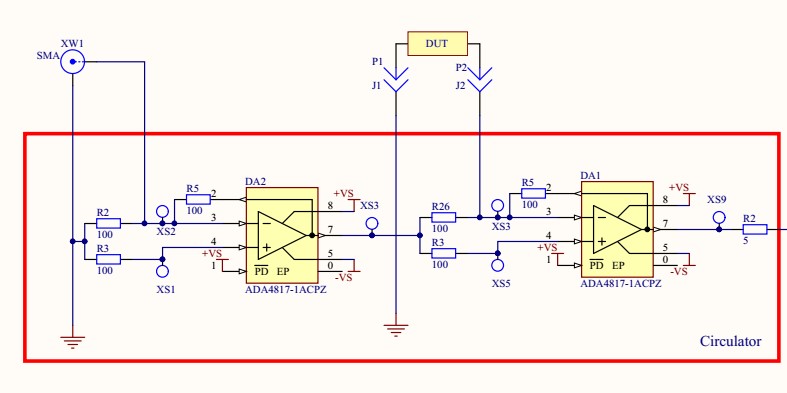

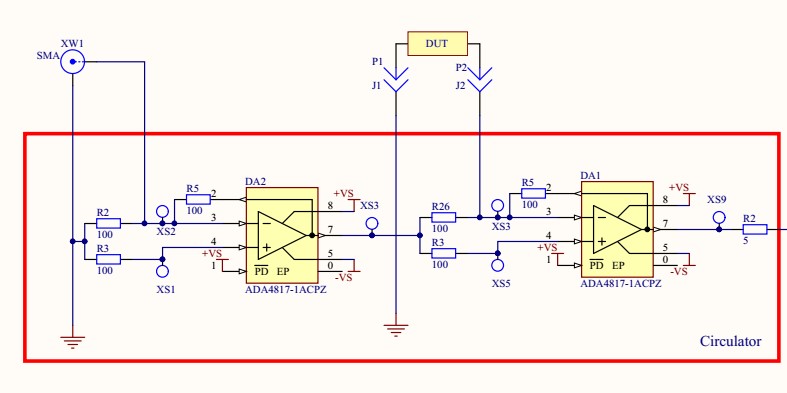

Циркулятор на операционных усилителях (ОУ) представляет собой схему последовательного соединения операционных усилителей, замкнутых в кольцо. Циркуляторы на ОУ применяются для многих целей, в частности, для настройки антенн, усилителей, генераторов, гигабитный Ethernet и т.п. в диапазоне частот до сотен мегагерц. При создании ВАЦ использовалась схема циркулятора, созданная на основе двух операционных усилителей [5].

Схема циркулятора для подключения измеряемого устройства

Схема детектирования отраженного сигнала

На деле умножение реализовано как переключение режима работы операционного усилителя, а переключение управляется двумя меандрами, поступающих с платы DE10-Nano: один из них в фазе с исходным сигналом (поступающим на вход устройства), а другой с задержкой по фазе на 90 градусов.

Результатом умножения становится перенос полезного сигнала в постоянную составляющую, а все частоты выше уже не интересны и поэтому могут быть отфильтрованы:

Спектр сигнала до и после умножения: на выходе операционного усилителя можно собрать простой ФНЧ для выделения только постоянной составляющей

Циркулятор на операционных усилителях (ОУ) представляет собой схему последовательного соединения операционных усилителей, замкнутых в кольцо. Циркуляторы на ОУ применяются для многих целей, в частности, для настройки антенн, усилителей, генераторов, гигабитный Ethernet и т.п. в диапазоне частот до сотен мегагерц. При создании ВАЦ использовалась схема циркулятора, созданная на основе двух операционных усилителей [5].

Схема циркулятора для подключения измеряемого устройства

Обновленная концепция проекта

Синусоидальные сигналы с частотой от 1 Гц до 1 МГц с выставленным шагов в несколько Гц поступали на первый порт циркулятора. Ко второму порту подключалось исследуемое устройство, в зависимости от частотной характеристики которого происходило изменение коэффициента отражения сигнала. Отраженный сигнал поступал на 3 порт, где для определения частотной и фазовой характеристик была собрана схема синхронного детектора. Для корректной работы было осуществлено согласование портов циркулятора под импеданс 100 Ом, что было связано с выходным сопротивлением ЦАП и выбором исследуемых устройств.

До сдачи проекта оставалось меньше месяца, а к концу срока необходимо было ещё и подготовить отчетные материалы: подробное описание проекта на странице конкурса, проект, выложенный на GitHub в открытом доступе и видеоотчет о проделанной работе.

Поскольку теперь мы понимали, какие данные будут поступать на входы и выходы, мы начали работу над проектом для SoC FPGA. Реализуемый проект нам виделся следующим образом: пользователь задаёт частотный диапазон, в котором планируется проведение измерения, ПЛИС начинает генерировать по очереди гармоники в указанном промежутке с помощью ЦАПа, АЦП принимает на вход квадратурную и фазовую составляющие, преобразуя их в значение амплитуды и фазы на текущей частоте, полученные значения отображаются в реальном времени на мониторе, подключённому к отладочной плате. Наработки по отображению информации на монитор уже до этого были, поэтому основная часть заключалась в корректной отрисовке данных в реальном времени и выдаче картинки на HDMI. Мы разгруппировались. Первая группа занялась задачами по программе для процессора, разбираться подробнее с необходимыми инициализациями, вопросами по визуализации данных. Также мы попросили их поднять разрешение экрана до 1024х768 [6]. За второй группой остались детали по реализации части на FPGA, которые затем должны быть подведены в процессор через шину интерфейса lightweight_h2f, а также проверка работоспособности первого прототипа синхронного детектора. После устранения недочетов и удачного измерения характеристик нескольких элементов оставалось немного времени, поэтому следующие два дня были посвящены соединению систем вместе, дописыванию отчетности и монтированию видео.

Внешний вид файла верхнего уровня в программе Quartus II

Последние минуты

Проведя не одну пару выходных в лаборатории, мы собрали всю систему. Она работала не на весь потенциальный частотный диапазон, измеряла только параметр S11 и на мониторе отражала измеряемые фазовую и амплитудную характеристики подключаемого устройства. Внешне собранное устройство ещё пока выглядело не слишком привлекательно – три отдельных платы соединяемых между собой одножильными проводками, однако это рабочий прототип, а уж навести марафет можно в следующем этапе. Мы написали текст, проиллюстрировали этапы реализации, сняли видео, все загрузили на сайт и стали ждать.

Конечно же мы разослали некоторым знакомым ссылки на эти материалы чтобы слегка добавить просмотров. Однако в один день просмотры начали сами расти, будто кто-то слил это на раскрутку. Проведя небольшой анализ выяснилось: наш проект заметили на hackaday.io [7] и подавляющая часть просмотров была именно оттуда. Было интересно увидеть первые отклики на наш проект. Воодушевившись, мы стали ждать результаты.

Однако

Это не первый год нашего участия в конкурсе. Данный проект был для нас самым продуманным среди ранее реализованных нами студенческих работ. Но не срослось: мы не прошли в следующую стадию. Быть может это из-за непонимания между нами и судьями. Быть может просто проект не входит в область текущих трендов для FPGA в полной мере (криптография, параллельные вычисления, нейронные сети и пр.). Но для нас это большой шаг в разработке на SoC FPGA, новая ветвь развития и, главное, опыт.

P.s.

Поздравляем российских представителей, занявших второе место в финале конкурса!

Благодарю своих коллег по проекту Данилу Никифоровского и Евгения Вострикова и руководителей Ивана Дейнеку, Филиппа Шуклина и Артема Алейника за активное участие и поддержку.

Ссылки

[1] Innovate Europe 2015 Contest www.innovateeurope.org/eu/2015winner.html

[2] An Engineer’s Guide To Automated Testing Of High-Speed Interface, Jose Moreira, Hubert Wekmann, 2010, приложение F стр. 503

[3] Спектр периодической последовательности прямоугольных импульсов, ru.dsplib.org/content/fourier_series_pimp/fourier_series_pimp.html

[4] Principles of lock-in detection and the state of the art, Zurich Instruments www.zhinst.com/applications/principles-of-lock-in-detection

[5] Низкочастотный циркулятор/изолятор без феррита и магнита www.cqham.ru/oth9.htm

[6] проект ВАЦ для платы DE10-Nano github.com/tvShushtov/em078_vector_analyzer

[7] Статья про ВАЦ на Hackaday hackaday.com/2018/05/09/vector-network-analyzer-uses-soc-fpga

Комментарии (3)

McSava

06.10.2018 10:33Для победы недостаточно просто сделать интересный проект — его ещё нужно грамотно и красиво представить. Обратите внимание на написания величин и размерностей. Есть правило как их применять. Приставки к(ило) и М(ега). Размерности основанные на именах (фамилиях) начинаются с большой буквы поэтому Гц, кГц и т. д. SoCращения по тексту пляшут как хотят.

Не обидно, если в конкурсе выигрывает кто-то с более интересным, техничным или актуальным проектом. Но что если драгоценные были потеряны из-за оформления сопроводительной записки?

GREGOR_812

Молодцы!