Примечание. Радиус атома кремния составляет 110 пикометров или 0,11 нанометра. Термин «размер узла» в процессе фотолитографии с пометкой «14 нм», «10 нм», «7 нм», «5 нм», «3 нм» и «2 нм» является маркетинговым и не имеет отношения к геометрии транзисторов.

Один из лидеров полупроводниковой индустрии TSMC, похоже, не собирается хоронить закон Мура. Тайваньская компания сейчас ведёт массовое производство по технологическому процессу 7 нм (огромное количество заказов на процессоры Ryzen 3000 и графические карты Navi). Она вот-вот готова запустить 5 нм, а теперь объявила о начале исследований в области процесса с нормой 2 нм. Об этом сказано в годовом отчёте для акционеров, сообщает Digitimes.

В данный момент TSMC параллельно с Samsung налаживает производство технологического конвейера на 5 нм с использованием фотолитографии в глубоком ультрафиолете (EUV). Интересно, что единственным в мире производителем степперов для фотолитографии в глубоком ультрафиолете является голландская компания ASML. Это исключительно сложные машины весом 180 тонн и стоимостью порядка $170 млн каждая, компоненты для которых производят около 5000 поставщиков со всего мира.

Пока неизвестно, какие конкретные технологии TSMC собирается применить для нового технологического процесса, да и разработки пока в ранней стадии, так что пока рано говорить не то что о сроках запуска в производство, но даже об успехе этих разработок в принципе.

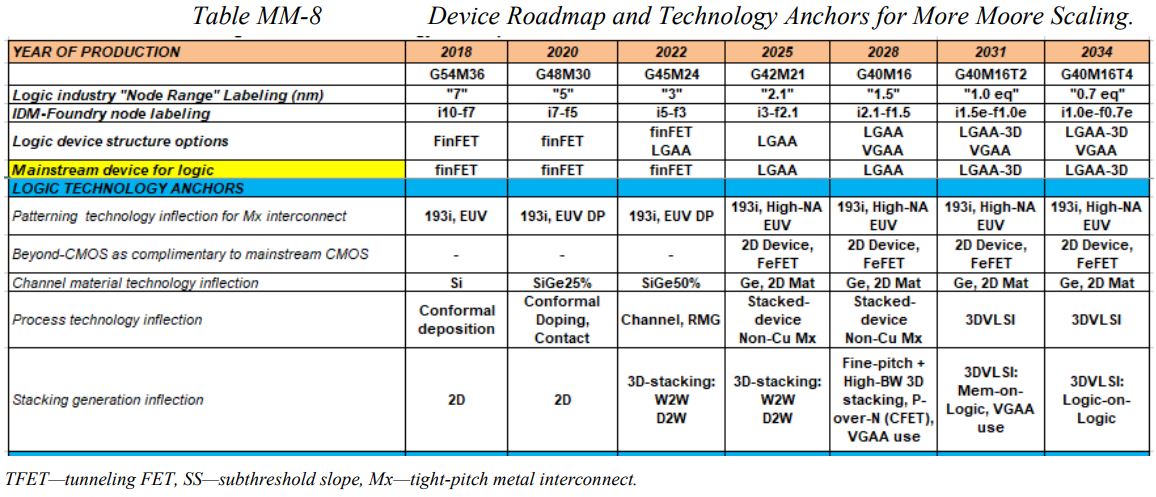

Однако TSMC придерживается своих долгосрочных планов, которые объявила ещё в 2018 году по девизом More Moore, что относится к продолжению масштабирования количества транзисторов на микросхемах в соответствии с законом Мура. Вот как TSMC очертила примерное развитие технологий до 2034 года:

Согласно этой «дорожной карте», транзисторы с размером узла 3 нм будут изготавливаться по архитектуре GAAFET и FinFET.

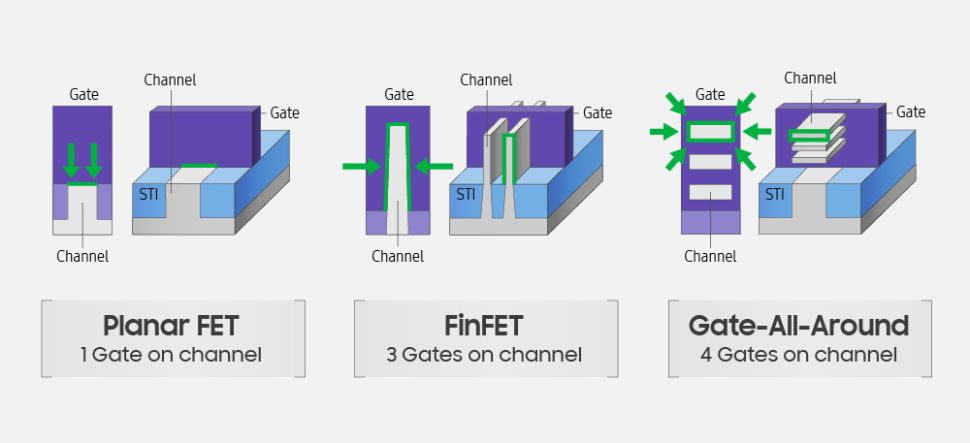

FinFET — трёхмерная архитектура, по которой сейчас изготавливаются транзисторы 7 нм и 5 нм. Возможно, её удастся применять и для 3 нм.

На смену FinFET должна прийти архитектура GAAFET (gate-all-around FET), её с 2000 года разрабатывает организация, в которую входят также IBM, Globalfoundries и Samsung. По информации источников, TSMC взвешивает разные варианты для 3 нм, включая нанослои, нанопровода и форсированные FinFET.

Как видно из названия, главной особенностью архитектуры GAAFET (gate-all-around FET) являются кольцевые затворы. Каналы транзисторов представляют собой нанопровода, сформированные из нескольких горизонтальных кремниевых «нанолистов», в то время как у FinFET канал транзистора представляет собой монолитную вертикальную конструкцию, что накладывает ограничения по масштабированию.

Внутренняя структура транзистора GAAFET 5 нм. Фото: IBM

В январе 2020 года южнокорейская компания Samsung сообщала о первых успехах в разработке транзисторов GAAFET по техпроцессу 3 нм. Вероятно, TSMC движется в том же направлении.

Иллюстрация: Samsung

Аббревиатура LGAA в плане TSMC относится к «горизонтальным» (lateral) GAAFET в 2D-процессоре, а «вертикальные» (VGAAFET) будут использоваться в неких 3D-структурах, о которых ещё ничего не известно.

Любопытно, что TSMC планирует ещё десятилетиями использовать 193-нм литографию, параллельно с фотолитографией в глубоком ультрафиолете.

В плане упоминается также технология high-NA EUV. Здесь NA означает произвольно количество измерений, то есть диапазон углов, под которыми система может принимать или излучать свет. То есть это нечто вроде «многомерной» фотолитографии как альтернатива многослойным конструкциям.

С запуском производство по техпроцессу 5 нм в 2020 году есть вероятность, что и дальше всё пойдёт по этому плану, так что можно ожидать 3 нм к 2022 году и 2 нм к 2024-2025 годам.

Firz

Когда довольно давно первый раз узнал про это, первая мысль была «Так вот где теперь работают те, кто создавал советский ГОСТ на провода».

То есть если на кабеле написано 2.5мм2 это не значит что это его физическое сечение, реальное сечение меньше.(актуально для России и тех кто в этом союзе)

Alert1234

Только недавно выбирал провод и смотрел на сечение. Думал ну как же так, даже тут экономят и подделывают.

Firz

Если по ГОСТ, то «2.5мм?» на самом деле около 2.3мм?, «1.5мм?» около 1.35мм?, а вот если только ТУ, без ГОСТ, то можно только надеяться что же там на самом деле.

Кстати говоря, импортность кабеля тоже не залог правдивости его сечения, не так давно попался китайский провод от какого-то бытового прибора, 0.75мм? и рядом был немецкий 0.5мм?, чисто визуально, у немецкого 0.5мм? сечение в два раза больше китайского 0.75мм?. На китайские 0.75мм? с легкостью оделся НШВИ 0.34мм?, а на немецкие 0.5мм? плотно оделся НШВИ 0.5мм?.

prototip_iv

Ладно если просто сечение, попадались медные провода с содержанием меди не более 40%.

Am0ralist

Вспоминаю сетевой омедненный кабель, который тянули абонентам, а потом через год массово меняли)

Gryphon88

А что такое, если не секрет? Я по загородному дому растаскивал такой, самая длинная трасса около 100м. Пока вроде всё ок. Единственное, что в нём плохого помню — ломкий офигенно.

Am0ralist

Просто через годок где-то как будто-сгнил (ибо его ж использовали и между подъездами в том числе, да и внутри подъездов климат в старых домах… отличный). Тут ещё вариант, что качество сильно может плавать от производителей и когда закупается самый дешевый, то ждать от него хорошего не стоит)

innovaIT

Firz

https://www.etm.ru/cat/nn/7231711/

Есть и еще меньше, 0.25мм?

Firz

Поправочка, есть даже 0.14мм?, но это уже и правда какая-то экзотика.

Длина металлической части может быть так же разной:

Snakey

Этот гост — прекрасная и логичная вещь, и очень слабо похожа на нанометры транзисторов.

Потому что когда ПБ считает мощность на например микрорайон, и потом из этой мощности считаем количество и марку кабелей — мне абсолютно наплевать, каково реальное сечение провода в каждом его конкретном месте. Мне важно именно сопротивление. Так что в этом конкретном случае это мудрость веков:)

xztau

Не понял. А как же максимальный ток по ПУЭ?

lolhunter

Сопротивление провода определяет ток, при котором провод начнет нагреваться. Сечение провода не говорит нам каково его сопротивление. Он может быть из меди, алюминия, сплава или золота. Сечение одно, а сопротивление как бы нет.

Firz

Сопротивление провода определяет количество выделяемого в нем тепла при определенном токе, а физические характеристики жилы и изоляции, а так же среды, в которой сам кабель находится, определяют как он может отводить это тепло и какой будет в итоге длительно допустимый ток.

xztau

Сопротивление как бы от длины так же зависит.

УПД

И ведь у нас не сверхпроводники в ИТЭРе. У нас чёткие медь и алюминий.

Am0ralist

innovaIT

Я конечно не уверен, но кажется не только сопротивление будет играть роль. При подаче большого тока сопротивление же может возрастать от температуры? И тут как раз сечение сыграет роль. Т. Е. Есть ГОСТ с номинальный сечением и током который должен пролазить через этот провод с соответствующим температурным диапазоном.

Snakey

Ну вообще все параметры берутся по марке, если уж так:)

Это я к тому, что сечение в расчетах вторично к сопротивлению, и проще стандартизировать именно его.

Firz

С бытовой точки зрения да, выглядит не совсем красиво. С другой стороны обычно в быту считают категориями «так, нужен утюг, кондиционер и три лампочки, ток такой-то, табличка в интернете говорит что нужен провод 2.5», человек идет в магазин и покупает 2.5, и фактически его тоже не волнует реальный размер провода, ему нужно что бы подходило и оно подходит:)

Так исторически сложилось, можно сказать.

Кабеля считаются по маркам. Там все параметры и париться не надо.

Firz

Вот в быту то как раз и пофигу на это, а вот «в промышленности/производстве», где и оборудование может быть импортное и кабеля, как раз не очень весело, потому что из-за этого теперь существует несколько разных видов наконечников, гильз, матриц для их опрессовки и прочего, потому что есть настоящие 120мм?(к примеру), со своими наконечниками, матрицами для опрессовки и прочим, а есть «ГОСТ 120мм?», со своими, потому что на самом деле они не 120мм?.

Am0ralist

Snakey

А в промышленности вы берете кабель по марке, и по этой же марке выбираете соединение. Потому что как минимум многожильное плетение может различаться у разных производителей, и как следствие — диаметр, и это не вспоминая изоляцию, и тем более не вспоминая сложные кабеля, где несколько слоев, несколько металлов, разное плетение, и все это в изоляции. Сечение в мм2 вам ничего не даст.

Поэтому что в быту, что в проме — никакой разницы, а стандартизировать по сопротивлению надежнее и проще.

Firz

Эти характеристики(диаметр в том числе) тоже нормированы в ГОСТе. Для этого он и нужен, чтобы взяв продукт, на котором написано «соответствует ГОСТу» была уверенность что все характеристики соответствуют.

В этом то весь и вопрос, зачем они стандартизировали так, чтобы физическое сечение было ниже номинального на ~10%.

Причем для некоторых сечений доходит до абсурда: по ГОСТу, если взять круглую алюминиевую жилу сечением 150мм?, она не будет соответствовать этому ГОСТу на номинальное сечение 150мм?(максимум можно 149.571мм?, иначе ограничение по максимальному диаметру жилы не пройдет).

p.s. Особые кабеля, да из нескольких металлов, вообще отдельный разговор, к ним этот ГОСТ даже не относится.

Firz

Для меня, к примеру, очень не логично официально разрешать провод 2.3мм? называть 2.5мм?. Ладно в AWG есть калибры, они не содержат физических величин в названиях, AWG 10, AWG 20 и так далее, а когда кабель называется «2.5мм?» и в характеристиках везде и всюду пишется «сечение 2.5мм?», а на самом деле он по факту 2.3мм?, это, извините,

официально одобренное наебаловополная фигня.А длительно допустимые токи как считать без физических размеров жилы и изоляции?

v1000

А вот реально, почему нельзя было сделать как в своё время называли частоту процессора у АМД — называть 2,5+, тогда, к примеру, медный 1,5мм и алюминиевый 2,3мм будут называться 2,5+. А физический размер указывать именно физический, по типу как AMD Athlon 3000+ 2.0 GHz

innovaIT

В госте есть понятие содержание меди. И тут мы подходим к примесям. Например медь+серебро, сечение будет меньшим, но ток будет протекать одинаково. ГОСТ регламентирует и состав и протекающие токи. Если провод меньшим сечением проводит одинаково, то какая разница? Кроме того, что на таком проводе наконечники меднолуженые не держатся ;)

Firz

А ткните пожалуйста ссылкой, везде где я видел пишут конкретно что должна использоваться отожженная медь и только иногда проскакивают исключения вида

«Токопроводящие жилы должны быть изготовлены из отожженной меди, кроме проволок мишурных токопроводящих жил, для которых может применяться сплав на основе меди.»

Меньше физическое сечение — меньше длительно допустимые токи, при одинаковой изоляции, т.к. хуже отвод тепла.

innovaIT

ВЗАМЕН ГОСТ 22483-77

И вот как раз в ГОСТ 22483-77 было все что нужно, а в новом исчезло. Прошу прощения что ввел в заблужение.

«ТУ 16.К71-003-87» уже не действует. На катанку нашел действующий стандарт ГОСТ Р 53803-2010 Катанка медная для электротехнических целей. Технические условия. Но какая разница, раз в госте теперь материал звучит как «Жилы должны состоять из одного из следующих материалов: — из отожженной меди с металлическим покрытием или без него;»

Ну вы же не спорите, что в медном кабеле сечение меньше, чем в алюминиевом, при одинаковых допустимых длительных токах?

Firz

Если взять медный кабель и алюминиевый с одинаковым сопротивлением, длительно допустимые токи будут выше у алюминиевого, так как из-за большего сечения он может лучше отводить тепло, я это имел в виду.

innovaIT

Опять же к изоляции есть пугв есть Пв3. Во втором изоляция тоньше, но напряжение пробоя одинаково. И работать со вторым легче.

ReklatsMasters

Если это всё маркетинг, то какой реальный физический размер транзисторов?

mamont80

Реальный размер отдельного транзистора больше не измеряют, т.к. он не сильно то уменьшается, у него тоже свои физические ограничения. В качестве единицы измерения используют группу транзисторов из 6 штук, делённую на занимаемую ими площадь. Подробнее есть статья на хабре.

vsb

Я не могу найти точную цифру, но речь идёт о десятках нанометров, в районе 30-40.

ArsenAbakarov

А когда я учился на физ. факе один препод говорил все время что невозможно сделать транзистор менее, кажется, 22нм, так как будет туннельный эффект…

Firz

Хорошее видео, где и этот вопрос поверхностно затрагивают www.youtube.com/watch?v=rtI5wRyHpTg

Andriy1218

Ну по сути так оно и есть. Длина канала уже давно остановилась на отметке в 20-25нм.