Основная прелесть использования ПЛИС, на мой взгляд, состоит в том, что разработка аппаратуры превращается в программирование со всеми его свойствами: написание и отладка кода как текста на специализированных языках описания аппаратуры (HDL); код распространяется в виде параметризованных модулей (IP-блоков), что позволяет его легко переиспользовать в других проектах; распределенная разработка обширным коллективом разработчиков с системой контроля версий, такой же, как у программистов (Git); и, как и в программировании, ничтожно низкая стоимость ошибки.

Последнее очень важно, так как если при разработке устройства классическим методом разработчик несет вполне существенные затраты на сборку и производство изделия, и любая схемотехническая ошибка или ошибка трассировки печатной платы — это всегда выход на очередную итерацию и попадание на деньги, то при работе с ПЛИС ошибки ничтожны по своей стоимости и легко устранимы. И даже если в серийном изделии обнаруживается ошибка, то её во многих случаях можно устранить очередным апгрейдом прошивки «в поле» без замены изделия. Короче, с приходом ПЛИС разработка цифровой аппаратуры все больше и больше выглядит как программирование, а это, помимо всего прочего, существенно понижает порог вхождения в тему, и все больше программистов становятся разработчиками «железа». А новые люди, в свою очередь, приносят с собой в индустрию новые подходы и принципы.

В этой статье я хочу поделиться своим небольшим опытом «программирования» микросхем ПЛИС и тем, как я постепенно погружался в тему ПЛИСоводства. Изначально я собирался написать небольшую заметку про открытый тулчейн для синтеза Yosys. Потом — про язык SpinalHDL и синтезируемое микропроцессорное ядро VexRiscv, на нём написанное. Потом — про замену микроконтроллеров микросхемами ПЛИС на примере моей отладочной платы «Карно». Но в процессе я погрузился в историю появления Hardware Description Languages (HDL), и когда я начал писать, Остапа, как это часто бывает, понесло... В общем, получилось то, что получилось.

А еще эту статью можно рассматривать как глубокое погружение в то, что происходит вот на этом новогоднем видео.

СОДЕРЖАНИЕ

2. Появления программируемых логических устройств

3. Производители микросхем ПЛИС

4. Синтез цифровых схем для ПЛИС

6. Как установить утилиты тулчейна Yosys

7. Пример использования открытого тулчейна Yosys

7.1. Установка и настройка «basics-graphics-music»

7.2 Лабораторная работа «01_and_or_not_xor_de_morgan»

7.3 Загрузка битстрима в микросхему ПЛИС

8. Типовой Makefile для синтеза с помощью Yosys

9. Файл описания внешних сигналов и ограничений (LPF, PCF, CST)

10. Особенности синтаксиса Yosys

10.2 Многомерные массивы сигналов

10.3 Функция возведения в степень ($POW) и оператор **

10.4 Функция не может иметь доступ к сигналу, описанному за её пределами

10.5 Сигналы нулевой или отрицательной размерности

10.6 Сложные битовые манипуляции иногда могут выдавать ошибку о loopback-ах

11. Анализируем сообщения от тулов

11.1 Сообщения от утилиты yosys

11.2 Сообщения от утилиты nextpnr

12.1 Синтезируемое вычислительное ядро VexRiscv

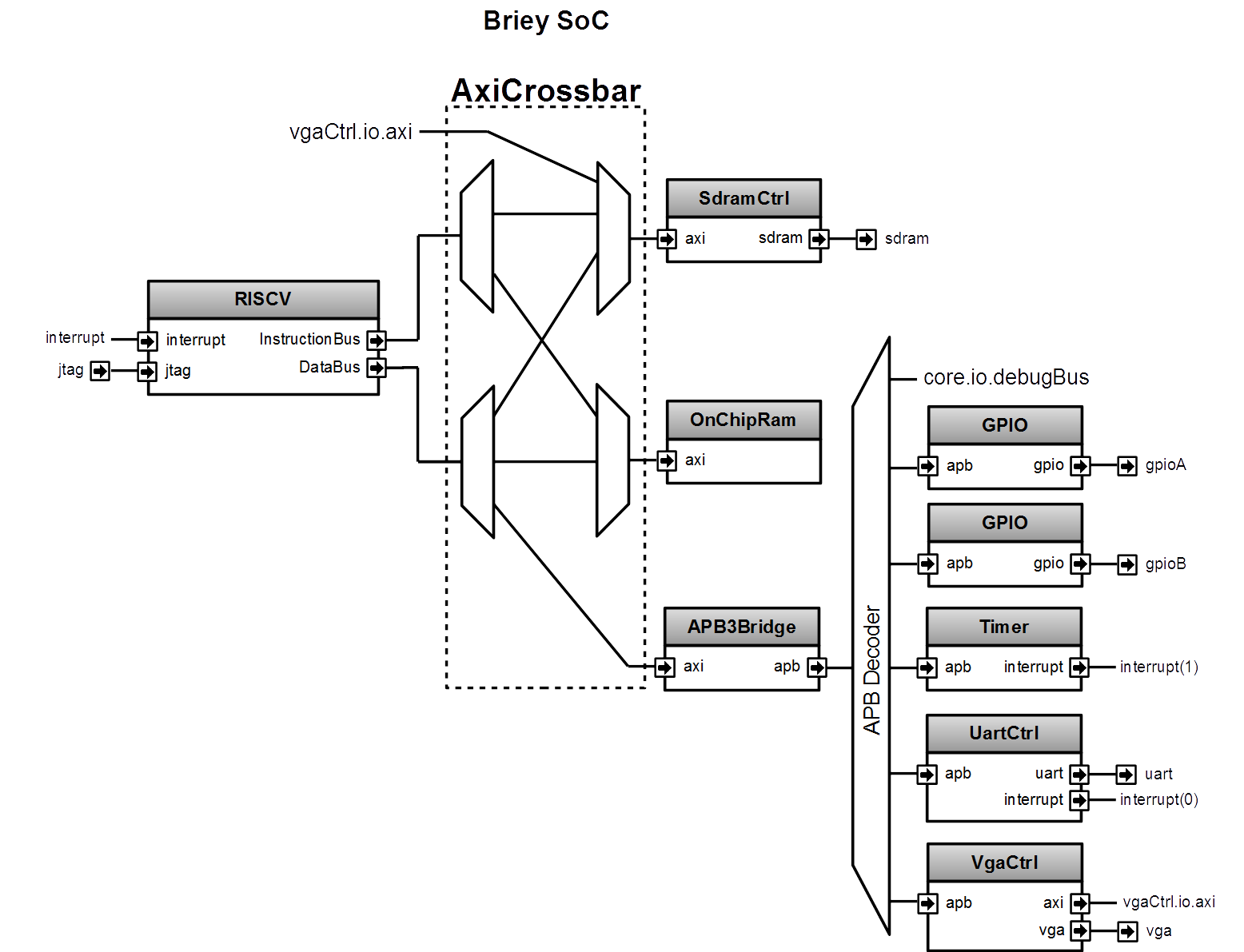

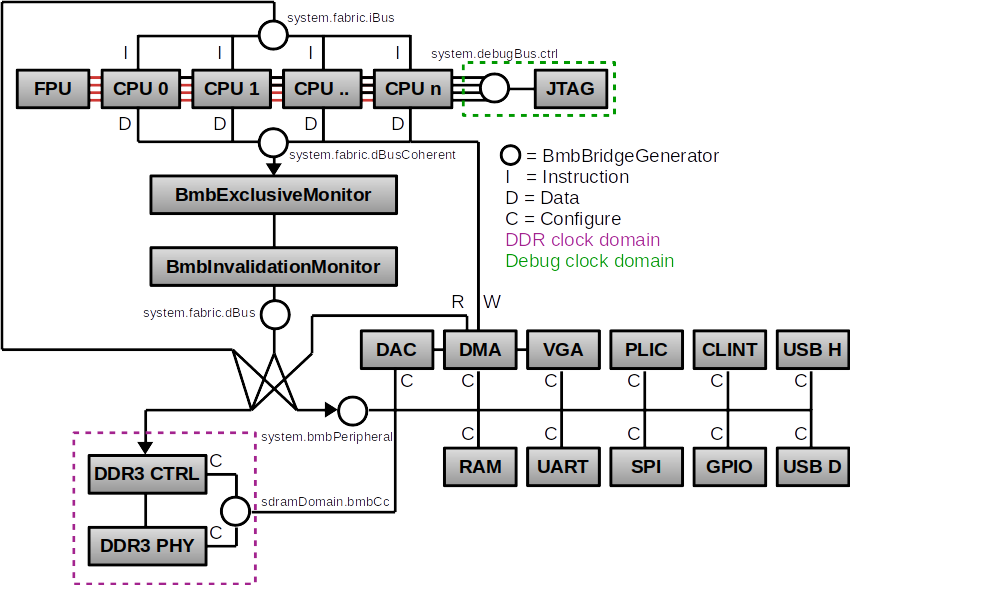

12.2 Синтезируемые системы-на-кристалле на базе VexRiscv

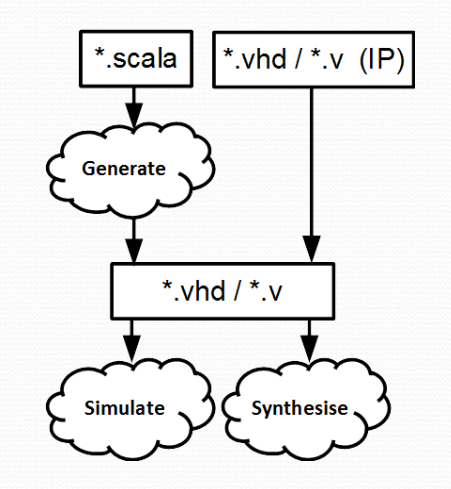

13. Язык описания аппаратуры SpinalHDL

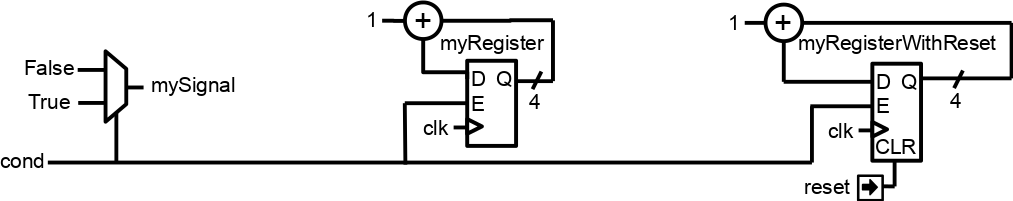

13.1 Базовые конструкции языка SpinalHDL

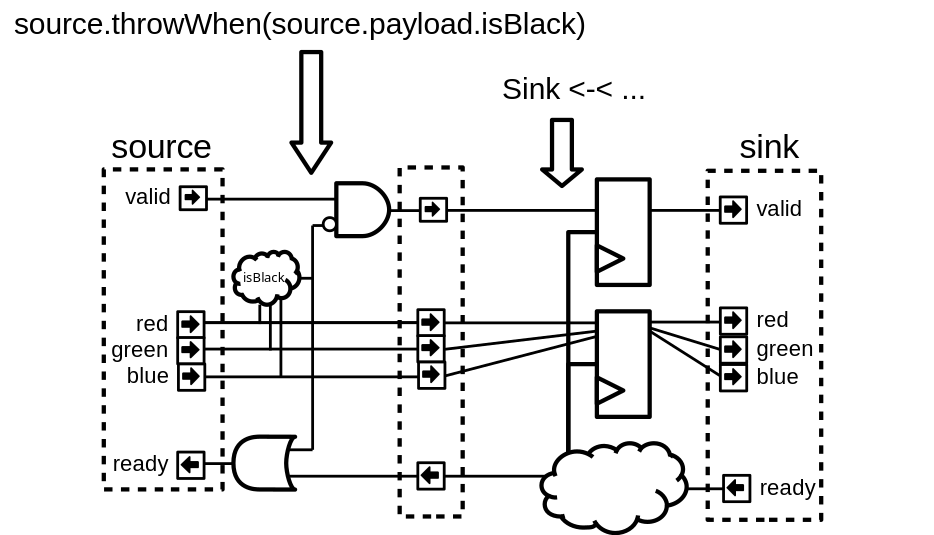

13.2 FSM, потоки, конвейеры, тактовые домены

13.4 Разбор шаблона SpinalTemplateSbt

13.5 Подготовка Makefile-а для синтеза из SpinalHDL в битстрим

13.6 Анализируем вывод сообщений SpinalHDL

13.7 Симуляция и верификация в SpinalHDL

14. Синтез вычислительного ядра VexRiscv

14.1 Знакомство с репозиторием VexRiscv

14.2 Установка компилятора для архитектуры RISC-V

14.3 Подготавливаем Makefile, LPF и toplevel.v

14.4 Добавляем точку входа для генерации СнК Murax для платы «Карно»

14.5 Модифицируем код программы «hello_world»

14.6 Сборка СнК Murax и ядра VexRiscv

14.7 Запускаем СнК Murax на ПЛИС и тестируем «hello_world»

15. Устройство синтезируемого СнК Murax и ядра VexRiscv

15.1 Структура СнК Murax

15.2 Структура вычислительного ядра VexRiscv

15.3 Плагины вычислительного ядра VexRiscv

16. Эксперименты с ядром VexRiscv и СнК Murax

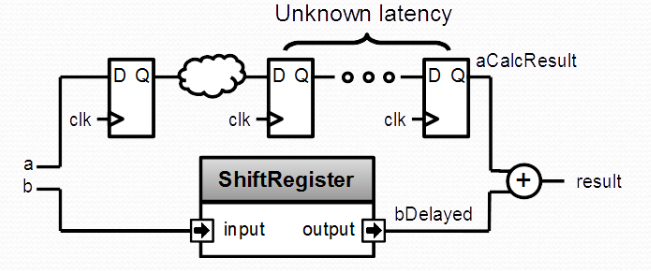

16.1 Оптимизация на примере плагина RegFilePlugin

16.2 Увеличиваем тактовую частоту ядра используя встроенный PLL

16.3 Увеличиваем производительность инструкций сдвига

17. Добавляем свои аппаратные блоки (IP-блоки)

17.1 Микросекундный машинный таймер MTIME

17.2 Подключаем микросхему SRAM

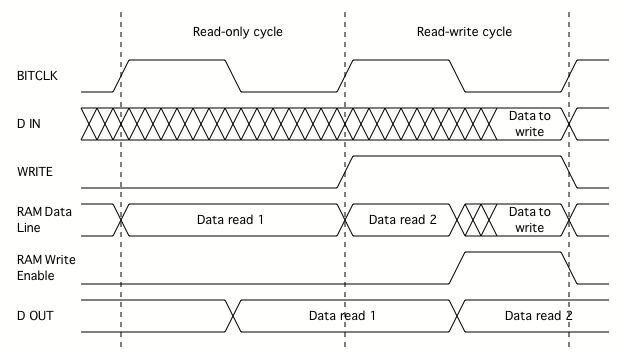

17.2.1 Разрабатываем контроллер SRAM

17.2.2 Тестируем память и контроллер SRAM

17.2.3 Используем SRAM с функцией malloc

17.2.4 Добавляем блоки вычислителей Div и Mul

17.2.5 Задействуем функцию printf

17.3 Подключаем контроллер прерываний PLIC

17.3.1 Разрабатываем простейший контроллер прерываний MicroPLIC

17.3.2 Задействуем контроллер прерываний MicroPLIC из Си программы

17.4 Подключаем контроллер FastEthernet (MAC)

17.4.1 Как работает Ethernet

17.4.2 Подключаем компонент MacEth

17.4.3 Разрабатываем драйвер для компонента MacEth

17.4.4 Отправляем запрос в DHCP сервер

18. Потактовая симуляция СнК Murax

19. Более сложный пример: RiscvWithHUB12ForKarnix

20. Эпилог

Ссылки на репозитории

1. Краткий экскурс в историю

История микросхем началась в 1960 году, когда группа Джея Ласта из Fairchild Semiсonductors продемонстрировала первый работающий полупроводниковый прибор, изготовленный по планарной технологии. Прибор получил название «Интегральная Схема» (или IC от «Integrated Circuit»), а в русскоязычной литературе часто используют просто слово «микросхема», независимо от степени её сложности. История создания микросхемы весьма запутанная, так как этому событию предшествовала серия открытий и изобретений, выполненных различными людьми из разных компаний и стран, поэтому вслед за изобретением микросхемы последовали патентные войны — каждый пытался откусить от пирога кусок поболее. Первая микросхема в СССР была создана в 1961 году в Таганрогском радиотехническом институте. В течении последующих 10 лет мировой радиоэлектронной промышленностью было предложено и испытано множество способов производства микросхем, почти все они полагались на планарный метод изготовления транзисторов на кремниевой, германиевой или сапфировой пластине с помощью процесса фотолитографии — итеративным процессом последовательного нанесения фоторезиста, засветки, проявления, травления, промывки, ионной имплантации и металлизации, а схема, которая образовывалась таким образом, задавалась набором фотомасок.

Примерно до средины 1980-х годов, а это почти 25 лет, все аналоговые и цифровые микросхемы, в том числе микросхемы памяти и микропроцессоров, разрабатывались исключительно путем черчения схем, сначала на бумаге, позже — с использованием САПР, которые по тем временам были весьма примитивны. Но в обоих случаях рисовалась схема электрическая принципиальная, в которой прослеживался каждый проводник. Когда схема была готова, разработчики переходили к её трассировке — формированию расположения отдельных электронных компонентов (транзисторов, резисторов и конденсаторов) на поверхности кристалла, по трассировке формировали набор фотомасок. В этом им часто помогала специальная клейкая лента-скотч Рубилит, которую тонкими полосками наклеивали на прозрачную майларовую пленку (или наоборот — удаляли лишнее), таким образом формируя узор будущей микросхемы в увеличенном формате. Этот узор фотографическим методом и с уменьшением в 100 раз переносился на фотомаску, которая далее использовалась в планарном фотолитографическом производстве.

Микросхемы очень быстро росли в степени интеграции — увеличении числа транзисторов и уменьшении площади на кристалле кремния, что в геометрической прогрессии тянуло за собой увеличение сложности изготовления фотомасок и их стоимости. Очевидно, что такой метод разработки микросхем не мог обойтись без ошибок и для достижения рабочего образца приходилось выполнить порой до десятка итераций, что также не могло не сказываться на стоимости продукции. Изготовление рабочего набора фотомасок занимало значительную часть финансовых и временных затрат на производство микросхемы. Для того, чтобы минимизировать затраты и сократить время, разработчикам приходилось вручную проверять и перепроверять свои дизайны на всех этапах. В какой-то момент схемотехника достигла такой сложности, что проверить её работоспособность вручную стало практически невозможно и логичным решением этой проблемы стало внедрение автоматизированных процессов верификации и симуляции дизайнов. А это означало, что весь дизайн, от схемы до фотомасок, должен был быть теперь представлен в цифровом формате, т. е. в виде данных в файлах: схемы в виде связанного графа элементов (нетлиста), а фотомаски — в виде последовательности команд на языке машин фотоплоттеров (Gerber). Так, для представления схемы в виде соединения отдельных её элементов в электронном виде появились языки описания аппаратуры — HDL от «Hardware Description Language», а процесс разработки стали назвать «VLSI design» от «Very Large Scale Integration» (в русскоязычной литературе — СБИС от «Сверх Большая Интегральная Схема»).

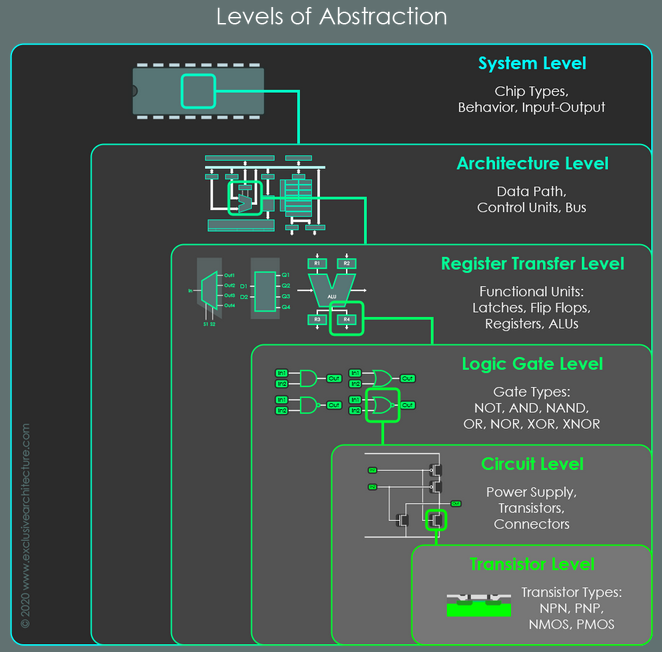

Языки описания аппаратуры (HDL) позволяют представить прежде всего цифровую схему (хотя конечно же есть языки для описания аналоговых схем) в виде текста, подобно языкам программирования, описывают структуру схемы, потоки данных и её поведение с течением времени. История появления HDL насчитывает множество способов описания схем, но способ представления схем на уровне регистровых передач (RTL от «Register Transfer Level») впервые предложенный Гордоном Беллом в 1971 году оказался наиболее удобен для верификации сложных цифровых схем. На основе RTL был создан языке ISP (ISPL и ISPS) на котором была создана модель ЭВМ DEC PDP-8. С тех пор RTL метод используется во всех современных HDL языках для разработки и верификации VLSI дизайнов.

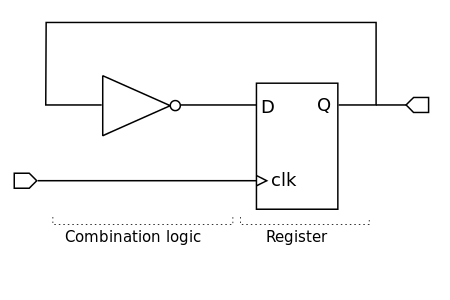

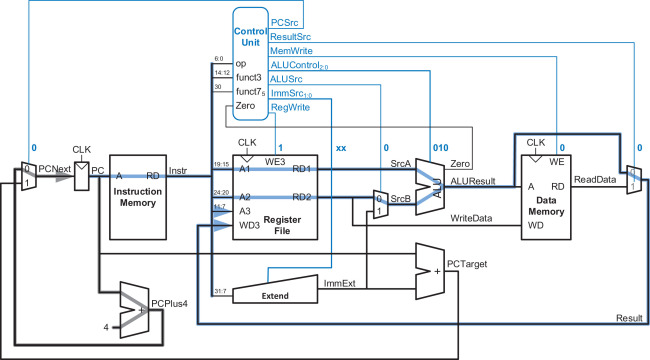

Что бы понять, что такое RTL, необходимо представить цифровую схему в виде отдельных регистров (D-триггеров), управляемых общим тактовым сигналом, а входы и выходы этих регистров обеспечить комбинационной логикой и связать между собой в заданную схему. Таким образом, все цифровые схемы в терминах RTL являются синхронными — данные в них перетекают из одного регистра в другой по переднему фронту тактового сигнала (иногда по спаду). Данные, перетекая между регистрами, претерпевают изменения (обработку) комбинационными схемами, которые работают асинхронно, а задержка распространения сигнала в них не учитывается на уровне RTL, т. е. условно полается, что комбинационные схемы срабатывают мгновенно и 100-процентно (что, разумеется, не так, но об этом отдельно). Ниже на рисунке 2 приведена простейшая синхронная цифровая схема, состоящая из одного регистра (триггера) и одного инвертора. Схема представляет собой делитель тактовой частоты на 2.

Приведенная выше схема может быть описана текстом на языке описания аппаратуры следующим образом:

if rising_edge(clk) then

Q <= ~D;

end if;Это означает, что выходной сигнал Q примет значение инверсное (противоположное) входному сигналу D в следующем такте (сигнал сброса не показан для упрощения понимания).

Данный текст на HDL может быть не только просимулирован, но и с помощью специальных программных средств т. н. «кремниевых компиляторов» может быть автоматически преобразован сначала в связанный граф примитивов (отдельных логических элементов и транзисторов), а затем в их геометрическое представление на кристалле кремния и в конечном счете может быть получен набор фотомасок. В современном производстве фотомаски для изготовления микросхем представляются в электронном формате GDSII, а формат Gerber занял нишу в производстве печатных плат. Процесс преобразования текста HDL в файлы фотомасок раньше было принято называть «аппаратной компиляцией», но сейчас больше используется термин «синтез цифровых схем» (logic synthesis), так как конечным результатом может быть не только геометрическая форма (фотомаска), но некий поток двоичных данных, определяющий конфигурацию микросхемы ПЛИС для реализации заданной цифровой схемы внутри неё.

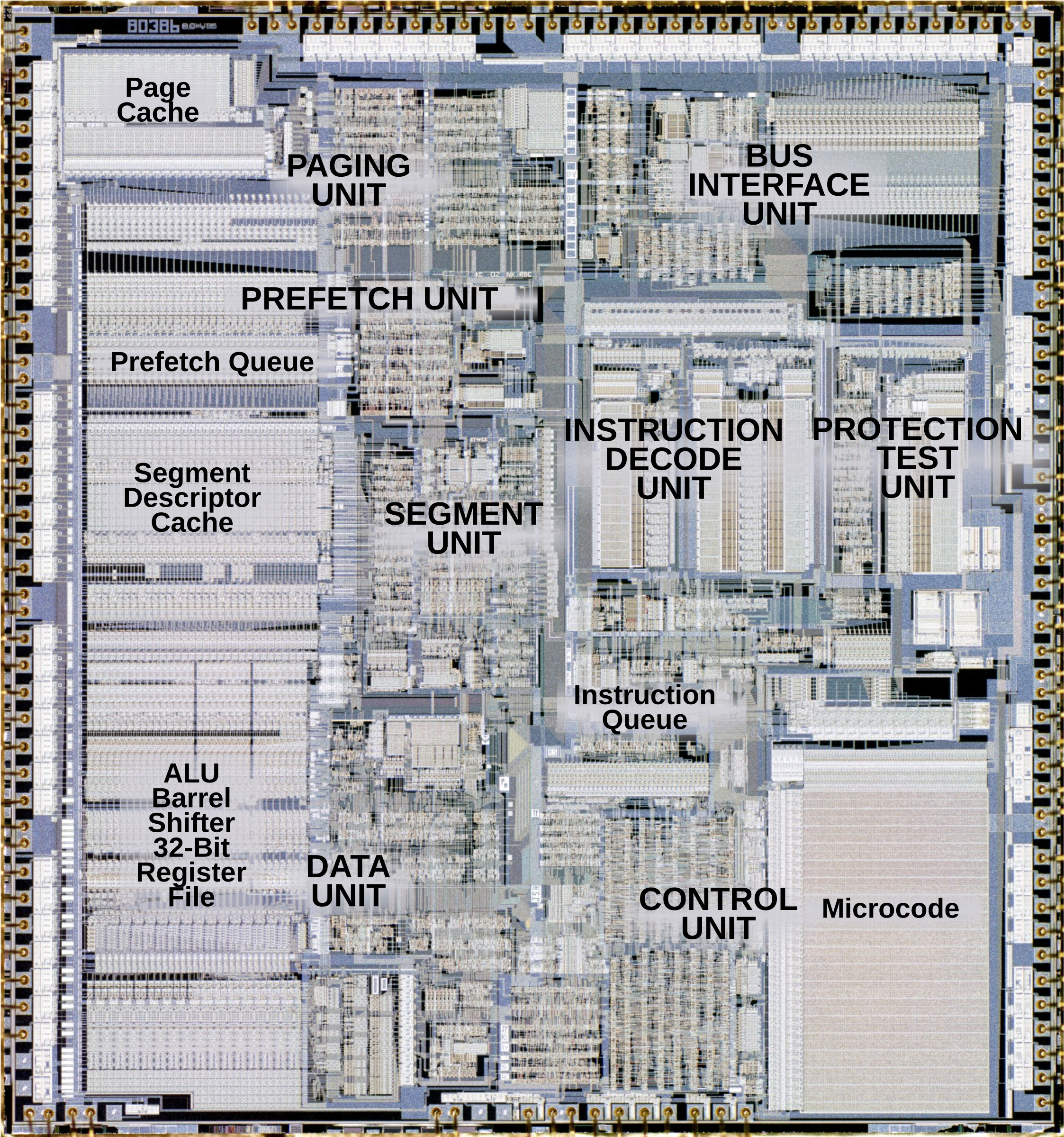

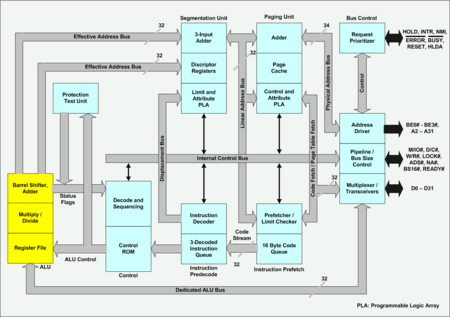

История гласит, что легендарный микропроцессор Intel 80386 является первым микропроцессором компании Intel, который был полностью разработан с помощью цифрового инструментария. Для него была построена полная RTL модель, дизайн итеративно дорабатывался и симулировался потактово до тех пор, пока не было достигнуто совпадение всех симулируемых сигналов с проектными значениями, или, как принято говорить, с «эталонной моделью» (golden reference model). Вот что пишет известный блоггер Кен Ширрифф в свой статье «Examining the silicon dies of the Intel 386 processor» про историю разработки i386:

The design process of the 386 is interesting because it illustrates Intel's migration to automated design systems and heavier use of simulation. At the time, Intel was behind the industry in its use of tools so the leaders of the 386 realized that more automation would be necessary to build a complex chip like the 386 on schedule. By making a large investment in automated tools, the 386 team completed the design ahead of schedule. Along with proprietary CAD tools, the team made heavy use of standard Unix tools such as sed, awk, grep, and make to manage the various design databases.

И далее:

The high-level design of the chip (register-level RTL) was created and refined until clock-by-clock and phase-by-phase timing were represented. The RTL was programmed in MAINSAIL, a portable Algol-like language based on SAIL (Stanford Artificial Intelligence Language). Intel used a proprietary simulator called Microsim to simulate the RTL, stating that full-chip RTL simulation was "the single most important simulation model of the 80386".

The next step was to convert this high-level design into a detailed logic design, specifying the gates and other circuitry using Eden, a proprietary schematics-capture system. Simulating the logic design required a dedicated IBM 3083 mainframe that compared it against the RTL simulations. Next, the circuit design phase created the transistor-level design. The chip layout was performed on Applicon and Eden graphics systems...

В современной практике широкое использование получили два языка описания аппаратуры: VHDL и Verilog. Verilog был предложен частной компанией Gateway Design Automation и входил в состав коммерческой системы разработки микросхем. Взамен проприетарному Verilog-у в недрах минобороны США был разработан VHDL и предложен как открытый стандарт. Изначально оба языка предназначались для документирования и симуляции цифровых схем, но к 1985 году стало понятно, что разрабатывать схемы «в тексте» гораздо легче, чем рисовать их, пусть даже на экране монитора. Такие схемы легче анализировать и модифицировать, легче систематизировать и каталогизировать, над одним и тем же куском кода (схемы) может работать несколько человек, но самое главное — код схемы можно переиспользовать от дизайна к дизайну, легко изменяя небольшую его часть. Код схемы даже может быть параметризован, выделен в отдельные блоки, упакован и продан. Появления HDL привело к созданию целой индустрии купли-продажи IP блоков (здесь IP от «Intellectual Property» — интеллектуальная собственность).

В 1990 году компания Cadence приобрела компанию Gateway Design Automation и сделала Verilog открытым, вскоре после чего оба языка были приняты IEEE как открытые стандарты. За почти 40-летнюю историю существования языки развивались, в них вносились серьезные изменения, добавлялись и расширялись стандартные библиотеки (VHDL), вводились и принимались новые стандарты. VHDL традиционно имел широкое хождение в авиакосмической и военной отрасли (как в США, так и в России, кстати), в то время как Verilog больше популярен в академической среде и в небольших коммерческих компаниях. На начало 2020 годов проявилась явная тенденция к превалированию языка Verilog и к спаду популярности VHDL. С чем это связано — мне сказать трудно.

В 2002 году от языка Verilog отпочковался SystemVerilog который в 2005 году так же был принял стандартом IEEE 1800-2005, а в 2009 году язык Verilog вошел как подмножество в язык SystemVerilog и был принят как стандарт IEEE 1800-2009 SystemVerilog. Отличие Verilog от SystemVerilog примерно такое же, как отличие языков C и C++. SystemVerilog поддерживает классы и объекты, а также сложные структуры сигналов. В современной практике, когда говорят Verilog, подразумевают именно SystemVerilog, либо явно подчеркивают его старую версию стандарта.

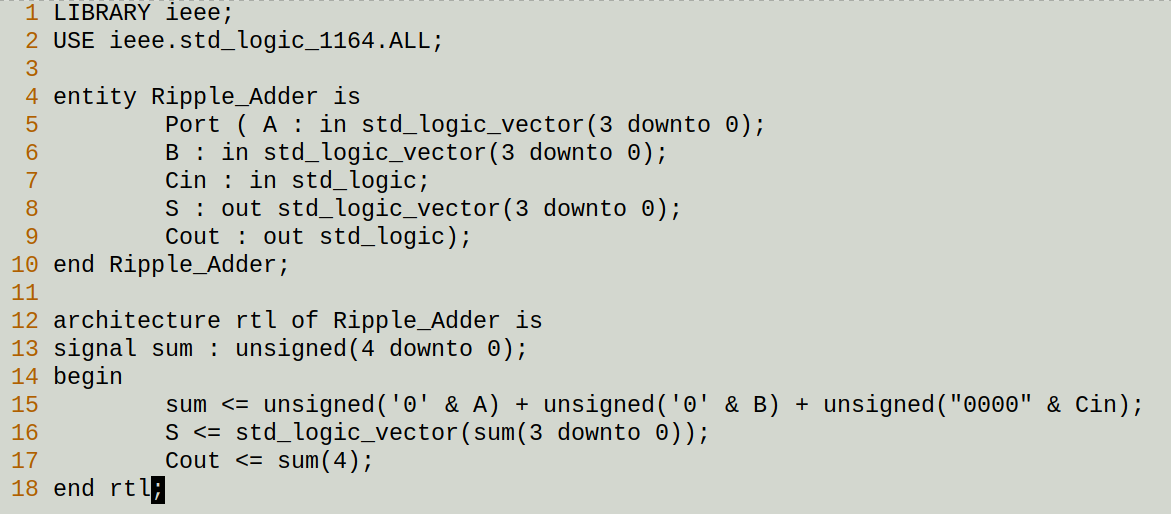

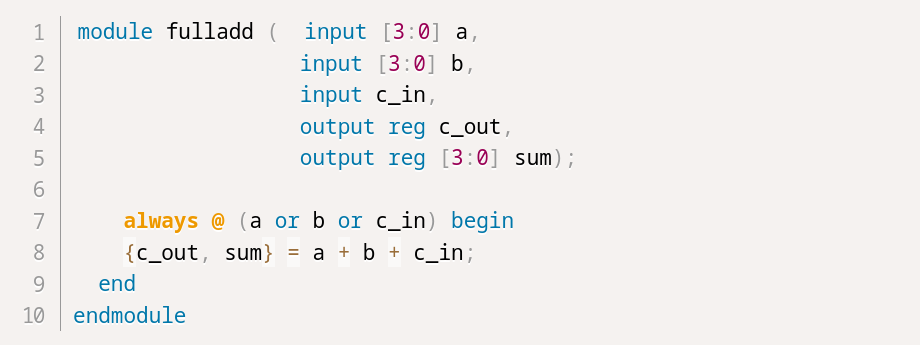

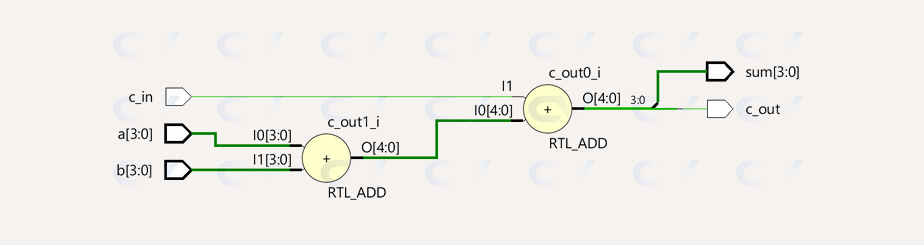

Ниже я приведу в качестве примера схему двоичного 4-х битового полного сумматора описанную на двух языках. На всякий случай напомню, что полным сумматором называется такой сумматор, который выполняет сложение двух входных двоичных чисел заданной разрядности с учетом входного сигнала переноса и формированием на выходе как суммы, так и выходного сигнала переноса, что позволяет соединять полные сумматоры в каскады и получать сумматоры большей битности.

Из приведенного выше примера видно, что VHDL гораздо более многословен, а его синтаксис не всегда понятен и очевиден. В то же время, синтаксис языка Verilog в какой-то степени похож на синтаксис языка Си. Возможно это является одной из причин падения популярности языка VHDL, так как за последние годы в тему разработки цифровых схем вливается всё больше программистов.

2. Появления программируемых логических устройств

Идея сделать логические схемы программно реконфигурируемыми пришла вместе с появлением микросхем памяти (ОЗУ, ПЗУ) в середине 1960х, так как любую микросхему памяти можно рассматривать как логическое устройство, преобразующее набор входящих сигналов, поступающих на линии адреса, в выходящие — снимаемые с линий данных. В этом смысле любая микросхема памяти является аппаратной таблицей преобразования («lookup table», «таблица истинности») и может быть использована для построения перепрограммируемых дешифраторов. И действительно, такое её применение часто использовалось в процессорах больших ЭВМ древности для построения дешифраторов команд, да и по сей день в современных микропроцессорах дешифратор команд часто строится на перепрограммируемой ПЗУ. Построение дешифратора команд на основе перепрограммируемой ПЗУ является поистине великим изобретением, так как позволяет относительно легко исправлять ошибки в системе команд (но не всегда, привет Intel-у) либо вести отладку процессора загружая в память дешифратора специально подготовленные тестовые последовательности.

Использование перепрограммируемых ПЗУ для построения логических схем, разумеется, имеет свои ограничение. Пожалуй, самое очевидное из них — это гигантское число ячеек памяти, необходимое для построения дешифраторов с большим числом входов и выходов. Вспомним, что в 60-х и 70-х годах прошлого века компьютеры были большие, а память у них была крохотной и жутко дорогой. Поэтому в начале 70-х годов сразу несколько компаний, среди которых были такие известные и ныне гиганты полупроводниковой индустрии, как Texas Instruments, General Electric и National Semiconductor, представили на рынок свои варианты микросхем, содержащих массивы логических элементов, соединения между которыми можно было в некоторой степени конфигурировать программно — путем одноразового пережигания перемычек, т. е. использовался тот же самый принцип, что и при программировании ПЗУ. А в некоторых изделиях «прошивку» можно было даже стирать ультрафиолетом и перепрограммировать перемычки повторно. Такие изделия получили название «Programmable Logic Array» — PLA или PAL.

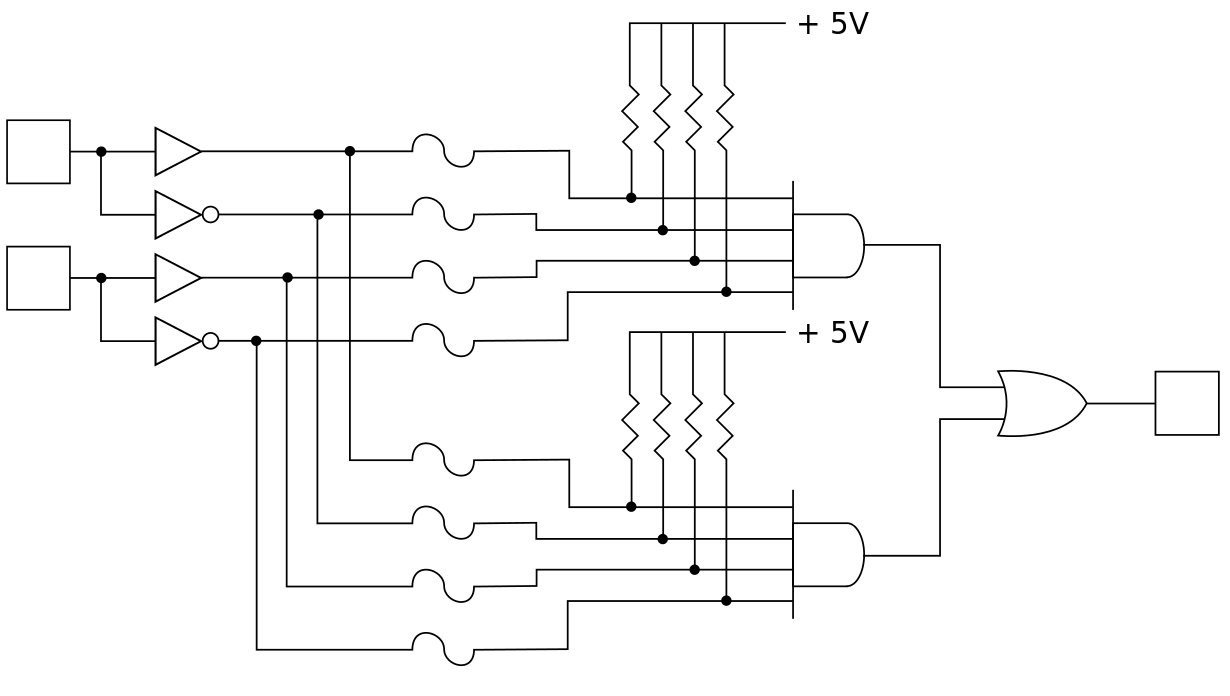

В микросхемах PAL использовалась регулярная структура (рис. 7) из логических элементов «И», обычно рисуемых на схемах горизонтально, выходы которых соединялись логическими элементами «ИЛИ», рисуемых вертикально, таким образом образуя «сумму произведений» (sum of product), что соответствует дизъюнктивной нормальной форме (ДНФ), к которой, согласно булевой алгебре, может быть сведена любая булева формула. Данные структуры в микросхемах PAL, многократно повторяясь, образовывали массив, используя который можно было реализовать любую булеву функцию.

Для программирования микросхем PLA/PAL в 1983 года компанией Monolithic Memories, Inc был разработан специальный язык описания программируемой логики — PALASM, который позволял преобразовать булевы функции и таблицы переходов состояний в таблицу пережигаемых «фьюзов». Компания MMI производила свой вариант микросхемы программируемой логики PAL16R4, появление такого программного инструмента сделало эту микросхему очень популярной, а сам язык PALASM превратился в стандарт «де факто», который использовали подавляющее большинство разработчиков, имеющих дело с PAL.

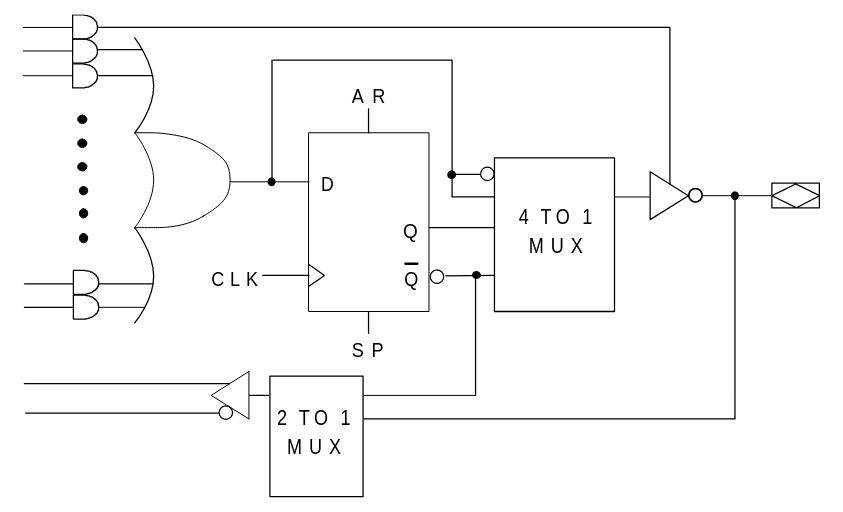

В 1985 году компания Lattice Semiconductor представила свой, расширенный и углубленный вариант микросхемы PAL, которую также можно было перепрограммировать многократно электрическим путем по технологии ЭППЗУ (EEPROM). Эта микросхема имела некоторые структурные усовершенствования: в структуру были введены так называемые «макроячейки» («macrocels») содержащие помимо логических «И» и «ИЛИ» еще регистры (D-триггеры) и мультиплексоры для обхода регистров. Также появилась возможность организовывать обратные связи — подавать сигнал с выхода триггера на вход этой же или других ячеек. Схемы программируемой логики такого типа получили название «Generic Logic Array» (GAL). На рис 9. приведена структурная схема «макроячейки» Lattice GAL22V10, сама микросхема содержала десять таких «макроячеек» (22 входа и 10 выходов).

Микросхема Lattice GAL22V10 была и остается очень популярной в схемах управления и автоматики, а также в качестве связывающей логики (glue logic). Микросхема производилась до 2010 года, а её аналог Atmel ATF22V10 производится и по сей день. Для программирования этой микросхемы был разработан специализированный HDL язык CUPL и среда разработки Atmel WinCUPL. Эта среда позволяет синтезировать из кода на языке CUPL простые цифровые схемы для большого ряда PAL/GAL микросхем или экспортировать его в формате PALASM для применения в других программных продуктах.

Недавно, занимаясь «цифровым ретро», в процессе которого мне требовалось отображать состояние шины адреса и данных для 8-ми битной машины, я с удивлением для себя обнаружил, что в стандартном наборе логики 7400 отсутствует такое полезное устройство, как дешифратор 4-х битовых двоичных чисел в их шестнадцатеричное представление для отображения на 7-ми сегментном индикаторе. Проблема быстро решилась с помощью микросхемы ATF22V10 и небольшого кусочка кода для CUPL, позаимствованного из репозитория Дуга Габбарда, за что ему огромное спасибо. Полный проект и схему подключения микросхемы GAL22V10 (она же ATF22V10) к 7-ми сегментному индикатору можно получить по ссылке: https://sourceforge.net/projects/dual-bcd-to-hex-7-seg-driver/?source=navbar

Добавлю, что опенсорсная реализация компилятора с языка CUPL/PALASM называется Portable GAL Assembler — GALasm и доступна в репозитории на Github-е. GALasm разработал Алессандро Зумо в начале 2000-х годов, но не смотря на такую «древность» его код прекрасно компилируется и работает в современных ОС на основе Linux и BSD.

Также хочу отметить, что на Хабре есть интересная статья «PAL, GAL и путешествие в цифровое Ретро» от пользователя @alecv о структурах и истории PLA, PAL и GAL, с примерами кода на PALASM.

Изделия PLA, PAL и GAL бурно развивались, количество вентилей (логических элементов) и «макроячеек» стремительно увеличивалось, добавлялись новые логические блоки, и позже такие устройства стали называть Programmable Logic Device (PLD) и Complex Programmable Logic Device (CPLD), а в русскоязычной литературе — «Программируемые Логические Устройства». Подавляющее большинство ПЛУ (CPLD) имеют встроенную «перепрошиваемую» память, определяющую связи элементов внутри микросхемы. Так как процесс перепрошивки подразумевает восстановление и повторное прожигание «фьюзов», то количество итераций записи в такие устройства ограничено — от нескольких десятков до нескольких сотен циклов.

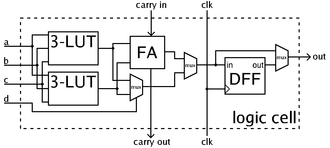

Параллельно с ПЛУ шло развитие программируемой логики и по другому пути. Вместо отдельных вентилей с программируемыми связями, стали использовать массив достаточно крупных блоков логики — «Configurable Logic Blocks» (CLBs), «Logical Units» (LUs), «Logical Cells» (LCs) или «макроблоков». Терминология здесь сильно разнится и зависит от фантазии продаванов конкретного производителя микросхем. Каждый макроблок в таких изделиях имеет в составе программируемую таблицу преобразования («lookup table» или LUT) с двумя, тремя или четырьмя входами, а так же регистр и набор мультиплексоров. Макроблоки располагали в прямоугольную структуру, поверх которой располагалась матрица коммутации. Схема коммутации между входами и выходами макроблоков в таких устройствах задается ячейками статической памяти, выходы которых подключаются к транзисторным ключам матрицы коммутации. Для того чтобы внутри устройства образовалась какая-то схема соединений между макроблоками и сами макроблоки приобрели определенные свойства, необходимо записать данные в требуемые статические ячейки памяти, т. е. загрузить в микросхему битовый поток конфигурации. Такие устройства получили название «Field Programmable Gate Array» (FPGA), в русскоязычной литературе — «Программируемые Логические Интегральные Схемы» (ПЛИС). Структурная схема макроблока (логической ячейки) классической микросхемы ПЛИС приведена на рисунке 10 ниже.

На схеме: 3-LUT — трехвходовая таблица преобразования, FA — полный сумматор, DFF — D-триггер (регистр).

Устройства из массива макроблоков такой структуры имеют определенные преимущества над массивом логических вентилей PLA/PAL и PLD. Если посмотреть на структуру макроблока, то можно определить сходство макроблока с элементарной синхронной схемой, изображенной на рис. 2, которая лежит в основе RTL — комбинационная логика на входе (LUT + сумматор) и регистр (DFF) на выходе. А значит из таких кирпичиков можно складывать синхронные схемы обработки данных и вычислительные блоки.

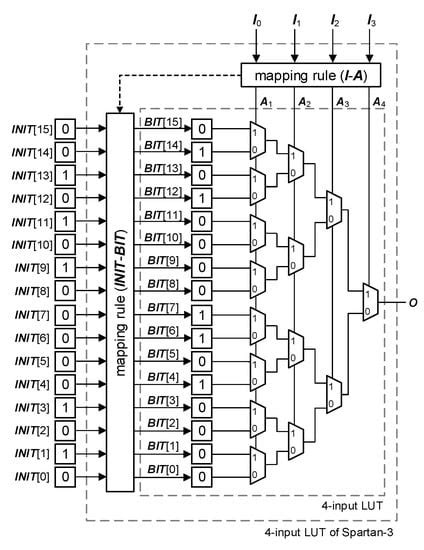

Пару слов про LUT («lookup table»). LUT представляет собой аппаратную программно реконфигурируемую булеву функцию (это может быть «И», «ИЛИ», «НЕ» или любая другая). Реализуется LUT обычно в виде иерархической структуры мультиплексоров, входы нижнего уровня которых подключены к ячейкам статической памяти, задающим выполняемую функцию, а входы управления — к входным сигналам, над которыми эта функция применяется.

На схеме рис. 11 приведена типовая схема четырехвходовой «lookup table» (4-LUT). Линии управления мультиплексорами I0, I1, I2 и I3 являются входными двоичными сигналами для блока 4-LUT, а логическая операция, которая над ними выполняется, задается шестнадцатью битами статической памяти (SRAM) обозначенных на схеме как BIT[0]...BIT[15], состояние которых определяется в момент загрузки конфигурации в микросхему ПЛИС, т. е. в момент её инициализации. Результат операции подается на выход O. На такую таблицу 4-LUT можно посмотреть и с другой стороны — это просто блок статической памяти, который содержит шестнадцать однобитовых ячеек, адресуемых линиями I0...I3. Из схемы видно, что 4-LUT состоит из двух 3-LUT блоков, соединенных мультиплексором верхнего уровня, каждый 3-LUT состоит их двух 2-LUT, также объединенных мультиплексором уровнем пониже, и так далее. Современные ПЛИС могут содержать разное количество LUT разной структуры, вплоть до 7-LUT.

Отличительной особенностью микросхем ПЛИС от ПЛУ (PLA/PAL/PLD/CPLD) долгое время была необходимость в наличии внешнего блока памяти, обычно NOR flash, для сохранения битового потока конфигурации ПЛИС, который должен быть загружен в микросхему ПЛИС при её включении в процессе инициализации. Этим же и определялся основной их недостаток — ПЛИС требует некоторого весьма существенного (до 100 мс) времени для выхода на рабочий режим. В этом смысле микросхемы ПЛУ более удобны, так как в них конфигурация внутренних связей всегда сохраняется состоянием прошитых «фьюзов» даже при отключении питания, а значит ПЛУ готовы к работе почти мгновенно после подачи питания или сброса. В некоторых случаях микросхемы ПЛУ использовались для загрузки конфигурации в микросхемы ПЛИС.

Однако многие современные микросхемы ПЛИС либо уже содержат внутри себя блок NOR flash памяти для сохранения конфигурации (хоть это и не решает проблемы медленного выхода на рабочий режим), либо также как ПЛУ используют технологию перепрограммируемых перемычек («фьюзов»). Последнее относится к изделиям с относительно небольшим числом макроблоков, так как электрически перепрограммируемые «фьюзы» занимают достаточно большую площадь на кристалле, которую целесообразней использовать для «материи» ПЛИС.

Первопроходцем в создании микросхем ПЛИС принято считать компанию Altera (ныне входит в состав Intel). Altera начала в 1983 году с создания достаточно простых PLA/PLD устройств, которые эволюционировали в сложные FPGA. Другим известным производителем микросхем ПЛИС является компания Xilinx (принадлежит AMD), которая вышла на рынок со своими PLD изделиями в 1985 году и на данный момент Xilinx является лидером рынка программируемой логики. Если я не ошибаюсь, то на момент написания данной статьи рекордсменом по числу макроблоков на одном кристалле является микросхема Virtex UltraScale+ VU19P пр-ва Xilinx, которая содержит умопомрачительные 9 миллионов «logical cells» и огромное количество разнообразных «hard blocks».

Надо отметить, что в современных микросхемах ПЛИС помимо макроблоков (логических блоков, LUT-ов) присутствуют т. н. «hard blocks» — блоки специализированной логики и обработки данных, такие как: блоки преобразования частот (PLL), умножители и делители (MUL/DIV) и целые ALU, блоки обработки сигналов (DSP), блоки распределенной памяти (BRAM), блоки динамической памяти (SDRAM), сериализаторы-десериализаторы (SERDES), блоки цифровых интерфейсов и шин (DDR, PCIe, USB), высокоскоростные трансиверы и т. д. С некоторых пор в микросхемы ПЛИС начали активно интегрировать вычислительные ядра ARM.

Таким образом, современные ПЛИС — это сложные гибридные многофункциональные устройства, средствами которых можно решать тяжелые специализированные задачи по высокоскоростной обработке сигналов; строить высокопроизводительные вычислительные системы для симуляции сложных физических процессов или симуляции других специализированных цифровых и аналоговых схем (т. н. ASIC - «Application Specifiс Integrated Circuits») и их верификации при разработке и производстве.

По некоторым данным (Wikipedia), при симуляции ASIC средствами ПЛИС исходят из следующих эмпирических соотношений: площадь симулируемого кристалла будет в 40 раз меньше выбранной для симуляции микросхемы ПЛИС, скорость симуляции составит примерно 1/3 от скорости работы ASIC, а потребляемая мощность ПЛИС будет в 12 раз больше.

Также отмечу, что ряд производителей микропроцессоров (AMD, Intel), начали внедрять в свои высокопроизводительные микропроцессорные изделия «материю» ПЛИС, связь с которой обеспечивается специализированными высокоскоростными интерфейсами внутри одного кристалла. Как применять на практике такие изделия и для решения каких именно задача — мне пока не понятно.

3. Производители микросхем ПЛИС

Я буду использовать термин ПЛИС (или англоязычный вариант — FPGA) как собирательный для всех видов программируемой логики, основанной на макроблоках или макроячейках, так как в современной действительности грань между CPLD и FPGA устройствами сильно размыта, а принципы работы с ними мало чем отличаются.

Прежде всего надо сказать, что каждый производитель микросхем ПЛИС разрабатывает и распространяет свой инструментарий (toolchain или IDE или просто «тул») — целую среду разработки, позволяющую выполнить всё: от разработки схем на нескольких HDL языках (SystemVerilog и VHDL поддерживаются всеми), до верификации, симуляции, визуализации, синтеза и заливки полученной конфигурации. Но важно понимать, что этот инструментарий поддерживает синтез только для микросхемы ПЛИС конкретного производителя и, как правило, является отдельным коммерческим продуктом, который реализуется за отдельные, весьма серьезные деньги. Разумеется, существуют условно-бесплатные ограниченные лицензии на эти тулы. Эти лицензии распространяемые в исключительно «образовательных целях» вполне пригодны не только для обучающихся, но и для вполне опытных разработчиков. Однако, если Вы пожелаете использовать какие-то специфичные «hard blocks» присутствующие в выбранной для Вашего дизайна микросхеме ПЛИС, то скорее всего придется раскошелиться.

Еще один важный момент состоит в том, что на рынке присутствует с десяток производителей микросхем ПЛИС, каждый предлагает огромный модельный ряд своих изделий. Если в рамках одного производителя, точнее даже в рамках одной серии микросхем от одного производителя, присутствует хоть какая-то совместимость, то между микросхемами и тулами разных производителей совместимости нет никакой, а порой даже находятся отличия в синтаксисе HDL языков (несмотря на то, что есть стандарты). Иными словами, если разработчик пристрастился к продукции, скажем, производства Xilinx, то перейти на использование и перенести свои разработки на изделия Alter-ы будет катастрофически непростой задачей. Проблемой здесь являются эти самые «hard blocks», которые специфичны для конкретной микросхемы и конкретного тула конкретного производителя. «Hard blocks» очень сильно упрощают разработку, а во многих случаях без них вообще нельзя обойтись. Для части таких блоков у разных производителей могут быть эквивалентные замены (как например блоки PLL и SERDES есть у всех), но это не значит, что при переходе от одного вендора к другому вы сможете взять и просто перекомпилировать (пересинтезировать) свой дизайн с использованием других блоков. Нет, вам придется хорошо поработать руками и головой — переписать код и плотно протестировать его.

Далее я перечислю список известных производителей микросхем ПЛИС, некоторые из популярных моделей, а также среды разработки (тулы).

Известна следующими линейками микросхем ПЛИС: Vertex (топовые), Kintex (среднего уровня) и Artix — для тех кому попроще. Также широко известна серия гетерогенных изделий Zynq-7000 содержащая целую систему-на-кристалле с вычислительными ядрами ARM в комбинации с «фабрикой» ПЛИС.

Широко известна также серия «классических» ПЛИС микросхем SPARTAN 2/3/4/5/6/7, часть из которых уже снята с производства.

Основной тул: Vivado Design Suite.

2. Atera, Inc. Куплена и поглощена компанией Intel в 2015г, но в октябре 2023г Intel заявил, что собирается выделить бизнес по производству ПЛИС в отдельное независимое подразделение с выходом на IPO.

Известна следующими сериями микросхем ПЛИС: MAX (CPLD); Cyclon I, II, III, IV — классические ПЛИС; Stratix — ПЛИС с высокоскоростными интерфейсами; Cyclon V — гетерогенные с ядрами ARM Cortex-A9; Топовые изделия: Cyclon 10, Arria 10, Stratix 10.

Основной тул: Intel Quartus Prime. Quartus Prime Lite Edition доступен для скачивания бесплатно, но требуется регистрация и получение лицензии.

Устаревший, но имеющий очень широкое хождение тул Altera Quartus II, для которого есть бесплатная версия — Quartus II Web. Если не ошибаюсь, Quartus II работает только с микросхемами, произведенными до 2015г.

3. Microsemi Corporation (бывшая Actel), в 2018г поглощенная компанией Microchip Technology Inc. Специализируется на радиационно-стойких ПЛИС для авиации и космоса, в связи с чем изделия этого производителя содержат небольшое количество логических блоков. Редкий гость в наших краях.

Известна следующими сериями микросхем: IGLOO, PolarFire и PolarFire SoC — содержит ядра RISC-V.

Основной тул: Libero SoC Design Suite

4. Lattice Semiconductor, Inc. Один из старейших производителей микросхем ПЛИС на рынке (основана в 1983г). Производит классические ПЛИС малой и средней плотности (до 100K LUs), низким энергопотреблением и со встроенной конфигурационной памятью.

Известна следующими сериями микросхем: iCE40, ECP5 и ECP5-5G, MachXO (CPLD). Все эти серии микросхем имеют широкое хождение среди студентов и любителей самоделок и на то есть особая причина — поддержка открытым тулчейном Yosys, но об этом позже.

Основной тул: Lattice Diamond. Предоставляет возможность запросить бесплатную краткосрочную лицензию для «образовательных целей».

5. Efinix, Inc. Относительно молодой производитель (основана в 2012 году) с китайскими корнями. Специализируется на микросхемах ПЛИС малой, средней и высокой плотности — 4K-500K LEs. Также редкая птица в наших краях.

Известна следующими сериями микросхем: Trion (T8) и Trion Titanium — содержит ядра RISC-V.

Основной тул: Efinity Software. Доступен бесплатно для скачивания, выдается лицензия на 1 год сопровождения (бесплатные апгрейды) при приобретении комплекта разработчика Xyloni Development Kit.

6. GOWIN Semiconductors. Еще один производитель с китайскими корнями. Специализируется на микросхемах ПЛИС малой и средней плотности, но со своей «изюминкой». В виду своей дешевизны и доступности с Aliexpress, изделия этого производителя имеют широкое хождение в среде самоделкиных. Популярность ПЛИС этого производителя растет. Доступен в России.

Известен следующими микросхемами: LittleBee GW1N (от 1K до 8K LUs), Arora GW2A-18 (20К LUs) и GW2A-55 (54K LUs). Эти ПЛИС также содержат большое количество блоковой статической памяти (BSRAM), а серия GW1NR содержит до 64 Mbits динамической (SDRAM) памяти и доступную пользователю Flash память. Поддерживаются открытым тулчейном Yosys.

Основной тул: GOWIN EDA. Доступен бесплатно, но требуется регистрация и получение лицензии. Доступно в России через посредника.

Под «классическими» я понимаю такие ПЛИС, которые внутри построены на регулярных макроблоках, структура которых приведена на рис. 10 или близкая к ней. Современные изделия от Xilinx и Altera сильно отошли от этой изящной структуры.

4. Синтез цифровых схем для ПЛИС

Не ошибусь если скажу, что появления микросхем программируемой логики PLD/CPLD и FPGA, а это середина-конец 1980-х, произошло в самый подходящий для этого момент. К этому времени уже существовали различные HDL языки; разработка микросхем с использованием HDL и верификация их дизайнов перед запуском производства широко входила в практику. Поэтому для конфигурирования программируемой логики почти сразу начали использовать HDL языки. Для этого был создан инструментарий, позволяющий выполнять «синтез» схем, т. е. преобразование схемы с языков HDL в набор битов конфигурации микросхемы ПЛИС, реализующий заданную схему.

Как же выглядит синтез цифровых схем для ПЛИС на практике? Вкратце, последовательность действий разработчика выглядит следующим образом:

Этап 0. Составление спецификации и эталонной модели

Как и при разработке программного обеспечения, разработка цифровых схем начинается с постановки задачи. Для этих целей проектировщик описывает свойства будущего изделия сначала в виде структурной диаграммы (рис. 13), которая постепенно, сверху вниз детализируется (принцип «top-down design») с использованием микроархитектурных диаграмм (см. пример на рис. 14). Из микроархитектурных диаграмм прослеживаются все присутствующие в изделии сигналы, регистры и логические блоки. По микроархитектурным диаграммам строятся временные диаграммы, описывающие все возможные состояния входных и выходных сигналов и их изменение с течением времени.

Когда готов набор микроархитектурных и соответствующих временных диаграмм, производят создание «эталонной модели» (golden reference model). Для этого часто используют обычные языки программирования или язык SystemC, который представляет собой набор классов для C++. Смысл этого этапа состоит в том, чтобы, во-первых промоделировать систему в целом и понять какие у неё могут быть свойства, какая теоретически достижимая производительность и вообще проверить идею. Во-вторых, чтобы использовать полученную эталонную модель далее для верификации дизайна.

Этап 1. Выбор ПЛИС

Имея на руках спецификации, диаграммы и модель будущего изделия, разработчик определяется с производителем и моделью ПЛИС, на которой он собирается решать поставленную задачу. В этом деле очень много субъективизма и личных предпочтений. Кто-то исторически привык к ПЛИС-ам Altera; кто-то считает, что изделия Xilinx — лучшие, так как микросхемы этого производителя на данный момент самые насыщенные по функционалу; кто-то довольствуется аскетизмом классических ПЛИС от Lattice или дешевизной GOWIN. Главное, чтобы ресурсов ПЛИС, т. е. число LEs, LUTs, блоков памяти и прочих «строительных блоков» имелось с хорошим (читай — двойным) запасом. А для того, чтобы как-то оценить количество требуемых ресурсов, нужны микроархитектурные диаграммы.

Совет от себя лично — для начинающих рекомендую обратить внимание на микросхемы ПЛИС Lattice iCE40 и ECP5, а также GOWIN GW1N и GW2A (LittleBee и Arora).

Этап 2. Приобретение средств разработки

Разработчик определяется с приобретением средств разработки (тулом) и его установки на рабочий ПК (или на сервер). Все современные тулы поддерживают ОС Windows и Linux и могут быть использованы как в интерактивном режиме (IDE), так и в пакетном (командная строка и набор скриптов). Параллельно с этим приобретается отладочная плата (или несколько разных), содержащая выбранную модель микросхемы ПЛИС и устройство для её программирования — как правило, JTAG программатор. Многие отладочные платы сейчас уже идут со встроенным программатором с USB разъемом, что очень удобно. Если для Вашей модели ПЛИС вдруг не оказалось отладочной платы со встроенным программатором, то стоит приобрести отдельный JTAG адаптер, например USB Blaster — этот программатор (JTAG адаптер) поддерживается огромным спектром как коммерческих тулов, так и «опенсорсных» (СПО). Вообще, подойдет любой USB<->Serial адаптер на основе популярной микросхемы FTDI FT2232.

Этап 3. Составление плана распиновки

Изучается спецификация (даташит) на выбранную микросхему ПЛИС и создается описание её внешних выводов — каждому внешнему сигналу назначается один или несколько pad-ов (пинов). Это описание представляется в текстовом файле, обычно имеющего расширение .lpf или .cst. Для создания этого файла в коммерческих тулах имеются специальные средства, позволяющие выбрать модель микросхемы из списка поддерживаемых и визуально распределить сигналы по выводам корпуса микросхемы. Использование таких визуальных средств не всегда удобно, иногда проще создать и редактировать текстовый файл вручную, а параметры pad-ов подсмотреть в даташите на конкретную микросхему.

Ниже, для примера, я приведу небольшую выдержку LPF файла из своего проекта с микросхемой ПЛИС Lattice серии ECP5 (25K LEs). Файл karnix_hub12_cabga256.lpf, структуру которого мы рассмотрим более подробно чуть ниже, содержит примерно следующее:

PORTFREQUENCY PORT "io_clk25" 25.0 MHz;

LOCATE COMP "io_clk25" SITE "B9";

IOBUF PORT "io_clk25" IO_TYPE=LVCMOS33;

LOCATE COMP "io_rgb[0]" SITE "A13"; # LED0

IOBUF PORT "io_rgb[0]" IO_TYPE=LVCMOS33;

LOCATE COMP "io_rgb[1]" SITE "A14"; # LED1 - WORK

IOBUF PORT "io_rgb[1]" IO_TYPE=LVCMOS33;

LOCATE COMP "io_rgb[2]" SITE "A15"; # LED2 - TEST

IOBUF PORT "io_rgb[2]" IO_TYPE=LVCMOS33;

LOCATE COMP "io_rgb[3]" SITE "B14"; # LED3

IOBUF PORT "io_rgb[3]" IO_TYPE=LVCMOS33;

LOCATE COMP "io_gpio[0]" SITE "L1"; # HUB_00

IOBUF PORT "io_gpio[0]" IO_TYPE=LVCMOS33;

IOBUF PORT "io_gpio[0]" PULLMODE=NONE DRIVE=16;

…Этап 4. Написание кода

Разработчик пишет код цифровой схемы на языках HDL — традиционно на Verilog (SystemVerilog) или VHDL. Нетрадиционно — на Chisel, SpinalHDL или nMigen/AmaranthHDL. Существует приличное количество экзотических HDL языков, но почти все они в конечном счете сводятся к генерации кода на языках Verilog или VHDL.

Очень часто при разработке используются библиотечные или приобретенные функциональные блоки (IP блоки) — большие куски кода на HDL, которые требуют адаптации и интеграции в новый дизайн. Языки HDL позволяют создавать (описывать) блоки параметризованными, что сильно упрощает повторное их использование.

Этап 5. Верификация и симуляция

Код отлаживается, верифицируется и симулируется (реализуется потактово). Производится это либо встроенными средствами коммерческого тула от поставщика микросхем ПЛИС, либо приобретенным коммерческими тулами специального назначения, как-то ModelSim и Questa. Крупные компании по разработке микросхем часто используют свои доморощенные тулы для верификации и симуляции, как в примере с Intel 80386 — помните слова Кена Ширриффа про sed, awk и grep ? В академической среде, а так же среди самоделкиных и небольших компаний разработчиков имеют широкое хождение «опенсорсные» тулы, такие как Icarus Verilog и Verilator. Весь процесс разработки, верификации и симуляции итеративно повторяется до тех пор, пока не будет получен дизайн, удовлетворяющий требованиям спецификации или соответствующий «эталонной модели», в которой, кстати, тоже могут быть ошибки.

Следует заметить, что в микроэлектронной промышленности широко проповедуется принцип «Design for Verification» — некий свод правил для инженеров разработчиков и проектировщиков, обеспечивающий выход годной продукции с первого раза. Т.е. дизайн поступает на фабрику только тогда, когда пройдены все этапы верификации и симуляции и есть твердая уверенность в отсутствии ошибок. Причем, «фабы» тоже проверяют поступающие к ним дизайны на соответствие уже своим правилам — «Design Rule Check» (DRC check).

Этап 6. Синтез

Из полученного кода на HDL, средствами выбранного тула производится синтез т. н. netlist-а. Netlist — это файл (обычно формата EDIF, BDIF или JSON) описывающий представление разработанной цифровой схемы из «атомарных» блоков, которые присутствуют в выбранной микросхеме ПЛИС. Такие блоки обычно называют «Standard cells». Синтезированный netlist при желании можно визуализировать в виде цифровой схемы.

Этап 7. Оптимизация и STA

Далее производится оптимизация netlist-а — из него удаляются лишние блоки, типовые структуры комбинируются и замещаются на упрощенные/эквивалентные или на специальные «hard» блоки, специфичные для выбранной ПЛИС. Вся эта процедура выполняется автоматически специальными утилитами, входящими в состав тула. Существует множество алгоритмов оптимизации, они вызываются один за другим из скриптов, повторяются в цикле с разными параметрами и т. д. Опытные разработчики предпочитают писать свои скрипты для оптимизации своих дизайнов.

На этапе оптимизации netlist-а подключаются алгоритмы «Static Timing Analisys» (STA) которые достаточно точно позволяют рассчитать временные задержки распространения сигналов в синтезированной схеме, а также позволяют выполнить ряд оптимизаций по улучшению этого показателя (т. е. уменьшить задержки). Часто бывает так, что на этом этапе дальнейшая обработка netlist-а невозможна, так как в нём присутствуют логические цепочки, рассчитанное время распространения сигнала в которых превышает заданное при разработке схемы значение (нарушение спецификации). В этом случае разработчику приходится возвращаться и перепроектировать схему — переписывать код на HDL, применять другие решения, отказываясь от громоздких комбинационных схем или оптимизировать их вручную разбивая регистрами (т. е. выполнять «конвейеризацию»), после чего повторять весь процесс верификации, симуляции, синтеза и оптимизации.

Этап 8. Расстановка и трассировка

Оптимизированный netlist поступает на вход следующей утилите, которая выполняет процесс расстановки блоков по местам и маршрутизацию сигнальных линий их связывающих, это т. н. процесс «place and route» (PnR или «плэйсер»). В этом процессе каждому блоку из netlist-a определяется фиксированное место внутри микросхемы ПЛИС, а блоки связываются между собой доступными средствами матрицы коммутации, к которой также подключаются внешние вывода (pad-ы) микросхемы и тактовые сигналы. На этом этапе происходит очень тяжелый и затратный по времени и ресурсам процесс оптимизации, но уже не структурной, а топологической — утилита PnR ищет оптимальное расположение блоков и их связей, так чтобы не нарушить дизайн и его временные характеристики. Результатом работы утилиты плэйсера является топологическое представление схемы внутри ПЛИС (тоже файл формата EDIF или JSON). После работы плэйсера временные характеристики дизайна, как правило, улучшаются, но бывает и наоборот — всё становится только хуже и разработчику приходится возвращаться к редизайну на HDL. Иногда проблемы с расстановкой можно решить изменением числа «рандомизации» (seed), так как алгоритмы плэйсера не являются строго детерминированными и часто основываются на случайных последовательностях. Т.е. покрутив «seed» несколько раз, можно попытаться добиться результата, удовлетворяющего требованиям STA, и это будет работать.

Надо отметить, что трассировка тактовых сигналов, как правило, производится отдельно от остальных цифровых сигналов, и для них в микросхемах ПЛИС предусматриваются специальные глобальные линии («global nets») с минимальными задержками и искажениями фронтов. Если в дизайне используются генерируемые внутри него тактовые сигналы, то такие сигналы требуют особого внимания — их требуется вывести на глобальные линии, для чего используется специальный синтаксис и специализированные «hard» блоки, предназначенные для этой цели. Также глобальными линиями принято трассировать сигналы сброса (resets) и некоторые общие для множества блоков схемы сигналы разрешения (enable signals). Иногда утилита синтеза автоматически распознает такие сигналы и маркирует их специальным образом, чтобы плэйсер на этапе размещения и трассировки использовал глобальные линии, но это не всегда работает верно и требует внимания разработчика.

Синтезатор, оптимизатор и плэйсер обычно сообщают в log-ах о том, какие решения были приняты в процессе и какие из сигналов и каким способом были трассированы. Также в log-ах могут появляться предупреждающие сообщения о сомнительных моментах дизайна, которые могут в конечном счете работать совсем не так, как это запланировал разработчик, поэтому log нужно внимательно читать и анализировать.

В больших и сложных дизайнах для FPGA (и особенно для ASIC) обычно присутствует еще один этап, предшествующий вызову плэйсера, который называется «floorplanning» и в процессе которого для плэйсера задают набор правил и ограничений. Например, разработчик может посчитать необходимым размещение каких-то отдельных блоков рядом друг с другом или возле выходных сигналов (возле pad-ов) или поближе к линиям питания. Но в большинстве случаев этот процесс планирования расстановки проистекает автоматически внутри плэйсера и дает приемлемый результат.

Этап 9. Генерация битстрима

Завершающим этапом синтеза является генерация «битстрима» — последовательности бит которую можно загрузить в микросхему ПЛИС. Для этого используется отдельная утилита в составе тула, она принимает на вход JSON файл от плэйсера и генерирует на выходе двоичный файл (обычно с расширением .bit, .bin или .fs) готовый к загрузке в ПЛИС. В большинстве случаев это чисто технический этап выполняемый автоматически и не требующий взаимодействия с разработчиком.

Этап 10. Загрузка в ПЛИС и проверка на железе

После того как разработчик получил «битстрим», его можно и нужно загрузить в NOR flash память на отладочной плате чтобы микросхема ПЛИС считала его при следующей инициализации. Производится это с помощью JTAG программатора (см. выше) и специальной утилиты. В коммерческих тулах такая утилита входит в поставку. Существуют и «опенсорсные» утилиты, например openFPGALoader.

Очень частно, при активной отладке дизайна и прогонке его «на железе», имеет смысла загружать битстрим не в NOR flash, а прямо в конфигурационные регистры SRAM микросхемы ПЛИС. Это позволяет, во-первых, экономить число операций записи во flash, во-вторых, это существенно быстрее и позволяет экономить время разработчику. Но тут надо не забывать о том, что при сбросе (инициализации), микросхема ПЛИС всегда считывает конфигурацию из NOR flash, т. е. заново перезапишет содержимое своей конфигурационной памяти, а загруженный в неё ранее битстрим будет потерян. Если разработчик случайно выпускает этот момент из вида, то это часто приводит к разного рода «необъяснимым» эффектам в поведении отлаживаемого дизайна. Поэтому, мой небольшой совет начинающим — если что-то идет не так, перезалейте Ваш битстрим в NOR flash и выполните сброс по питанию!

5. Yosys Open SYnthesis Suite

Про существование программируемой логики я лично узнал еще в конце 90-х, будучи студентом, но микросхему ПЛИС живьём увидел много лет спустя - в 2010 или где-то около того. Если не ошибаюсь, то была микросхема про-ва Altera серии Cyclon II на небольшой плате в комплекте с кварцевым генератором и стабилизаторами питания. Больше на плате ничего не было, все выводы ПЛИС были попросту выведены на штыревые разъёмы, расположенные по четырем сторонам платы. Разумеется, у меня возникло желание попробовать «запрограммировать» её, но я тут же столкнулся с рядом трудностей. Во-первых, требовался какой-то JTAG программатор, а эти устройства в то время стоили баснословных денег (и софт для них тоже). Во-вторых, всё сообщество российских (да и западных) разработчиков-плисоводов плотно сидело на ОС Windows и интенсивно ёрзало мышами по экрану. Для меня, человека, привыкшему работать в командной строке удаленно по SSH и люто ненавидящему не только «винду», но и весь проприетарный софт, это вызывало стойкое отвращение (разумеется, мне часто приходилось использовать «винду», но только лишь для того, чтобы запустить PuTTY). Я несколько раз выкачивал Quartus II под Linux и пытался устанавливать его на сервер разработки, но сталкивался с какими-то нерешаемыми трудностями — понять, как пользоваться этим мульти-гигабайтным тулом из shell-а было не просто, так как детальной инструкций никто не написал, а все форумы в то время были завалены инструкциями со скриншотами окошек. Короче, ни Quartus, ни Vivado, ни любой другой проприетарный тул я осилить так и не смог. А может быть, просто не захотел.

Зато в 2018 году я узнал про существование полностью open source решения для синтеза цифровых схем и это сильно прибавило мне энтузиазма. Интерес к теме программирования ПЛИС также подогревался начавшей бурно цвести темой RISC-V (по-русски читается как «риск-5», а не как вакцина от Ковида) — полностью открытой микропроцессорной архитектуре, вычислительные ядра которой уже можно было синтезировать для ПЛИС. Так я повторно начал погружаться в тему, но уже совсем c другим, нетрадиционным подходом.

Основная утилита в этом опенсорсном решении, Yosys, представляет собой тул для выполнения синтеза, т. е. преобразования описания цифровой схемы из текста на языке Verilog в netlist с последующим выполнением процедур оптимизации, используя библиотеку Berkeley ABC. Если быть более точным, то Yosys — это всего лишь фронтэнд, преобразующий текст на языке Verilog (позже добавили поддержку VHDL) в структуры, которые может обрабатывать библиотека ABC, а вся магия происходит именно в ней. Библиотека ABC появилась очень давно и уходит своими корнями в 1980-е годы. Всё это время основное применение библиотека ABC находила в академических застенках для моделирования, симуляции и верификации, и лишь появление утилиты Yosys в 2014 году сделало доступным всю мощь ABC для широких масс. Вместе Yosys, ABC, NextPNR и еще ряд других открытых проектов устроили настоящую революцию в индустрии синтеза цифровых схем в конце 2010-х годов, где преобладало засилье закрытых, проприетарных, бесконечно раздутых и заоблачно дорогих программных пакетов с входом «только для своих».

И Yosys это не только для ПЛИС. На данный момент на основе цепочки утилит, во главе которых находится Yosys, построен пакет открытых программ OpenLane/OpenROAD, предназначенный для автоматизации разработки и автоматической трассировки микросхем (ASIC), с помощью которого любой желающий может полностью выполнить дизайн цифровой микросхемы и даже бесплатно заказать её в производство в составе «Multi Project Wafer». MPW — это способ производства, когда на одной кремниевой пластине («вафле») размещается несколько разных проектов с целью удешевления производства прототипов.

Интересно и то, что Yosys изначально это бакалаврская дипломная работа Клиффорда Вулфа, выполненная при работе над другим проектом.

Wol13] Wolf, Clifford: Design and Implementation of the Yosys Open SYnthesis Suite. 2013. – Bachelor Thesis, Vienna University of Technology.

Отличная документация, написанная Вулфом по утилите Yosys, находится тут.

Как я отметил выше, Yosys — это своего рода верхушка айсберга, под которой скрывается целая цепочка связанных воедино опенсорсных проектов с целью предоставить широкой общественности вариант законченного альтернативного решения для синтеза цифровых схем и не только. Ниже я попытаюсь кратко разобрать некоторые, самые важные, из них.

Arachne-pnr («паук»). Утилита-плэйсер и первая попытка реализовать полностью законченный опенсорсный тул синтеза для ПЛИС, автором является Коттон Сид. Сид связал проекты IceStorm и Yosys и дописал к ним недостающее звено — «плэйсер», в результате получил тул для синтеза под микросхемы ПЛИС Lattice iCE40. На данный момент «паук» больше не поддерживается, весь его функционал полностью перекрывается другим, более мощным инструментом — NextPNR.

IceStorm. Проект по документированию внутреннего устройства микросхемы ПЛИС Lattice iCE40. Проект выполнен Мэтиасом Лассером (Mathias Lasser) и всё тем же Клиффордом Вулфом в 2015 году.

Идея проекта следующая. Всем очень хочется иметь открытый тул для синтеза, но внутренняя структура микросхем ПЛИС тщательно скрывается их производителями «за семью патентами», что сильно препятствует созданию такого полезного тула. Не беда. Возьмем самую простую по структуре микросхему ПЛИС, возьмем проприетарный тул от производителя и будем синтезировать много «случайных» схем, а к полученному битстриму применим статистический анализ. Ну почти как арабский математик Аль-Кинди, который в 9-м веке придумал статистический метод взлома шифров. И это сработало! Первая микросхема ПЛИС, которую полностью документировали Мэт и Клифф, была iCE40 производства Lattice Semiconductors.

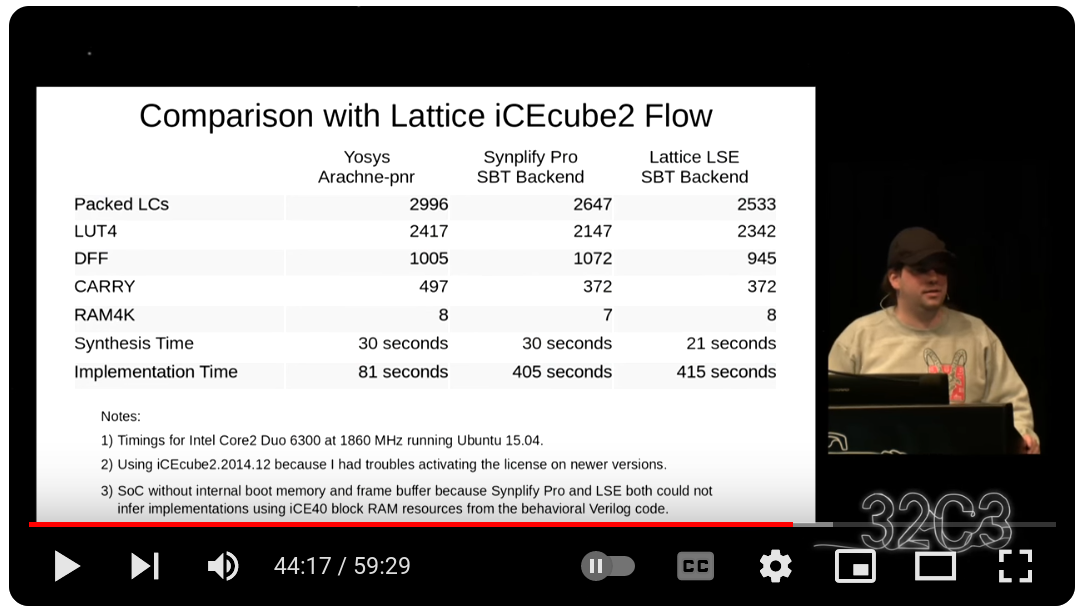

С результатами этой ошеломляющей работы Клифф выступил на регулярном съезде Der Chaos Computer Club (видео). В своем выступлении Клифф демонстрировал слайды, в которых сравнивал качество и скорость синтеза созданного ими инструмента с проприетарным. Результат потрясающий — несмотря на некоторое отставание в оптимальности использования ресурсов микросхемы, опенсорсный тул работал в разы быстрее проприетарного!

Чуть позже в рамках проекта Project Trellis была полностью документирована микросхема ПЛИС Lattice ECP5 со всеми её «hard» блоками. А это очень интересная по своим возможностям микросхема, позволяющая синтезировать в ней ядро RISC-V с MMU и гонять на этом ядре настоящий Linux.

Разумеется, идею Клиффа и Мэта тут же подхватило сообщество, и процесс не пошел, а полетел, моментально последовали проекты по документированию ПЛИС других производителей. Проекты IceStorm, Trellis, Oxide, Apicula, Mistral, X-ray и Chibi нацелились на реверс-инжиниринг и документирование популярных микросхем ПЛИС и на данный момент в разной степени готовности имеется документация на Lattice iCE40, ECP5 и Nexus; Altera Cyclon V; Intel MAX; Xilinx Artyx и UltraScale; Gowin LittleBee и Arora. Эта документация формализована и представляется в виде специализированной базы данных — ChipDB.

В этом видео Дэйвид Шах (David Shah) из Project Trellis рассказывает, как он и его команда зареверсили микросхему ПЛИС Lattice ECP5, как выглядит битстрим для этой ПЛИС и какие инструменты ему пришлось создать, чтобы проводить анализ («fuzzing») битстрима.

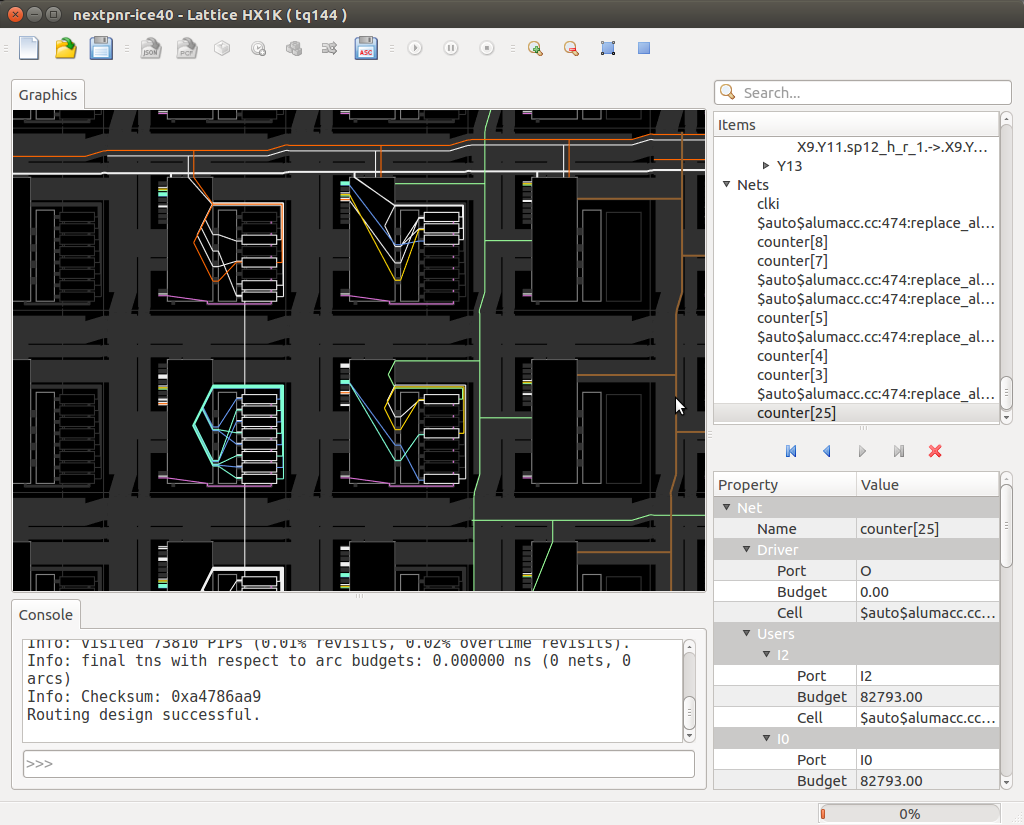

NextPnR — новый, продвинутый, универсальный (вендоро-независимый), timing driven, плэйсер с открытым исходным кодом, поддерживающий все микросхемы ПЛИС из ChipDB. NextPNR работает в полностью автоматическом режиме, принимает на вход результат работы синтезатора Yosys, а также файлы с описанием ограничений (LPF и ряд других) и выдает на выходе файл, по которому можно уже легко построить битстрим. Помимо этого, NextPNR может генерировать файлы в формате SVG с изображением схемы, полученной в результате размещения и трассировки, что может быть использовано для визуализации, отладки и дальнейшей ручной оптимизации дизайнов.

при синтезе для микросхемы ПЛИС Lattice iCE40HX1K.

openFPGALoader — универсальная утилита-программатор для загрузки битстрима. Поддерживает огромное количество устройств-программаторов, микроcхем ПЛИС и ПЛУ (не только тех, что присутствуют в ChipDB). Имеет возможность гибкой подстройки сигнальных линий JTAG, позволяя использовать программаторы, даже если их нет в списке поддерживаемых. Позволяет загружать битстрим как в NOR flash, с которой работает ПЛИС, так и в RAM самой ПЛИС. Может быть использована для прошивки большого количества различных моделей микросхем NOR flash памяти. Утилита openFPGALoader уже присутствует в репозиториях пакетов почти всех известных дистрибутивов Linux и *BSD.

На данный момент существует над-проект YosysHQ который покрывает все вопросы синтеза, верификации, симуляции, трассировки и создания документации для микросхем ПЛИС с использованием решений с открытым исходным кодом. Авторы и активные коммиттеры этого проекта организовали свою компанию (YosysHQ GmbH) и предлагают услуги консалтинга, а также ряд коммерческих продуктов на основе созданных ими опенсорсных решений.

6. Как установить утилиты тулчейна Yosys

Самый простой способ — это скачать и установить готовый пакет бинарных программ «OSS CAD Suite» подготовленный разработчиками из YosysHQ, который оформлен двумя способами: в виде docker контейнера и в виде тарболла. Бинарный пакет собирается каждую ночь (nightly builds) и выкладывается в репозиторий, поэтому тут нужно быть осторожным, чтобы случайно не попасть на «сломанную» версию пакета (если что-то пошло не так, то нужно попробовать более раннюю версию пакета). На данный момент «еженощно» формируются билды для нескольких платформ, вот выдержка из README репозитория:

linux-x64

Any personal Linux based computer should just work, no additional packages are needed to be installed on system to make OSS CAD Suite working. Distributed libraries are based on Ubuntu 20.04, but everything is packaged in such a way so it can be used on any Linux distribution.

darwin-x64

Any macOS 10.14 or later with Intel CPU should use this distribution package.

darwin-arm64

Any macOS 11.00 or later with M1 CPU should use this distribution package.

windows-x64

This architecture is supported for Windows 10 and 11, but older 64-bit version of Windows 7, 8 or 8.1 should work.

linux-arm

ARM based Linux devices such as Raspberry Pi 3, 4 or 400 can use this distribution package.

linux-arm64

ARM64 based Linux devices using 64bit CPU as in Raspberry Pi 4 and 400 (with 64bit version of OS installed), and also laptops like the MNT Reform 2 can use this distribution package.

linux-riscv64

RiscV-64 based Linux devices should use this distribtuion package, but please note that this is currently untested

Установка через docker, пожалуй, наиболее простой вариант, так как у YosysHQ имеется свой «Hub» на сайте Docker-а, на котором выкладываются docker файлы для всех имеющихся вариантов пакета. Это значит, что выкачать и установить контейнер, собранный для платформы linux-x64, можно командой вида:

$ docker pull yosyshq/cross-linux-x64Установить из тарболла тоже не сложно. Достаточно сходить в репозиторий по ссылке:

https://github.com/YosysHQ/oss-cad-suite-build/releases/latest

и скачать требуемую версию пакета (.tgz файл объемом около 500МБ). После чего распаковать скачанный пакет в домашний каталог или любое другое удобное место, прописать пути к исполняемым файлам в $PATH и подготовить окружение:

Для Linux и MacOS:

export PATH="<extracted_location>/oss-cad-suite/bin:$PATH"Для FreeBSD:

setenv PATH "<extracted_location>/oss-cad-suite/bin:$PATH"далее подготовить переменные окружения специальным скриптом:

source <extracted_location>/oss-cad-suite/environmentДля пользователей Windows:

из текущей оболочки:

<extracted_location>\oss-cad-suite\environment.batили создать новое окно с оболочкой:

<extracted_location>\oss-cad-suite\start.batТе, кому религия не позволяет использовать готовые бинарные пакеты, а я придерживаюсь именно этого течения, могут попробовать собрать весь стек утилит (или какую-то его часть) из исходных кодов. Мне удавалось успешно собирать почти весь стек под ОС ALT Linux p10 (x64) и под ОС FreeBSD 13.2 (amd64). Но это тема отдельного, очень длинного разговора.

После того как Вы установили Yosys тулчейн любым из способов, необходимо проверить, запускаются ли у Вас соответствующие утилиты:

rz@devbox:~$ yosys -V

Yosys 0.36+58 (git sha1 ea7818d31, gcc 7.5.0-3ubuntu1~18.04 -fPIC -Os)

rz@devbox:~$ openFPGALoader -V

openFPGALoader v0.11.0 Для работы с ПЛИС Lattice ECP5 потребуются следующие утилиты:

rz@devbox:~$ nextpnr-ecp5 -V

"nextpnr-ecp5" -- Next Generation Place and Route (Version nextpnr-0.6-157-g4a402519)

rz@devbox:~$ ecppack --version

Project Trellis ecppack Version 1.2.1-14-g488f4e7

rz@devbox:~$ ecpbram

Project Trellis - Open Source Tools for ECP5 FPGAs

ecpbram: ECP5 BRAM content initialization tool

rz@devbox:~$ ecpprog --help

Simple programming tool for FTDI-based Lattice ECP JTAG programmers.

Usage: ecpprog [-b|-n|-c] <input file>

ecpprog -r|-R<bytes> <output file>

ecpprog -S <input file>

ecpprog -t Для работы с ПЛИС Lattice iCE40 потребуются следующие утилиты:

rz@devbox:~$ nextpnr-ice40 -V

"nextpnr-ice40" -- Next Generation Place and Route (Version nextpnr-0.6-157-g4a402519)

rz@devbox:~$ icepack -h

Usage: icepack [options] [input-file [output-file]]

rz@devbox:~$ icebram

Usage: icebram [options] <from_hexfile> <to_hexfile>

icebram [options] -g [-s <seed>] <width> <depth>

Replace BRAM initialization data in a .asc file. This can be used

for example to replace firmware images without re-running synthesis

and place&route.

rz@devbox:~$ iceprog --help

Simple programming tool for FTDI-based Lattice iCE programmers.

Usage: iceprog [-b|-n|-c] <input file>

iceprog -r|-R<bytes> <output file>

iceprog -S <input file>

iceprog -t

Для работы с ПЛИС GOWIN LittleBee и Arora потребуются следующие утилиты:

rz@devbox:~$ nextpnr-gowin -V

"nextpnr-gowin" -- Next Generation Place and Route (Version nextpnr-0.6-157-g4a402519)

rz@devbox:~$ gowin_bba -h

usage: gowin_bba [-h] -d DEVICE [-i CONSTIDS] [-o OUTPUT]

Make Gowin BBA

rz@devbox:~$ gowin_pack -h

usage: gowin_pack [-h] -d DEVICE [-o OUTPUT] [-c] [-s CST] [--allow_pinless_io] [--jtag_as_gpio] [--sspi_as_gpio] [--mspi_as_gpio]

[--ready_as_gpio] [--done_as_gpio] [--reconfign_as_gpio]

Pack Gowin bitstream Также для работы Вам потребуется ряд вспомогательных утилит:

rz@devbox:~$ make -v

GNU Make 4.1

Built for x86_64-pc-linux-gnu

rz@devbox:~$ netlistsvg --version

1.0.2

rz@devbox:~$ xdot -h

usage: xdot [-h] [-f FILTER] [-n] [-g GEOMETRY] [--hide-toolbar] [file]

xdot.py is an interactive viewer for graphs written in Graphviz's dot language.

Для проверки синтаксиса, верификации и симуляции Вам потребуются:

rz@devbox:~$ iverilog -V

Icarus Verilog version 10.1 (stable) ()

rz@devbox:~$ gtkwave -V

GTKWave Analyzer v3.3.117 (w)1999-2023 BSI

rz@devbox:~$ verilator --version

Verilator rev v5.020-157-g2b4852048 Ну и последний, но важный момент. Чтобы утилита openFPGALoader могла иметь доступ к USB программатору в операционной системе Linux, требуется добавить набор правил для systemd. Для этого необходимо скачать файл с правилами https://github.com/trabucayre/openFPGALoader/blob/master/99-openfpgaloader.rules, поместить его в каталог /etc/udev/rules.d/ и перезагрузить операционную систему. Выполнять это нужно от имени суперпользователя (root-а).

7. Пример использования открытого тулчейна Yosys

Настало время попробовать Yosys в деле. По законам жанра здесь должен был бы следовать пример а-ля «hello, world», то есть мигание светодиодом или что-то в этом роде. Но я хотел бы направить читателя несколько другим путём и познакомить с очень интересным проектом по обучению широких масс основам цифрового синтеза и верификации. Этот проект так и называется «Школа синтеза цифровых схем», его идейным вдохновителем является Юрий Панчул (@YuriPanchul), наш соотечественник, который несколько десятков лет трудится в именитых электронных компаниях в «Кремниевой Долине» и имеет огромный опыт в этой сфере. У Юрия есть свой блог на Habr-е, где он регулярно выкладывает тематические статьи и посты о том, как устроена эта индустрия, какие в ней превалируют тенденции и какие актуальные проблемы присутствуют.

Со слов Юрия, по долгу службы ему часто приходится проводить собеседования молодых специалистов, претендующих на должность «digital hardware engineer» и в какой-то момент у него родилась идея сделать свой набор небольших лабораторных работ на языке SystemVerilog, чтобы использовать их, во-первых, на «собесе» для проверки знаний, а во-вторых — для повышения квалификации своих коллег из смежных ведомств. Этот набор лабораторных работ называется «basiсs-graphics-music» и он свободно доступен в репозитории Юрия на Github-е по ссылке: https://github.com/yuri-panchul/basics-graphics-music. Этот же набор лабораторных работ активно используется в «Школе синтеза».

Сам проект «basics-graphics-music» устроен так, что позволяет его использовать с большим спектром тулов (Quartus, Vivado, Gowin EDA), а также с большим количеством отладочных и учебных плат, содержащих микросхемы ПЛИС, и он по праву может называться первым портабельным (portable) репозиторием обучающих примеров для программирования ПЛИС. Для поддержки проект имеется список рассылки: portable-hdl-examples@googlegroups.com.

Еще из интересных особенностей данного сборника лабораторных работ можно отметить их идеологическую выверенность стиля кода и последовательность подачи материала. Лабораторные работы начинаются с демонстрации самых базовых принципов комбинационной логики (правила де Моргана) и описания машин-состояния (FSM) и доходят до весьма сложных (но небольших по объёму кода) примеров работы с VGA графикой, синтезированием и детектированием музыки.

Недавно в проект была добавлена поддержка тулчейна Yosys для нескольких плат с микросхемами ПЛИС Lattice и Gowin — работа, к которой я приложил свою руку.

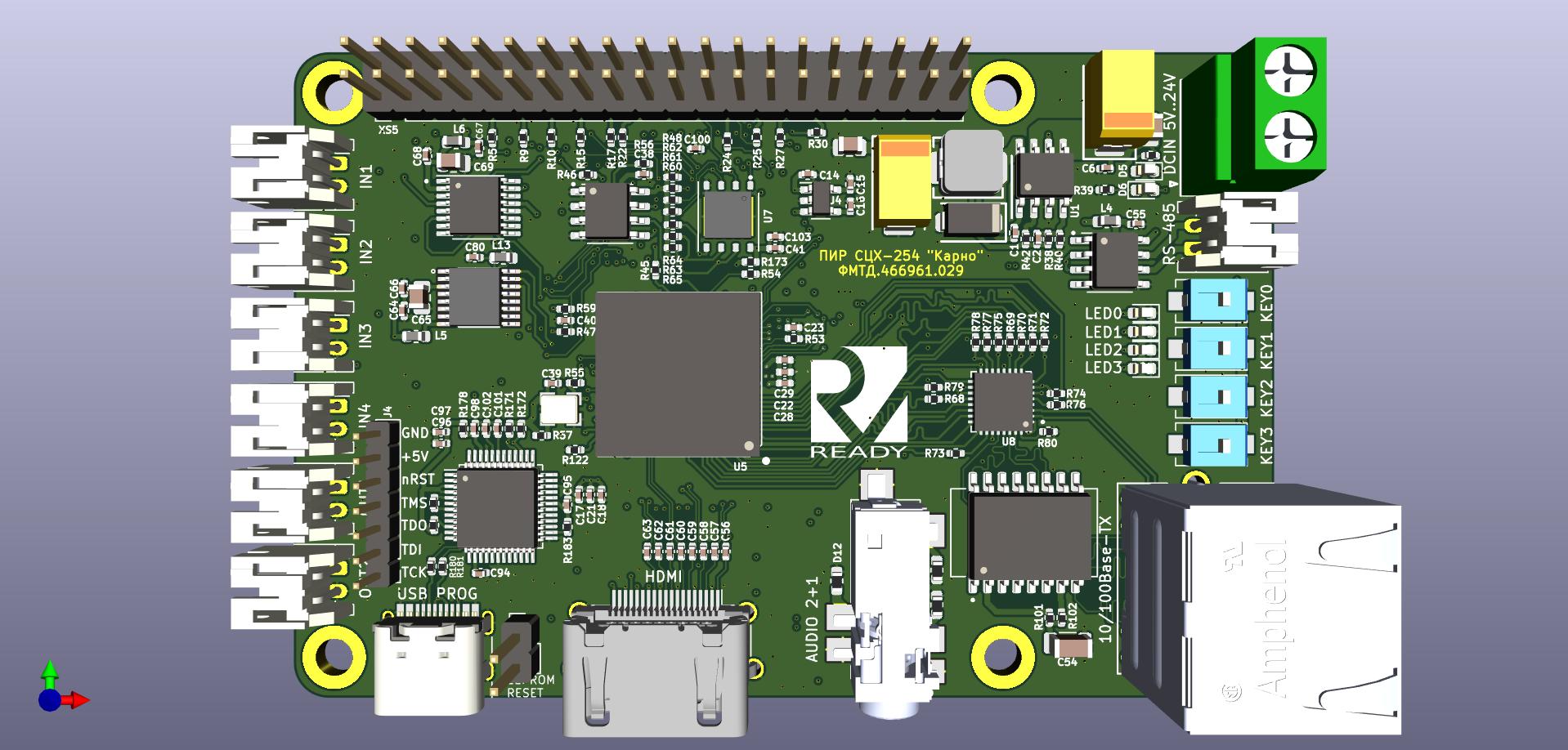

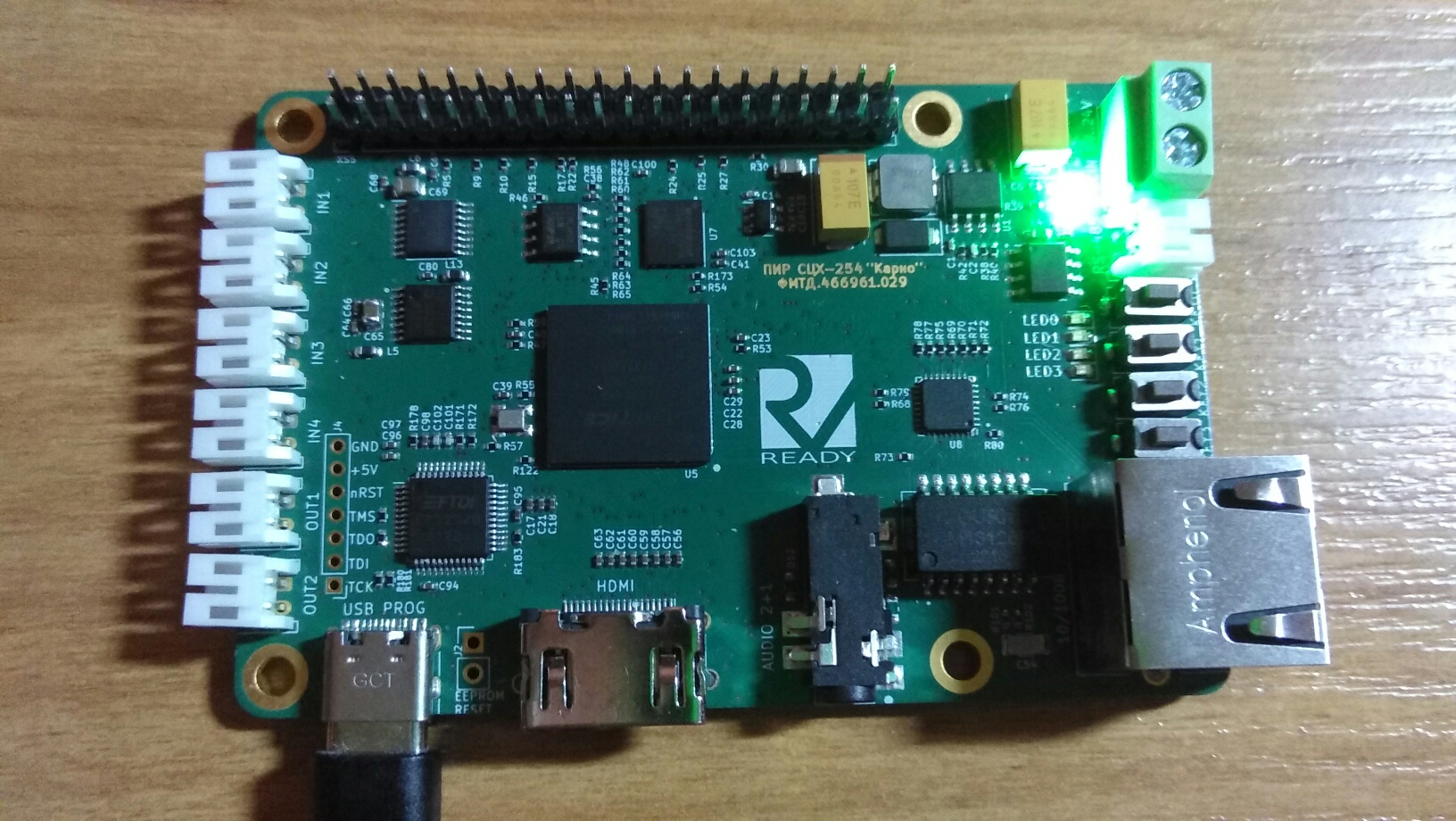

Среди множества отладочных плат, поддерживаемых проектом «basics-graphics-music» присутствует, в том числе, разработанная мной и моими коллегами из ООО «Фабмикро» плата «ПИР СЦХ-254 Карно» («Karnaugh Interactive Extendable ASIC Simulation Board») предназначенная для обучения азам цифрового синтеза и экспериментов с синтезируемыми микропроцессорными ядрами RISC-V.

Это полностью «open source and open hardware» проект на базе ПЛИС Lattice ECP5 с ~25К логических блоков, содержит ряд интересных периферийных устройств: многоканальный ЦАП и АЦП, блок статической SRAM памяти объемом 512КБ, FastEthernet, HDMI, кнопки и светодиоды и кое-что еще. Плата «Карно» имеет встроенный JTAG программатор.

Плата выполнена в САПР KiCAD 7 и весь проект со схемой, трассировкой платы и Gerber файлами, доступен для скачивания с Github-а по ссылке: https://github.com/Fabmicro-LLC/Karnix_ASB-254 . Для демонстрации возможностей платы «Карно» я записал и выложил на YouTube новогоднее видео ссылка на которе дана в начале этой стетьи.

Далее я буду приводить примеры работы с тулчейном Yosys с её участием. Но как я отмечал выше, выбор платы не сильно принципиален, так как проектом «basics-graphics-music» поддерживаются ряд других, легко доступных отладочных плат, среди которых можно отметить OrangeCrab и TangNano-9K.

7.1. Установка и настройка «basics-graphics-music»

Итак, приступим к рассмотрению нескольких лабораторных работ. Клонируем репозиторий «basics-graphics-music» в любой удобный рабочий подкаталог:

rz@devbox:~$ git clone https://github.com/yuri-panchul/basics-graphics-music.git

Cloning into 'basics-graphics-music'...

rz@devbox:~$ cd basics-graphics-music

rz@devbox:~/basics-graphics-music$Произведем настройку среды синтеза для нашей платы, для этого запустим скрипт check_setup_and_choose_fpga_board.bash следующим образом:

rz@devbox:~/basics-graphics-music$ bash check_setup_and_choose_fpga_board.bash

check_setup_and_choose_fpga_board.bash: The currently selected FPGA board: karnix_ecp5_yosys. Please select an FPGA board amoung the following supported:

1) alinx_ax4010 25) karnix_ecp5_yosys

2) arty_a7 26) nexys4

3) arty_a7_pmod_mic3 27) nexys4_ddr

4) basys3 28) nexys_a7

5) c5gx_audio 29) omdazz

6) c5gx_vga666 30) omdazz_pmod_mic3

7) c5gx_vga_pmod 31) orangecrab_ecp5_yosys

8) cmod_a7 32) piswords6

9) de0 33) qmtech_c4_starter

10) de0_cv 34) rzrd

11) de0_nano_soc_vga666 35) rzrd_pmod_mic3

12) de0_nano_soc_vga_pmod 36) saylinx

13) de0_nano_vga666 37) saylinx_pmod_mic3

14) de0_nano_vga_pmod 38) tang_nano_20k

15) de10_lite 39) tang_nano_9k

16) de10_lite_tm1638_arduino 40) tang_nano_9k_gowin_yosys

17) de10_nano_vga666 41) tang_primer_20k_dock

18) de10_nano_vga_mister 42) tang_primer_20k_dock_alt

19) de10_nano_vga_pmod 43) tang_primer_20k_dock_gowin_yosys

20) de1_soc 44) tang_primer_20k_lite

21) de2_115 45) zeowaa

22) dk_dev_3c120n 46) zeowaa_wo_dig_0

23) emooc_cc 47) zybo_z7

24) ice40hx8k_evb_yosys 48) exit

Your choice (a number): 25Выберем плату «karnix_ecp5_yosys», для этого введем её порядковый номер из списка (в данном случае — 25) и нажмем «ввод», скрипт продолжит выполнение и выдаст следующие сообщения:

check_setup_and_choose_fpga_board.bash: FPGA board selected: karnix_ecp5_yosys

check_setup_and_choose_fpga_board.bash: Created an FPGA board selection file: "/home/rz/basics-graphics-music/fpga_board_selection"

Would you like to create the new run directories for the synthesis of all labs in the package, based on your FPGA board selection? We recommend to do this if you plan to work with Quartus GUI rather than with the synthesis scripts. [y/n]Я нажму n, так как не использую Quartus. Скрип завершит работу с сообщением:

Configuring for Lattice ECP5...

OK

rz@devbox:~/basics-graphics-music$Настройка среды готова. Посмотрим какие лабораторные работы нам доступны:

rz@devbox:~/basics-graphics-music$ ls labs

01_and_or_not_xor_de_morgan 08_shift_register 15_uart 22_syst_ws

02_mux 09_7segment_word 16_round_robin_arbiter 23_i2s_synthesizer

03_decoder 10_hex_counter 17_geiger_muller_radiation_counter 24_i2s_music

04_priority_encoder 11_note_recognition 18_pow5_single_cycle 50_crash_course

05_7seven_segment_letter 12_snail_fsm 19_pow5_pipelined 90_valid_ready_etc_preview

06_vga 13_music_recognition 20_pow5_pipelined_valid 91_systemverilog_homework_preview

07_binary_counter 14_game 21_pow5_pipelined_valid_solution common 7.2 Лабораторная работа «01_and_or_not_xor_de_morgan»

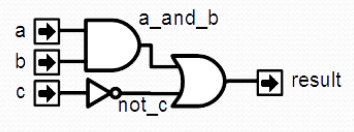

Данная лабораторная работа показывает, как выглядят цифровые схемы, построенные только на комбинационной логике, выраженной на языке SystemVerilog.

Комбинационные схемы — это асинхронные (нетактируемые) схемы состоящие только из логических элементов, таких как «И», «ИЛИ», «НЕ», «исключающее ИЛИ» и т. д. Такие схемы подчиняются законам булевой алгебры, в том числе поддаются различным преобразованиям и упрощениям, к ним применимы правила де Моргана.

Зайдем в каталог с лабораторной работой и посмотрим, что нам предлагается:

rz@devbox:~/basics-graphics-music$ cd labs/01_and_or_not_xor_de_morgan

rz@devbox:~/basics-graphics-music/labs/01_and_or_not_xor_de_morgan$ ls -l

-rwxrwxr-x 1 rz rz 495 Jan 5 22:39 01_clean.bash

-rwxrwxr-x 1 rz rz 495 Jan 5 22:39 02_simulate_rtl.bash

-rwxrwxr-x 1 rz rz 495 Jan 5 22:39 03_synthesize_for_fpga.bash

-rwxrwxr-x 1 rz rz 495 Jan 5 22:39 04_configure_fpga.bash

-rwxrwxr-x 1 rz rz 495 Jan 5 22:39 05_run_gui_for_fpga_synthesis.bash

-rwxrwxr-x 1 rz rz 495 Jan 5 22:39 06_choose_another_fpga_board.bash

-rwxrwxr-x 1 rz rz 495 Jan 5 22:39 07_synthesize_for_asic.bash

-rwxrwxr-x 1 rz rz 495 Jan 5 22:39 08_visualize_asic_synthesis_results_1.bash

-rwxrwxr-x 1 rz rz 495 Jan 5 22:39 09_visualize_asic_synthesis_results_2.bash

drwxrwxr-x 2 rz rz 4096 Jan 11 22:54 run

-rw-rw-r-- 1 rz rz 1142 Jan 5 22:39 tb.sv

-rw-rw-r-- 1 rz rz 2614 Jan 5 22:39 top.sv Каждый каталог с лабораторной работой содержит файлы: top.sv и tb.sv (расширение .sv означает текст на SystemVerilog), а также стандартный набор bash скриптов для выполнения операций синтеза (для ПЛИС и ASIC), запуска среды IDE и визуализации результатов. Далее я продемонстрирую только процесс синтеза и загрузки в ПЛИС. Но прежде давайте заглянем в top.sv.

rz@devbox:~/basics-graphics-music/labs/01_and_or_not_xor_de_morgan$ cat top.sv В самом начале файла мы видим описание интерфейса модуля top, который предоставляет нам окно во внешний мир — доступ к устройствам на плате, среди которых массив светодиодов, массив кнопок, порт UART и ряд других. Интерфейс модуля top общий для всех лабораторных работ в этом проекте, но отдельные примеры (лабы) могут использовать только часть предоставляемых возможностей.

`include "config.svh"

module top

# (

parameter clk_mhz = 50,

w_key = 4,

w_sw = 8,

w_led = 8,

w_digit = 8,

w_gpio = 100

)

(

input clk,

input slow_clk,

input rst,

// Keys, switches, LEDs

input [w_key - 1:0] key,

input [w_sw - 1:0] sw,

output logic [w_led - 1:0] led,

// A dynamic seven-segment display

output logic [ 7:0] abcdefgh,

output logic [w_digit - 1:0] digit,

// VGA

output logic vsync,

output logic hsync,

output logic [ 3:0] red,

output logic [ 3:0] green,

output logic [ 3:0] blue,

input uart_rx,

output uart_tx,

input mic_ready,

input [ 23:0] mic,

output [ 15:0] sound,

// General-purpose Input/Output

inout [w_gpio - 1:0] gpio

); Далее следует установка значений по умолчанию для всех внешних сигналов, не используемых в данном примере:

// assign led = '0;

assign abcdefgh = '0;

assign digit = '0;

assign vsync = '0;

assign hsync = '0;

assign red = '0;

assign green = '0;

assign blue = '0;

assign sound = '0;