Идея waferscale-процессоров наделала много шума в 80-х годах прошлого века, но оказалась забытой на десятилетия из-за сложности производства. Сегодня технологию вновь пытаются развивать. Рассказываем, кто работает в этой области.

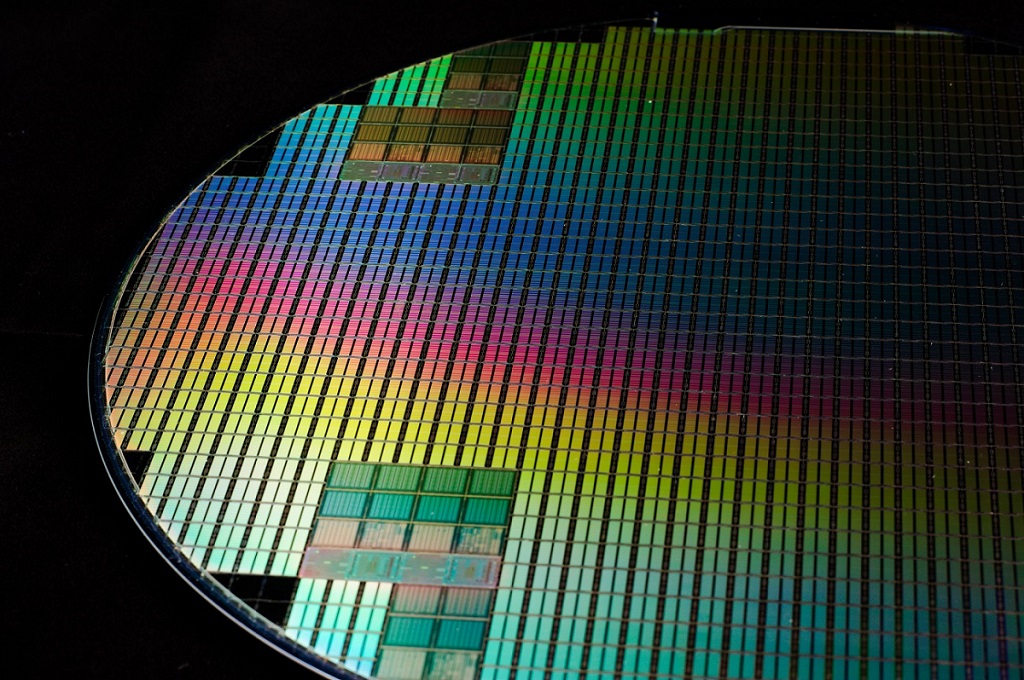

/ фото timo vn CC BY

При производстве современных процессоров кремниевая подложка распиливается на индивидуальные кристаллы, из которых потом собирается чип. Технология waferscale (WSI) подразумевает создание процессоров (как CPU, так и GPU) на единой полупроводниковой пластине — она становится одним большим «чипом». Такой подход увеличивает производительность системы: компоненты размещаются ближе, поэтому данные передаются быстрее.

В 1970-х и 1980-х годах технологию WSI предлагали использовать для создания чипов для суперкомпьютеров. Однако от этой идеи было решено отказаться — при производстве в чипах возникало слишком много дефектов.

Только недавно о WSI снова заговорили как о перспективном направлении. К примеру, ожидается, что такие устройства помогут повысить производительность ИТ-инфраструктуры в дата-центрах. Интерфейсы для передачи данных между компонентами сервера часто оказываются «бутылочным горлышком». Waferscale-системы, за счет размещения части компонентов на одной подложке, могут помочь решить проблему пропускной способности.

Организациями, развивающими waterscale-процессоры сегодня, являются Калифорнийский университет в Лос-Анджелесе и Иллинойсский университет в Урбане-Шампейне. В начале февраля этого года сотрудники вузов предложили создать систему, которая объединит на одной кремниевой десятки графических процессоров. Проект получил название Silicon Interconnect Fabric, или Si-IF.

Инженерам удалось создать два прототипа на 24 и на 40 GPU. Разработчики провели сравнительные тесты с классическими устройствами (с аналогичным числом вычислительных модулей) — производительность Si-IF-устройств оказалась выше в 2,5–5 раз. Потенциально технология может ускорить работу серверов на базе графических процессоров в дата-центрах.

Waferscale-процессорами с 2012 года занимается и тайваньский производитель TSMC. Их технология называется CoWoS — «чип на пластине на подложке». На кремниевом мосту (interposer) размещаются GPU и память, FPGA и память или сетевые контроллеры. Затем мост устанавливается на монтажную плату и «упаковывается» как обычный процессор. Решение уже используется в реальных устройствах, например графических чипах Nvidia серии Volta.

Также разработкой технологии занимаются инженеры в рамках проекта WIPE, который входит в европейскую инициативу по созданию инновационных решений Horizon 2020. В составе WIPE семь участников, среди которых — IBM, бельгийский центр микроэлектроники iMinds и ряд исследовательских институтов.

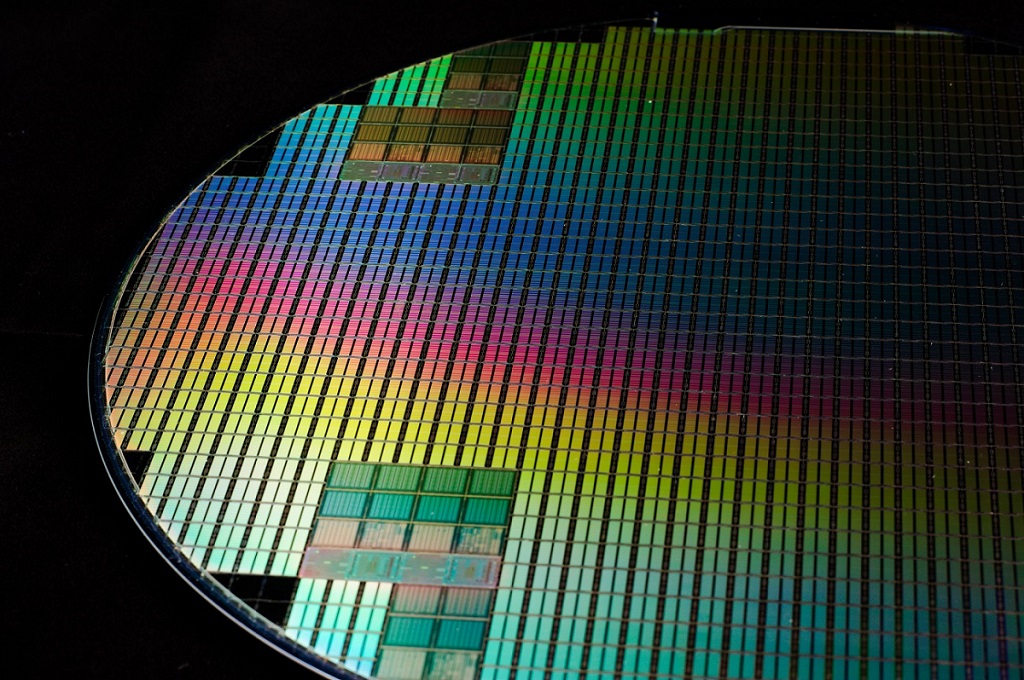

/ фото Enrique Jimenez CC BY-SA

Организация предлагает создать процессор для работы с оптоволоконными сетями. В нем модуль для преобразования оптического сигнала в электрический будет расположен над кремниевой пластиной с чипами и связан с ней напрямую через металлические контакты. Исследователи ожидают, что такая архитектура будет потреблять меньше энергии и работать быстрее, чем традиционные системы с раздельными трансиверами и процессорами.

Эксперты ожидают, что развитие WSI-процессоров поможет дата-центрам увеличить мощность серверов для ресурсоемких задач, например обучения нейросетей. По некоторым данным, над waferscale-процессором для машинного обучения уже работает стартап Cerebras — хотя сама компания скрывает подробности разработки.

Ещё одно преимущество WSI — простота управления. Для операционных систем и других программ waferscale-устройства выглядят не как несколько отдельных процессоров, а, например, как один большой GPU. Это упрощает работу программистов и системных администраторов, которым не нужно по отдельности настраивать каждый модуль waferscale-системы.

Но у waferscale-процессоров есть и ограничение, которое делает сложным масштабирование ИТ-инфраструктуры. Системы питания в WSI-чипах требуют установки регуляторов напряжения. Эти блоки занимают место, на котором можно было бы разместить дополнительные вычислительные модули. Ещё одно ограничение для waferscale-процессоров связано с охлаждением устройств. Высокая плотность модулей на чипе усложняет отведение тепла.

Но по мнению специалистов, эти проблемы преодолимы и сейчас для возрождения WSI настало подходящее время. С 1980-х технологии производства процессоров стали более совершенными, количество дефектов сократилось. Поэтому можно ожидать, что в ближайшее время будет появляться все больше проектов, посвященных разработке waferscale-устройств.

О чем мы пишем в корпоративном блоге:

И в Telegram-канале:

/ фото timo vn CC BY

Что такое waferscale

При производстве современных процессоров кремниевая подложка распиливается на индивидуальные кристаллы, из которых потом собирается чип. Технология waferscale (WSI) подразумевает создание процессоров (как CPU, так и GPU) на единой полупроводниковой пластине — она становится одним большим «чипом». Такой подход увеличивает производительность системы: компоненты размещаются ближе, поэтому данные передаются быстрее.

В 1970-х и 1980-х годах технологию WSI предлагали использовать для создания чипов для суперкомпьютеров. Однако от этой идеи было решено отказаться — при производстве в чипах возникало слишком много дефектов.

Например, в этой сфере работал стартап Trilogy Systems, который тогда стал самым финансируемым в Кремниевой долине — он получил $230 млн инвестиций. Но компании так и не удалось сформировать надежный техпроцесс. В 1985 году Trilogy прекратила исследования в области WSI и обанкротилась, что отрицательно сказалось на репутации waferscale-процессоров в целом.

Только недавно о WSI снова заговорили как о перспективном направлении. К примеру, ожидается, что такие устройства помогут повысить производительность ИТ-инфраструктуры в дата-центрах. Интерфейсы для передачи данных между компонентами сервера часто оказываются «бутылочным горлышком». Waferscale-системы, за счет размещения части компонентов на одной подложке, могут помочь решить проблему пропускной способности.

Кто развивает технологию

Организациями, развивающими waterscale-процессоры сегодня, являются Калифорнийский университет в Лос-Анджелесе и Иллинойсский университет в Урбане-Шампейне. В начале февраля этого года сотрудники вузов предложили создать систему, которая объединит на одной кремниевой десятки графических процессоров. Проект получил название Silicon Interconnect Fabric, или Si-IF.

Инженерам удалось создать два прототипа на 24 и на 40 GPU. Разработчики провели сравнительные тесты с классическими устройствами (с аналогичным числом вычислительных модулей) — производительность Si-IF-устройств оказалась выше в 2,5–5 раз. Потенциально технология может ускорить работу серверов на базе графических процессоров в дата-центрах.

Waferscale-процессорами с 2012 года занимается и тайваньский производитель TSMC. Их технология называется CoWoS — «чип на пластине на подложке». На кремниевом мосту (interposer) размещаются GPU и память, FPGA и память или сетевые контроллеры. Затем мост устанавливается на монтажную плату и «упаковывается» как обычный процессор. Решение уже используется в реальных устройствах, например графических чипах Nvidia серии Volta.

Также разработкой технологии занимаются инженеры в рамках проекта WIPE, который входит в европейскую инициативу по созданию инновационных решений Horizon 2020. В составе WIPE семь участников, среди которых — IBM, бельгийский центр микроэлектроники iMinds и ряд исследовательских институтов.

/ фото Enrique Jimenez CC BY-SA

Организация предлагает создать процессор для работы с оптоволоконными сетями. В нем модуль для преобразования оптического сигнала в электрический будет расположен над кремниевой пластиной с чипами и связан с ней напрямую через металлические контакты. Исследователи ожидают, что такая архитектура будет потреблять меньше энергии и работать быстрее, чем традиционные системы с раздельными трансиверами и процессорами.

Каковы перспективы

Эксперты ожидают, что развитие WSI-процессоров поможет дата-центрам увеличить мощность серверов для ресурсоемких задач, например обучения нейросетей. По некоторым данным, над waferscale-процессором для машинного обучения уже работает стартап Cerebras — хотя сама компания скрывает подробности разработки.

Ещё одно преимущество WSI — простота управления. Для операционных систем и других программ waferscale-устройства выглядят не как несколько отдельных процессоров, а, например, как один большой GPU. Это упрощает работу программистов и системных администраторов, которым не нужно по отдельности настраивать каждый модуль waferscale-системы.

Но у waferscale-процессоров есть и ограничение, которое делает сложным масштабирование ИТ-инфраструктуры. Системы питания в WSI-чипах требуют установки регуляторов напряжения. Эти блоки занимают место, на котором можно было бы разместить дополнительные вычислительные модули. Ещё одно ограничение для waferscale-процессоров связано с охлаждением устройств. Высокая плотность модулей на чипе усложняет отведение тепла.

Но по мнению специалистов, эти проблемы преодолимы и сейчас для возрождения WSI настало подходящее время. С 1980-х технологии производства процессоров стали более совершенными, количество дефектов сократилось. Поэтому можно ожидать, что в ближайшее время будет появляться все больше проектов, посвященных разработке waferscale-устройств.

О чем мы пишем в корпоративном блоге:

- Как IaaS помогает развивать бизнес: три задачи, которые решит облако

- Что скрывается за термином vCloud Director – взгляд изнутри

- Распределенный брандмауэр в vCloud Director 8.20: особенности решения

И в Telegram-канале:

SergeyMax

AN3333

Спасибо. Я тот самый тоже.

CorneliusAgrippa

Насколько я понял, от технологии «прибор размером с пластину» давно отказались. То, что делает TSMC — это отдельные чипы, которые производятся по классической технологии (разрезая пластину на чипы), которые сажаются на интерпозер, который тоже не с пластину размером, потом все это корпусируется. Смысл не в том, чтобы сделать процессор размером с пластину, а в том, чтобы уменшить расстояние с десятков миллиметров между микросхемами на обычной печатной плате до десятков микрон на интерпозере, что уменьшит время распространения сигнала, уменьшит потери и т.д.

AntonSor

Скорее всего, будут делать однородную сеть, а дефектные чипы можно будет отключать после тестирования. А как тепло отводить?

Marwin

ну отвести жар на огромный радиатор можно и водой, если не гнать ядра выше 3ГГц, то сильно греться-то не будет. Больше интересно как эту вундервафлю питать ))

Dorogonov_DA

А если запитывать «вычислительный модуль» посредством электромагнитной индукции? Вытравить прямо на кристалле для каждого процессора свою катушку, и наводить ЭДС внешним переменным магнитным полем на всех процессорах сразу?

VJean

И подводить к каждому модулю по ядерному реактору.

saege5b

Что бы запитать такую штуку, надо Ампер 500-1000. Если не гнаться за попугаями.

И первые десятки килоАмпер, в случае супер-пупер.

Я слабо представляю агрегат. По крайней мере, компактностью оно отличаться не будет.

Dorogonov_DA

Тогда — разрабатывать топологию так, чтобы питание на кристаллы подавалось сверху и снизу пластины, и накрывать её двумя "блинами", припаивая их на сплав Розе — заодно решится и проблема теплоотвода. Правда, в случае пробоя — знатно жахнет.

fshp

Современные чипы держат температуру до 105 градусов. Пластина будет плавать в Розе.

doctorw

Как быть с наводками на вычислительные цепи?

Dorogonov_DA

Выполнить шины данных по технологии диффиренциальных пар. Заодно, можно реализовать состояния на шине -1, 0, +1, ну и логику сделать троичной, выиграв примерно 1/3 в производительности и плотности памяти по сравнению с двоичной.

NetBUG

А смысл? Индуктивная связь имеет ограничения по напряжённости поля и его убыванию. Запитать вроде не так сложно, если достаточное число ножек вывести и пару слоёв чисто под это выделить. На мой взгляд, с охлаждением будет сложнее

dfgwer

Будет прикольно, если окажется что, единственным способом сделать сильные ИИ окажется нейроморфная пластина такого размера. И у каждой пластины будет свой уникальный рисунок дефектов. Который запретит копировать ИИ.

Dorogonov_DA

И интеллектуальные способности и склонности ИИ будут зависеть от количества и типа дефектов. Чихнул кто-то в стерильной комнате, и вышла пластина не математик, а художник.

fshp

Главное что бы не рэпер.

Sadler

Какие-то несколько процентов дефектных нейронов никак не мешают копированию ИИ. В современных сетях специально используют dropout-слои так, что на отдельной итерации может не работать более половины нейросети, и сети не просто справляются с этими дефектами, а получаются более устойчивыми и меньше сваливаются в переобучение.

AN3333

Может быть не «кремниевая подложка распиливается на элементарные кристаллы», а кристалл распиливается?

Как думаете?

IgorPie

35 лет назад обанкротились, что помешает обанкротиться сейчас?

Skigh

Некоторый прогресс в отрасли полупроводниковых производств, нет?

IgorPie

Но электроны не стали двигаться быстрее, поэтому построить устойчивую систему будет не проще.

«Кластер» — штука не новая.

oracle_and_delphi

Зато дефектов на пластинах стало меньше, потому и количество брака тоже должно уменьшиться.

dfgwer

Сейчас можно больше времени тратить на R&D, прогресс сильно замедлился.

IgorPie

Но и денег это стоит значительно больших, а продажи не очень-то растут, т.к. процессоры сильно дешевеют, обороты — падают.

Singrana

Вот интересно, а как выглядит надежность? Как бы пластина большая, повредить ее не сложно. Да и хрупкое все это будет.