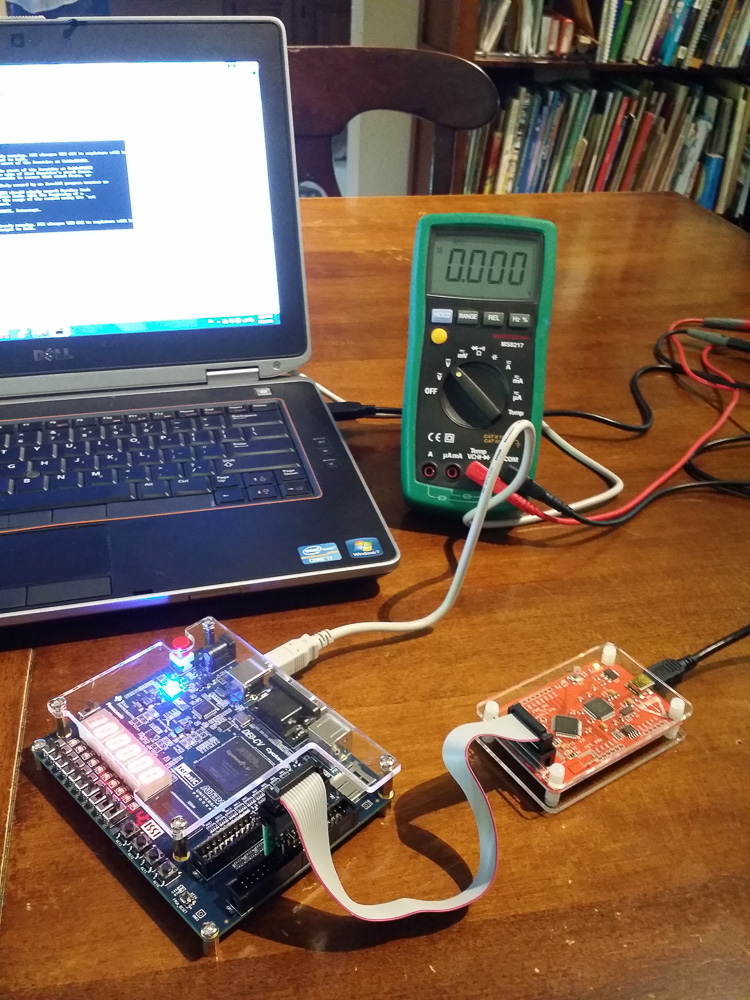

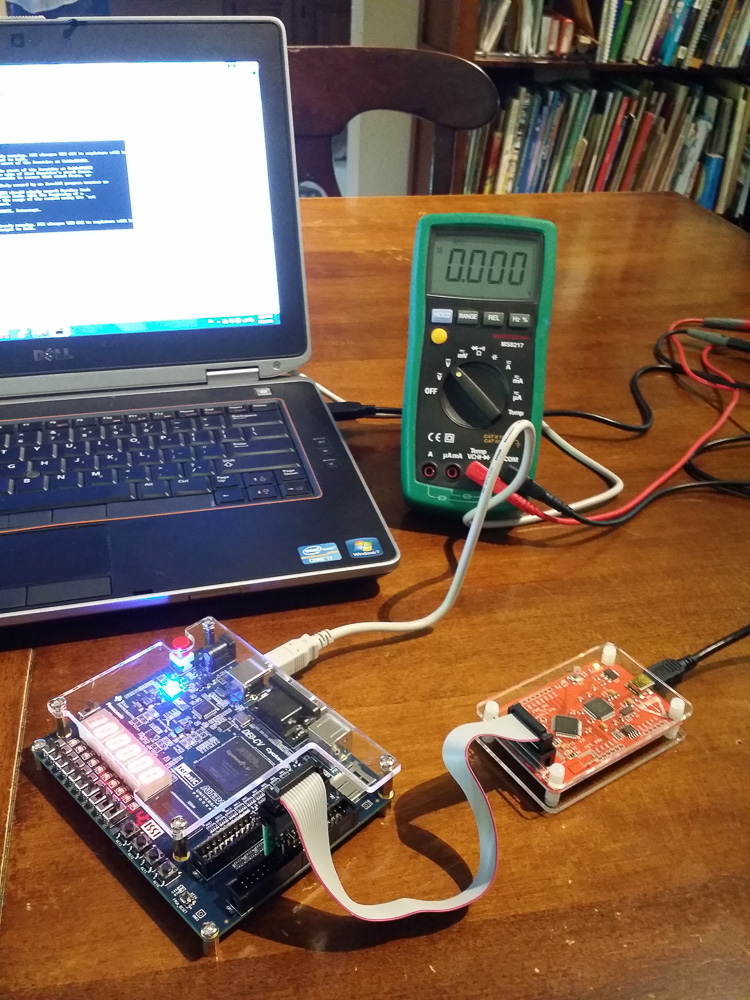

На днях мы вместе с Алексом и Владимиром (на фотке) спортировали MIPSfpga (пакет для введения в проектирование систем на кристалле) на плату Terasic DE0-CV с Altera Cyclone V FPGA. Эта плата — довольно хорошее решение для образовательного российского рынка, так как она дешевая ($150) и ее просто купить на сайте тайваньской компании Terasic, которая без лишней бюрократии доставляет платы в Россию. Мы попробуем использовать это на семинарах в МГУ, МИФИ, МИЭТ и ИТМО (см. в конце поста).

Процесс портировка включал создание проекта в Altera Quartus II с нужными параметрами, урезание размера памяти используемой внутри FPGA (в дальнейшем нужно просто использовать внешнюю память — она есть на плате), и подбор правильных выводов для соединения с платой отладочного адаптера BusBlaster. BusBlaster используется не для отладки хардвера, а для загрузки в память внутри системы и отладки, софтвера, работающего на процессорном ядре MIPS microAptiv UP в системе MIPSfpga. (MIPS microAptiv UP — это то же ядро, которое стоит внутри микроконтролера Microchip PIC32MZ, но с открытым кодом на Verilog)

Чтобы повторить это дома, вам прежде всего нужно скооперироваться с каким-либо университетом, так как Imagination Technologies лицензирует MIPSfpga бесплатно только университетам для образовательных и исследовательских целей. Заявку на MIPSfpga можно сделать на сайте образовательных программ Imagination Technologies:

community.imgtec.com/downloads/mipsfpga-getting-started-material-version-1-1

Далее вам нужно получить от Imagination Technologies отладочный адаптер BusBlaster или купить его на сайте www.seeedstudio.com/depot/Bus-Blaster-V3c-for-MIPS-Kit-p-2258.html

Наконец вам нужно иметь аккаунт на GitHub и присоединиться к организации github.com/MIPSfpga, после чего вы можете скачать код из директории github.com/MIPSfpga/boards/tree/master/de0_cv

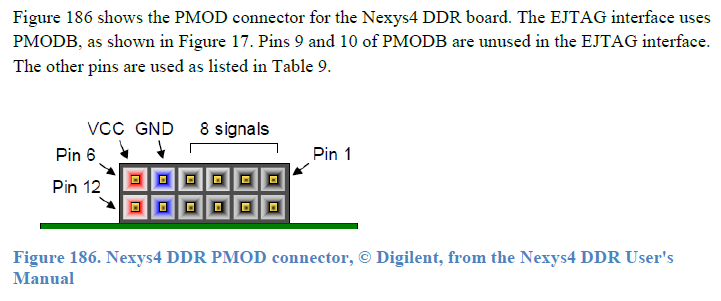

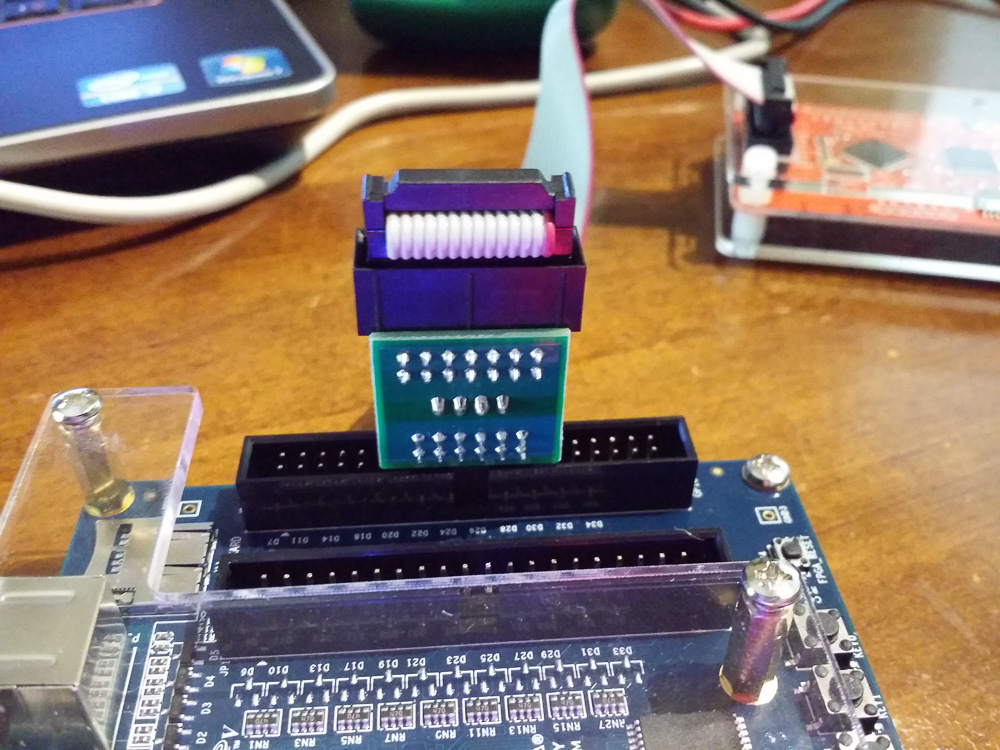

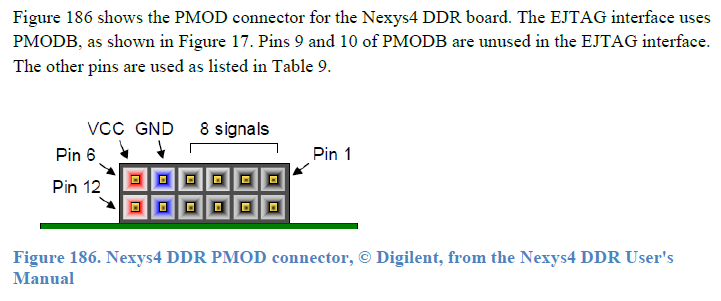

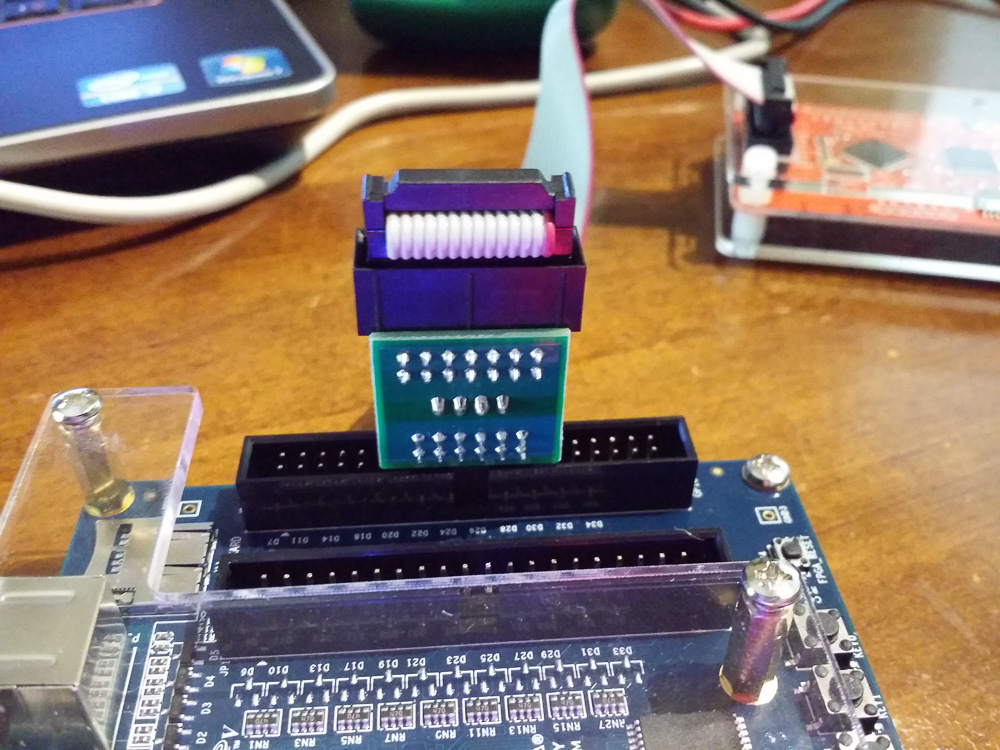

Пояснительные картинки про соединение выводов GPIO 1 платы Terasic DE0-CV и переходника для BusBlaster. Переходник создан изначально для соединения с платами Basys3, Nexys4 и Nexys4 DDR от digilentinc.com

Переходник пришлось ставить именно посередине, чтобы избежать нежелательного подключения питания и заземления.

Выход переходника который изначально предназначалься для соединения с платами от Digilent:

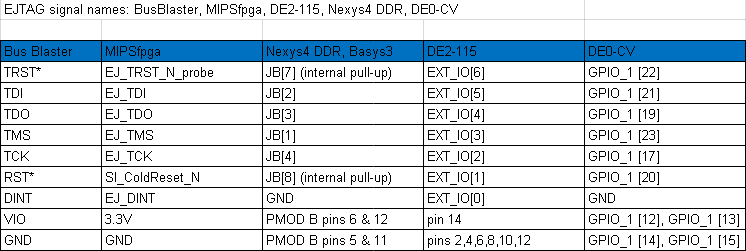

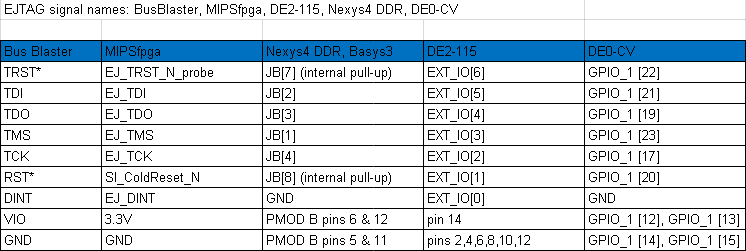

Табличка соединений:

Соединение:

Рекомендуемое соединение пробы BusBlaster с FPGA платой Terasic DE0-CV

Рекомендуемое соединение пробы BusBlaster с FPGA платой Terasic DE0-CV

Рекомендуемое соединение пробы BusBlaster с FPGA платой Terasic DE0-CV

Рекомендуемое соединение пробы BusBlaster с FPGA платой Terasic DE0-CV

Рекомендуемое соединение пробы BusBlaster с FPGA платой Terasic DE0-CV

Рекомендуемое соединение пробы BusBlaster с FPGA платой Terasic DE0-CV

Теперь в плату Altera Terasic DE0-CV можно загружать/конфигурировать харвер — систему MIPSfpga, и загружать в эту систему софтвер — программы для ядра MIPS microAptiv UP внутри системы.

Описание того, что можно сделать с такой системой — в посте про семинары по MIPSfpga, которые пройдут в МГУ, МИФИ, МИЭТ, ИТМО и Microchip Masters Russia этой осенью — см. habrahabr.ru/post/265045:

Процесс портировка включал создание проекта в Altera Quartus II с нужными параметрами, урезание размера памяти используемой внутри FPGA (в дальнейшем нужно просто использовать внешнюю память — она есть на плате), и подбор правильных выводов для соединения с платой отладочного адаптера BusBlaster. BusBlaster используется не для отладки хардвера, а для загрузки в память внутри системы и отладки, софтвера, работающего на процессорном ядре MIPS microAptiv UP в системе MIPSfpga. (MIPS microAptiv UP — это то же ядро, которое стоит внутри микроконтролера Microchip PIC32MZ, но с открытым кодом на Verilog)

Чтобы повторить это дома, вам прежде всего нужно скооперироваться с каким-либо университетом, так как Imagination Technologies лицензирует MIPSfpga бесплатно только университетам для образовательных и исследовательских целей. Заявку на MIPSfpga можно сделать на сайте образовательных программ Imagination Technologies:

community.imgtec.com/downloads/mipsfpga-getting-started-material-version-1-1

Далее вам нужно получить от Imagination Technologies отладочный адаптер BusBlaster или купить его на сайте www.seeedstudio.com/depot/Bus-Blaster-V3c-for-MIPS-Kit-p-2258.html

Наконец вам нужно иметь аккаунт на GitHub и присоединиться к организации github.com/MIPSfpga, после чего вы можете скачать код из директории github.com/MIPSfpga/boards/tree/master/de0_cv

Пояснительные картинки про соединение выводов GPIO 1 платы Terasic DE0-CV и переходника для BusBlaster. Переходник создан изначально для соединения с платами Basys3, Nexys4 и Nexys4 DDR от digilentinc.com

Переходник пришлось ставить именно посередине, чтобы избежать нежелательного подключения питания и заземления.

Выход переходника который изначально предназначалься для соединения с платами от Digilent:

Табличка соединений:

Соединение:

Рекомендуемое соединение пробы BusBlaster с FPGA платой Terasic DE0-CV

Рекомендуемое соединение пробы BusBlaster с FPGA платой Terasic DE0-CV Рекомендуемое соединение пробы BusBlaster с FPGA платой Terasic DE0-CV

Рекомендуемое соединение пробы BusBlaster с FPGA платой Terasic DE0-CV Рекомендуемое соединение пробы BusBlaster с FPGA платой Terasic DE0-CV

Рекомендуемое соединение пробы BusBlaster с FPGA платой Terasic DE0-CVТеперь в плату Altera Terasic DE0-CV можно загружать/конфигурировать харвер — систему MIPSfpga, и загружать в эту систему софтвер — программы для ядра MIPS microAptiv UP внутри системы.

Описание того, что можно сделать с такой системой — в посте про семинары по MIPSfpga, которые пройдут в МГУ, МИФИ, МИЭТ, ИТМО и Microchip Masters Russia этой осенью — см. habrahabr.ru/post/265045:

- Студенты могут строить свои собственные прототипы систем на кристалле, соединяя микропроцессорное ядро, память и спроектированные ими устройства ввода-вывода

- Внутренние регистры можно подсоединять к выходным портам и выводить наружу информацию о текущем состоянии процессорного конвейера, кэшей и устройства управления памятью. После этого процессор можно запустить на низкой тактовой частоте и наблюдать его работу «в замедленной съемке».

- Студенты могут экспериментировать со своими вариантами кэшей, проектировать многоядерные системы со специализированными сопроцессорами, эксперименторовать с разделением задачи на аппаратную и программную часть.

Deranged

Не очень ясно, зачем нужен внешний адаптер.

На DE0 (на всех) на борту есть ByteBlaster (он же USB Blaster). Это суть интерфейс USB-JTAG. Одним концом втыкается в порт USB (очевидно), второй конец уже разведен на аппаратный JTAG на самом FPGA. BusBlaster суть тоже самое. Зачем он нужен внешний USB-JTAG, если есть ByteBlaster?

Так же на борту есть флешка — EPCS64. FPGA теряет конфигурацию при потере питания, и загружает её из флеша на старте. Конфигурацию процессора нужно прошить в эту флешку. При прошивке из QUARTUS сначала ресетится FPGA, прямо в неё заливается конфигурация, которая делает из FPGA программатор, и по JTAG записывается файл конфигурации во флешку, после чего FPGA ресетится, и загружает конфигурацию уже из флешки. При этом совершенно никто не мешает во флешку записать такую конфигурацию, которая будет принимать и отправлять данные всё по тому же JTAG через набортный ByteBlaster.

Так же по поводу MIPS — вообще то в состав QUARTUS'а и так входит вполне себе штатный System Builder QSys, при помощи которого можно сконфигурировать SoC на ядре Altera NIOS II (32-bit RISC, софтпроцессор). «Медленная» реализация бесплатная. При этом не нужно шаманства с переходниками, JTAG-отладка работает «из-коробки» по ByteBlaster. Можно писать софт и отлаживаться из, например Eclipse, Keil, Atollic и т.д.

При этом, в квартусе софтпроцессор виден просто как блок, и к нему можно «дорисовать» любую периферию, какую захочется.

Сразу скажу, что я лично именно таким не занимался, но делал похожие вещи.

Вот отличная статья на тему: http://marsohod.org/index.php/projects/marsohod2/274-nios2.

VBKesha

>> Не очень ясно, зачем нужен внешний адаптер.

Если я правильно понял то MISPfpga это реализация MISP на FPGA(простите за тавтологию) именно как процессора, JTAG в нем получается тоже реализован «аппаратно» то есть он не имеет никакого отношения к JTAG от FPGA. ByteBlaster подключён к выходам JTAG выходам FPGA и поэтому до JTAG выходов реализованных в MISP FPGA получить не может(точней может но вот софт надо будет капитально доработать). Поэтому и используется отдельный JTAG адаптер

>> Так же по поводу MIPS — вообще то в состав QUARTUS'а и так входит вполне себе штатный System Builder QSys, при помощи которого можно сконфигурировать SoC на ядре Altera NIOS II (32-bit RISC, софтпроцессор). «Медленная» реализация бесплатная…

Только это проц привязан к FPGA Altera и при переходе на Xillinx или Actel или Atmel вы его использовать не сможете. А MIPSfpga не привязан к конкретному производителю FPGA, где нужно там можно и использовать.

YuriPanchul

О, вы за меня ответили! Спасибо

YuriPanchul

Nios привязан к Альтере, а вот в случае с MIPSfpga — это изначально ядро для ASIC-ов, т.е. если студент поиграется с системами на основе MIPSfpga на FPGA и придумает что-нибудь особо интересное, он потом может найти инвесторов, купить коммерческую лицензию на MIPS microAptiv UP и выпустить микросхему со своей системой на кристалле.