24-29 апреля в Киеве пройдет серия семинаров для школьников, которые не будут похожи на обычные классы со встроенными процессорами, которые стандартно используют Лего / Ардуино / Расберри Пай. Главный фокус семинаров — не научить программировать процессоры, а показать принципы, как процессоры проектируются внутри. Это как разница между «научить водить машину» и «научить проектировать двигатель». На семинарах школьники будут использовать язык описания аппарата Verilog и логический синтез — технологии, которые используют разработчики цифровых микросхем в Apple, Samsung и других электронных компаниях.

Главная официальная страница семинара, там же регистрация.

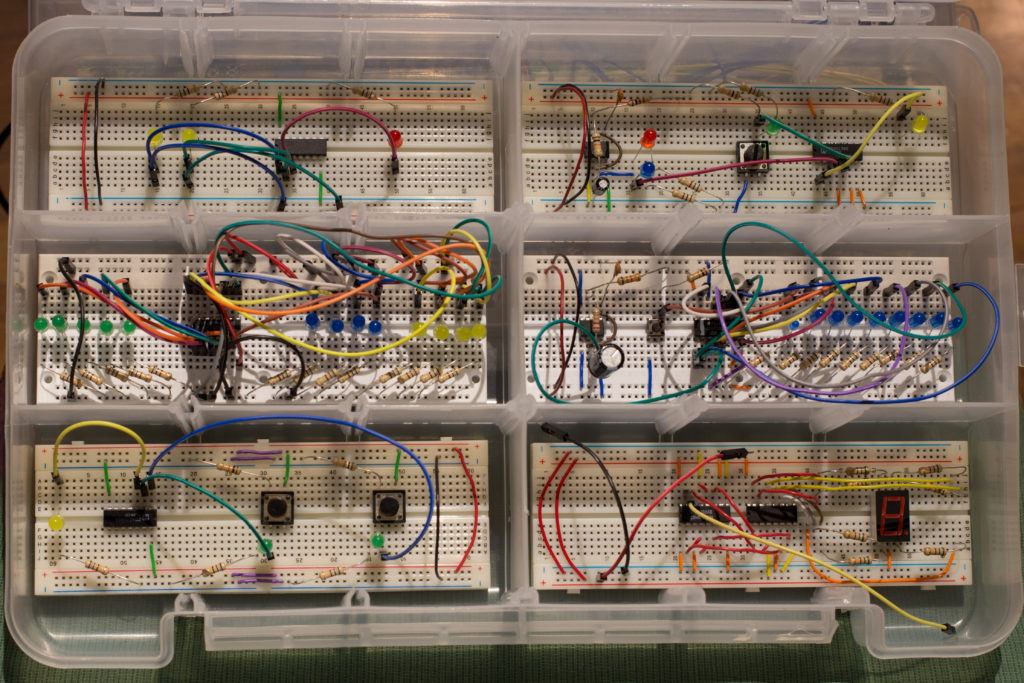

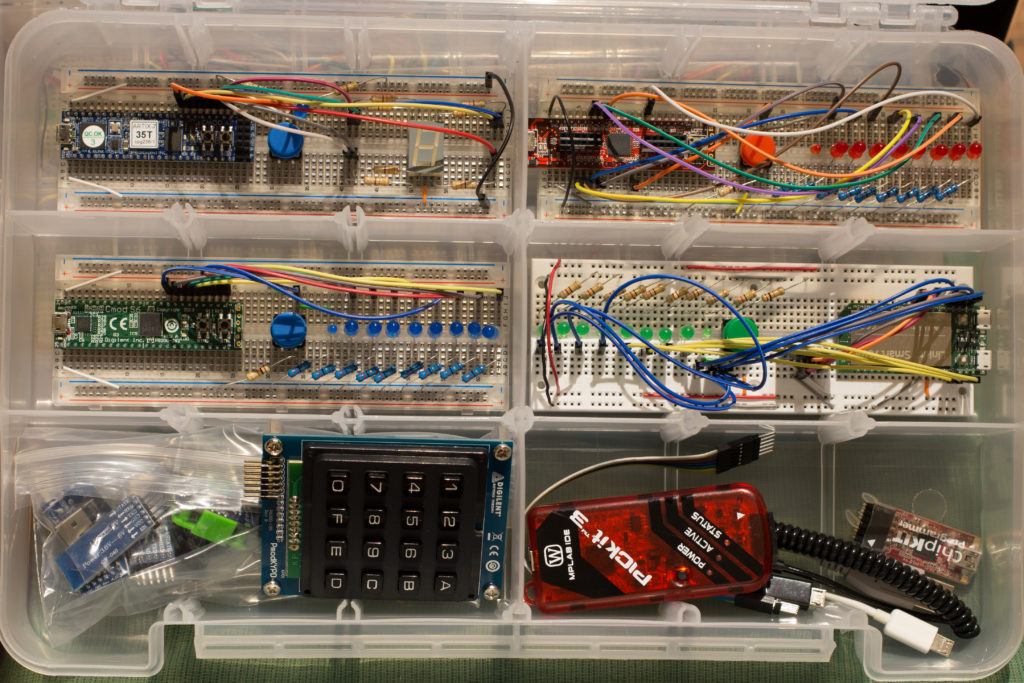

Для упражнений используются платы с ПЛИС — матрицами логических элементов с изменяемой функцией (это не обычный «процессор + память»). ПЛИС давно используются для обучения студентов проектированию электроники в Стэнфорде и МИТ, и более недавно — в российских и украинских вузах. Использование ПЛИС для обучения школьников — это эксперимент, и у вас есть шанс в нем поучаствовать. Для облегчения ввода в Verilog и ПЛИС мы сначала займемся упражнениями с микросхемами малой степени интеграции на безпаечных макетных платах. Затем мы займемся ПЛИС и в последний день семинаров сравним проектирования ПЛИС с программированием микропроцессора для интернета вещей.

Вы наконец увидите то, что происходит между транзистором и Ардуино, в область, куда школьники заглядывают редко!

Программа для старших школьников и младших студентов

Понедельник 24 апреля. Начинаем путь к ПЛИС: комбинационная логика и двоичная арифметика на микросхемах малого степени интеграции

Место: Студенческий пространство Belka КПИ

- 16:00-17:00 Александр Барабанов, КНУ. От физики к логике.

- Что такое ток, напряжение и сопротивление.

- Как устроена макетная плата.

- Упражнение 1. Первая схема с батарейкой, светодиодом и резистором. Зачем включать резистор в цепь со светодиодом.

- Что такое транзисторы и как из них строятся логические элементы.

- Упражнение 2. Наблюдаем работу транзистора.

- Что такое ток, напряжение и сопротивление.

- 17:00-18:00 Юрий Панчул, Imagination Technologies. Булева алгебра логики, логические элементы И-ИЛИ-НЕ.

- Упражнение 3. Каждому ученику выдается персональная микросхема логики серии CMOS 4000, с техническим описанием от производителя, с задачей нарисовать таблицу истинности, продемонстрировать ее работу и словесно описать функцию. Логические элементы AND, OR, XOR, NOR, NAND с различным числом входов.

- Упражнение 4. Изучаем, что такое подтягивающие резисторы и зачем они нужны. Добавляем к Упражнения 3 кнопки и подтягивающие резисторы.

- Упражнение 3. Каждому ученику выдается персональная микросхема логики серии CMOS 4000, с техническим описанием от производителя, с задачей нарисовать таблицу истинности, продемонстрировать ее работу и словесно описать функцию. Логические элементы AND, OR, XOR, NOR, NAND с различным числом входов.

- 18:00-19:00 Двоичная арифметика, сложения и умножения.

- Упражнение 5. Каждому ученику выдается сумматор CMOS 4008. Демонстрация работы сумматора на макетной плате.

- Упражнение 5. Каждому ученику выдается сумматор CMOS 4008. Демонстрация работы сумматора на макетной плате.

- 19:00-21:00 Дополнительные упражнения для тех, кто справился с упражнениями 1-5 и не хочет идти домой.

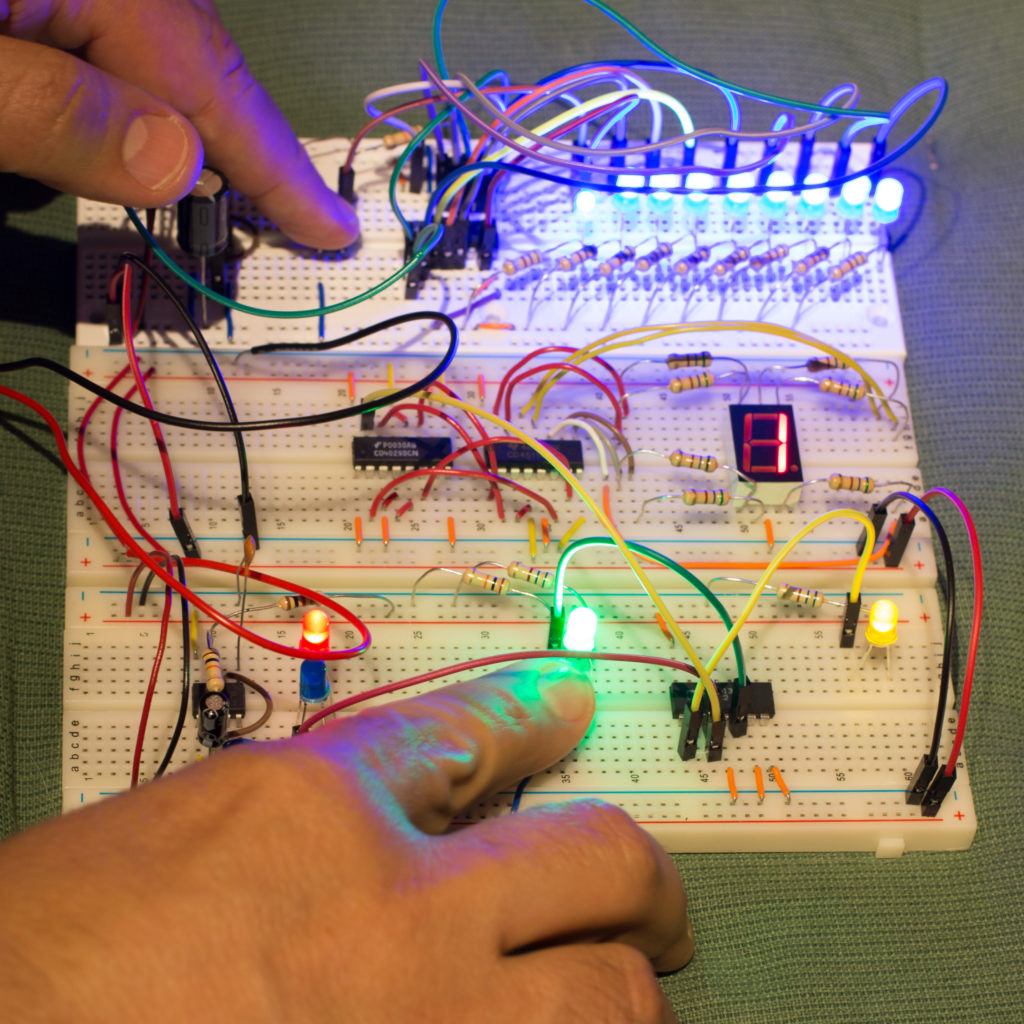

- Упражнение 6. Семисегментный индикатор и его драйвер, как пример комбинационной схемы. Вывод результата работы сумматора на семисегментный индикатор.

- Упражнение 6. Семисегментный индикатор и его драйвер, как пример комбинационной схемы. Вывод результата работы сумматора на семисегментный индикатор.

Вторник 25 апреля. Добавляем память: Последовательностная логика на микросхемах малой степени интеграции.

- 16:00-16: 30 Юрий Панчул. Последовательностная логика — это то, что делает компьютер «умным», она дает ему память и возможность повторять операции.

- 16: 30-17:00 Юрий Панчул и инструкторы по КПИ.

- Что такое D-триггер.

- Упражнение 7. Подсоединяем генератор тактового сигнала на основе 555 таймеру в D-триггера и исследуем работу составленной схемы.

- Что такое D-триггер.

- 17:00-19:00 Более сложные элементы последовательностной логики.

- Упражнение 8. Регистр сдвига и подвижные огоньки.

- Упражнение 9. Счетчик с выводом состояния на семисегментный индикатор.

- Упражнение 8. Регистр сдвига и подвижные огоньки.

- 19:00-21:00 Евгений Короткий, КПИ. Дополнительные упражнения для тех, кто справился с упражнениями 6-8 и не хочет идти домой.

- Упражнение 10. Исследуем генератор тактового сигнала на основе микросхемы 555 таймеру. Наблюдаем, как меняется период тактовой частоты в зависимости от сопротивлений резисторов и емкости конденсатора.

- Упражнение 10. Исследуем генератор тактового сигнала на основе микросхемы 555 таймеру. Наблюдаем, как меняется период тактовой частоты в зависимости от сопротивлений резисторов и емкости конденсатора.

Среда 26 апреля. Комбинационная логика и двоичная арифметика на Verilog и ПЛИС.

Место: Студенческий пространство Belka КПИ.

- 16:00-16: 30 Юрий Панчул, а также инструкторы из КПИ, КНУ. Быстрое вступление в язык описания аппаратуры Verilog и использования логического синтеза для ПЛИС / FPGA. Рассматриваем только комбинационную логику.

- 16: 30-17:00 Инструкторы из КПИ, КНУ. Комбинационная логика на Verilog.

- Упражнение 11. Повторяем упражнение 2 (логические элементы) на ПЛИС с использованием платы Digilent CMOD A7 35T: Breadboardable Artix-7 FPGA Module.

- Упражнение 12. Выводим первые буквы своего имени и фамилии на семисегментный индикатор, переключаясь между ними с помощью кнопки.

- Упражнение 13. Повторяем Упражнение 3 (сумматор) на ПЛИС. Результат выводим на семисегментный индикатор.

- Упражнение 11. Повторяем упражнение 2 (логические элементы) на ПЛИС с использованием платы Digilent CMOD A7 35T: Breadboardable Artix-7 FPGA Module.

- 19:00-21:00. Дополнительные упражнения для тех, кто справился с упражнениями 9-11 и не хочет домой.

- Упражнение 14. Иерархия модулей. Построение мультиплексоров с подмодулей.

- Упражнение 15. Моделирование Verilog кода без ПЛИС. Создаем среду для проверки работы схемы, описанной в Verilog. Используем симулятор Icarus Verilog для моделирования и программу GTKWave для просмотра временных диаграмм.

- Упражнение 14. Иерархия модулей. Построение мультиплексоров с подмодулей.

Пример кода на языке описания аппаратуры Verilog, который транслируется (синтезируется) в схему:

module counter

(

input clock,

input reset_n,

output reg [31:0] count

);

always @(posedge clock or negedge reset_n)

begin

if (! reset_n)

count <= 32'b0;

else

count <= count + 32'b1;

end

endmodule

//----------------------------------------------------------------------------

module seven_segment_display_driver

(

input [3:0] number,

output reg [6:0] abcdefg

);

// a b c d e f g dp Буквы с картинки

// 7 6 4 2 1 9 10 5 Выводы 7-сегментного индикатора

// 7 6 5 4 3 2 1 Выводы сигнала pio в ПЛИС

// --a--

// | |

// f b

// | |

// --g--

// | |

// e c

// | |

// --d--

always @*

case (number)

4'h0: abcdefg = 7'b1111110;

4'h1: abcdefg = 7'b0110000;

4'h2: abcdefg = 7'b1101101;

4'h3: abcdefg = 7'b1111001;

4'h4: abcdefg = 7'b0110011;

4'h5: abcdefg = 7'b1011011;

4'h6: abcdefg = 7'b1011111;

4'h7: abcdefg = 7'b1110000;

4'h8: abcdefg = 7'b1111111;

4'h9: abcdefg = 7'b1111011;

4'ha: abcdefg = 7'b1110111;

4'hb: abcdefg = 7'b0011111;

4'hc: abcdefg = 7'b1001110;

4'hd: abcdefg = 7'b0111101;

4'he: abcdefg = 7'b1001111;

4'hf: abcdefg = 7'b1000111;

endcase

endmodule

//----------------------------------------------------------------------------

module top

(

input CLK, // Тактовый сигнал 12 MHz

inout [48:1] pio // GPIO, General-Purpose Input/Output

);

wire reset_n = ! pio [8];

wire [31:0] count;

counter counter_i

(

.clock ( CLK ),

.reset_n ( reset_n ),

.count ( count )

);

seven_segment_display_driver display_driver_i

(

.number ( count [26:23] ),

.abcdefg ( pio [ 7: 1] )

);

endmodule

Четверг 27 апреля. Последовательностная логика и конечные автоматы на Verilog и ПЛИС.

Место: Студенческий пространство Belka КПИ.

- 16:00-17:00. Юрий Панчул. Последовательностная логика на Verilog, конечные автоматы, концепция методологии RTL (уровень регистровых передач), задержки распространения сигналов и ограничения на процедуру синтеза цифровых схем, определение максимально возможной тактовой частоты работы цифровой схемы.

- 17:00-19:00. Инструкторы из КПИ, КНУ. Последовательностная логика на Verilog.

- Упражнение 16. Счетчик с выводом состояния на семисегментный индикатор. Реализация Упражнения 9 на ПЛИС.

- Упражнение 17. Регистр сдвига и подвижные огоньки. Реализация Упражнения 8 на ПЛИС.

- Упражнение 18. Генерация звуковых тонов различной частоты и их наложения.

- Упражнение 16. Счетчик с выводом состояния на семисегментный индикатор. Реализация Упражнения 9 на ПЛИС.

- 19:00-21:00. Дополнительные упражнения для тех, кто справился с упражнениями 17-18 и хочет работать дальше.

- Упражнение 19. «Улитка улыбается»: пример конечного автомата.

- Упражнение 20. Строим арифметический конвейер. Используем симулятор Icarus Verilog для налаживания работы последовательностных схем.

- Упражнение 19. «Улитка улыбается»: пример конечного автомата.

Пятница 28 апреля. Сравнение проектирования схем с программированием встроенных микропроцессоров.

Место: Студенческий пространство Belka КПИ.

- 16:00-16: 30. Юрий Панчул. Чем программирования отличается от схемотехники. Машина фон Неймана — особый случай электронной схемы. Программы, как цепочки инструкций для машины фон Неймана. Обзор микропроцессорного ядра, используемого в MediaTek MT7688 и Microchip PIC32MZ.

- 16: 30-19:00 Евгений Короткий. Пример: платформа для Интернета Вещей LinkIt Smart 7688 на основе MediaTek MT7688.

- Упражнение 21. мигает светодиодом с помощью программы на Python.

- Упражнение 22. считывает данные с датчика освещенности Digilent PMOD ALS с помощью протокола SPI.

- Упражнение 23. Вступление в концепции прерываний.

- Упражнение 21. мигает светодиодом с помощью программы на Python.

- 19:00-21:00. Дополнительные упражнения для тех, кто справился с упражнениями на LinkIt Smart 7688 и хочет продолжать работу. Пример: Microchip PIC32 микроконтроллер.

- Упражнение 24. мигает светодиодом с помощью программы на языке Си.

- Упражнение 25. считывает данные с датчика освещенности Digilent PMOD ALS с помощью протокола SPI.

- Упражнение 26. Разгружаем основную программу, используя прерывания. Прерывания от таймера запускает SPI транзакцию, прерывания от SPI сигнализирует о получении пакета.

- Упражнение 24. мигает светодиодом с помощью программы на языке Си.

Cуббота 29 апреля. Хакатон

Место: Национальный университет «Киево-Могилянская академия»

- Проекты с микросхемами малого степени интеграции: «Детектор влажности почвы», «Полицейская сирена»

- Проекты с ПЛИС: интерфейсы для сенсоров, конечные автоматы типа «кодовый замок»

- Проекты с микроконтроллерами и встроенные микропроцессоры для Интернета Вещей: соединение с сенсорами и актуаторами

Программа для младших школьников

Апрельский интенсив «Введение в электроники»

Понедельник 24 апреля.Знакомство с основами: закон Ома, пассивные электронные элементы (резисторы и конденсаторы)

Место проведения:офис ООО «Радиомаг Украина», Чоколовский бульвар, 42-А

Время:17:00-19:00

Лектор:Сергей Ченаш

- Что такое ток, напряжение и сопротивление, закон Ома

- Как устроена макетная плата

- Как работать с мультиметром

- Резисторы и их применение

- Конденсатор как накопитель электрического заряда и его применение

Вторник 25 апреля.Активные электронные компоненты: строение и принципы работы диодов и транзисторов

Место проведения:офис ООО «Радиомаг Украина», Чоколовский бульвар, 42-А

Время:17:00-19:00

Лектор:Сергей Ченаш

- Характеристики полупроводников, строение p-n-перехода

- Как работают диоды и их классификация

- Принципы работы транзисторов и их применение

Четверг 27 апреля.Исследования элементов оптоэлектроники: светодиоды, фоторезисторы, фототранзисторы, оптопары

Место проведения:офис ООО «Радиомаг Украина», Чоколовский бульвар, 42-А

Время:17:00-19:00

Лектор:Сергей Ченаш

- Элементы оптоэлектроники, принципы работы и применение

Пятница 28 апреля.Знакомство с микросхемой NE555

Место проведения:офис ООО «Радиомаг Украина», Чоколовский бульвар, 42-А

Время:17:00-19:00

Лектор:Сергей Ченаш

- Что такое микросхемы и их классификации

- Типы сигналов в электронике

- Знакомство с микросхемой NE555, создание генератора

- Работа с осциллографом

Суббота 29 апреля.Бонусное занятия по пайке

Место проведения:офис ООО «Радиомаг Украина», Чоколовский бульвар, 42-А

Время:11:00-12: 30

До встречи на семинарах!

- Открытая лаборатория электроники Lampa и Студенческое пространство Belka, Национальный технический университет Украины «Киевский политехнический институт имени Игоря Сикорского»

- Киевский национальный университет имени Тараса Шевченко

- Национальный университет «Киево-Могилянская академия»

- Малая академия наук Украины

- ООО «Радиомаг Украины»

- Imagination Technologies

Главная официальная страница семинара, там же регистрация.

Комментарии (18)

crazyblu

19.04.2017 10:07Пятница 16:00-16:30 — поправьте название процессора MediaTek — там опечатка.

Leerooooy

19.04.2017 13:59+1Я теперь понимаю почему в наших странах такая «пятая точка». Люди организуют мероприятие, читают курсы, отвечают адекватное в комментариях, а их минусуют. Ассоциируется с 1917-м, когда пьяные революционные матросы кололи штыками интеллигенцию и прочих, кто умнее их самих.

Юрий, а теперь вопрос к вам — планируются ли подобные образовательные мероприятия в России? Хотя бы Питер или Москва? И планируется ли что-то большее чем просто вводный курс? Очень интересно было бы пообщаться о MIPS, их применение, посетить какие-то базовые занятия. Все таки не ARM-ом единым сыты)

YuriPanchul

19.04.2017 20:11-1В этом году будет мероприятие в Новосибирске:

http://school.iis.nsk.su/lshyup-2017/masterskie-6

Мастерская №1 «Мастерская архитекторов микросхем»

Мастер: Юрий Панчул

Цифровое железо, от логических элементов до собственного процессора

Хотите узнать, как проектируют микросхемы в современных устройствах — от телефона до космического корабля? Последние 25 лет это делают с помощью методологии логического синтеза кода на языках описания аппаратуры. Именно эту технологию мы выучим в нашей мастерской и применим для проектирования собственных устройств.

Мы начнем с трех ключевых кирпичиков цифровой электроники — логического элемента, тактового сигнала и D-триггера, памяти для одного бита информации. Для наглядности мы освоим их старомодным способом, соединяя проводами микросхемы малой степени интеграции на макетной плате.

Затем мы повторим построенные схемы на языке описания аппаратуры SystemVerilog и промоделируем их на программе-симуляторе. Но как мы можем воплотить их в микросхемы? Ведь заказ коммерческой микросхемы на фабрике очень дорогой? К счастью, существуют “перестраиваемые” программируемые логические интегральные схемы (ПЛИС), платы с которыми которые мы и будем использовать для наших занятий.

Помимо упражнений с арифметическими блоками и конечными автоматами, мы попробуем построить простой процессор, похожий по микроархитектуре на процессор Mongoose-V внутри космического корабля New Horizons, который год назад пролетел мимо Плутона.

Заодно мы изучим немного программирования на ассемблере, концепцию прерываний, сравним свой процессор с промышленными микроконтроллерами и встроенными микропроцессора, вплоть до микропроцессора EyeQ5 для самодвижущегося автомобиля, который планируется для выпуска в 2020 году.

И потом в Томске:

http://nanoandgiga.com/ngc2017/digital-design

Digital Design and Computer Architecture in the Era of System on Chip (SoC) and Internet of Things (IoT)

Chairs: Yuri Panchul and Stanislav Shidlovsky

For workshop program draft in Russian, click here.

The workshop will involve its participants in the task of building the educational infrastructure for the future of Russian microelectronics. The organizers will present the educational programs originated in Imagination Technologies (the company that designed PowerVR GPU inside Apple iPhone), Radeon Technology Group of Advanced Micro Devices, and University of California Santa Cruz Extension in Silicon Valley. The lectures will be structured to show the path from student projects and research activities to popular devices in consumer electronics, automotive and airspace industries. The participants will have an opportunity to experiment with prototyping system on chips using boards with Field Programmable Gate Arrays (FPGAs) during hands-on exercises. The subtopics of the workshop will include:

Setting up the basic education in digital design in a university using Nanometer ASIC program, with the focus on RTL-to-GDSII flow, the mainstream design methodology for the past 25 years;

Improving university curriculum in embedded microcontrollers with Connected MCU course that links the traditional microcontroller subjects with computer architecture and RTOSes;

Exploring topics for the research projects in processor microarchitecture and heterogeneous computing, using MIPSfpga industrial IP core and FPGA boards;

Path to productize the research prototypes of chips for Internet of Things (IoT) using Imagination Oberon platform and Europractice IC services;

Discussion of how the market shapes the offerings in licensable processor IP market using MIPS cores from Imagination Technology as examples;

Real cases of Russian microelectronic projects that use the discussed technologies, namely Baikal Electronics, ELVEES-NeoTek, MRI Progress and Lab Systems;

<

General-purpose computing meets graphic processors, what it means for high-performance software, VR, AR and AI applications

For sample slides of the workshop speaker, Charles Dancak, click here

For previous nanometer scale ASIC seminars information, click here

Presenters include:

Sergey Brazhnikov, Science and Technology Center, Zelenograd, Russia

Master-slice Semicustom VLSI Design Flow by Means of “Kovcheg” CAD: Introduction to SystemVerilog

Charles Dancak, University of California Santa Cruz, Santa Cruz, California, USA

The Nanoscale Application-Specific Integrated Circuit (ASIC) Development Process

Boris Ivashinnikov, Komsomolsk-na-Amure State Technical University, Komsomolsk-na Amure, Russia

Intergration into MIPS: A Simple Text Terminal with Output via VGA Interface

Alexander Kamkin, Institute for the System Programming of the Russian Academy of Sciences, Moscow, Russia

A MicroTESK-based Test Program Generator for MIPS Microprocessors

Ilya Kudryavtsev, Samara National Research University, Samara, Russia

HDL Application for Digital Synthesis in FPGA

Timour Paltashev, Northwestern Polytechnica University, Fremont, California, USA

AMD Exoscale Supercomputers Strategy

Yuri Panchul, Imagination Technologies, Sunnyvale, California, USA

Digital Design and Computer Architecture in the Era of System on Chip (SoC) and Internet of Things (IoT)

Evgenii Primakov, National Research University of Electronic Technology, Zelenograd, Russia

Implementation of Wishbone as System Bus for MIPSfpga

Alexander Silantiev, National Research University of Electronic Technology, Zelenograd, Russia

Implementation of Wishbone as Sysem Bus for MIPSfpga

Stanislav Zhelnio, Gazprom Inform, Moscow, Russia

Introduction into SoC: Building an fpga-based System by Integration of MIPSfpga Processor Core with Memory and Peripheral Devices Using AHB-Lite Bus

Isarf

19.04.2017 22:47Скажите, данный семинар ориентирован исключительно на школьников, или людям которым просто интересны ПЛИС также могут прийти и узнать что либо новое?

YuriPanchul

19.04.2017 22:48Если останется место, приходите, но сначала попробуйте загеристрироваться по ссылке. Если не получится, пришлите мне емейл на yuri.panchul@imgtec.com и я перешлю его в КПИ.

bp_2000

20.04.2017 12:17Очень интересно и хотим зарегистрироваться.

Но возник вопрос какой из курсов выбрать сыну. Есть ли какие-то возрастные градации (или по классам)? Кто, по мнению организаторов, подпадает под старшие и младшие классы? Обрисую более конкретно — 13-14 лет, 8 класс, с физикой/математикой на «ты» (оилимпиады и т.п.), но электроника, пока, на уровне пользователя гаджетов. Куда нам лучше податься?

Заранее очень благодарен

YuriPanchul

20.04.2017 22:25Я бы на вашем месте смотрел бы так: если ваш сын 1) знает что такое закон Ома 2) может складывать двоичные числа и 3) на чем-нибудь программировал, пусть даже немного (все равно — C, Java, Python), то он может рассмотреть группу для старших школьников. В противном случае лучше группу для младших школьников, в которой тоже есть масса интересных и полезных моментов, например работа конденсатора и пайка, которых нет в группе для старших школьников.

Shyster

Отлично, что проводятся такие семинары. Но вот скажите, а есть ли более дешевые решения для обучения? Breadboardable Artix-7 FPGA — 75$ даже мне дороговато, на поиграться, не то что школьникам

YuriPanchul

В целом платы с ПЛИС дороже, чем микроконтроллерные, при этом на AliExpress есть сверхдешевые платы (типа за $30 или ниже). Правда их нужно выбирать осторожно — некоторые требуют внешнего устройства для конфигурации, другие требуют использования старых версий софтвера для синтеза (это несмертельно, но нужно иметь это в виду).

x86128

Artix-7 крутая штука.

А где в России с доставкой можно это купить?

Я правильно понимаю, что эту «ардуину» можно сразу подключить к ПК и через Vivado начать с ней работать? Или нужен какой-то программатор?

YuriPanchul

Да, плату от Digilent можно сразу подключить, на ней есть встроенный программатор

Leerooooy

Есть копеечные отладки на Cyclone IV на той же алишке. У xilinx есть вроде более дешевая серия — спартан-6. Не стоит забывать о Lattice, у них есть FPGA в пределах 2000 LE и за копейки, а главное корпуса паябельные и мелкие QFN.

Fandir

http://www.terasic.com.tw/en/ Эти ребята вместе с Altera/Intel делают платы altera university program принять участие в ней не так сложно… Правда не знаю насколько сложно для школьников, но с университетами они сотрудничают охотно. Самая дешевая плата у них стоит 61 доллар.

YuriPanchul

Я использую платы от Terasic для семинаров в России и использовал в прошлый раз в Украине. Да, вот эта плата Terasic DE10-Lite, которая стоит 61 доллар — это отличная плата. Единственно она не breadboardable, поэтому для этого мероприятия в Киеве мы используем Digilent Cmod A7 от их конкурентов.

Если вы сможете уломать Altera university program проводить семинары в России и Украине для школьников, я двумя руками за. У них хорошие материалы для студентов, но для школьника нужно еще и растолковать функцию D-триггера, которую нагляднее делать на микросхемах малой степени интеграции.

Fandir

Идея altera university program заключается в том, что они предоставляют платы и материалы преподавателю, которой заинтересован обучать студентов сами они не проводят семинаров.

YuriPanchul

Образовательеые материалы от Altera можно скачать у них на сайте. А какое количество плат они предоставляли вам или людям, которых вы знаете? Насколько мне известно, они не обеспечивают целый класс плат.

Fandir

Ответил в личку