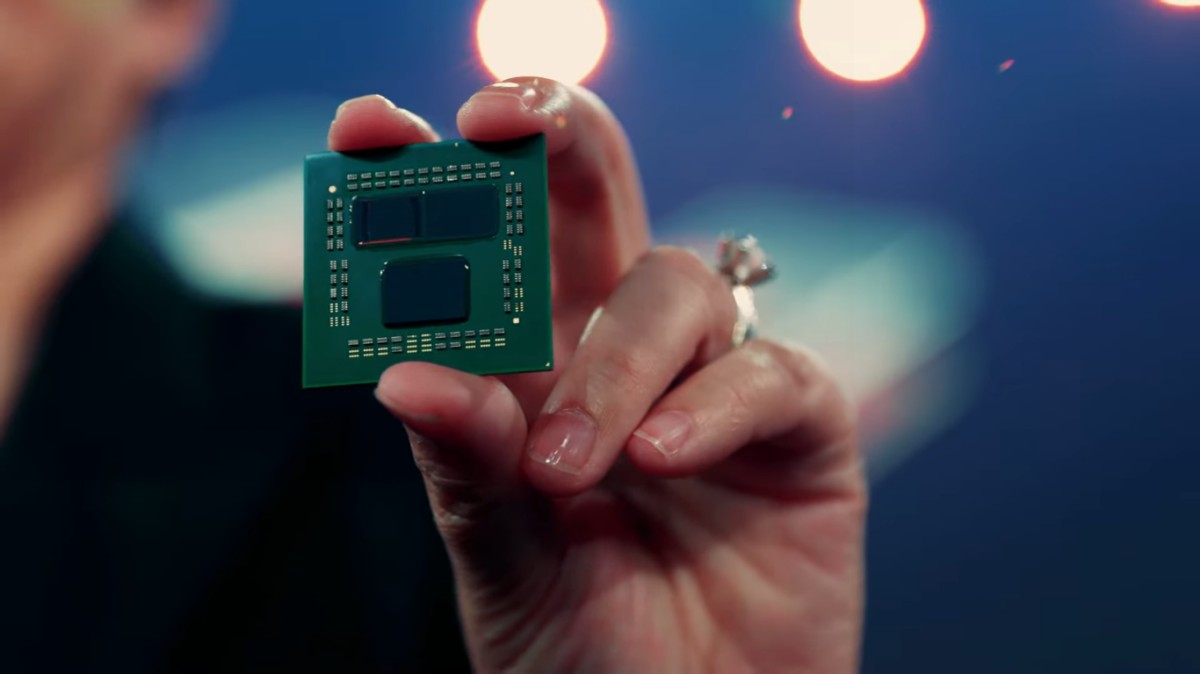

1 июня 2021 года на выставке Computex 2021 глава американской компании Advanced Micro Devices (AMD) и доктор по электротехнике Лиза Су (Lisa Su) представила прототип 12-ядерного процессора Ryzen 9 5900X с трехмерной компоновкой. У него на одном из чиплетов с ядрами Zen 3 распаяна микросхема с дополнительной кэш-памятью третьего уровня (L3) размером 64 МБ. Новая технология называется 3D V-Cache. С ее помощью можно увеличить объем кеш-памяти третьего уровня новых потребительских процессоров Ryzen до 192 МБ путем установки двух дополнительных кристаллов 3D V-Cache, а серверных EPYC до 768 МБ.

Глава AMD рассказала, что в среднем прирост игровой производительности достигает 15 % при использовании этой технологии по сравнению с аналогичными процессорами AMD без нее.

Лиза Су сравнила возможности прототипа Ryzen 9 5900X с технологией 3D V-Cache и такого же обычного процессора в игр Gears 5. Первый оказался быстрее на 12%. В играх Dota 2, Monster Hunter World, League of Legends и Fortnite этот показатель на пару процентов выше.

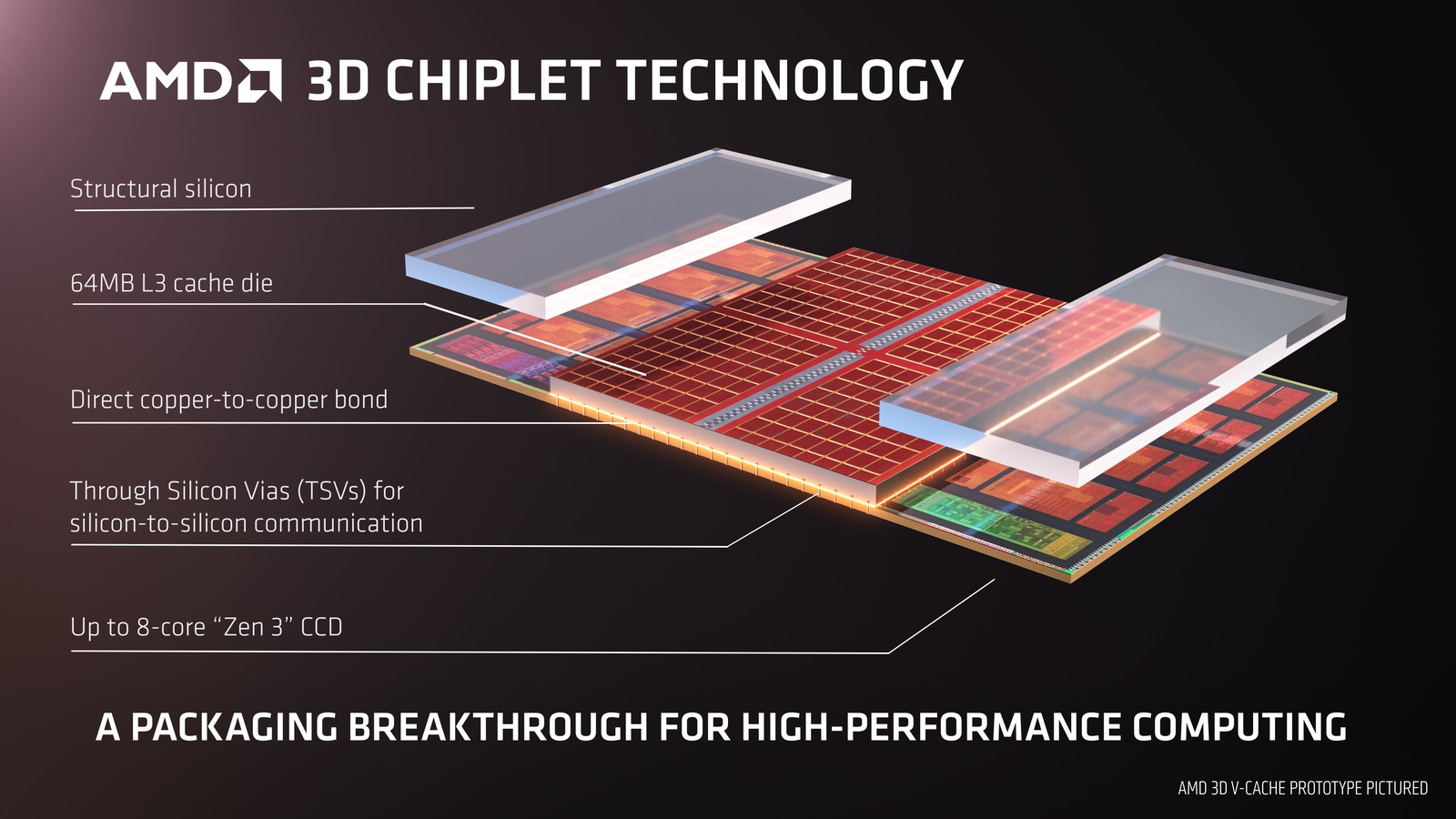

Лиза Су сравнила возможности прототипа Ryzen 9 5900X с технологией 3D V-Cache и такого же обычного процессора в игр Gears 5. Первый оказался быстрее на 12%. В играх Dota 2, Monster Hunter World, League of Legends и Fortnite этот показатель на пару процентов выше.Новая микросхема памяти SRAM технологии 3D V-Cache изготавливается по 7-нм техпроцессу, имеет площадь 36 мм кв.мм, что почти в два раза меньше чиплета Zen 3. Для связи микросхем внутри чипа используются вертикальные межкремниевые соединения Through Silicon Via (TSV). Добавление новой памяти не вносит изменения в физические параметры процессора.

Новая многослойная компоновка чипа Ryzen с 3D V-Cache.

Новая многослойная компоновка чипа Ryzen с 3D V-Cache.AMD заявила, что общая пропускная способность кэш-памяти третьего уровня при применении 3D V-Cache составляет более 2 ТБ/с.

AMD собирается выпустить на рынок процессоры Ryzen на архитектуре Zen 3 с технологией 3D V-Cache в конце этого года. Причем выход новых процессоров AMD на архитектуре Zen 4 все равно намечен на 2022 год.

Видеопрезентация AMD на Computex 2021.

vanxant

Как-то маловат прирост для 7-нм SRAM с лютой шириной шины (интересно, какой?)

Может игори не в память упираются просто? Матаноёмкое бы что-нибудь погонять.

cepera_ang

Отличный прирост для такого относительно простого с концептуальной точки зрения улучшения. Всё же кеши 1 и 2 уровня съедают 99+% всех обращений к памяти, особенно в играх (и другом оптимизированном софте), иначе современные процессоры недалеко от второго пентиума бы ушли по производительности.

С другой стороны — если разрабатывать новый софт и ориентироваться на наличие таких гигантских кешей (на эпике три четверти гигабайта, вот это да), то можно более интересных оптимизаций ожидать.

vanxant

99% это пока у вас только чтение.

Вот кстати да, современный софт на электроне с редуксом должен хорошо бустануться. В отличие от игр, они там на каждый чих копируют весь мир — пусть скромный и убогий, но всё же, из-за выравнивания и оверхеда динамической памяти в L2 кэш обычно не влезающий.

creker

Как правило игры очень эффективно работают с кэшами, минимизируя промахи. Zen 3 тот же получил буст в играх в очень большой части за счет изменения компоновки L3 и ссх. Собственно, в играх между zen 3 и zen 2 была разница где-то 15-20%, а ведь там еще дофига изменений в микроархитектуре. Так что 15% «просто так» получить, приклеив кэша сверху, это дофига. Этого вполне будет достаточно, чтобы перекрыть возможный прирост новых продуктов интел.

Собственно, я думаю ради этого в том числе это и было показано. Это упреждающий удар, чтобы показать, что амд в любой момент готова ответить интел в играх и для этого ей даже не нужен zen 4, до которого еще год с лишним. Математику и нет смысла показывать — она параллелится и интелу там вообще ловить нечего.

Am0ralist

Даже интересно, что они с zen4 умудрятся выкрутить, а особенно с апушками — переход на ddr5, добавить rdna2 и если ещё такой кэш, то это наверно свернуло бы рынок бюджетных видиков напрочь…

creker

Zen4 по утечкам более 20% прирост IPC. Т.е. им и без кэшей дополнительных есть чем ответить.

А HBM вещь хитрая. Да, у не шина большая, но у нее латентность существенно выше DDR обычной. Это не важно для GPU и прочих ускорителей, где доступ линейный в основном, а вот CPU может стать плохо.

Am0ralist

Поэтому и написал «асиметричный»)

Zen4 это ж 12 чиплетов по 8 ядер на 5 нм, если добавочный кэш тоже на 5 нм переведут, то суммарный кэш как бы не до 1,5 гб стал. На фоне текущих интеловских 60 мб кэша для 40 ядер…

Am0ralist

С третьей стороны этот l3 кэш имеет скорости вроде как выше обычного l3 при этом, только задержки выше чем для 1 и 2 уровня будут…

Будет интересно посмотреть, не получится ли разработчикам оптимизировать под это дело и получить ещё больший прирост в итоге. Ещё интереснее, что будет, если они подобное прикрутят к APU.