Можно ли обойтись без этой платы?

Тут, может быть, сразу последует вопрос — а зачем вообще выносить функции управления с материнской платы на отдельную карточку? Зачем умножать число компонентов, не проще ли всё засунуть на материнку, как это обычно делают производители серверов?

Согласен, в обычных условиях и мы поступили бы именно так — но в этом проекте и в таком вопросе пришлось поступить нестандартно. Из-за плотности компоновки материнской платы просто не было лишнего места для размещения чипов BMC, USB-хоста, PCIe-коммутатора и разводки всех связанных с ними цепей. А кроме того, просто не было места на задней панели шасси для установки коннекторов Ethernet/USB напрямую на материнской плате. В общем, мы решили не усложнять и без того сложную системную плату, и вынесли все эти компоненты на отдельную плату управления. Этот способ, кроме всего прочего, даёт больше гибкости в плане будущих доработок и изменений.

Что внутри?

Собственно, структурная схема платы весьма проста:

Структурная схема платы управления сервером.

Главный компонент — чип BMC ASPEED AST2400, очень популярный и наверняка многим хорошо знакомый. У него есть своя выделенная память DDR3 объёмом 512 МБ.

К BMC подключен хост USB3.0, для которого мы используем чип TI7340. От него два порта USB3.0 выводятся наружу. Также к BMC прицеплен двухканальный контроллер Gigabit Ethernet (BCM5720), порты которого выведены наружу. Это очень распространённый контроллер, который отлично поддерживается архитектурой POWER.

Всю эту компанию объединяет PCIe-коммутатор (по цене оптимально было поставить PEX8714), напрямую присоединённый к разъёму для подключения к системной плате. Он разводит PCIe x4 на x2 и 2 по x1.

Разъём для подключения к системной плате имеет небольшую особенность. Сам-то коннектор полностью стандартный. Но чтобы полностью исключить установку платы управления в обычный PCIe-слот (на материнке у нас есть специальный выделенный слот для платы управления), мы развернули коннектор на 180 градусов и сдвинули его относительно стандартного для PCIe размещения.

На схеме можно также заметить видеовыход VGA и два последовательных порта — их наружу не выводили, оставили в виде header-ов. Они нужны в основном для отладочных целей — да и на внешней панели низкопрофильной PCIe-карты просто не осталось места после размещения двух USB и двух Ethernet портов.

Как выглядит плата

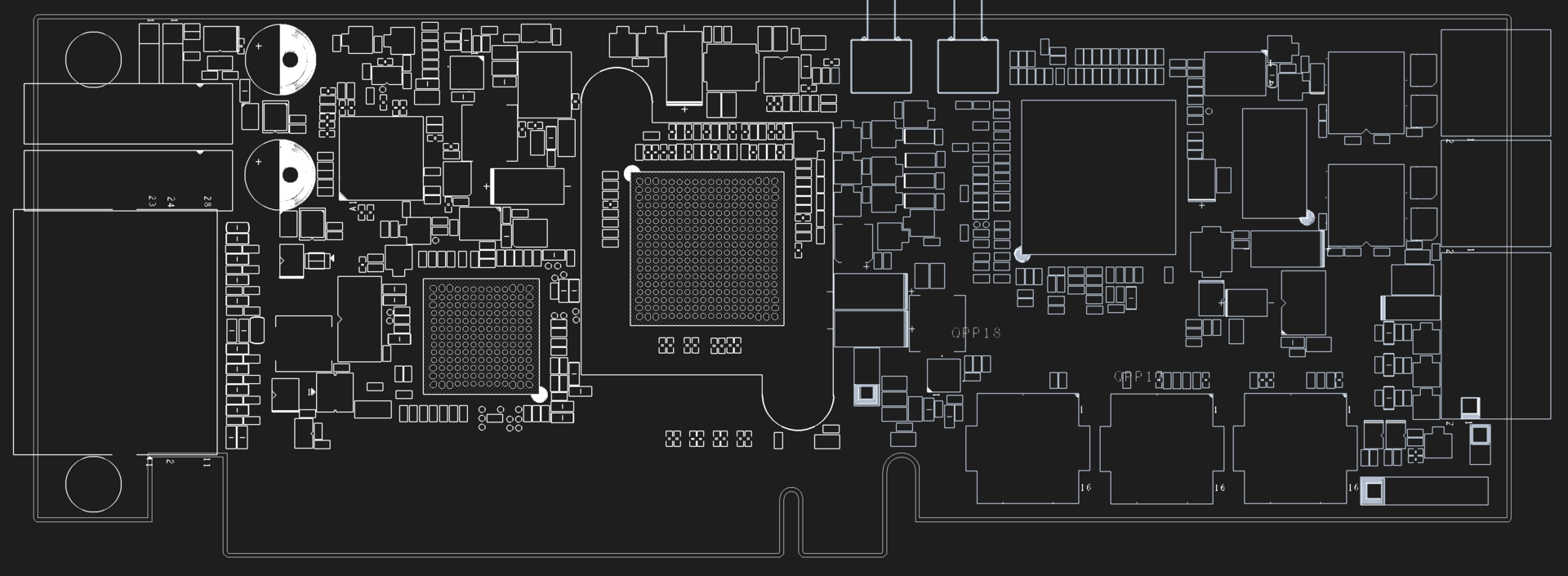

Собственно, геометрия платы получилась такая (плата низкопрофильная, но длинная):

В левой стороне изображения задняя панель платы — из неё выведены 2 порта USB3.0, а под ними — сдвоенные порты GbE.

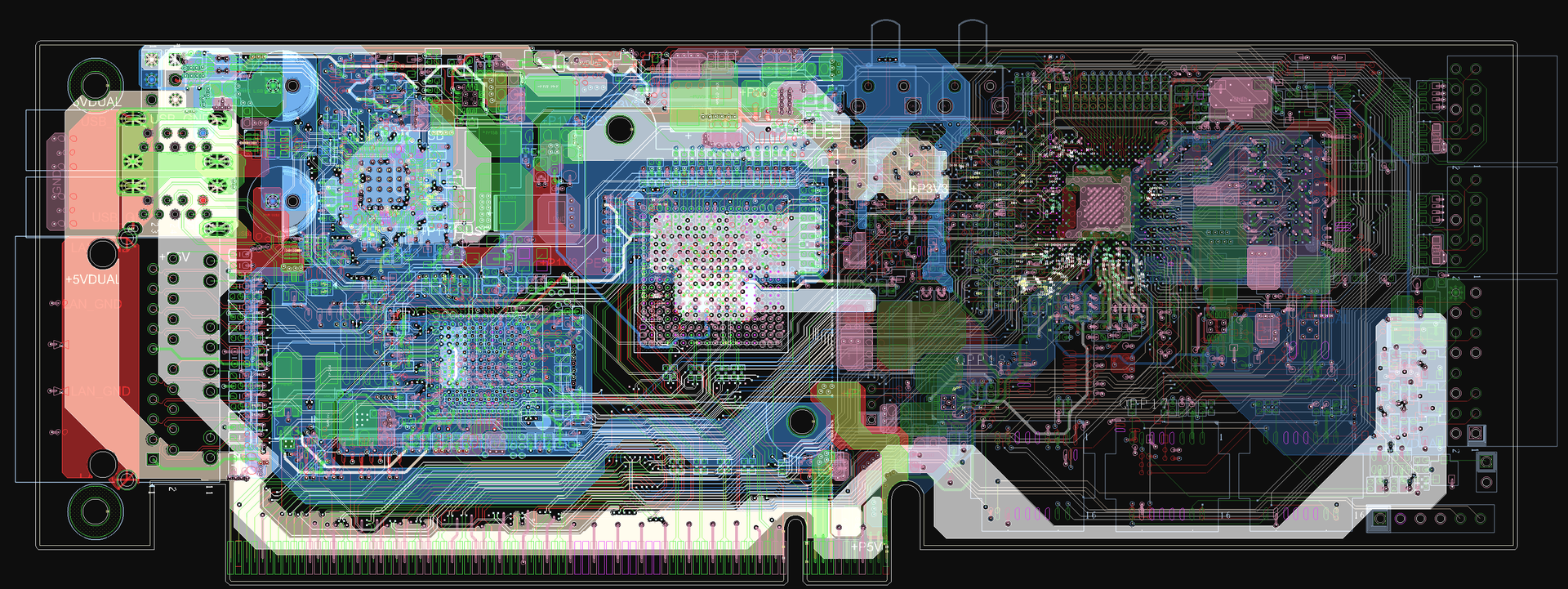

Покажу и нашу любимую техноживопись дорожками по плате:

Сигналы и питание разведены по 8 слоям.

Считаю, отлично годится, чтобы распечатать в цвете и повесить на стенку — нарядно, воодушевляюще, и очень жизненно! :)

Пожалуй, стоит ещё немного сказать про BMC. Прошивку для него мы разрабатываем сами на основе OpenBMC. Собственно, задачи стоят простые:

- зафиксировать требования к прошивке и расставить приоритеты по их реализации;

- поднять исходный вариант на нашем сервере (адаптировав базовый функционал к нашему железу);

- добавить нужный для нас функционал.

Получившуюся в результате версию, естественно, в OpenBMC будем коммитить.

Комментарии (25)

maxbrsw

01.10.2016 17:52Здравстуйте!

Позвольте, пожалуйста, полюбопытствовать- как Вы и/или Ваши PCB Designer-ы/CAD librarian-ы, разрабатывают библиотеки футпринтов? Просто смотрю под увеличением на плату и вижу несколько принципиально разных методологий, в числе которых большой интерес представляют скругленные пады: возможно это глюк рендера Allegro, однако сравнивая с результатом PCB Library Expert PRO последней версии, пресловутое скругление в некоторых местах видится несколько с перебором.

Также хотелось бы спросить вот что: правильно ли я понимаю, в Ваших библиотеках футпринтов не используется courtyard(особенно пропорциональный), при этом зазоры между партами контролируете только через DFA boundary?

Paging

01.10.2016 22:43Библиотеки — вещь во многом историческая (зачем заново рисовать футпринт который был нарисован еще пять лет назад?), отсюда может быть некоторый зоопарк конечно: что-то рисовалось давно и совсем другими людьми и даже в бытность нашу в других компаниях, где-то просто берутся футпринты от вендоров компонентов. Основной принцип простой: работает — не трогай!

Зазор контролируется по DFA.

maxbrsw

02.10.2016 03:15Правильно ли я понимаю, вы не следуете IPC-7351, и стало быть, никогда не устанавливаете компоненты courtyard edge-to-edge(т.е по-настоящему плотная упаковка)? И вытекающий вывод- в ваших платах возможны футпринты сделанные по «любой» методологии и/или с любой плотностью во вышеозначенному стандарту: главный критерий- раньше запаивалось и «заработало»?

Что касается «новый футпринт vs. старый 5 летней давности»- очевидно что результат в пользу нового футпринта, ибо по вышеприведенному стандарту поменялся что land pattern, что courtyard: все это имеет критическое значение как в плане качества пайки, так и возможности устанавливать плотно компоненты. Говоря же о «футпринтах вендоров», очень часто бывает что они сделаны либо кривовато, либо попросту скопированы с сомнительных мест- особенно это касается платных библиотек американского происхождения.

Paging

02.10.2016 08:57Не совсем так. Мы в первую очередь ориентируемся на рекомендации производителей компонентов из документации на компоненты. Если там футпринт отсутствует — естественно делаем по IPC. Иногда футпринты слегка правятся при получении фидбека от наших партнеров — производителей PCB (это может быть вызвано их технологическими ограничениями или опытом).

Если компонент пять лет назад прекрасно паялся и мы не имели брака с ним — нет повода считать, что брак появится сейчас из-за того, что в IPC изменились рекомендации. И здесь даже не то, что «лучшее — враг хорошего» — просто у нас и без перелопачивания по десять раз библиотек хватает занятий. И да, никакие платные библиотеки (или просто библиотеки скачанные непонятно откуда) мы не используем. Логика всегда простая, в порядке убывания предпочтительности — либо берется уже готовый футпринт от производителя компонента (кто-то выкладывает их в явном виде, где-то можно быстро выдрать из выложенных референс-дизайнов), или рисуем его сами по рекомендациям из datasheet'а, или рисуем сами по IPC. И естественно везде не выключаем голову (это насчет кривовато сделано — да, бывает, но редко довольно).

VJean

01.10.2016 17:52Вы издеваетесь?

Paging

01.10.2016 22:35Нет.

VJean

01.10.2016 23:11+1Я понимаю, что это блог компании и описываемая железка наверняка с кучей навешанных ярлыков авторских прав, патентов, NDA и т.д. Открывая статью на хабре в хабе Разработка с подобным названием (не от ализара) хочется прочесть что-то более техническое и более развернутое, а не упоминание пары чипов на пару картинок.

Вкратце: очень разочаровали.

czed

01.10.2016 23:15-1Зачем? Это мало кому интересно.

При всей своей технической направленности — данный ресурс является в первую очередь развлекательным. Поэтому тексты должны читаться легко а картинки быть красивыми.

Paging

02.10.2016 09:00+1Мы описываем разработку сервера, и статьи в целом освещают его устройство (даже эта, хотя она конечно совсем поверхностная, но тем не менее). Можно начать описывать какие-то совсем узкие технические аспекты — но круг лиц, кому это хоть как-то может быть интересно будет совсем небольшим.

Для нас эти статьи в первую очередь — просто worklog, а не цикл мастер-классов.

Xalium

01.10.2016 17:52А в какой программе сделана разводка платы, в которой (проге) сделаны скриншоты?

Paging

01.10.2016 22:34Cadence Allegro

maxbrsw

02.10.2016 03:17Используете ли IFP/GRE а также опцию предоставляющую возможность одновременной работы нескольких человек?

Paging

02.10.2016 09:04Первое — да, а тимдизайн — нет.

maxbrsw

02.10.2016 10:05Т.е по сути отдельно взятый проект серверной матплаты разводит также отдельно взятый человек?

Paging

02.10.2016 13:18Отдельно взятую серверную плату делает один человек, да.

maxbrsw

02.10.2016 17:40Если не секрет, сколько по времени «в среднем» это занимает?

Paging

02.10.2016 18:33Единицы месяцев. Больше месяца назад у нас был первый пост, в котором были видны уже некоторые прикидки и наброски по плате. Они сами по себе, понятное дело, требовали времени. Сейчас работа по трассировке сильно продвинулась, но сказать что через две недели совсем закончим — точно нельзя. Плюс еще будет цикл ревью, как внутреннего, так и внешнего (IBM) — это тоже время.

foxmuldercp

03.10.2016 11:32а почему отказались от стандартного порта и сделали свой для платы?

Paging

03.10.2016 11:46Помимо PCIe через этот коннектор проходит еще много всяких специфических сигналов (например для подключения BMC к менеджмент-шине процессоров), не предусмотренных в стандартной распиновке PCIe слота.

erlyvideo

простите, немного не понял: вы сами скомпоновали материнку и к ней ещё приделали такую плату с пачкой разъёмов?

czed

ИМХО все очевидно:

Есть мать — https://habrahabr.ru/company/yadro/blog/308508/

На матери кроме разъемов памяти и слотов расширения нет ничего и быть не может, ибо не помещается.

Есть отдельный Management модуль с BMC о котором эта публикация.

Paging

Да, все верно.

Paging

Выше уже правильно написали — в целом да, все именно так :)