Вообще здесь будет нечто вроде рабочего журнала (worklog-а)— вместе с коллегами будем постить рассказы о зарождении жизни в железках. Сначала про сервер, а дальше и про остальное.

Как сюда лучше всего поставить преобразователи напряжения?

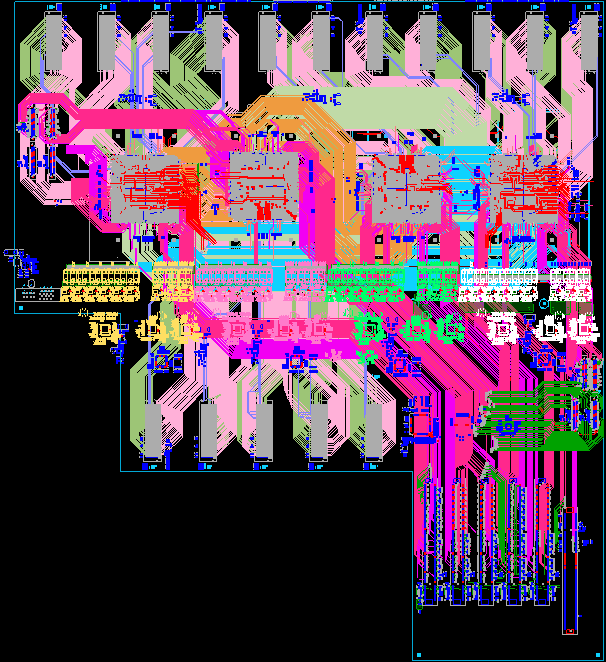

На скрине выше — не результат галлюцинаций художника, творящего в стиле ПОП-АРТ, а системная плата, на которой надо уместить четыре группы преобразователей напряжения — по одной на каждый процессор (жёлтые, розовые, ярко-зелёные и белые на скриншоте).

Сначала хотели вынести их на внешние платы, как на рисунке ниже:

Первоначальная идея по размещению преобразователей

По изначальной задумке, каждая плата должна была нести VRM-ы для двух процессоров и связанных с ним модулей памяти. Но после проработки решили отказаться от этого варианта — дико большой ток требует большого CardEdge-разъёма, что сильно усложнит трассировку межпроцессорных шин.

Теперь пробуем запилить VRM-ы на системной плате. Это тоже усложняет трассировку — теперь уже высокоскоростных шин, т.к. придётся менять расположение дорожек, чтобы огибать переходные отверстия (vias), которые необходимы для подведения напряжений на процессоры от преобразователей. А отверстий нужно не мало! Для процессоров и модулей памяти необходим большой ток, и нужно плотность этого самого тока, проходящего через переходные отверстия, минимизировать. Если сэкономить на количестве переходных отверстий, то это вызовет их перегрев (из-за большой плотности тока) и со временем деградацию до полного выгорания.

Практически скриншот из TRON 2.0, хочется плакать кровавыми слезами. Отверстия подсвечены жёлтым — на самом деле это подсветка ошибок из-за пересечения с ними дорожек различных шин. Нужно все эти дорожки отводить в сторону.

Вообще, сложность проекта в рамках моих задач состоит в том, что приходится трассировать на плате, помимо шин питания с большим током (до 250 А!), много высокоскоростных шин — PCIe Gen3 (8 Gbps), DMI (9.6 Gbps, Differential Memory Interface, шина подключения чипов буфера памяти Centaur), межпроцессорные шины A-bus (6.4 Gbps, SMP линк).

Если интересно, можно отдельно про них написать.

Компонентов тоже немало — 4 процессора, 16 разъёмов для райзер-карт памяти DDR4, в общей сложности 14 разъёмов для PCIe (из которых 8 — NanoPitch, а 6 — обычные разъёмы для карт расширения), и монтаж выходит очень плотный. Первый скрин даёт достаточное представление о масштабе бед — это упрощённое изображение с изрядным количеством скрытых от показа компонентов, чтобы и без того плотную картинку не перегружать.

Участок между двумя процессорами. Удалось проложить дорожки между ними весьма плотно.

Много высокоскоростных интерфейсов — много ограничений. Приходится строго соблюдать требования по трассировке — максимальная длина, статическая и динамические фазы в дифференциальных парах; дистанция между дифф-парами; максимальный разброс по длине в группе, волновое сопротивление и т.д.

Это, в свою очередь, накладывает ограничения на маршруты шин по плате, выбору материала печатной платы (материал с низкими потерями), количеству слоёв, и т.д.

Сейчас у нас стэк с 28 слоями — из них 4 слоя выделено под шины питания, для увеличения площади полигонов питания — это позволяет минимизировать IR drop (падение напряжения на проводнике). Хотим не превышать это число слоёв, и думаю, должны это сделать.

В общем, такие вот рабочие будни. Привыкаешь смотреть на такие схемы пристальным взглядом — а потом замечаешь, что они в своём роде даже художественны, как смешение линий и цветовых пятен различных форм и оттенков. Да и сама трассировка таких масштабов — само по себе искусство.

Напоследок хочу показать ещё один скрин, который скрывает целую историю:

Это не пришествие Ктулху из морской пучины.

Из-за особенностей расположения разъёмов памяти пришлось развернуть один процессор на 180 градусов. Почему нельзя было расположить разъёмы памяти иначе? Это уже история следующей серии и героем в ней буду не я.

Комментарии (73)

Indemsys

25.08.2016 14:46-7Не понял где здесь искусство и на каком основании оно тут может быть?

Трассировка из последнего скриншота делается за полчаса. Сплошная рутина.

Но почему при наличии моря места все трассы собраны в плотные скопления вот это вопрос.

Видать трассировщик еще не пуганный перекрестными наводками.

Paging

25.08.2016 15:00Искусство — это так, заголовок. Абстракционистов видели? Авангардистов? :)

Трассировки как таковой тут еще нет — просто прикидки, как лучше шины по плате разложить и куда засунуть VRM-ы. Рутинные прикидки, да.

Трассировщики у нас не пугливые совсем — не первая плата же, причесывать все будем потом. По этим картинкам вообще я бы не стал о спейсинге между парами судить — все хорошо там с этим на самом деле.

GREGOR_812

25.08.2016 15:23+2Какая интересная затравочка! Спасибо, подписываюсь на блог, буду следить)

Мне, как человеку относительно новому в этом деле, интересно было бы видеть указания на подводные камни при плотной высокоскоростной трассировке, варианты их обхода, какие-то эмпирические фишки, всё-такое)

Paging

25.08.2016 15:33Нюансов очень много, в принципе, если действительно интересно — стоит почитать для начала например «High Speed Digital Design: A Handbook of Black Magic».

Но в будущем попробуем писать про какие-то наиболее заковыристые и специфичные вещи.

GREGOR_812

25.08.2016 16:10+1Я уже осилил первую часть и сел за вторую, но она медленнее идёт, сложнее)

Ещё нашёл книгу такого автора как Кечиев, на первый взгляд показалась довольно подробной и интересной.

mns_15

25.08.2016 16:11Какую программу используете — Cadence Allegro?

В какой прогамме будете делать анализ — Power и Signal Integrity?

Paging

25.08.2016 16:15Да тут все стандартно, почти весь мир материнки в Cadence делает (по крайней мере я исключений не видел, а общаемся мы очень много с кем), и мы в этом плане не исключение. Анализ — тоже все стандартно, Sigrity, плюс Ansys местами.

GREGOR_812

25.08.2016 16:20А какие перспективы у меня, если я Altium использую? Почему стандартом является Cadence?)

Paging

25.08.2016 16:24Мне кажется тут больше играют исторические причины — в этом сегменте рынка «так повелось» очень давно. Поэтому если хочется заниматься именно материнскими платами и всем что вокруг этого — то лучше переехать на Cadence. Да и вообще, хорошая же система :)

К Altium у серьезных компаний до сих пор отношение как к какому-то пионерскому инструменту (у нас — нет, мы считаем что все инструменты на вкус и цвет разные и каждый выбирает то, что ему ближе).

GREGOR_812

25.08.2016 16:29Я просто подумал, мб какие-то объективные причины есть, о которых опытные разработчики знают.

Попробую переехать, попытка не пытка) Лично для меня Altium привлекателен тем, что очень много актуальных ресурсов и хорошая документация на русском языке, ну и в целом в моём окружении все с ним работают

Strannii

25.08.2016 16:49Исходя из трехлетнего опыта работы в Альтиуме, и после этого уже почти двухлетнего опыта работы в Cadence, скажу точно: Альтиум у Вас будет крашиться несколько раз на дню. Иногда роняя весь проект. Пару раз он у нас сделал ошибки в гербераъх, отправляемых в производство. С Cadence таких проблем нет. Единственная проблема — это интерфейс) У него своя философия, идеология, религия и вообще. Но спустя несколько проектов понимаешь, что оно так и правильней будет.

GREGOR_812

25.08.2016 16:53Да, кстати, вот с крэшами иногда сильно подбешивает. Ещё нужно особый ритуал производить при переименовывании компонентов при удалении/добавлении/перемещении, чтобы связи на плате не испортились. Но интерфейс очень дружелюбный и легко осваиваемый) эх, нет в жизни совершенства...(

Спасибо за ответ)

Strannii

25.08.2016 16:59В Альтиуме при добавлении/переименовывании компонентов очень важно соблюсти порядок внесения изменений из схемы в плату. Там появляется длинный список (Engineering Change Order кажется), и его НИКОГДА не стоит слепо применять весь целиком. По отдельности, группами, сохраняя правильный порядок применения изменений. Я с помощью этого умудрился когда-то импортировать из Cadence референсный дизайн связки мобильного процессора с DDR3 памятью на восьми чипах, связать схему с платой, вписать в свою собственную, и ничего при этом не потерять.

Так что подытожу — Engineering Change Order — крайне важный шаг при переносе данных из схемы в плату

AndriAnoBoTS

25.08.2016 16:15дорогущая полагаю получилась плата, столько места ничем не занято, а техпроцесс наверное далеко не самый дешевый.

обычно разводят более компактные платы с более плотным монтажем и в резутате намного дешевле в пересчет на мм кв получается.

Paging

25.08.2016 16:2128 слоев дешевыми быть не могут, и это все не от хорошей жизни или неумения. 4 процессора класса POWER8 — это _очень_ много высокоскоростных шин. И чтобы все это по плате растянуть — нужно место. Плата для своего класса кстати и так мегакомпактная. Да, конечно можно было попробовать сделать плату еще немножко плотнее — но тогда пришлось бы пользоваться всякими технологическими извращениями типа слепых и погребенных переходных отверстий, что на цене сказалось бы очень отрицательно.

Strannii

25.08.2016 16:50Так получается палка о двух концах. Если вы сделаете микропереходные отверстия и стек типа 2+N+2 или 3+N+3 у вас может сократиться количество слоев, и цена получится та же. И места под ногами процессора будет больше за счет того, что не будет кучи сквозных отверстий. Вы проводили анализ стоимости такого исполнения?

Paging

25.08.2016 16:57Всегда есть аргументы за и против. Для данной конкретной платы оценку не проводили, потому что исходя из предыдущего опыта, когда это делали — стоимость применения microvia и прочего перекрывала экономию на паре слоев и 10% размера платы (по крайней мере у тех EMS партнеров, с которыми мы работаем). К тому же в нашем случае меньше ее делать нам просто не надо — незачем, сервер имеет вполне определенные размеры.

Strannii

25.08.2016 17:03Ну раз размеры позволяют, то дерзайте! Эх, смотрю я на этот ваш Routing Plan, и завидно становится — сколько места для выравнивания дорожек по длинам) Кстати, какой класс исполнения платы? Зазоры/дорожки/отверстия-ободок?

Так же прошу статейку о правильном задании правил совпадения длин в Cadence на таких масштабных проектах)

Paging

25.08.2016 21:33Как правило мы стараемся не использовать нормы уже чем 0.1/0.1/0.3, но для ряда плат приходится уходить и на более тонкие нормы (в частности недавно была плата 2.4мм толщиной (14 слоев) с отверстиями 0.2, ну или вот например райзер с памятью для материнки из этой статьи (4 канала DDR4, 2DPC плюс тот самый Centaur) — там дорожки-зазоры по 3 mil, иначе никак.

maxf75

25.08.2016 16:42 .

.

На самом деле, ещё далеко не все компоненты размещены, работа в разгаре. На этом скрине ещё не размещённые компоненты выстроены по периметру материнки, и это только наиболее существенные, без мелочёвки.

SemperFi

25.08.2016 16:32это вы бодро начали:

Фирма делает серверы и другое железо

Можно объявить конкурс — «Найди десять отличий между»:

- СХД IBM Storwize v5000 и Yadro CX1-2

- сервером IBM Power 870 и Yadro P1-24

- ленточной библиотекой Overland Storage NEOs T48, она же IBM TS3200 и Yadro M1-2

"- Побойся бога, Истерлинг… — Пайк умолк, не договорив." Одиссея капитана Блада

Paging

25.08.2016 22:38Красиво, с цитатой даже…

В идеальном мире, где пони какают радугой (ну или бабочками — я плохо понимаю идеальные миры), наверное все так и выглядит — люде где-то находят много денег, чтобы хватило на разработку, после чего продают исключительно и только свои продукты.

Реальность же жестока — разработка таких вещей, которыми занимаемся мы, имеет долгий цикл — до полутора лет, а кушать хочется всегда. Поэтому мы совершенно не стыдимся того факта, что продаем собранное в рамках OEM-соглашения с IBM оборудование под своей торговой маркой. И не только IBM. И кстати реально собранное, а не просто с переклеенным шильдиком. И именно это позволяет нам реализовывать очень дорогостоящие разработческие проекты.

SemperFi

25.08.2016 22:50-1очень круто

а на производство попасть можно, в рамках блог-тура? пофотографировать?

особенно интересует сборка YADRO M1-8 и YADRO P1-80

прям особенно-особенно про YADRO M1-8 интересно — всегда считал, что во всем мире один завод их делает, и тот в Мексике. А тут — то ли Мексика в Шуе, то ли завод в Румянцево переехал.

про ОЕМ с Hewlett-Packard еще интересно, не расскажете?

Paging

25.08.2016 22:57Ленточные библиотеки мы не собираем. А вообще идея с туром с фото интересная, так что при следующем большом заказе, когда будет собираться партия — можем и пригласить.

У вас цель-то какая? ))) Доказать миру, что мы не все собираем? Ок, мы не все собираем конечно :) Но все же собираем сильно больше чем многие. Показать, что мы не занимаемся реальной разработкой in-house? К сожалению, мы именно на это делаем ставку и живые продукты появятся уже меньше чем через год…

SemperFi

26.08.2016 10:37-2моя цель — показать вам, что начинать общение на хабре с (как минимум) подтасовки фактов — это плохая примета.

Здесь много технически грамотных и образованных граждан, для которых слово «маркетинг» в топорном его проявлении — синоним ругательства, а вы прямо с порога считаете, что лучший способ понравиться аудитории — это проявить к ней неуважение.

Paging

26.08.2016 11:17+1Доброе утро! :)

А вы знаете — спасибо вам за то, что указали нам на то, что мы были неправы (мы правда пока плохо понимаем, где именно, поскольку никаких искажений ни в самой статье, ни в наших ответах мы не видим).

Мы ценим и уважаем аудиторию данного ресурса и надеемся что было немало людей, кому было любопытно почитать статью о том, что и как мы разрабатываем, и мы намерены продолжить цикл этих публикаций.

И конечно мы будем вам благодарны если вы продолжите внимательно следить за нашей деятельностью и указывать нам на недочеты.

Хорошего дня! :)

SemenovNV

26.08.2016 11:20+4Похоже, что Вы отвечаете на утверждения, которых в статье нет. В чём, собственно, подтасовка фактов?

Мы написали, что делаем серверы и другие железки — мы их действительно делаем, и в публикации осветили некоторые моменты из проработки системной платы. В статье нигде не утверждали, что наши собственные разработки активно продаём — напротив, не скрывали, что сейчас сервер находится в проработке, и открытых вопросов ещё много. Меньше чем через год доделаем, тогда начнём продавать.

Чтобы вернуться в конструктивное русло, предлагаю дождаться следующих нескольких статей — покажем другие аспекты процесса разработки.

ikoev

25.08.2016 23:00+1В рамках IBM Business Days в cентябре будет подробно рассказано и показано про компонентую сборку (9-ое производство в мире за пределами IBM) на заводе в Шуе, и о программно-аппаратных комплексах Talon идентичных тем, что стоят на заводах в Мексике, Германии, Сингапуре и т.д.

Вы я так понимаю из интегратора, попасть наверное туда сможете же, да?

lelik363

27.08.2016 20:36Платы сами паяете?

Paging

27.08.2016 20:39Нет, у нас нет своего монтажного производства, так что и изготовление PCB, и их монтаж заказываем (для своих проектов естественно, к OEM это не относится — там только сборка части позиций).

lelik363

27.08.2016 22:00Китай?

Paging

27.08.2016 22:09Что-то Китай, что-то Тайвань. Попозже будем думать о локализации — в стадии разработки это пока не актуально (образцы гораздо проще паять «там»). В принципе все платы вполне можно монтировать и у нас — с точки зрения монтажа в России хватает вполне прилично оснащенных производств. Основная головная боль — необходимость закупки практически всех компонентов по BOM под конкретное изделие (в отличие от того же Китая, где наши EMS-партнеры имеют огромные стоки).

lelik363

27.08.2016 22:20После монтажа функциональное тестирование как будет проводится?

Paging

27.08.2016 22:24Если мы про QC — то помимо стандартных процедур производителя мы на фабрике ставим свой стенд для финального тестирования перед упаковкой, который для производителя является полным black-box'ом и исключает любую возможность вмешательства и подтасовки результатов. Проверяются в целом только те вещи, которые направлены на оценку именно качества монтажа — что все компоненты работают, прошито все правильными прошивками и при этом ничего не забыли, плюс короткий цикл нагрузочных тестов (в условиях серийного производства ни одна фабрика не пойдет на длительные циклы тестирования).

ikoev

25.08.2016 22:44+1никаких противоречий. мы действительно делаем железо. а еще мы продаем собранное нами по oem-контракту c ibm оборудование, зарабатываем деньги, которые частично покрывают разработку железа над которым мы трудимся.

Strannii

25.08.2016 16:53Интересное начало череды статей)

Очень хотелось бы в дальнейшем увидеть результаты анализа высокоскоростных шин в Sigrity SI и цепей питания в PowerDC

SemenovNV

25.08.2016 17:12Вообще в рамках цикла про этот сервер мы планируем много о чём писать, не только о печатных платах — про архитектуру сервера, подсистемы и т.д.

Позже, вероятно, параллельные циклы начнём по другим железкам. Но заявку приняли, пожелания учтём.

Paging

25.08.2016 21:28Я с одной стороны прекрасно понимаю любопытство, но с другой стороны надо понимать, что деньги мы все же зарабатываем не литературой :) А технические люди вообще как правило если что и пишут — то только по принуждению. Хотя, кое-кому конечно графоманство не чуждо :)

В общем, мы будем стараться писать почаще и именно про какие-то интересные моменты. Рутины много — про нее писать нет смысла (хотя и это наверное тоже нашло бы свою аудиторию).

Wigaro

26.08.2016 15:39+1В списке хабов есть FPGA, но в статье про них ни слова.

Вы используете ПЛИС или это ошибка? Какие? Для каких целей? Было бы интересно про эту кухню почитать, на хабре такого мало.

SemenovNV

26.08.2016 15:53+1Я всё думал, спросит кто-то или нет. Спасибо. :)

Это не ошибка, хотя ПЛИС в этом сервере не используем.

На самом деле долго думали, какие хабы указывать при публикации — специального хаба про печатные платы не обнаружили. Некоторое количество статей на эту тему на ресурсе есть, но лежит даже не в потоке «Разработка», а в «Разном». Но в «Разное» идти не хотелось, т.к. речь всё-таки идёт именно про разработку сервера.

В итоге посоветовались с администрацией хабра, и предположили, что читателям хаба FPGA подобный материал может быть понятен и в чём-то интересен. Надеюсь, не ошиблись.

На будущее учтём — если будут проекты с использованием ПЛИС, постараемся описать.

Paging

26.08.2016 16:08У нас скорее всего в начале 2017-го будет проект на Kintex UltraScale+, задумка там довольно интересная, с DDR4 и PCIe Gen4, плюс NVMe endpoint, когда начнем реальную работу — попробуем рассказать. Собственно график этого проекта определяется выходом сэмплов подходящих нам FPGA — поколение новое совсем.

dernuss

27.08.2016 20:36+1А вот что я делал в альтиуме, 18 слоёвОбщий вид

Выравнивание параллельных шин, данные с АЦП.

3d вид. 3d особо не заморачивался. Следующие платы с хорошими моделями 3d.

Ну и что вышло, то есть фото. Верх.

Низ

Paging

27.08.2016 20:41Что лишь подтверждает факт, что для профессионала инструмент — это просто инструмент, не он определяет качество (это к вопросу Altium vs Cadence vs Mentor).

bunchofjudas

27.08.2016 20:36За кадром осталась пара интересных моментов.

Power8 процессора существуют в вариантах от 4-way до 12-way. В каких вариантах они будут ставиться в этот новый сервер?

Из картинок я не совсем понял: процессора планируется разместить прямо на плате? Или они пойдут в виде процессорных карт, как в той же E850? И в целом, учитывая, что проектируется прямой competitor E850 — нет ли соблазна подсмотреть, как разные инженерные задачи уже решили коллеги из IBM? .-)

Paging

27.08.2016 20:44POWER8 есть разные, да, но есть один момент — в OpenPOWER зарелизен всего один вариант, сильно обрезанный относительно тех POWER8 что использует сам IBM в больших системах. Да, ядер может быть разное число (до 12), но систему с более чем четырьмя сокетами на нем не построить. А POWER9 в варианте OpenPOWER будет еще сильнее задушен кстати.

Мы очень плотно работаем с IBM, потому что мы первые, кто делает OpenPOWER-систему такой плотности (4 сокета и 32 DIMM на сокет). В нашем варианте все 4 сокета на одной плате, а вся память — на райзерах.

bunchofjudas

27.08.2016 23:03В этом как раз ничего удивительного нет. E850 тоже 4 сокета максимум. Дальше уже идёт hi-end (E870 и E880) и совершенно логично не взращивать себя прямых конкурентов.

Планируется ли на новых серверах запускать AIX? Насколько я помню из того, что говорили ваши коллеги, когда приходили к нам, AIX можно было крутить, если приобретался сервер IBM с шильдиком Yadro. А как с этим будет у новых серверов? Не открою Америки, если скажу, что большинство из тех, кто с радостью купит новые сервера, сделают это в рамках апгрейда инфраструктуры Power+AIX. Если на серверах можно будет крутить только Linux — это уже совсем не так интересно.

Paging

27.08.2016 23:09Все же разница есть — E850 построен на «больших» POWER8.

AIX в рамках OpenPOWER недоступен насколько я понимаю. И мы в этом смысле не собираемся конкурировать с IBM. Скорее мы просто делаем сервер с определенными ключевыми преимуществами (поддерживаемый объем памяти, дисковая подсистема) — в том числе и по отношению к машинам с архитектурой x86. Основное позиционирование — IMC/IMDB приложения.

bunchofjudas

28.08.2016 00:00> построен на «больших» POWER8

Я где-то утерял нить. OpenPOWER — это же консорциум third-party производителей с определёнными ограничениями. Мне всегда казалось, что сами процессоры в рамках OpenPOWER полностью идентичны тем, что поставляет IBM.

Что такое тогда «большой» POWER8 и что такое та железка, что будет ставиться в сервера в рамках OpenPOWER?

> AIX в рамках OpenPOWER недоступен насколько я понимаю

Это вот, конечно, губит отличную идею :-( не понимаю IBM в этом плане. Судьба IRIX / HP-UX никого ничему не научила, видимо.

Paging

28.08.2016 09:03К сожалению про процессоры — это распространенное заблуждение. В OpenPOWER отдана слегка ограниченная версия процессора (из существенных моментов — только 4хDMI вместо 8 у «больших» и значительные ограничения по межпроцессорному интерконнекту).

Вообще для IBM OpenPOWER — это в первую очередь попытка поконкурировать с Intel в low-end (2-4S) сегменте, и попытка пока явно не сильно удачная. POWER9 в этом плане будет иметь больший успех (как минимум в HPC, поскольку будет поддерживать PCIe Gen4 и NVLINK).

AndrewN

28.08.2016 00:48Простите, 250 Ампер?

Так это не менее 60 мм? по меди сечение шин, о каких платах речь идет?

Paging

28.08.2016 09:11Не очень понятно, откуда именно 60 мм? получилось? Обычно в электротехнике принимают 10 А/мм? для медных проводов. Но даже если 25 мм? брать — конечно на плате никто такого сечения себе позволить не может. Все рассчитывается исходя из максимально допустимого нагрева полигонов (собственно в этом вопросе тепловыделение — единственное ограничение). Собственно, максимальные токи получаются по шинам питания процессоров — напряжение там низкое, меньше вольта, а ток огромный. Но и расстояние от VRM до процессора по плате смешное, так что это не очень большая проблема. Конечно все это требует моделирования, хотя бы потому, что недостаточно удачная сшивка полигонов переходными отверстиями может привести к большой неравномерности тока между переходушками и всяческие связанные с этим неприятности.

AndrewN

28.08.2016 09:22Из ПУЭ.

На таких токах 10 А/мм? уже в несколько раз превышает длительно допустимый ток

Теплоотвод зависит от площади поверхности шины, т. е. пропорционален периметру сечения, а площадь сечения — это квадратичная функция от стороны.

Поэтому допустимая плотность тока никак не постоянна, а уменьшается при увеличении сечения.

275/60=4,58 А/мм?

Paging

28.08.2016 15:04Теплоотвод зависит не только от площади поверхности, но и от наличия принудительного охлаждения например (не надо забывать, что в нашем случае система продувается вентиляторами). Кстати в плане площади поверхности полигоны в плате очень хороши — отношение площади к сечению очень велико.

В общем, как я уже говорил, конечно же эти вещи моделируются.

sav6622

PCB платы такого уровня в России делаете?

maxf75

Разрабатываем здесь, производство пока не здесь, причин тому много.