Итак расписания:

Сначала Алма-Ата.

18-20 октября 2016 — Алма-Ата, Казахский национальный технический университет имени К. И. Сатпаева.

Главный организатор — Кафедра автоматизации и управления КазНИТУ, в партнерстве с Almaty Management University.

Емейл для регистрации на комбинированный семинар по MIPSfpga и Connected MCU — seminar-kazntu@silicon-kazakhstan.com.

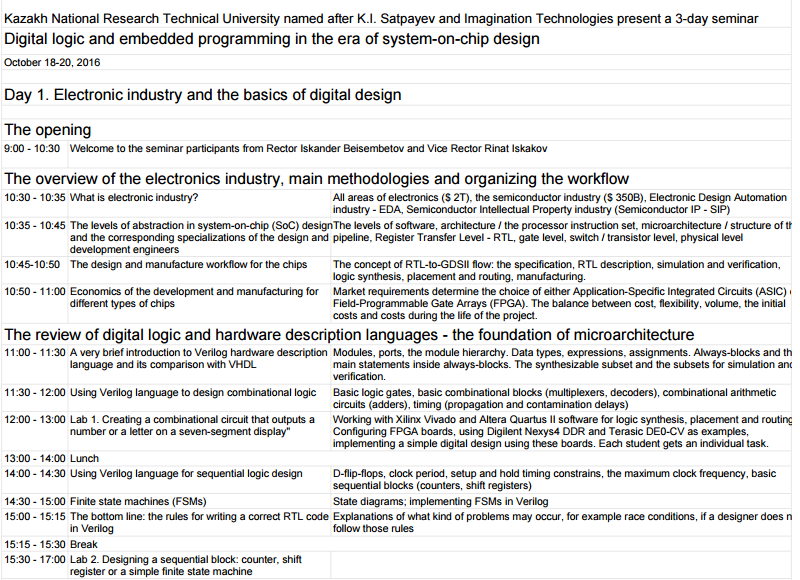

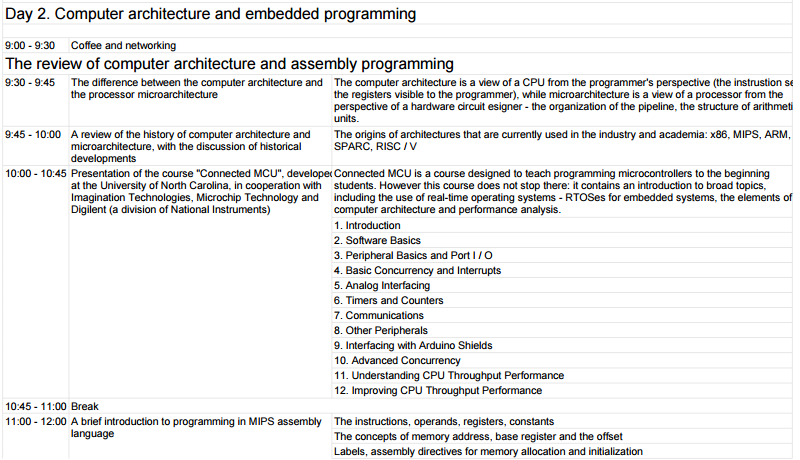

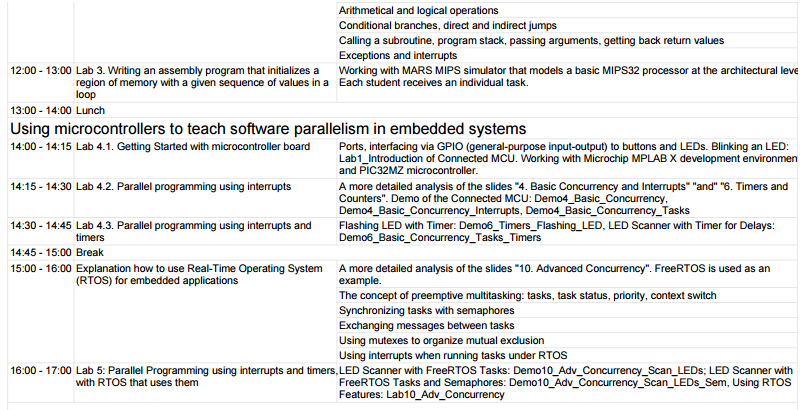

Алма-атинцы попросили сделать семинары на английском, посему вот вам расписание трехдневных семинаров на английском:

Даты и контактная информация про семинары в России и Украине приведена в посте Микросхемы с разных сторон: семинары Nanometer ASIC, MIPSfpga и Connected MCU в России, Украине и Казахстане. Кратко:

- 18-20 октября 2016 — Алма-Ата, КазНИТУ (в партнерстве с Almaty Management University) — MIPSfpga и Connected MCU — seminar-kazntu@silicon-kazakhstan.com

- 24 октября 2016 — Москва, МГУ — MIPSfpga и немного Connected MCU — seminar-msu@silicon-russia.com

- 25 октября 2016 — Долгопрудный, МФТИ — MIPSfpga и немного Connected MCU — seminar-mipt@silicon-russia.com

- 26 октября 2016 — Зеленоград, МИЭТ — MIPSfpga и немного Connected MCU — seminar-miet@silicon-russia.com

- 27 октября 2016 — Москва, компания Наутех (ООО «Наукоемкие Технологии») — MIPSfpga и немного Connected MCU — seminar-nautech@silicon-russia.com

- 28 октября — серия докладов на конференции SECR в Москве по тематике, связанной с семинарами Imagination Technologies и Наутеха

- 31 октября — 1 ноября 2016 — Москва, МИСиС / ФИОП РОСНАНО / eNANO — Nanometer ASIC — Yulia.Osaulets@rusnano.com, можно с копией на seminar-misis@silicon-russia.com

- 2 и 3 ноября 2016 — Санкт-Петербург, ИТМО — Nanometer ASIC — seminar-itmo-nanometer-asic@silicon-russia.com

- 7 ноября 2016 — Санкт-Петербург, ИТМО — MIPSfpga и немного Connected MCU — seminar-itmo-mipsfpga@silicon-russia.com

- 9 и 10 ноября 2016 — Киев, КПИ / Lampa / Belka — Nanometer ASIC — seminar-kpi-nanometer-asic@silicon-ukraine.com

- 11 ноября 2016 — Киев, КПИ / Lampa / Belka — MIPSfpga и немного Connected MCU — seminar-kpi-mipsfpga@silicon-ukraine.com

- 12 ноября 2016 — Киев, КПИ / Lampa / Belka — Хакатон по MIPSfpga — hackathon-kpi@silicon-ukraine.com

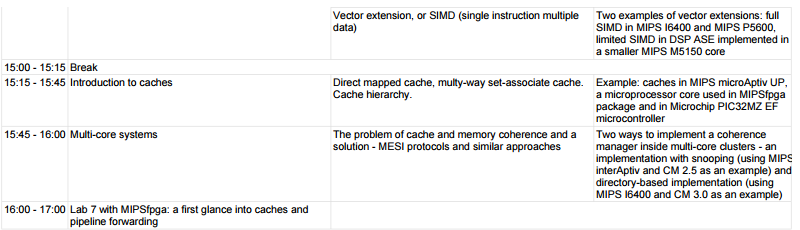

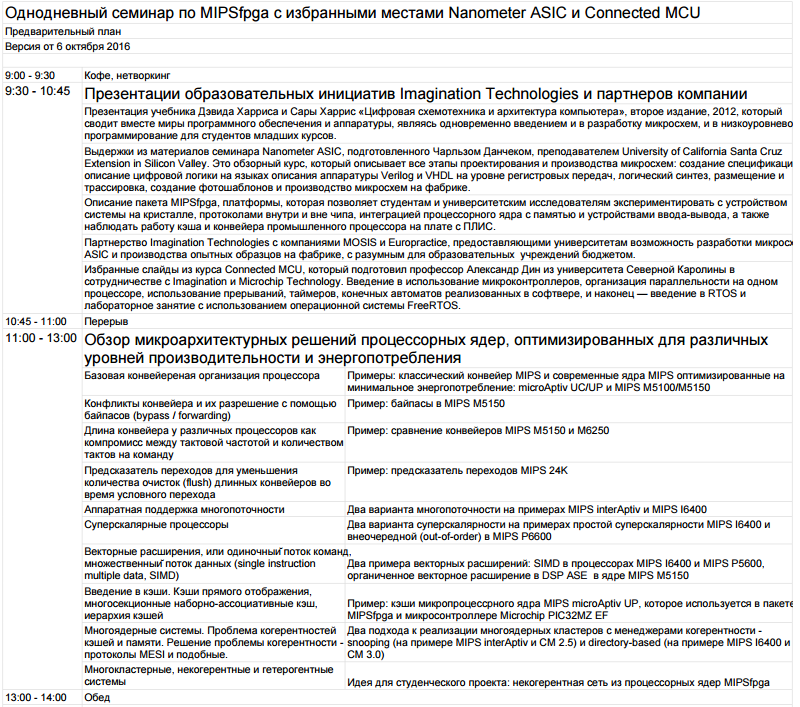

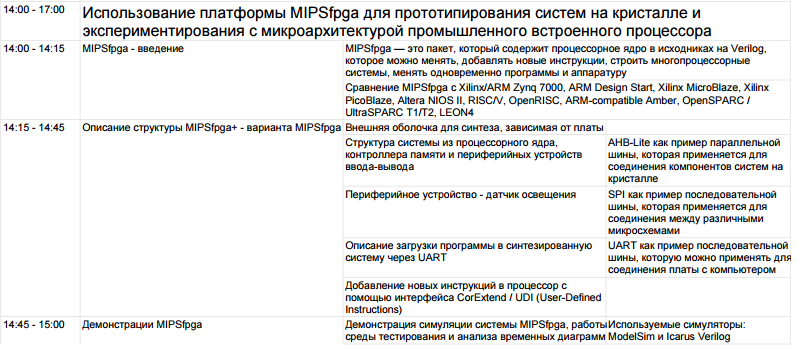

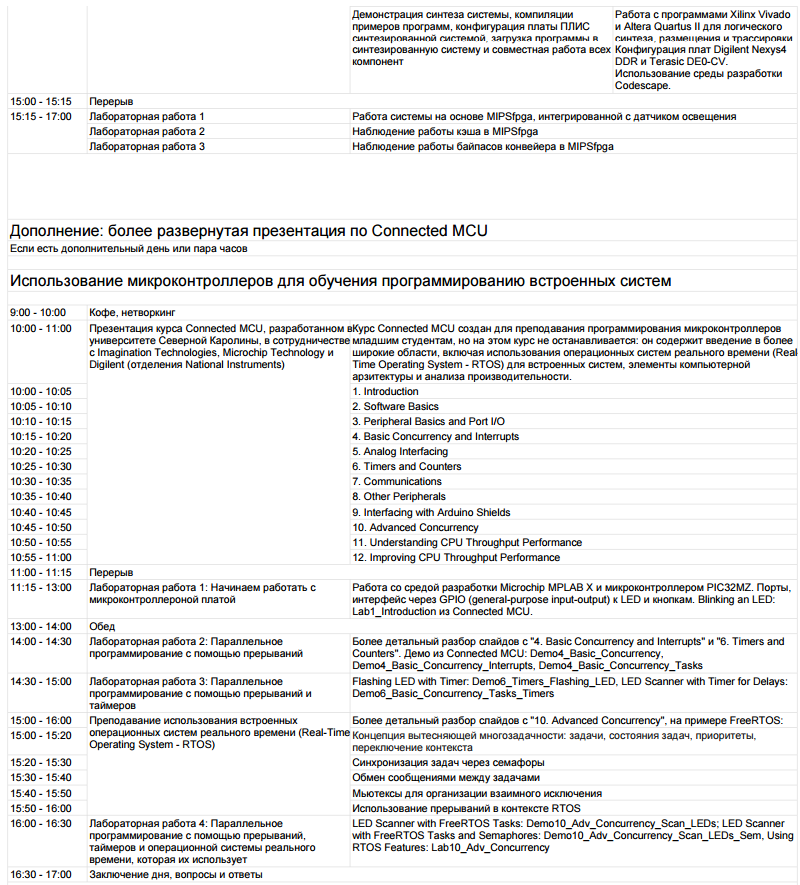

Предварительное расписание однодневных семинаров по MIPSfpga в МГУ, МФТИ, МИЭТ, ИТМО и КПИ стоит ниже. В конце стоит инфо про возможный дополнительный день, который теоретически может возникнуть в МГУ в дополнение к текущему расписанию:

Про семинар Nanometer ASIC недавно пост уже был ( habrahabr.ru/post/311662 ) и будет еще один, так как к семинару может быть сделано добавление. Текущее расписание — http://edunano.ru/doc/6335690702352234538.

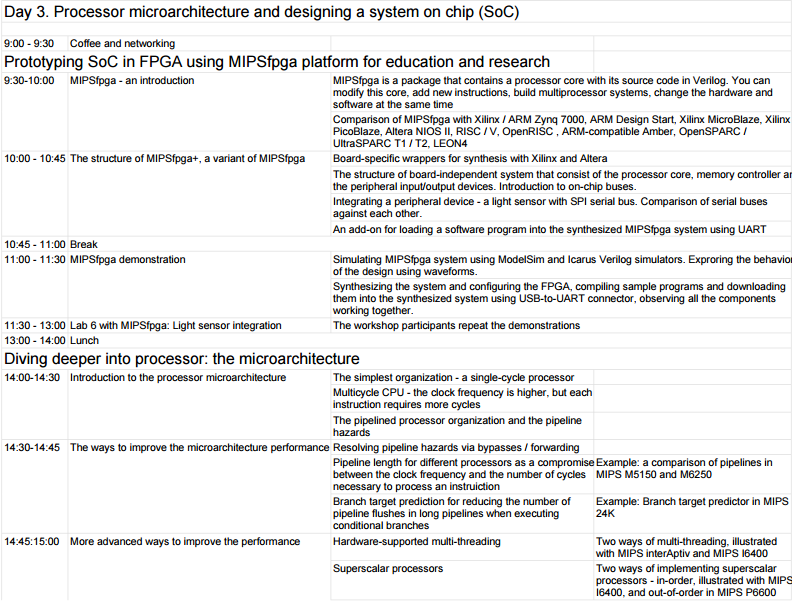

А теперь несколько диаграмм конвейеров встроенных микропроцессорных ядер, оптимизированных под разный баланс производительности, максимальной тактовой частоты и энергопотребления. Об этом мы поговорим немного в каждом из семинаров:

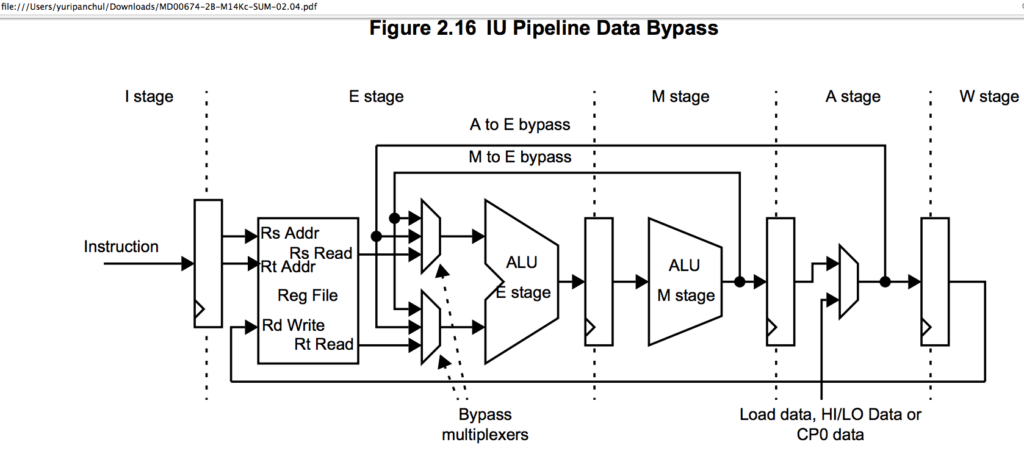

Короткий конвейер, невысокая максимальная тактовая частота, зато низкое энергопотребление:

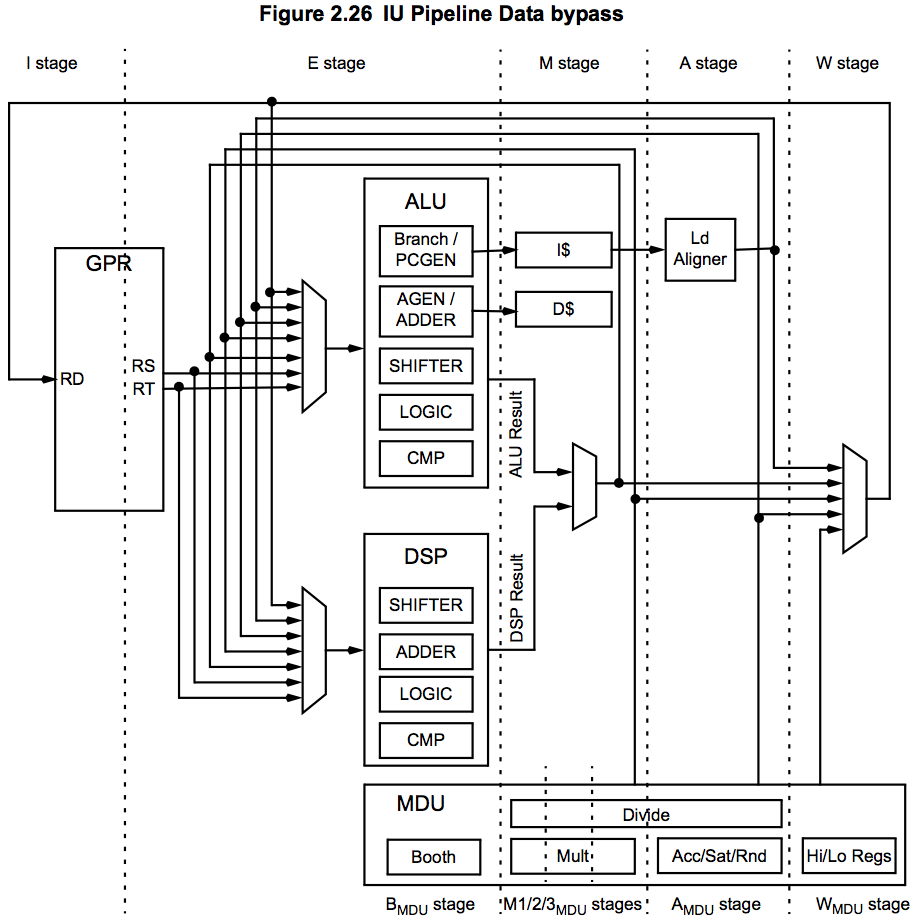

Конвейер чуть длиннее, зато максимальная тактовая частота повыше:

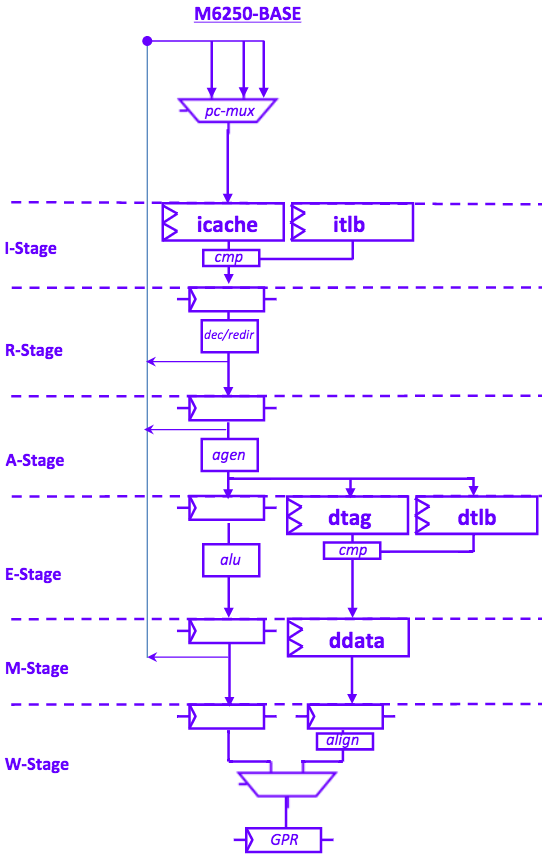

А вот процессор оптимизированный на эффективность (достаточно высокая производительность при невысоком энергопотреблении):

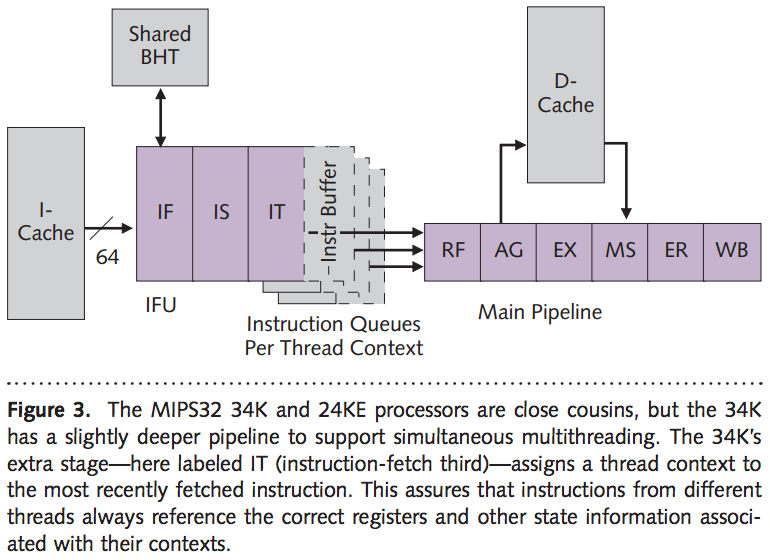

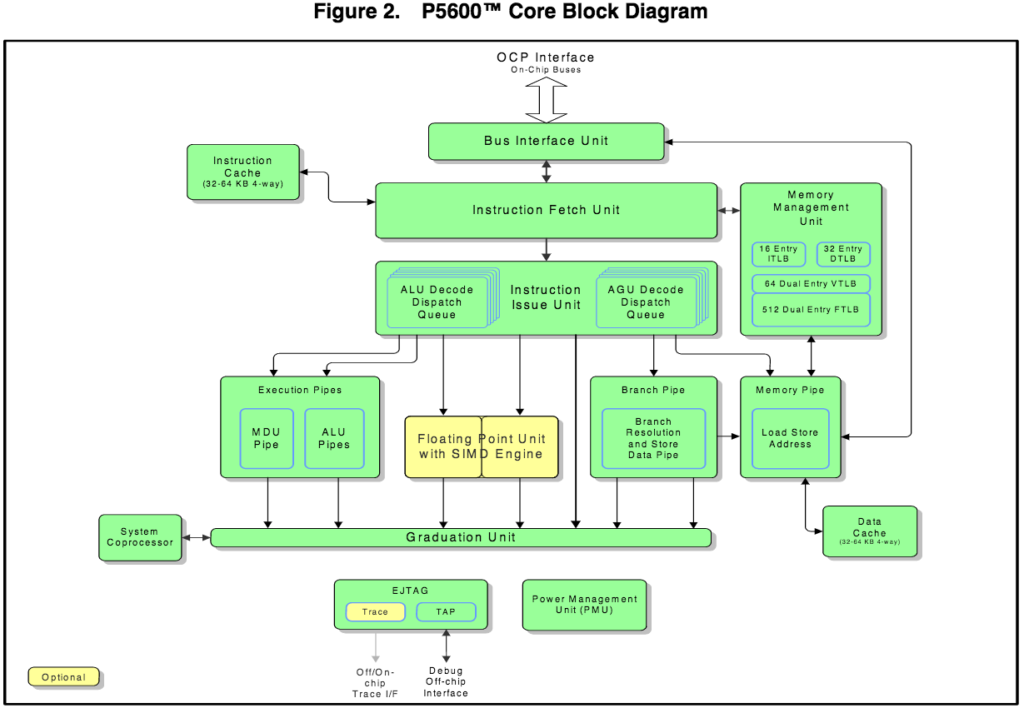

Оптимизирован на скорость: суперскаляр с OoO:

До встречи!

Комментарии (10)

nckma

12.10.2016 10:11+2А как же Ростов/Казань/Новосибирск?

Эх… за КАДом жизни нет.

Halt

12.10.2016 11:09+1За Новосибирск всеми конечностями!

P.S.: Алма-Ата далеко за пределами КАДа и тем не менее. Видимо, все дело в организации и желании.

YuriPanchul

12.10.2016 17:03Девушка на фото из новосибирского Академгородка кстати. В следующем посте от нее будет речь, в частности про Новосибирск

Varkus

12.10.2016 14:51-2Хотел почитать статью, но в первом абзаце увидел РОСНАНО, далее вспомнил слова Чубайса в кризисный год:

https://life.ru/t/новости/176551 и не стал читать статью, жаль.

square

12.10.2016 19:27+2Хотел перевести бабушку через дорогу, но вспомнил, что в России плохие дороги и не стал переводить, жаль

antonsosnitzkij

12.10.2016 22:46В семинарах информация о Xilinx, а на фото — Altera (^:

YuriPanchul

12.10.2016 22:48MIPSfpga идет и на Xilinx, и на Altera. В России и Украине для образовательных целей лучше использовать Altera, так как сейчас импорт учебных плат с Xilinx Artix-7 — геморой.

Alexeyslav

Чайка на КДПВ супер!

YuriPanchul

Вы еще увидите видео с девушкой :-)