Хакатон в КПИ по MIPSfpga был экспериментальным в том смысле, что обычно в хакатонах участники или просто программируют (например решения SaaS), или делают устройства из готовых фиксированных микросхем и программируют их (Ардуино, STM32 Discovery). Здесь же участники и писали программу, и разрабатывали схему, интерфейсный блок на уровне регистровых передач (Register Transfer Level — RTL), после чего встраивали этот блок в синтезируемую систему с процессорным ядром MIPS microAptiv UP и шиной AHB-Lite, и реализовывали эту систему в FPGA.

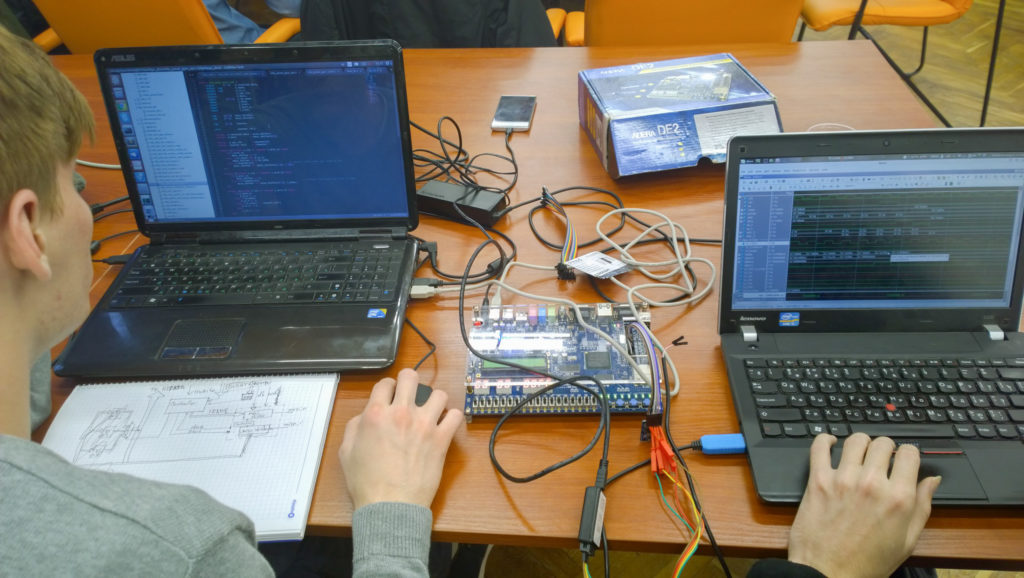

Вот как это выглядело на экранах их ноутбуков, на FPGA-плате и концептуально:

Зачем нужны такие задачи?

Такие упражнения помогут вырастить инженеров систем, знакомых и с разработкой схемотехники, и с программированием, что необходимо в 21 веке, эпохе систем-на-кристалле (СнК — System-on-Chip, SoC). Также это путь к прототипированию специализированных микросхем ASIC (Application Specific Integrated Circuits), таких же, которые стоят в разнообразных встроенных системах — от кофеварок до спутников. Потом украинские исследователи в КПИ и КНУ смогут работать с европейским сервисом Europractice и производить опытные микросхемы на фабрике через MPW shuttle. Если при этом исследователи придумают что-нибудь коммерчески интересное, то они могут использовать такой прототип для привлечения венчурного капитала и создания стартапов в определенных нишах, например нише «умных датчиков» для интернета вещей.

Фотографии и видео с хакатона

Перед хакатоном по MIPSfpga было три дня семинаров Nanometer ASIC и лекций по MIPSfpga. На Nanometer ASIC записалось больше сотни человек и пришло более восьмидесяти:

На лекционную часть про MIPSfpga тоже пришло довольно много людей, причем опрос выявил, что среди них довольно много владеют Verilog, знаниями про архитектуру и микроархитектуру:

На хакатон остались самые целеустремленные:

С фейсбука ключевого организатора хакатона (Відкрита лабораторія електроніки Lampa КПИ):

… А пока вот видосик с одним из победителей, Денисом Солдатовым, который первым закончил разработку устройства и получил в подарок плату DE0-CV и фирменную флешку MIPSfpga.

Денис интегрировал ультразвуковой дальномер от Digilent (https://goo.gl/Txoxl6) в систему-на-кристалле MIPSfpga. Написал на Verilog интерфейсный модуль, который работает с сенсором по аппаратному uart и имеет управляющие регистры, отображенные в адресное пространство MIPSfpga посредством шины AMBA. Также Денис написал управляющую программу, которая считывает показания датчика из упомянутых регистров и при превышении порога подает звуковой сигнал определенной частоты. ...

Фоточки с еще одной командой победителей!

Сергей Сачов и Валера Марченко интегрировали в систему-на-кристалле MIPSfpga клавиатуру от Digilent (https://goo.gl/Xmbba6). Ребята написали на Verilog интерфейсный модуль, который работает с клавиатурой по 16-пиновому интерфейсу и имеет регистр, содержащий код нажатой клавиши, отображенный в адресное пространство MIPSfpga посредством шины AMBA. Также была написана управляющая программа, которая считывает код нажатой клавиши из упомянутого регистра и выводит соотвествующее клавише число на семисегментный индикатор.

И еще одна команда:

Посмотреть 50 фотографий с Nanometer ASIC и MIPSfpga в Киеве

Теперь поговорим про техническую часть.

Предварительные разъяснения к технической части

Пару слов для тех читателей, которые не знакомы с тем, что такое Verilog, ASIC и FPGA:

Из поста на Geektimes «Оруженосцы микроэлектроники. Видеорепортаж с конференции по проектированию электроники в Сан-Франциско»:

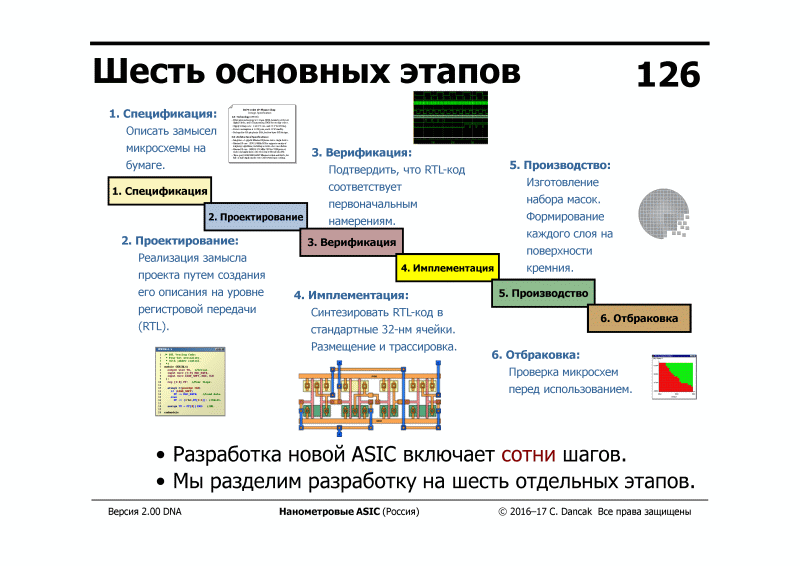

Пока мы обсудили кульминацию микроэлектронного проекта — изготовление микросхемы на фабрике. Но как такой проект начинается?

В последние 25 лет дизайн микросхемы чаще всего пишется на языке описания аппаратуры Verilog ([ранее] в Европе и у военных — VHDL), после чего специальная программа (logic synthesis) превращает дизайн в граф из проводов и логических примитивов, другая программа (static timing analysis) сообщает дизайнеру, вписывается ли он в бюджет скорости, а третья программа (place-and-route) раскладывает этот дизайн по площадке микросхемы.

Когда дизайн проходит все этапы: кодирование на верилоге, отладка, верификация, синтез, static timing analysis, floorplanning, place-n-route, parasitics extraction и т.д. — получается файл под названием GDSII, который отправляют на фабрику, и фабрика выпекает микросхемы. Самые известные фабрики этого типа принадлежат компании Taiwan Semiconductor Manufacturing Company или TSMC.

Из поста на Habrahabr Как начать разрабатывать железо, используя ПЛИС — пошаговая инструкция:

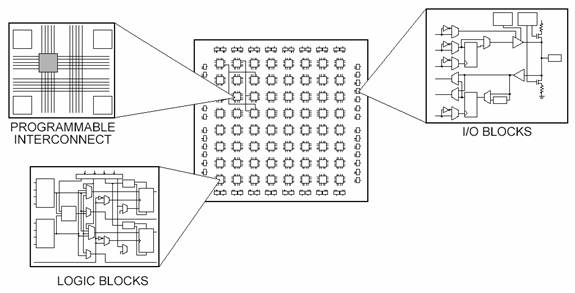

В самом простом варианте FPGA состоит из матрицы однородных ячеек, в функцию каждой из которых можно поменять с помощью мультиплексоров, подсоединенных к битам конфигурационной памяти. Одна ячейка может стать гейтом AND с четырьмя вводами и одним выводом, другая — однобитным регистром и т.д. Загружаем в конфигурационную память последовательность битов из памяти — и в FPGA образуется заданная электронная схема, которая может быть процессором, контроллером дисплея и т.д.

ПЛИС-ы / FPGA — не процессоры, «программируя» ПЛИС (заполняя конфигурационную память ПЛИС-а) вы создаете электронную схему (хардвер), в то время как при программировании процессора (фиксированного хардвера) вы подсовываете ему цепочку написанных в память последовательных инструкций программы (софтвер).

Если вы хотите изучить такой материал с нуля, вы можете бесплатно скачать Harris & Harris, чрезвычайно популярный учебник, скачивание русского перевода которого положило британский сайт Imagination два раза (первый раз, второй раз).

Если учебник для вас слишком большой и вам хочется просто бегло понять основные концепции, вы можете скачать набор слайдов (тоже бесплатно), которые помогают преподавателям читать лекции на основе Harris & Harris. Эти слайды являются дополнением к учебнику, они также эффективны для самообразования и быстрого введения в предмет.

И наконец, по пожеланиям читателей, в дополнение к бесплатной электронной версии Harris & Harris, в новогоднюю ночь выйдет бумажная версия Harris & Harris, правда не бесплатная (целлюлоза дороже электронов):

Правда Харрис-энд-Харрис помогает в основном если вы хотите изучить фронт-энд (то бишь логическое проектирование цифровых микросхем и микроархитектуру). Если же вы хотите получить ликбез по физической части проектирования и производства, то вы можете скачать перевод на русский язык слайдов Чарльза Данчека.

Кроме этого, eNANO (дочка РОСНАНО по образовательным программам) собирается добавить видео лекций Чарльза Данчека (с синхронным переводом на русский) вот в этот каталог:

Но вернемся к хакатону в КПИ:

Организация хакатона

Главными организаторами хакатона были Кафедра конструирования электронно-вычислительной аппаратуры Факультета электроники КПИ, Відкрита лабораторія електроніки Lampa КПИ, Студентський простір Belka и Кафедра компьютерной инженерии Факультета радиофизики, электроники и компьютерных систем Киевского национального университета имени Тараса Шевченко.

На фотографии слева доцент Киевского Университета КНУ Александр Барабанов, он переводил на русский язык часть Harris & Harris, а также значительную часть материалов по MIPSfpga, Nanometer ASIC и Connected MCU. Справа Евгений Короткий, руководитель Лампы КПИ:

Шановні учасники хакатону, привіт!

Сподіваємось ви вже ознайомились з MIPSfpga та переліком периферії запропонованої для інтеграції.

Кілька організаційних моментів.

Задача хакатону.

Необхідно інтегрувати периферійний пристрій в систему на кристалі на основі MIPSfpga. Інтеграція полягає у відображенні регістрів периферійного пристрою в адресний простір MIPSfpga. Необхідно написати на Verilog / VHDL періфеійний модуль, який буде висіти на шині AHB-Lite, буде містити набір регістрів, що повторюють регістри пристрою і синхронізувати вміст цих регістрів з регістрами пристрою. Ну і виконувати обмін даними з пристроєм по протоколу цього пристрою. Також треба буде написати програму для MIPSfpga, що демонструє роботу з периферійним пристроєм.

Оновлений перелік периферійних пристроїв:

https://docs.google.com/spreadsheets/d/1djURILzdHSwnvxC5SzO4izU2imyimAgjOuqXAef6-rQ/edit?usp=sharing

Однак ми вирішили не обмежуватись лише інтеграцією периферійних пристроїв. Якщо у вас виникнуть інші цікаві ідеї проектів на основі MIPSfpga, надішліть їх на цю поштову адресу.

Команди.

У нас буде 14 FPGA плат на які портовано MIPSfpga (9 плат DE2, 1 плата DE1, 4 плати DE0-CV). Тому максимум може бути 14 команд. Ви можете принести власну fpga плату з переліку тих, на які портовано MIPSfpga (перелік тут:

https://github.com/MIPSfpga/mipsfpga-plus/tree/master/boards), або якусь іншу fpga плату (тоді вам доведеться додактково портувати на неї MIPSfpga і це буде додатковим плюсом), максимальна кількість команд може бути збільшена.

Ви уже можете формувати команди. Список периферії для інтеграції відкритий для реагування:

https://docs.google.com/spreadsheets/d/1djURILzdHSwnvxC5SzO4izU2imyimAgjOuqXAef6-rQ/edit?usp=sharing

Щоб потрапити до команди з інтеграції певного пристрою впишіть своє прізвище в стовбчик «Команда». У випадку наявності в команді кількох учасників вписуйте прізвища через кому. Людина яка зареєструється першою стає капітаном команди. Звертаємо вашу увашу, що у гугл таблиць доступна вся історія редагування.

Таймінги хакатону.

Починаємо о 8-й ранку. Протягом дня у нас буде два обіди і дві менторські сесії, протягом яких будемо оцінювати прогрес (час ментрських сесій уточнимо трохи пізніше, оскільки це поки не принципово). Також протягом дня можете вільно задавати запитання менторам (Юрій Панчул, Короткий Євген) з питань цифрового дизайну, MIPSfpga та його програмування.

Презентації створених проектів починаються о 20-й годині.

Презентація являє собою демонстрацію роботи пристрою, протягом якої ви розказуєте, що було зроблено. Для презентації можете користуватися проектором. В презентації та демонстрції може приймати участь кілька людей. Тривалість презантації — 3 хвилини. О 20-45 завершуємо презентації. Приблизно о 21-00 оголосимо переможців та роздамо призи всім учасникам.

Призи.

Головний приз — плата Altera DE0-CV з числа тих, що використовувались у хакатоні. Якщо ми не зможемо визначитись з кращим проектом, подаруємо плати двом кращим командам. Зверніть увагу, що головний приз дарується команді. Як ви його ділитимете — на ваш розсуд. Також усі учасники отримають заохочувальні призи, про які ви дізнаєтесь під час нагородження. Єдине що можемо зараз сказати — вони точно будуть вам корисні.

Їжа.

Протягом хакатону буде дві перерви на обід. Їжу придбаємо в Noodle Doodle:

https://eda.ua/restorany/lapsha-bar-noodle-doodle?gclid=CjwKEAiAr4vBBRCG36e415-_l1wSJAAatjJZgqN6K9uVvj4_XnQRioEBzgScrYK6BNi0lZb-HWTfbxoCZDzw_wcB

Якщо у вас є побажання по стравам, можете надіслати їх Дмитру

(https://vk.com/im?sel=75362095) до вечора п'ятниці. Можна обрати якусь одну страву на кожен з двох прийомів їжі.

До зустрічі на хакатоні)

— З повагою,

Організатори заходу

Пример для участников — датчик освещения

В качестве примера участникам хакатона был показан код для интеграции датчика освещения — Digilent PmodALS — Ambient Light Sensor. Вот так выглядит датчик:

Для передачи данных датчик использует последовательный протокол SPI. Вариант протокола, используемого сенсором — довольно прост; его описание в документации с сайта компании-производителя Digilent занимает всего два абзаца текста:

Заметим, что протокол сенcора (SPI) — последовательный, а протокол шины процессора (AHB-Lite) — параллельный. Сравним:

По протоколу SPI данные передаются и принимаются бит за битом. Это экономит количество сигналов, что важно для протоколов, передающих данные между микросхемами:

По протоколу AHB-Lite биты данных передаются параллельно. Кроме этого, данные в этом протоколе связаны с адресом, причем биты адреса тоже передаются параллельно. Вот диаграммы для части сигналов транзакций чтения и записи на шине AHB-Lite:

Чтение:

Запись:

Для интеграции сенсора в систему нужно спроектировать три компонента:

- Хардверный модуль, который принимает данные по протоколу SPI и складирует их в некоторый регистр текущего значения. Код на верилоге для этого модуля находится в файле, а также ниже.

- Код на верилоге для передачи данных из этого регистра по шине AHB-Lite в процессорное ядро для обработки данных софтвером, так сказать glue code. Его можно найти в файлах директории, если сделать поиск по строке `ifdef MFP_DEMO_LIGHT_SENSOR..

- Софтвер, работающий на процессорном ядре, который принимает данные с датчика освещения и как-то их использует, например выводит значение освещенности на 7-сегментный индикатор на FPGA плате. Это небольшая программа на Си, которая компилируется с помощью стандартной GCC toolchain и линкуется с кодом для инициализации, написанным на ассемблере — см. тут.

Код на верилоге для хардверного модуля, который принимает данные по протоколу SPI и складирует их в регистр текущего значения:

Вот в какую схему превращается этот код во время логического синтеза с помощью Altera Quartus II версии 16.0 (после анализа, но перед mapping-ом и оптимизацией):

Выводы и планы на будущее

Хакатон по MIPSfpga оказался еще более интересным мероприятием для всех участвующих, чем ожидалось:

- Хакатон не был очень легким — к финишу пришли не все, а меньше половины команд

- Хакатон не был очень тяжелым — две команды пришла уверенно, еще одна-две — с некоторыми натяжками

- В процессе хакатона участники сделали кучу ошибок как новичков, так и более продвинутых разработчиков, в частности:

- Тривиальная ошибка новичка: Перепутывание вводов и выводов

- Недопонимание механизма работы Verilog-а: Сдвиг на цикл тактового сигнала из-за непонимания концепции дельта-циклов и ожидания немедленного изменения внешнего сигнала внутри комбинационного always-блока в ответ на присваивание сигналу, от которого зависит внешний сигнал через continuous assignment

- Недопонимание методологии Register Transfer Level Methodology (RTL): использование контрольных сигналов в «always @(posedge control_signal) ...» вместо «always @(posedge clock)… if (control_signal) ...»

- Неправильные timing constraints

- Нашли даже ошибку в в коде пакета MIPSfpga!

Посему есть идея повторить такой Хакатон в других странах. Для повторения в России: в Москве лежит 16 плат Altera / Terasic DE0-CV, которые можно использовать для таких мероприятий. В Казахстане и Украине тоже можно чего-нибудь придумать. Если есть идеи, просьба сообщать в комментариях.

Только зарегистрированные пользователи могут участвовать в опросе. Войдите, пожалуйста.

Комментарии (20)

unixwz

28.11.2016 14:21+2Замечательный хакатон, приезжайте в Пензу. У нас есть целое предприятие которое ведет разработку хардвеера на базе ПЛИС, участники явно найдутся.

А то на наших местных хакатонах один JS и прочее, для хардварщиков инфраструктура очень плохо развита. Даже если придешь с "железным" проектом на хакатон, то мало кто из участников поймет в чем суть.

valeriyk

28.11.2016 21:33И в электронном, и в планируемом печатном варианте книги про архитектуру компьютера так и не определились, зовут ли авторов Харрис или Хэррис. И там, и там используются оба варианта.

roscha

30.11.2016 23:12… в Киеве...

дальше не читал.

YuriPanchul

30.11.2016 23:13А чего так? Закон Ома и булевская алгебра в Киеве те же, что и в Москве, и в Санта-Клара, Калифорния.

tangro

07.12.2016 17:37«Хакатон нового типа» очень смахивает на одну из десятков лабораторок по какой-нибудь схемотехнике, которые довелось делать по ходу учёбы в универе.

YuriPanchul

07.12.2016 20:00У вас были лабораторные работы с интеграцией написанного вами блока на верилоге с микропроцессорным ядром в синтезированной системе? Каким именно ядром? На какой FPGA плате? Вам давали готовый модуль на верилоге или документацию на устройство с требованием написать блок? Нельзя ли подробностей?

tangro

07.12.2016 22:48Я так понимаю, что по Вашему мнению студенты на лабах нынче святое писание по молебнику учат? Или вот все эти пришедшие на несколько-часовой марафон студенты — до этого всё это железо и софт в руках не держали, а тут впервые увидели и понеслось?

YuriPanchul

07.12.2016 23:35Нет, вы меня не поняли. Я задал не риторический вопрос, а информационный. Я в курсе, что студенты украинских вузов проходят курсы, на которых они делают лабы со штуками типа дизайн мультиплексора или там интеграция периферийного устройства с микроконтролером. Ну упражнения, которые я описал в посте — это не то же самое. Поэтому я и спрашиваю, что вы писали на лабах на RTL и какие использовали soft cores. Это мне нужно для моего понимания, а не чтобы вас переспорить.

AnotherReality

08.12.2016 00:44схемотехнической (Verilog) частей системы

Вопрос: ааа, что за такая схемотехническая часть и коим образом она относится к языку описания аппаратуры?

YuriPanchul

08.12.2016 00:46Я написал выше:

В последние 25 лет дизайн микросхемы чаще всего пишется на языке описания аппаратуры Verilog ([ранее] в Европе и у военных — VHDL), после чего специальная программа (logic synthesis) превращает дизайн в граф из проводов и логических примитивов, другая программа (static timing analysis) сообщает дизайнеру, вписывается ли он в бюджет скорости, а третья программа (place-and-route) раскладывает этот дизайн по площадке микросхемы.

Когда дизайн проходит все этапы: кодирование на верилоге, отладка, верификация, синтез, static timing analysis, floorplanning, place-n-route, parasitics extraction и т.д. — получается файл под названием GDSII, который отправляют на фабрику, и фабрика выпекает микросхемы. Самые известные фабрики этого типа принадлежат компании Taiwan Semiconductor Manufacturing Company или TSMC.

См. http://www.silicon-russia.com/public_materials/2016_11_04_one_day_mipsfpga_connected_mcu_materials_public_for_the_website/02_explain_the_concept_of_rtl_to_gdsii_flow/ruscitech_yuri_panchul_imgtec_march_2014_with_appendix.pptx

начиная со слайда 12

Далее:

В самом простом варианте FPGA состоит из матрицы однородных ячеек, в функцию каждой из которых можно поменять с помощью мультиплексоров, подсоединенных к битам конфигурационной памяти. Одна ячейка может стать гейтом AND с четырьмя вводами и одним выводом, другая — однобитным регистром и т.д. Загружаем в конфигурационную память последовательность битов из памяти — и в FPGA образуется заданная электронная схема, которая может быть процессором, контроллером дисплея и т.д.

ПЛИС-ы / FPGA — не процессоры, «программируя» ПЛИС (заполняя конфигурационную память ПЛИС-а) вы создаете электронную схему (хардвер), в то время как при программировании процессора (фиксированного хардвера) вы подсовываете ему цепочку написанных в память последовательных инструкций программы (софтвер).

См. https://habrahabr.ru/post/250511

AnotherReality

08.12.2016 01:42Ухты, спасибо за пояснение. Я занимаю трассировкой и оттого некий диссонанс в терминологии возник =) но в университете нам не так объясняли. Грустно, но факт, мы изучали железо без железа. Потому такие мероприятия (хакатоны) безусловно полезны из-за дефицита специалистов на отечественном рынке и не очень хорошая подготовка в университетах

ittakir

Сколько стоит та отладочная плата, которую использовали?

Сколько стоит и сколько потребляет та FPGA? Корпус только BGA?

Понимаете, то что делали эти ребята, не приближает их ни на шаг к созданию устройств «IOT». Можно делать гораздо проще, быстрее, эффективнее на микроконтроллере. Он будет просыпаться, опрашивать датчик по аппаратному SPI, и снова засыпать, в среднем потребляя микроамперы. Стоимость такого решения будет меньше 100 руб, детали легко купить в любом магазине.

Если бы я был VC и ко мне бы пришли 2 человека и принесли бы 2 прототипа, одно на отладочной плате FPGA, другое спаяно на коленке на самом доступном микроконтроллере. Догадайтесь, чей бы проект я проспонсировал. Тот, который реально собрать в наших условиях и продать не только военным или в госкомпанию, а обычным рядовым гражданам.

Кстати, ничего не имею против FPGA в целом, просто область применения у нее куда более хардкорная. Стереокамеры для VR системы — отлично. 64 канальный анализатор сигналов — самое то. Коммутация гигабитных Ethernet пакетов.

Повысьте уровень ваших уроков. Сделайте проект, который загоняет в плату поток с двух камер и строит карту глубины. Да, это не для новичков. Но и не будет ощущение фуфлагонства.

YuriPanchul

Я прошу вас прочитать пост внимательно.

Никто не предлагает строить устройства для интернета вещей на основе FPGA как таковых.

FPGA предлагается как платформа для обучения инженеров, которые будут в будущем проектировать чипы, ASIC-и, в том числе микроконтроллеры.

Это мейнстрим последних 25 лет. Инженеры-проектировщики чипов для интернета вещей, например чипов от Media Tek, в процессе своего обучения проходят через лабы на основе FPGA плат. Везде — от Беркли и Стенфорда до провинциального Университета Монтаны.

К инвесторам предлагается идти не с устройством для IoT, а с прототипом чипа, который можно будет продавать компаниям, которые «на коленке» как сказали, будут делать прототипы устройств для IoT

ittakir

Хорошо, не подскажете пример таких вот вчерашних студентов, сделавших в свободное от работы время чип для IOT (что это, кстати, RF передатчик?), получивших финансирование, и затем изготовивших его на фабрике в Тайване и успешно продавших всю партию?

Сдается мне, что это удел очень крупных компаний с бюджетами в миллиарды долларов, а никак не студентов.

Если же предлагается просто втянуть таким образом людей в мир FPGA, чтобы они работали винтиками в большой корпорации, то так и пишите, зачем обманывать(ся).

SADKO

Успешно пройти путь от дизайна до распродажи чипов, на моей памяти такое было только у разработчиков ASIC-ов, некоторые из которых действительно были студентами на момент событий тех…

Вы видимо сами далеки от темы, (не узнали популярнейшую плату, считаете сложными простые для железячника задачи, итд) а правда в том, что дизайнеры чипов, либо на зарплятах у производителей и крупных дизайн хаусов, либо пашут в одиночку или в группе единомышленников, а результаты своего труда продают в виде блоков, так и живём собственно…

Лично мне инициатива таких хактонов нравится с точки зрения раскачки мозгов, расшатывания границ возможного. Да FPGA это ремесло, но если у вас есть какие-то иные таланты, то это может стать востребованным искусством, та же обработка изображений.

ittakir

Что я считаю сложным? Прокинуть чтение SPI датчика в параллельную шину — нет, не сложно. В 99% устройств и не нужно. Написать одному вечерами конкурентоспособный RF чип, на который можно получить реальное финансирование — практически невозможно.

Буду честен. Хотел написать, что фрилансеров на FPGA практически нет. Но перед этим решил проверить Upwork. Все таки есть. https://www.upwork.com/o/jobs/browse/?page=1&q=fpga

24 заказа за год. Больше чем stm32 (11), avr(12). Я удивлен.

Для сравнения https://www.upwork.com/o/jobs/browse/?q=ruby 469 заказов.

SADKO

Я к тому, что технически работа с видео сенсорами, проста как коммутация гигабита на соответствующем железе, но начинается это всё с элементарной логики и велосипедостроения.

RF чипы не пишут, пишут, только их логические «свистоперделки», а дизайн RF и вообще аналога, это отдельная тема сильно завязанная на производство.

Нашли где искать заказы\исполнителей на FPGA :-) говорю-же не в теме