Здравствуйте, друзья.

Возвращаемся к публикации последних событий из мира FPGA/ПЛИС. Ниже приведены несколько ссылок на новости, анонсы, вебинары, воркшопы, туториалы, видео и тд. Подобные новостные дайджесты есть, например, на хабе про php, почему бы и не сделать что-то подобное и для ПЛИС?

Мы решили вернуться к традиционному формату представления: картинка — заголовок/ссылка — небольшое описание

Новостная лента FPGA/ПЛИС сентябрь 2020

|

Начинающим: Выложены материалы Сколковской школы цифрового дизайна С 15-17 сентября 2020 в рамках выставки Чип-Экспо проводилась «СКОЛКОВСКАЯ ШКОЛА СИНТЕЗА ЦИФРОВЫХ СХЕМ НА VERILOG». Рады сообщить, что материалы этой школы — запись видеолекций и исходники заданий выложены в открытый доступ на Youtube. |

|

Релиз Quartus Prime Pro Edition: Version 20.3Intel FPGA выпустила информацию об обновлении программного обеспечения Quartus Prime версии Pro. В частности, в новой версии: |

|

Высокоуровневое программирование FPGA для терабитных линий связиЧто такое частота семплирования 5кГц? Для цифровой обработки сигналов даже на микроконтроллере такое число звучит вполне посильно. Однако, в задаче оптической связи между спуником и наземной станцией, где на последней расположен массив линз, каждая из которых фокусирует изображение на часть сенсора камеры ... |

|

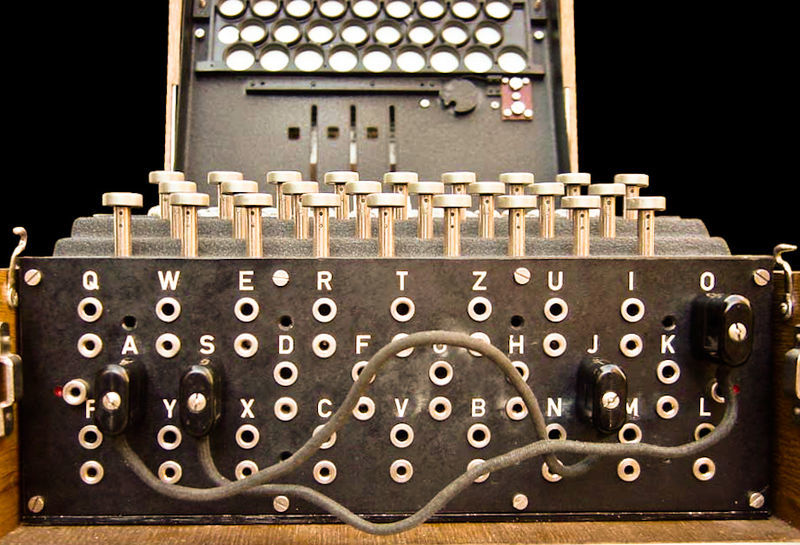

Это интересно: Шифровальная машина Enigma M3 в FPGA Intel MAX10Шифровальная машина имела систему роторов, которые по некоторому закону делали многократную замену букв: |

|

Онлайн конференция: Verification Day 2020Компания Synopsys проводит онлайн конференцию Verification Day 2020. Это виртуальное мероприятие дает возможность оставаться в курсе последних инноваций, методов и методологий в области статической, формальной и маломощной верификации. |

|

Вебинар: Презентация инструментов для верификации процессорных ядер на базе RISC-VStatic Verification for RISC-V Cores and SoCs В настоящее время вся отрасль разработки процессорных систем претерпевает смену парадигмы — новые поколения специализированных процессорных ядер разрабатываюся на основе открытой системы команд RISC-V. |

|

Реализация: Мондельбротим на PYNQПостроение фракталов на ПЛИС, в целом не ново. На выставках частенько можно встретить их реализацию. Такое демо всегда привлекает, не то что эти ваши отчеты в консоли и распознавание котиков. |

|

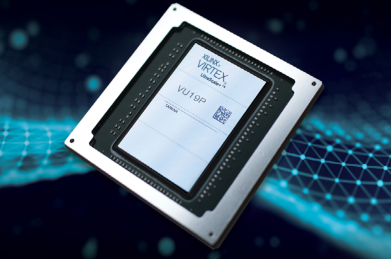

Анонс: Самая большая FPGA Xilinx перешла в статус ProductionПЛИС Virtex UltraScale+ VU19P позволяет создавать прототипы и эмулировать самые передовые ASIC и SoC, а также разрабатывать сложные алгоритмы. ПЛИС VU19P обладает самой высокой плотностью логики и количеством портов ввода-вывода — это самая большая FPGA когда-либо выпускаемая компанией Xilinx.... |

|

Практика: Подключаем Xilinx FPGA софт-процессор к сенсорам ST Microна портале element14.com появился анонс трех предстоящих воркшопов по работе с MicroBlaze — софт-процессор от компании Xilinx и его интеграции с несколькими сенсорами от компании ST Micro. Работа будет проходить на бюджетном отладочном комплекте Arty-S7. |

|

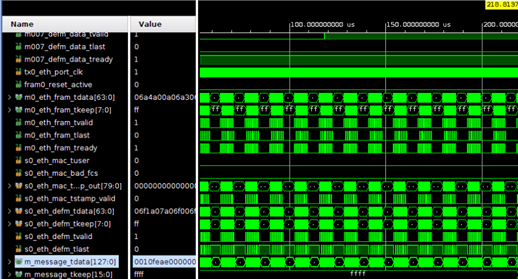

Туториал: Демонстрация и моделирование RoEВ блоге компании Xilinx появилось новое руководство по моделированию радио-через-ethernet — Roe |

|

Это Интересно: Как устроена первая ПЛИС в миреРеверс инжиниринг — тема очень занятная. На этой неделе появилась статья о том, как была устроена первая ПЛИС в мире от компании Xilinx, но самое любопытное, что в стате не просто картинки с LUT и триггерами, а полноценные фотографии кристалла этой ПЛИС с объяснением микроархитектуры. |

|

Заметка: 5 Вызовов для высокоуровнего синтеза на ПЛИСЛюбопытная заметка появилась на сайте компании Silexica. John Inkeles рассматривает 5 пять проблем, с которыми приходится сталкиваться при использовании HLS для проектирования ПЛИС |

|

Вебинар: Максимизация производительности системы при использовании FPGA с интерфейсом PCIe Gen5На вебинаре от компании Achronix вы узнаете, как максимизировать производительность системы с помощью ПЛИС с интерфейсами PCIe Gen5. Вы поймете, почему вам нужно не только высокоскоростное подключение, но и возможность обрабатывать входящие данные на высоких скоростях для ускорения производительности приложений. |

|

Вебинар: Проверка пользовательских инструкций RISC-V с помощью UVMБлагодаря интеграции в Aldec Rivera-PRO утилиты Codasip’s Studio становится возможным верификация пользовательских инструкций процессора RISC-V. |

|

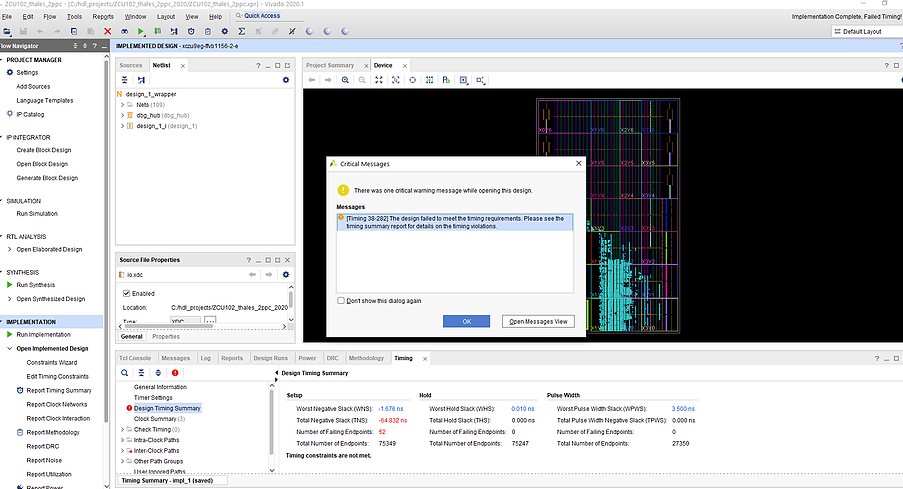

Заметка: Vivado подскажет, как свести тайминги в проекте (перевод)Что делать, если тайминги вашего проекта не сходятся? Как найти эти места и как исправить положение? |

|

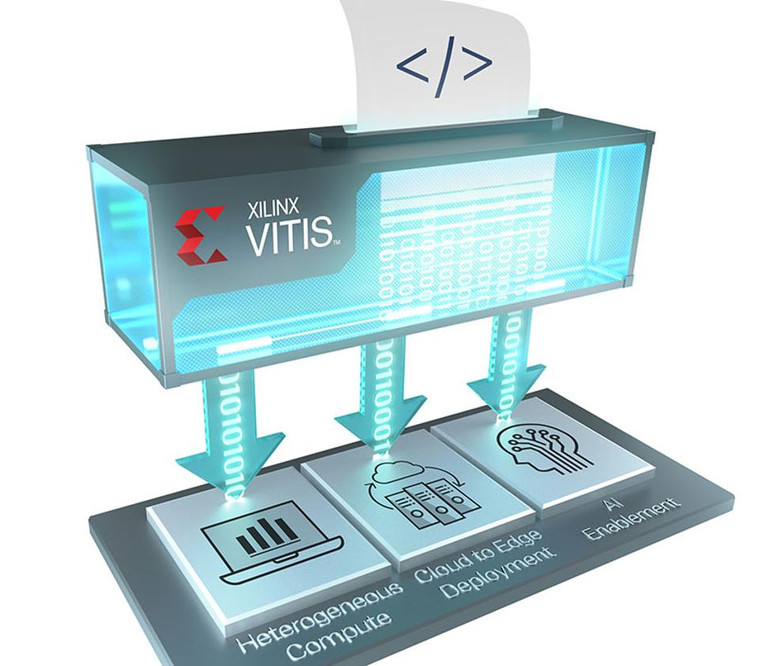

Онлайн-семинар: Разработка ускорителей в Xilinx VitisЕдиная программная платформа Vitis позволяет разработчикам легко использовать преимущества гетерогенных SoC Xilinx и ускорять свои приложения, не нуждаясь в передовых знаниях по разработке аппаратного обеспечения. Этот семинар предоставит вам базовые знания о том, как начать работу с Vitis и Vitis AI. |

|

Очень маленькая FPGA плата M02mini от marsohod.orgКоманда проекта marsohod.org сообщила о выходе новой очень маленькой FPGA платы M02mini на базе чипа Intel MAX10 10M02DCV36C8. |

|

Аналитика: Сможет ли HLS код побить HDL по производительности? (перевод)По общему убеждению, HLS проигрывает в производительности написанному вручную HDL. С правильным выбором инструментов может оказаться верным обратное утверждение. |

|

Cadence открыла бесплатный доступ ко всем видео-тренингам и обучающим материаламКомпания Cadence открыла свои учебные курсы. Теперь для того чтобы обучаться по программам Cadence достаточно только иметь активированный Cadence Support Account. |

|

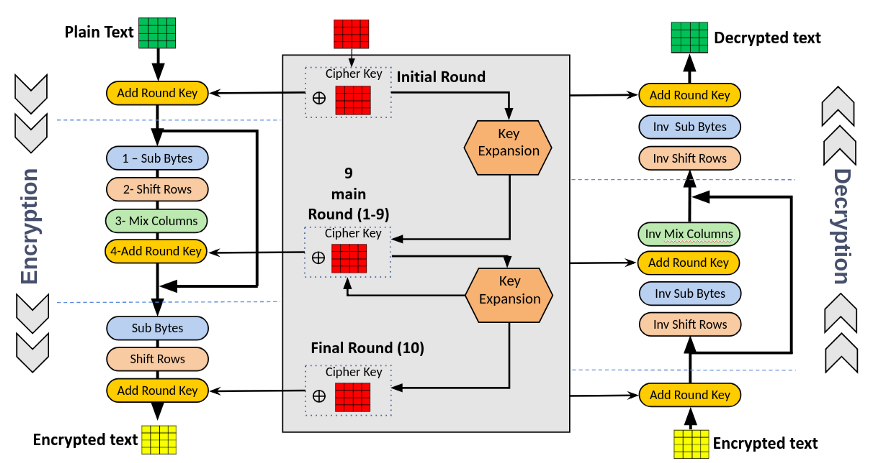

Руководство: Делаем алгоритм шифрования AES на VerilogИнтересное руководство попалось на портале medium.com |

|

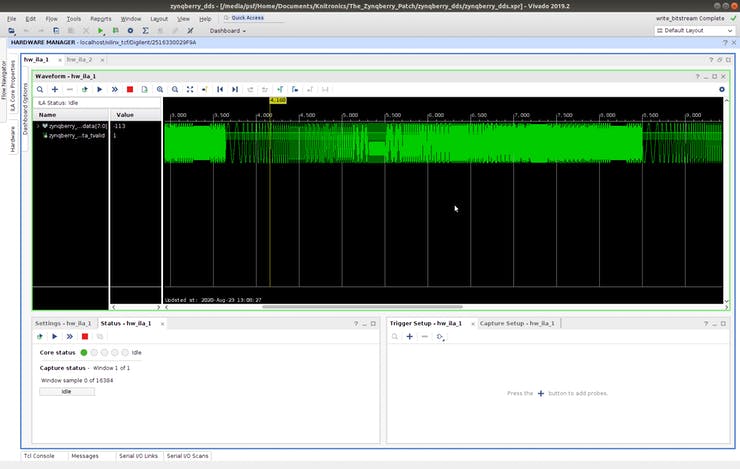

Туториал: Генерация синусоиды на C и Xilinx ZynqНа портале hackster.io появилась новая статья/гайд по использованию созданию генератора синусоиды с использованием Xilinx DDS Compiler + C+ baremetal + Zynq. Это полноценное руководство с боль... |

|

Презентация: Компиляция для Xilinx AI Engine с использованием MLIRЕсли вы интересуетесь развертыванием нейронных сетей и ИИ на новых адаптируемых ACAP — Versal AI, то эта презентация вероятно вам пригодится при изучении. Несмотря на ее относительную давность создания (02-02-2020), презентация пригодится как дополнительный материал для изучения. Возможно, вам удастся узнать что-то нов... |

|

Проведение тестирования проекта с помощью VUnit (перевод)Что делать, если после завершения проектирования мы обнаруживаем ошибку, требующую значительного отката? |

Конференция FPGA разработчиков

Конференции по FPGA за рубежом проходят достатоно часто, по крайней мере 3-4 раза в год, что нельзя сказать про отечетсвенный сегмент. Ребята вот из этого проекта организуют конференцию по FPGA тематике, которая пройдет в Мск 28 ноября и Спб 5 декабря, также планируется онлайн трансляция мероприятия. Участие в конференции бесплатное.

Более подробную информацию, ответы на наиболее частые вопросы и зарегистрироваться Вы можете на странице конференции

PS: по словам организаторов, колчество докладов для Мск уже хватает, чего нельзя сказать про СПб. Поэтому если Вы планируете учавствовать в Санкт-Петербурге, то может у Вас есть что рассказать за FPGA ?

Предыдущие выпуски новостного дайджеста

Новостной дайджест событий из мира FPGA/ПЛИС — №004 (2020_04)

Новостной дайджест событий из мира FPGA/ПЛИС — №002-003 (2020_02/2020_03)

Новостной дайджест событий из мира FPGA/ПЛИС — №001 (2020_01)

Приглашаю желающих помочь в наполнении новостной ленты. Пишите в личку.

SignallerK

Спасибо, за полезную подборку.