Сотрудники Исследовательского центра Уотсона компании IBM Тайфун Гокмен (Tayfun Gokmen) и Юрий Власов разработали новый чип Resistive Processing Unit (RPU), сочетающий в себе центральный процессор и энергонезависимую память и способный обеспечить существенное ускорение процесса глубокого обучения нейросетей (Deep Neural Networks, GNN) в сравнении с существующими процессорами при сравнительно меньших значениях энергопотребления.

“Системе, которая состоит из кластера ускорителей RPU окажутся под силу задачи больших данных, обрабатывающих одновременно триллионы параметров. В качестве примера таких массивов можно привести распознавание и перевод естественной речи между всеми языковыми парами, существующими в мире, аналитику интенсивных потоков научной и деловой информации в режиме реального времени или анализ мультимодальных потоков данных, поступающих от колоссального числа сенсоров IoT”, — комментируют событие исследователи на страницах ресурса arxiv.org.

На протяжении последних нескольких десятилетий достигнут внушительный прогресс в скорости машинного обучения. Это стало возможным благодаря использованию графических процессоров, массивов программируемой логики FPGA и специализированных микросхем (ASIC). Сегодня обеспечить дальнейшее ощутимое ускорение процесса, по мнению авторов разработки, позволит использование концепции параллельности и локальности алгоритмов обработки информации. Базой для успешной реализации таких концепций в лаборатории IBM стали принципы, реализованные в технологиях энергонезависимой памяти следующего поколения — фазовой (PCM) и резистивной (RRAM).

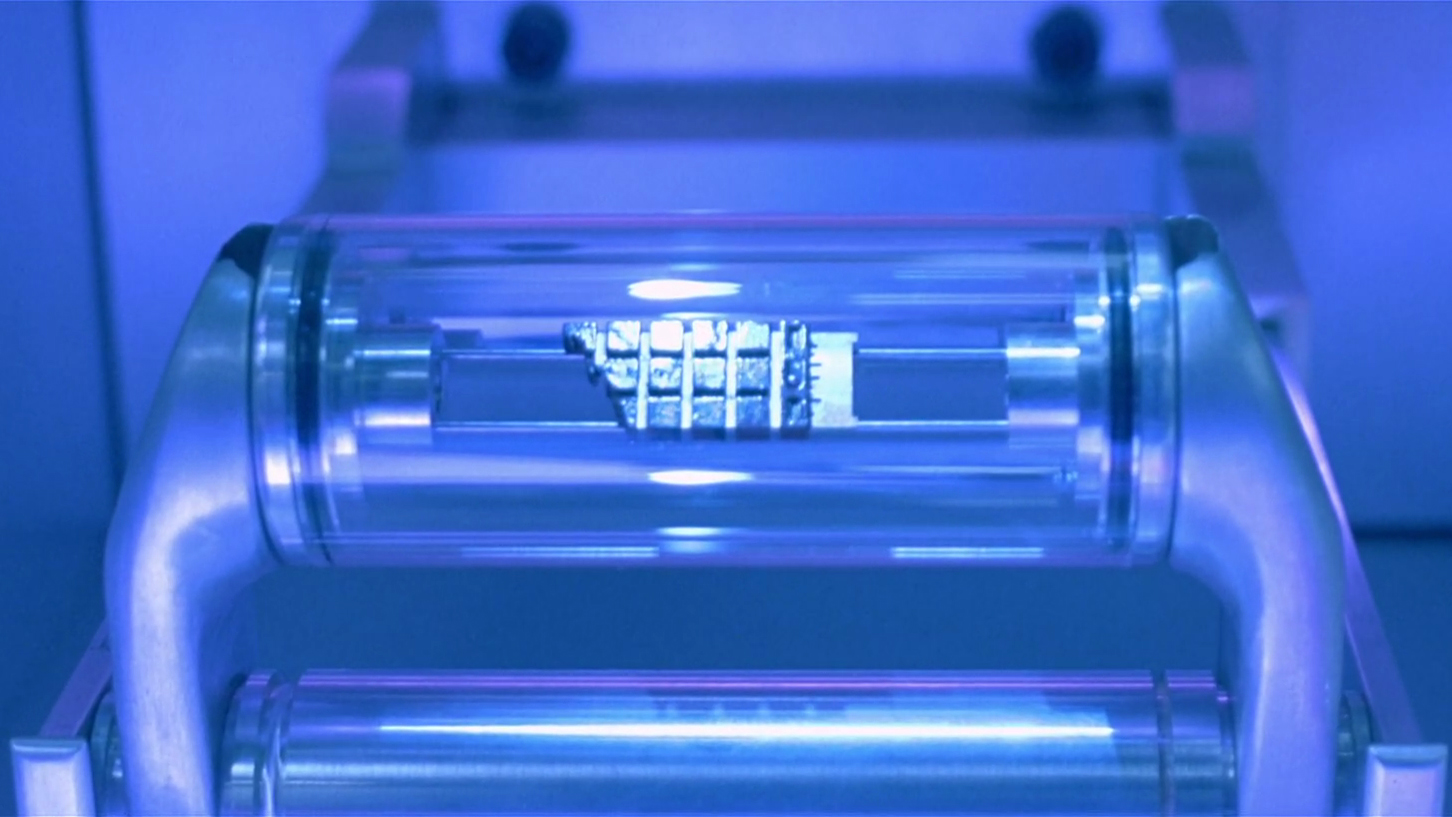

Schematics of original weight update rule of Eq.1 performed at each cross-point. (B) Schematics of stochastic update rule of Eq.2 that uses simple AND operation at each cross-point. Pulsing scheme that enables the implementation of stochastic updates rule by RPU devices for © up and (D) down conductance changes.

Сама по себе предложенная память позволяет ускорить DNN (процесс глубокого машинного обучения) в 27–2140 раз, но исследователи убеждены, что, сняв некоторые конструкционные ограничения запоминающих ячеек, им удастся обеспечить ещё более впечатляющие результаты. Как утверждает объединенная команда специалистов, работающая над инновационной технологией, чип, базирующийся на новой энергонезависимой памяти, созданный по разработанным ими спецификациям, позволит обеспечить прирост скорости работы алгоритма в сравнении с самыми мощными микропроцессорами в 30 тыс. раз.

Как полагают Власов и Гокмен, реализовать такие чипы возможно будет на базе традиционных КМОП-технологий. Вместе с тем, воплотить описанную концепцию на уровне коммерческих решений, скорее всего, удастся не ранее, чем через несколько лет, когда указанные технологии памяти «дотянутся» до рынка. Проведенные IBM исследования и достигнутые в теории результаты, по мнению экспертов уже сегодня выглядят очень многообещающе, поскольку открывают путь к новым качественным и количественным возможностям в освоении технологий машинного обучения.

Важно, что помимо самой IBM, совместная разработка специалистов T.J. Watson Research Center, вероятнее всего, окажется в центре внимания Google и других IT-гигантов, уже включившихся в многолетнюю гонку за право первыми обуздать возможности искусственного интеллекта. И это, в свою очередь, станет дополнительным мощным стимулом для скорейшего внедрения технологии на уровне коммерческих продуктов.

Источник

Техническое обоснование (pdf)

Уважаемые читатели, мы всегда с удовольствием встречаем и ждем вас на страницах нашего блога. Мы готовы и дальше делиться с вами актуальными новостями, обзорными материалами и другими публикациями, и постараемся сделать все возможное для того, чтобы проведенное с нами время было для вас полезным. И, конечно, не забывайте подписываться на наши рубрики.

Другие наши статьи и события

- Gator Caref Watch. Забота о вашем ребенке

- Весенние скидки от KitchenAid

- Распродажа полезных гаджетов и интересных штук

- Jawbone UP3 vs. Xiaomi Mi Band 1S Pulse — битва за наши сердца!

- Выбор умных часов сегодня. Что изменилось?

- ТОП 10 самых популярных гаджетов в iCover

- Как чехол не спас мой iPhone. Выбирай правильно

Комментарии (30)

aydahar

29.03.2016 12:34чип, базирующийся на новой энергонезависимой памяти, созданный по разработанным ими спецификациям

Интересно, связаны ли эти новые RPU с мемристорами?

potan

29.03.2016 14:27А как именно такая память может ускорить машинное обучение? Вроде ML с эноргонезависимостью ни как не связаны.

ironsnake

29.03.2016 14:40Подозреваю, что за счет того, что данные находятся рядом с вычислительным блоком и нет оверхэда на доступ к ним.

potan

29.03.2016 15:14А почему тоже самое не сделать на обычной хорошо отлаженной памяти?

ironsnake

29.03.2016 15:16Возможно, эта просто быстрее? Не знаю, характеристик не видел. Но если тут получается "жесткий диск" со скоростью оперативки, то на текущих технологиях этого не сделать. А вообще, вопрос хороший.

asd111

29.03.2016 18:23+1Intel обещали в этом году начать продажу памяти Xpoint(Optane), которая будет поставляться в том числе в виде модулей оперативной памяти. Между тем сама память является не временной, а постоянной.

geektimes.ru/post/259576

geektimes.ru/post/265448

Mad__Max

29.03.2016 18:43+3Это ничем не поможет, т.к. это отдельные внешние модули.

Тут предлагается совместить обработчики (исполнительные устройства) и память в одном чипе. Причем не просто рядом их разместить в одном кристалле и соединить какой-то быстрой внутренней шиной, а вообще без всяких шин — исполнительные устройства и запоминающие ячейки перемешаны и соединены напрямую друг с другом. С прямым доступом без задержек при чтении. (как регистры процессора, т.к. даже L1 кэш уже имеет задержки и ограниченную пропускную способность).

Аналог биологических нейронных сетей (мозга), где обрабатывающие схемы(программы) и данные которые они обрабатывают неотделимы друг от друга и представляют собой одно целое.

potan

29.03.2016 19:57Быстрые жесткие диски интересны во многих областях. Непонятно, чем они ценны именно в машинном обучении, что бы в одном устройстве стоило бы использовать несколько новых еще сырых технологий. Обычно без веской причины так не делают.

Mad__Max

29.03.2016 18:35+1На какой? DRAM? Нужна энергонезависимая — т.к. в ней хранятся не обрабатываемые временны данные (например образцы данных из обучающей выборки), а сам "опыт" тренируемой сети который должен сохраняться (и накапливаться/уточнятся) в процессе обучения и потом многократно использоваться после окончания процесса обучения.

Причем если в оригинал заглянуть эти ячейки запоминающие веса они предлагают делать не цифровыми(двоичными) а аналоговыми — сопротивление(проводимость) = весу связи между нейронами. Т.е. 1 ячейка кодирует не 1 бит, а описывает 1 связь.

В общем это практически полный электронный аналог живого мозга с нейронами и синапсами выполненный на аппаратном уровне, где нейроны заменены схемками на обычных транзисторах, а синапсы — ячейками резистивной памяти.

В общем нейроморфный чип, а совсем не чип для ускорения вычислений по традиционным алгоритмам используемым для модерирования нейронных сетей.

potan

29.03.2016 19:54Во время обучения будет отключаться электричество? Я не понимаю профита энергонезависимости именно в задаче машинного обучения.

Если такая ячейка используется как аналоговая, это уже интересно. Но хорошо бы это было описать, что бы не надо было копаться в первоисточнике для оценки интересности данного решения.

ironsnake

29.03.2016 23:08Ну вот прошли мы итерацию, веса изменились. Их надо либо сразу отправить в ПЗУ и гарантировать, что они правильно записались, либо оставить в оперативке и уходить на следующий круг. Отправка в отдельно стоящую энергонезависимую память означает, что у нас во первых появляются расходы на то, чтобы данные пропихнуть через интерфейс, а во вторых, если эта память общая для нескольких ячеек, появляется еще какой-то арбитраж, кто-куда-чего пишет. Любой сбой в процессе синка приводит к тому, что система оказывается в абсолютно недетерминированном состоянии. Здесь же получается (даже если забыть про то, что пишем аналог), что либо не поломается ничего, либо поломается несколько "нейронов".

hombre

31.03.2016 11:39+2насколько я понял после беглого прочтения статьи на arXiv, они предлагают КОНЦЕПТ, где процесс обучения моделируется аналоговыми схемами и хранятся «аналоговые» веса — а потом на выходе стоит аналогово-цифровой преобразователь, чтобы из них получить численные значения. А в статье подробно обсуждают, что делать с шумом и не убьет ли он все выгоды от такой схемы — и вывод, что можно попробовать.

Mad__Max

31.03.2016 14:46Ну в том числе и электричество — обучение сложных сетей может идти днями и неделями непрерывно и за это время всякое может случится. Но не только на обучение — потом такая обученная аппаратная сеть сама в себе результаты своего обучения и хранит — их не нужно откуда-то загружать и пересылать перед каждым началом работы с ней (разве что офлайн бекап один раз сделать — на случай физических повреждений, чтобы потом новую сеть с нуля не тренировать), они всегда доступны причем с мгновенным (в буквальном смысле) доступом. Как константы сохраненные прямо в программном коде. И поскольку после окончания обучения при обычном использовании эти веса уже не меняются, то их постоянное и энергонезависимое хранение — это то что нужно.

Хотя главный довод в пользу этого не столько сама способность долговременного хранения, а сопутствующее ей отсутствие необходимости постоянно и часто "освежать" эти данные как происходит с традиционными типами памяти наподобие DRAM — для чего нужны свои отдельных схемы, линии(соединения в чипе) и немалые затраты энергии. Т.е. плюсы в виде упрощения структуры чипа и увеличения энергоэффективности.

Про статью — это к автору. Штатные редакторы к сожалению часто дальше абстракта и введения не читаю когда "пересказ" пишут. А про аналоговые ячейки идет где-то в середине, и не как строго обязательное условие, а как один из вариантов реализации. Предпочтительный перед цифровым (двоичным) если удастся решить сопутствующие проблемы. Благо все основные энергонезависимые типы ячеек по своей сути "аналоговые" и их оцифровка происходит только в момент чтения.

ironsnake

29.03.2016 23:12Вопрос в том, сколько значений этот аналоговый "бит" может в себе хранить. Оригинал не посмотрел, но терзают смутные сомнения, что там что-то типа "сопротивление от A до B — это 0, сопротивление от С до D — это 1. Сопротивление от B до C — что-то пошло не так." Но если там хотя бы 256 градаций — это уже интересно.

zirf

30.03.2016 07:45логика трех состояний на матмаше была разработана как реализована не знаю, но была, но по-моему применить не успели. И "Матмаш" уже не матмаш...

ironsnake

30.03.2016 10:35Вы про Сетунь? Она серийно выпускалась (согласно википедии, построено 46 машин, 30 использовалось). Память там была магнитная, один трит занимал 2 бита, четвертое состояние запрещено.

Mad__Max

31.03.2016 15:23+1Там вообще не предполагается фиксированных градаций. Есть только естественное (натуральное) значение сопротивления от минимально возможного (максимальная проводимость) и до стремящегося к бесконечности (минимальная проводимость) с теоретически бесконечным количеством градаций между ними.

Оцифрованные (двоичные) данные предполагаются только на входе и на выходе из сети, а внутри нее все в аналоговой форме хранится.

На практике конечно бесконечного количества градаций не будет. С одной стороны и из-за ограничений используемых материалов, которые уже проявляются при нанометровых размерах ячеек — например для ячеек постоянной памяти с ловушкой заряда (наподобие флеш памяти) изготовленных по современным тех.процессам счет на кол-во электронов "пойманных" в подобной ловушке уже идет на сотни или даже десятки штук всего и поэтому хоть значение проводимости и аналоговое — оно начинает квантоваться пропорционально заряду 1 электрона уже из-за физических ограничений, а не архитектурных.

С другой — из-за того, что процессом обучения будут управлять внешние (обычные цифровые традиционной архитектуры) схемы, которым эти значения нужно модифицировать и отслеживать эффекты от этих модификаций. При бесконечном числе градаций весов получим бесконечное кол-во итераций для внешних цифровых схем — в результате им нужен какой-то фиксированный "шаг".

Для примера в статье рассматривался вариант с 600 градаций весов.

icover

29.03.2016 18:26Подозреваю, что за счет того, что данные находятся рядом с вычислительным блоком и нет оверхэда на доступ к ним.…

Вы абсолютно правы: So why does it take so much computing power and time to teach AI? The problem is that modern neural networks like Google's DeepMind or IBM Watson must perform billions of tasks in in parallel. That requires numerous CPU memory calls, which quickly adds up over billions of cycles. The researchers debated using new storage tech like resistive RAM that can permanently store data with DRAM-like speeds. However, they eventually came up with the idea for a new type of chip called a resistive processing unit (RPU) that puts large amounts of resistive RAM directly onto a CPU.

Sadler

29.03.2016 23:16Отдельный энергоэффективный девайс был бы как нельзя кстати, очень жду нормальное решение в этом плане, а то моя игровая видюшка на CuDNN вечно гудит, греется и в самый неподходящий момент упирается в память. Даже не ускорение просчёта как таковое интересует, а возможность работать с более сложной топологией, большим числом слоёв, большим числом фильтров и т.д.

Romich777

30.03.2016 14:47Думаю RPU что-то сродни FPGA с возможностью на ходу обучать модель, сохранять и переносить схему. Без необходимости долгой и ресурсоемкой компиляции или заказа партии ASIC отделяющих кошек от собак.

Mad__Max

31.03.2016 15:45+1Да, предлагаемая концепция весьма похожа на FPGA.

Из минусов — весьма ограниченные возможности по "программированию" — можно только менять веса связей между "нейронами". Сами нейроны, их принципы функционирования и схема связей между ними (кол-во, топология и т.д.) жестко определены еще на этапе производства, одинаковы для всех чипов одной модели и не могут быть изменены.

Из плюсов — большая плотность "упаковки", в частности программируемый массив 4096х4096 по оценкам авторов можно уложить примерно в 3 мм2 современного чипа и большая энергоэффективность вычислений. Ну и подстройка/дообучение "на лету" — можно в любой момент поменять некоторые веса и сразу посмотреть что изменится на выходе, без необходимости полной "пересборки"(перепрограммирования) чипа.IgorKh

03.04.2016 17:18Не согласен что жесткое определение топологии — минус. Наоборот имеем стандартизированный чип, под который кто угодно может продавать свою обученную под любые цели логику. Да это будет менее эффективно чем разработка топологии под каждую задачу но гораздо более универсально. К тому же можно выпустить несколько разных топологий, путь пользователи выбирают по вкусу.

Wowa69

02.04.2016 04:00Представляю себе новую игру, в которой будет сильный ИИ НПЦ, обучающийся на действиях игроков.

Halt

Может все-таки Власов, а не Волков?

VoiceDao

Да, конечно Власов, спасибо, подправили.