Продолжаем рассматривать UDB на основе фирменной документации Cypress, а именно полезные мелочи, связанные с Datapath.

Предыдущие статьи цикла:

UDB. Что же это такое? Часть 1. Введение. PLD.

UDB. Что же это такое? Часть 2. Datapath

UDB. Что же это такое? Часть 3. Datapath FIFO..

UDB. Что же это такое? Часть 4. Datapath ALU

21.3.2.6 Поддержка CRC/PRS

Datapath поддерживает генерацию Контрольного Циклического Кода (англ. Cyclic Redundancy Checking, CRC) и псевдослучайных последовательностей (англ. Pseudo Random Sequence, PRS). Объединенные в цепочку сигналы трассируются между блоками Datapath для поддержки CRC/PRS длиной более 8 бит.

Номер старшего бита (англ. Most Significant Bit, MSB) старшего блока CRC/PRS выбирается и трассируется (и связывается в цепочку с другими блоками) к младшим блокам. После этого к MSB применяется операция XOR с входными данными (данными SI), обеспечивая сигнал обратной связи (feedback, FB). После этого сигнал обратной связи трассируется (и связывается в цепочку с другими блоками) к младшим блокам. Это значение обратной связи используется на всех блоках, чтобы выполнять операцию XOR полинома (с регистра Data0 или Data1) с текущим значением аккумулятора.

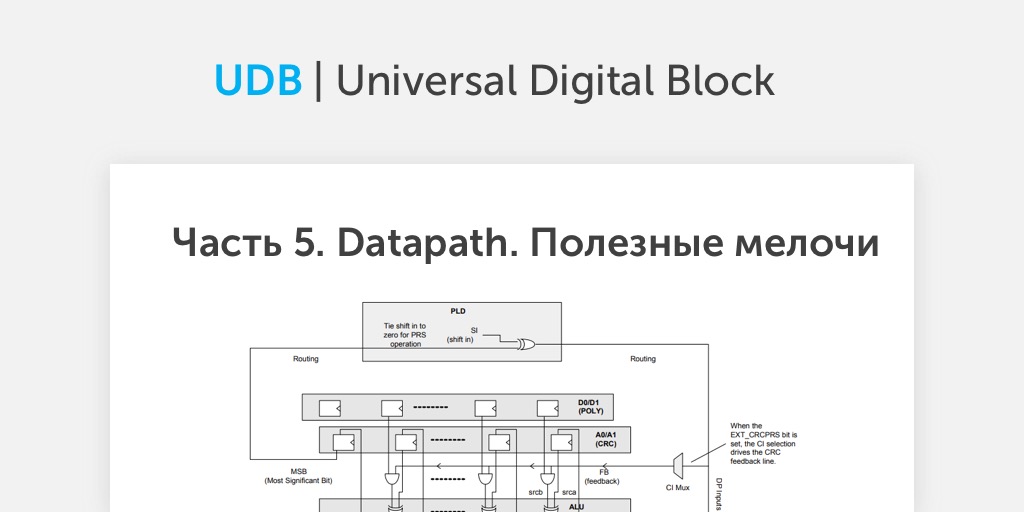

Рисунок 21-18 показывает структурную конфигурацию операции CRC. Конфигурация PRS идентична, но входные данные сдвига (SI) притянуты к 0. В режиме PRS D0 или D1 содержит значение полинома, а А0 или А1 содержит начальное значение (seed) и значение CRC, получившееся после вычисления.

Примечание переводчика.

По всей видимости, в этом предложении в фирменной документации опечатка, поскольку в режиме PRS должно получатся случайное число. А информация про CRC размещена чуть ниже.

Рисунок 21-18. Функциональная структура CRC.

Чтобы активировать поддержку CRC, необходимо присвоить биту CFB_EN в ОЗУ динамической конфигурации значение 1. Это активирует операцию И по отношению ко входу SRCB ALU и сигналу обратной связи CRC. Если этот бит установлен в ноль, сигнал обратной связи присвоится единице, что позволит выполнять нормальные арифметические операции. Динамическое управление этим битом на каждом цикле позволяет чередовать операции CRC/PRS с другими арифметическими операциями.

Связывание CRC/PRS в цепочки

Рисунок 21-19 показывает пример связывания CRC/PRS в цепочки между тремя UDB. Этот сценарий поддерживает работу в режимах с разрядностью от 17 до 24 бит. Управляющие биты связывания в цепочки задаются согласно положению Datapath в цепочке (см. рисунок).

Рисунок 21-19. Конфигурация связывания CRC/PRS в цепочки.

Как связывается в цепочку сигнал обратной связи CRC/PRS (cfbo, cfbi):

- Если выбранный блок является младшим, сигнал обратной связи на этом блоке генерируется из встроенной логики, которая берёт вход сдвига вправо (sir) и выполняет над ними операцию XOR со старшим битом. (В случае PRS сигнал «sir» установлен в “0”).

- Если выбранный блок не является младшим блоком, бит конфигурации CHAIN FB должен быть взведен, а обратная связь передается по цепочке с предыдущего блока.

Как связывается в цепочку сигнал CRC/PRS MSB (cmsbo, cmsbi):

- Если выбранный блок является старшим, бит конфигурации MSB (согласно выбранному полиному) конфигурируется при помощи битов конфигурации MSB_SEL.

- Если выбранный блок не является старшим, бит конфигурации CHAIN MSB должен быть взведен, а сигнал MSB передается по цепочке со следующего блока.

Полиномиальная спецификация CRC/PRS

В качестве примера конфигурации полинома для записи в соответствующий регистр D0/D1, рассмотрим полином CCITT CRC-16, который имеет вид x16 + x12 + x5 + 1. Метод извлечения формата данных из полинома показан на рисунке 21-20. Член X0 по определению всегда равен 1, следовательно, его не нужно записывать. Для всех остальных членов полинома единица устанавливается в необходимые позиции, как показано на рисунке.

Рисунок 21-20. Формат полинома CCITT CRC16.

Обратите внимание, что формат полинома немного отличается от формата, указанного в классическом шестнадцатеричном виде. Например, полином CCITT CRC16 обычно обозначается как 1021H. Чтобы преобразовать его в требуемый формат для Datapath, необходимо выполнить сдвиг вправо на одну позицию и добавить 1 в бит MSB. В данном случае, правильным значением полинома, которое нужно записать в D0 или в D1, является 8810H.

Пример конфигурации CRC/PRS

Ниже приведено краткое описание требований к конфигурации CRC/PRS, при условии, что D0 – полином, а CRC/PRS вычисляется в А0:

- Выбрать подходящий полином (пример выше), и записать его в D0.

- Выбрать подходящее начальное значение (seed) (например, все нули для CRC или все единицы для PRS) и записать его в A0.

- При необходимости, настроить связывание в цепочки, как описано выше.

- Выбрать позицию MSB как описано выше.

- Настроить поля ОЗУ динамической конфигурации:

a. Выбрать D0 в качестве ALU “SRCB” (источник данных ALU B)

b. Выбрать А0 в качестве ALU “SRCA” (источник данных ALU A)

c. Выбрать XOR для операции ALU

d. Выбрать SHIFT LEFT для операции SHIFT

e. Выбрать CFB_EN чтобы включить поддержку CRC/PRS

f. Выбрать ALU в качестве источника записи A0

При выборе CRC, необходимо настроить поле shift in right для входных данных и подавать на этот вход данные на каждом такте. При выборе PRS необходимо присвоить shift in right значение 0.

Такая конфигурация UDB генерирует необходимый CRC либо вырабатывает старший бит, который можно пробросить наружу, снимая с него псевдослучайную последовательность.

Внешний режим CRC/PRS

Чтобы включить поддержку внешних вычислений CRC или PRS можно задать статический бит конфигурации (EXT CRCPRS). Как показано на рисунке 21-21, вычисление обратной связи CRC выполняется в блоке PLD. Когда бит взведен, сигнал обратной связи CRC передается напрямую с входного мультиплексора CI (Carry In), в обход внутренних вычислений. На рисунке показана простая конфигурация, которая поддерживает CRC или PRS вплоть до 8-битных. Обычно используются встроенные электронные схемы, но этот параметр позволяет реализовывать более сложные конфигурации, например 16-битные функции CRC/PRS в одном UDB, используя мультиплексирование с временным разделением.

Рисунок 21-21. Внешний режим CRC/PRS.

В этом режиме бит CFB_EN ОЗУ динамической конфигурации также контролирует, используется ли операция И к сигналу обратной связи CRC на входе CRCB ALU или нет. Таким образом, как и в случае с внутренним режимом CRC/PRS, эта функция может при необходимости чередоваться с другими функциями.

21.3.2.7 Выходы Datapath и мультиплексирование

Условия генерируются из значений триггеров аккумуляторов, выходов ALU и статуса FIFO. Эти условия могут быть переданы через цифровые трассировочные каналы на другие UDB, для формирования запросов на прерывания или на DMA, либо на «ножки микросхемы». 16 возможных условий показаны в таблице ниже.

Таблица 21-16. Генерация условий Datapath.

| Название | Условие | Цепочка? | Описание |

|---|---|---|---|

| ce0 | Сравнение «Равно»/Compare Equal | Да | A0 == D0 |

| cl0 | Сравнение «Меньше, чем»/Compare Less Than | Да | A0 < D0 |

| z0 | Обнаружен нуль | Да | A0 == 00h |

| ff0 | Обнаружены единицы | Да | A0 = FFh |

| ce1 | Сравнение «Равно»/Compare Equal | Да | A1 или A0 == D1 или A0 (динамический выбор) |

| cl1 | Сравнение «Меньше, чем»/Compare Less Than | Да | А1 или А0 < D1, или А0 (динамический выбор) |

| z1 | Обнаружен нуль | Да | А1 == 00h |

| ff1 | Обнаружены единицы | Да | A1 == FFh |

| ov_msb | Переполнение/Overflow | Нет | Carry(msb) ^ Carry (msb-1) |

| co_msb | Перенос/Carry Out | Да | Перенос определенного бита MSB |

| cmsb | CRC MSB | Да | MSB функции CRC/PRS |

| so | Выход операции сдвига/Shift Out | Да | Выход данных выбранной операции сдвига |

| f0_blk_stat | Статус блока FIFO0 | Нет | Описание зависит от конфигурации FIFO |

| f1_blk_stat | Статус блока FIFO1 | Нет | Описание зависит от конфигурации FIFO |

| f0_bus_stat | Статус шины FIFO0 | Нет | Описание зависит от конфигурации FIFO |

| f1_bus_stat | Статус шины FIFO1 | Нет | Описание зависит от конфигурации FIFO |

Рисунок 21-22. Подключения к выходному мультиплексору.

Сравнения

Существуют два сравнения, одно из которых имеет фиксированные источники (Compare 0), а другое – динамически выбираемые (Compare 1). Каждое сравнение имеет 8-битный статический регистр наложения маски, позволяющий выполнять сравнение в указанном битовом поле. По умолчанию, наложение маски отключено (сравниваются все биты) и его необходимо активировать вручную.

Входы Сompare 1 конфигурируются динамически. Как показано в таблице ниже, существует четыре параметра Compare 1, применяемые к условиям «меньше» и «равно». Биты конфигурации CMP SELA и CMP SELB определяют возможные конфигурации сравнений. Биты ОЗУ динамической конфигурации задают одну из конфигураций (А или В) на каждом цикле.

Таблица 21-17. Конфигурация сравнений.

| CMP SEL A CMP SEL B |

Режим сравнения для Сompare 1 |

|---|---|

| 00 | А1 сравнивается с D1 |

| 01 | A1 сравнивается с A0 |

| 10 | A0 сравнивается с D1 |

| 11 | A0 сравнивается с А0 |

Рисунок 21-23. Связывание в цепочку сравнения «равно».

Рисунок 21-24 показывает связывание в цепочку сравнения «меньше». В этом случае выходной результат (cl0) для данного блока формируется схемой сравнения «меньше, чем» и является безусловным. Этот сигнал объединяется по ИЛИ со входящим результатом из цепочки, если для текущего блока выполняется условие «равно» и включён режим связывания в цепочки.

Рисунок 21-24. Связывание в цепочку сравнения «меньше, чем»

Обнаружение всех нулей и всех единиц

Каждый аккумулятор имеет детектор всех нулей и детектор всех единиц. Эти условия можно статически связывать в цепочку, как указано в регистрах конфигурации UDB. Режим связывания задается в регистрах конфигурации UDB. Связывание в цепочку обнаружения нулей происходит по той же концепции, что и у сравнения «равно». Если связывание в цепочку активировано, к успешно связанным данным применяется операция И.

Переполнение

Переполнение определяется как операция XOR переноса в MSB и переноса из MSB. Вычисления выполняются с текущим MSB, как указано в битах MSB_SEL. Это условие нельзя связывать в цепочку, однако вычисление будет корректным, если будет выполнено на старшем Datapath функции суммарной разрядности до тех пор, пока перенос между блоками связан.

21.3.2.8 Параллельные входы и выходы Datapath

Как показано на рисунке 21-25, сигналы Parallel In (PI) и Parallel Out (PO) дают ограниченную возможность по доставке данных и трассировочных ресурсов в Datapath и выводу данных из него. Сигналы PO всегда доступны для трассировки в качестве выбора значения ALU asrc между А0 и А1.

Примечание переводчика.

Это чрезвычайно важный механизм, который позволяет UDB работать не только с последовательными, но и с параллельными данными. Почему-то в данном документе это не подчёркивается, но об этом можно вскользь прочитать в одном из Application Notes.

Рисунок 21-25. Сигналы Parallel In/Out Datapath.

Для ввода данных в ALU необходимо выбрать Parallel In. Существует два режима: статический и динамический. В статическом режиме бит PI SEL приводит значение ALU asrc к PI. Бит PI DYN используется для обеспечения динамического режима PI. Когда он взведен, а также, при условии, что PI SEL равен 0, мультиплексором PI можно управлять битом динамического управления CFB_EN. Основной функцией бита CFB_EN является обеспечение функционала PRS/CRC.

21.3.2.9 Связывание Datapath в цепочку

Каждый блок Datapath имеет 8-битное ALU, которое разработано для связывания в цепочку переносов, сдвигов, триггеров захвата и условных сигналов с ближайшим соседним Datapath для создания арифметических функций и регистров сдвига большей разрядности. Эти сигналы, связываемые в цепочки, являются выделенными и позволяют эффективно реализовывать 16- 24- и 32-битные функции в рамках одного цикла без гонок и прочих проблем, возникающих от задержек в трассировочных каналах. Кроме того, связывание в цепочку захватов поддерживает атомарное чтение аккумуляторов в связанных блоках. Как показано на рисунке 21-21, все сгенерированные условные сигналы и сигналы захватов связаны в цепочку, которая двигается от младшего к старшему блоку. Сдвиг влево также выполняется от младшего к старшему. Сдвиг вправо выполняется от старшего к младшему. Сигнал связывания в цепочку CRC/PRS для обратной связи направляется от старшего к младшему, а выход MSB — от старшего к младшему.

Рисунок 21-26. Поток цепочек Datapath.

21.3.2.10 ОЗУ динамической конфигурации

Каждый Datapath содержит ОЗУ динамической конфигурации с 8 словами по 16 бит (см. рисунок 21-27). Назначением такого ОЗУ является управление битами конфигурации Datapath на каждом цикле, основываясь на выбранном тактировании для данного Datapath. ОЗУ имеет синхронные порты чтения и записи для загрузки конфигурации через системную шину.

Для быстрого вывода этих 16-битных слов на Datapath в качестве битов управления предоставляется дополнительный асинхронный порт для чтения. Асинхронные адресные входы выбираются мультиплексорами из входов Datapath, которые могут быть взяты из любых возможных сигналов, включая ножки микросхемы, выходы PLD, выходы блока управления или любые выходы Datapath.

Основной задачей асинхронного порта для чтения является обеспечение быстрого декодирования управляющих битов Datapath за один цикл.

Рисунок 21-27. ОЗУ конфигурации ввода/вывода.

Поля слова ОЗУ динамической конфигурации показаны в следующих таблицах вместе с описанием использования каждого поля.

| Регистр | Адрес | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|---|---|---|---|---|---|---|---|---|---|

| CFGRAM | 61h-6Fh (нечетный) |

FUNC[2:0] | FUNC[2:0] | FUNC[2:0] | SRCA | SRCB[1:0] | SRCB[1:0] | SHIFT[1:0] | SHIFT[1:0] |

| Регистр | Адрес | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|

| CFGRAM | 60h-6Eh (четный) |

А0 WRSRC[1:0] | А0 WRSRC[1:0] | A1 WRSRC[1:0] | A1 WRSRC[1:0] | CFB EN | CI SEL | SI SEL | CMPSEL |

| Поле | Биты | Параметр | Значения |

|---|---|---|---|

| FUNC[2:0] | 3 | Функция ALU | 000 PASS 001 INC SRCA 010 DEC SRCA 011 ADD 100 SUB 101 XOR 110 AND 111 OR |

| SRCA | 1 | Источник входных данных ALU A | 0 A0 1 A1 |

| SRCB | 2 | Источник входных данных ALU B | 00 D0 01 D1 10 A0 11 A1 |

| SHIFT[1:0] | 2 | Функция сдвига | 00 PASS 01 Left Shift 10 Right Shift 11 Nibble Swap |

| A0 WR SRC[1:0] | 2 | Источник записи для A0 | 00 None 01 ALU 10 D0 11 F0 |

| A1 WR SRC [1:0] | 2 | Источник записи для А1 | 00 None 01 ALU 10 D1 11 F1 |

| CFB EN | 1 | Активатор обратной связи CRC | 0 Enable 1 Disable |

| CI SEL | 1 | Выбор конфигурации для переноса | 0 ConfigA 1 ConfigBa |

| SI SEL | 1 | Выбор конфигурации для сдвига | 0 ConfigA 1 ConfigBa |

| CMP SEL | 1 | Выбор конфигурации для сравнения | 0 ConfigA 1 ConfigBa |

Продолжение следует…

VBKesha

Читаешь и прямо возникает желание прикупить эту штуку попробовать…

PTM

На самом деле интересная штука.

EasyLy Автор

Если что — самая минималистичная макетка на PSoC5 — это CY8CKIT-059

Что на АЛИ, что в Терре она стоит около 1650 рублей (в Терре от трёх штук — дешевле, но кто для себя больше одной сразу берёт?). На АЛИ доставка включена, в Терре придётся добавить доставку, если нет пункта выдачи поблизости.

PTM

Если что на psoc4 уже доступны udb правда не много и макета стоит около 5usd на psoc 3 не уверен

EasyLy Автор

Судя по описанию, UDB у PSoC3 и 5 унифицированы.

1) Как отмечалось в прошлой части перевода, там есть логика атомарного захвата аккумулятора, которая на ARM ядре совершенно не нужна

2) Если создавать DataPath в Datapath Config Tool, то там создаётся cy_psoc3_dp даже для пятого (как именно — я сейчас делаю авторскую статью)

Так что в третьем всё то же самое должно быть на уровне UDB. Разве что эпоха процессоров MCS-51 уже уходит в прошлое. Поэтому на практике — не проверял.

PTM

как нечто среднее между psoc4 и psoc5 самое то. особенно у cypress. миграция почти безболезненна. ( ну если тока сильно в дебри не лезть)

VBKesha

На него давно и гляжу, но жаба давит… хотя видимо придётся её пересилить.