Cadence Design Systems, одна из двух крупнейших мировых компаний в области автоматизации разработки микросхем, 15-16 октября проведет семинары в Московском институте электронной техники (МИЭТ) в Зеленограде и Питерском Университете ИТМО, в котором (по опыту моей поездки 2012 года) студенты очень хорошо понимают Verilog и системы на кристалле.

В семинарах примут участие и три российские компании «Элекроприбор», НИИМА «Прогресс» и НПЦ «Элвис». См. статью про сотрудничество с Imagination Technologies родственной НПЦ «Элвис» организации «Элвис-Неотек» на сайте Роснано.

Среди презентаций я лично рекомендую посмотреть на новый тул для синтеза Genus — я видел и заснял его презентацию в июне на выставке Design Automation Conference в Сан-Франциско:

Объявление, которое мне пришло про российский семинар — ниже. На фото справа — я на фоне здания МИЭТ в Зеленограде во время поездки по делам MIPS Technologies в 2011 году. Там люди из Cadence проведут один из семинаров:

Cadence проводит два Technology Days в Питере в ИТМО 15-ого октября и в Зеленограде в МИЭТе 16-ого октября. Заявки на участие в ИТМО напишите Павлу Кустареву: kustarev@yandex.ru. Заявки на участие в МИЭТ напишите Владимиру Лосеву: dsd@miee.ru.

Адресс ИТМО: СПб, Биржевая линия В.О. 14 «Технопарк ИТМО»

Программа в ИТМО выглядит так:

Technology day at ITMO – Seminar Title:

Virtual Model Prototyping, High Level Synthesis, Synthesis and Digital Implementation by Cadence

9:15 – 9:45 Welcome and Cadence Overview

9:45 – 11:15 Cadence: Virtual Model Prototyping

11:15 -11:30 Break

11:30 – 12:30 Cadence: High Level Synthesis

12:30 – 13:30 Lunch

13:30 – 14:30 Cadence: Genus the new synthesis solution

14:30 – 15:30 Cadence: Innovus – state of the art digital implementation

15:30 – 15:45 Break

15:45 – 16:45 “Элекроприбор» — experience with Cadence tools

16:45 – 17:45 Выступление преподователей ИТМО

17:45 – 18:15 Round table and open discussions with the speakers

Программа в МИЭТе выглядит так:

09:00 – 09:15 Регистрация.

09:15 – 09:45 Вступление от Cadence; 0:30 hour.

09:45 – 11:15 Cadence: Virtual Model Prototyping

11:15 – 11:30 Кофе – брейк.

11:30 – 12:30 Cadence: High Level Synthesis

12:30 – 13:30 Обед.

13:30 – 14:45 Cadence: Genus the new synthesis solution

14:45 – 15:00 Кофе – брейк.

15:00 – 16:15 Cadence: Innovus – state of the art digital implementation

16:15 – 16:45 АО «НИИМА «Прогресс» – опыт использования ПО Cadence

16:45 – 17:15 ОАО НПЦ «ЭЛВИС» – опыт использования Cadence Incisive для создания и отладки тестов СнК системного уровня.

17:15 – 18:00 Открытая дискуссия, круглый стол.

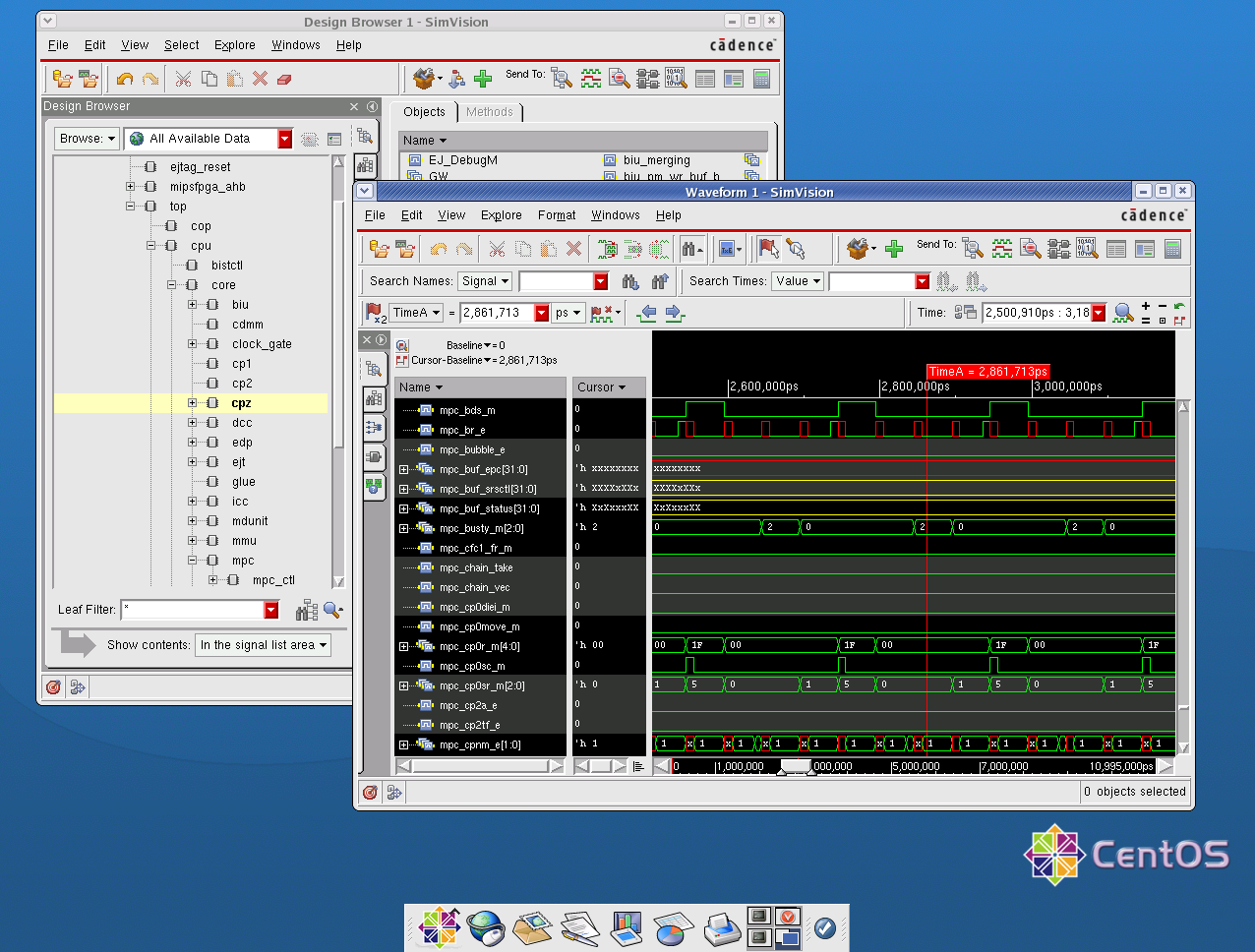

Я лично очень люблю тулы от Cadence. Вот например как выглядит на моем экране отладка процессорного ядра MIPS microAptiv UP из пакета MIPSfpga в среде SimVision:

Только зарегистрированные пользователи могут участвовать в опросе. Войдите, пожалуйста.

Комментарии (11)

kasperos

06.10.2015 11:57кому продать идею как сделать процессор на 1000 ядер? :)

beeruser

06.10.2015 15:01Буратине какому-нить. ru.wikipedia.org/wiki/Kilocore

Такие процессоры, как правило, заканчивают жизнь одинаково печально.

YuriPanchul

06.10.2015 17:26Это зависит от применения. Специализированный процессор с сотнями некогерентных ядер можно применять для обработки сетевых пакетов (такое сделал один клиент нашей компании), но для общего назначения, как application processor это не тянет конечно.

beeruser

06.10.2015 17:48TILE-Gx, например. Но 100-ядерник они так и не выпустили.

Я собственно о том, что идея такого устройства не стоит ничего.

YuriPanchul

06.10.2015 17:24А зачем? Один из крупных азиатских клиентов нашей компании сделал сетевой процессор с 200 ядрами на одном кристалле, но они все выбли некогерентные.

ignat99

07.10.2015 12:53Один из моих студентов дипломников сделал простейший проект MIPS в 2005 году вот на этой системе staticfreesoft.com. Она бесплатная и с открытым исходным кодом.

nerudo

А есть ли у вас какая-либо альтернатива, любить тулы от Cadence или какие-нибудь другие? ;-)

По мне так у Cadence наиболее архаичный софт, как из 19 века, из того, что мне доводилось видеть (ну кроме Synopsis — с ними не приходилось сталкиваться).

YuriPanchul

У нас в конторе есть все более-менее значимые тулы — и от Synopsys, и Cadence и других производителей тулов. С альтернативой в индустрии туго. А open-source тулы в области EDA очень слабые — то же Icarus Verilog на моих тестах работал в 50 (!) раз медленнее Synopsys-а.

А чем вы пользуетесь и для чего?

nerudo

Altera, Xilinx — понятно, Mentor — схемы/разводка PCB, моделирование (ModelSim), разработка hdl-проектов (HDL designer), когда-то работал с их синтезаторами, но давненько уже. У Aldec щупал симулятор, Cadence — пытался поучиться разработке заказных ИС, но пока далеко не ушел за недостатком времени.