Привет, я Александр Калёнов, аспирант и инженер кафедры интегральной электроники и микросистем в МИЭТ, работаю дизайнером СБИС в «НИИМА «Прогресс». Для хакатона YADRO SoC Design Challenge я создавал задание по топологии, которое мы тут и рассмотрим.

Для тех, кто тут случайно, или О топологии на пальцах

Для начала определим место топологии в проектировании микросхем. Вся разработка делится на три больших блока. Первый — это структурное проектирование, зависящее от того, для чего именно проектируется микросхема.

Второй – это схемотехническое проектирование. В цифровом варианте – это написание RTL-блоков. Если говорим про аналоговый вариант, то это создание схем на транзисторном уровне, используя резисторы, конденсаторы и так далее.

И третий блок — это как раз формирование топологий, перенос электрической схемы в набор фотошаблонов, нормы проектирования которых предоставляет фабрика. Стоит отметить, что у каждой фабрики — свои нормы и просто прийти на другую фабрику с фотошаблонами, сделанными для другой — нельзя.

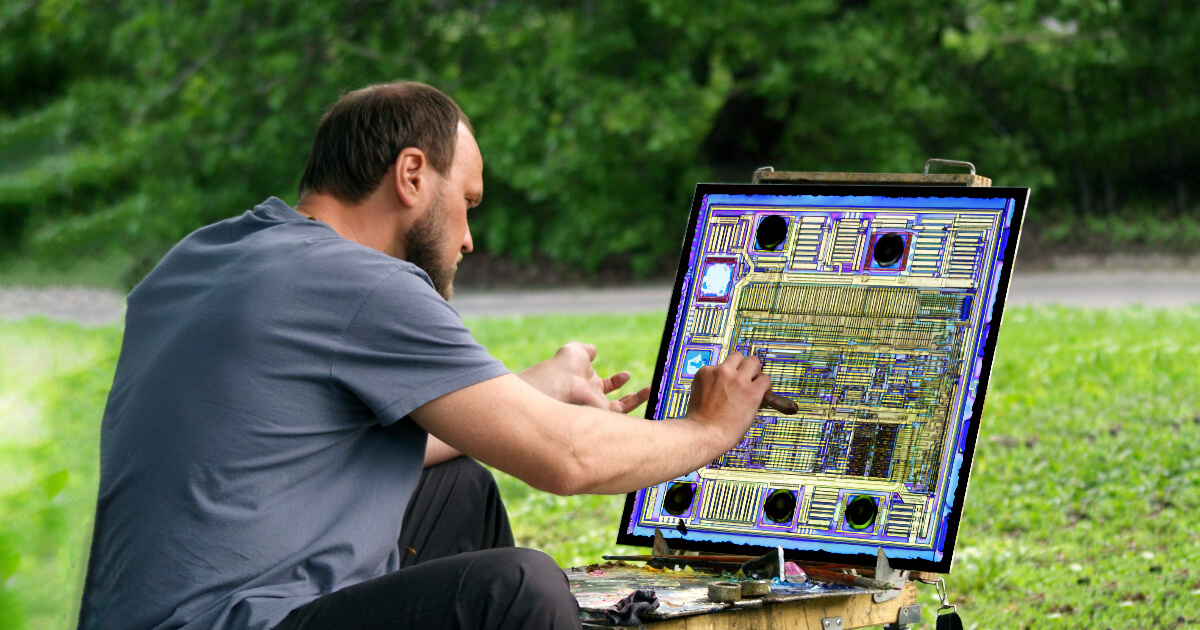

Тополог как художник «рисует» геометрические фигуры в творческом поле и в зависимости от того, какая была электрическая схема, переносит её в фотошаблоны (кремний или металлы), а затем проверяет.

Работающий с фотошаблонами литограф ASML за $170 млн.

У создания топологий есть два параметра верификации. Первый из них — это DRC (design rule check). Это первичная проверка на соответствие тем технологическим нормам, которые предоставляет фабрика. Если расположим металлы близко друг к другу, такую микросхему фабрика просто не произведёт из-за недостаточной точности оборудования. В задачу тополога входит это поправить и после этого провести ещё одну верификацию LVS (layout versus schematic), на соответствие электрической схемы с топологией. Всё, что будет произведено в кремнии, должно соответствовать тому, что спроектировано на транзисторном уровне.

После того как эти две верификации пройдены, идёт этап экстракции, входящий в проектирование топологии. На этом этапе устраняются недочёты, которые возникли раньше. Например, сделали длинный провод, и набежала дополнительная ёмкость на подложку, или сделали тонкий провод и появилось дополнительное сопротивление. Это сильно влияет на характеристики схемы, на время переключения из единицы в ноль, из нуля в единицу.

Исправленные параметры заново вносятся в схему, после чего она корректируется и в виде набора фотошаблонов передается на фабрику. По факту топология – это заключительный этап в создании микросхем.

Заменят ли топологов роботы

Популярный вопрос, который слышу от студентов — можно ли процесс автоматизировать? Ведь есть же предел человеческому вниманию. Истина, как и водится, где-то посередине.

В топологии существует разделение на цифровую, которая делается с минимальным вмешательством человека и аналоговую, которая делается только человеком.

Цифровая топология с помощью САПР (средства автоматизированного проектирования) решает задачи уменьшения технологических норм или нанометров и компоновки на одном микрометре большого числа элементов. А в аналоговой топологии инженер делает эдакий скетч микросхемы, вручную рисуя квадратики поликремния и металлов. Этап экстракции также проводится человеком.

Открывайте в полном размере, держа в голове мысль, что это «рисуется вручную».

Так зачем нужно участие человека, почему нельзя все доверить машине? И ответ прост — у машины пока нет технических возможностей, чтобы спроектировать микросхему самостоятельно.

Например, при проектировании шин питания и земли надо учитывать толщину этих шин, так как там протекает ток. Если сделать тонкую шину, то при включении, схемы сразу будут сгорать. Особенно если потребление там несколько сотен миллиампер. Бывали такие случаи, что произвели много схем, которые при включении сразу сгорали и не было возможности их проверить.

На текущем этапе развития машина не может соотнести тот ток, который протекает, с толщиной шины, которую необходимо сделать. Поэтому это рассчитывает человек. С уверенностью можно сказать, что в обозримом будущем топологам «нашествия роботов» можно не опасаться.

А что там с заданием?

Задание по топологии было максимально приближено к практике и разбито на три части. Первые две связаны с цифровой топологией.

Сперва участникам предстояло собрать схемы D-триггера, DV-триггера и СВЧ ключа, используя библиотеку DDK gpdk045 (gsclib045). Затем создать их символы, тестовую схему для проверки работоспособности и спроектировать топологию. Потом последовательно провести сначала DRC, а затем LVS верификацию и экстракцию топологии разработанных триггеров и ключа, которую нужно было учесть в последующем моделировании. Дальше начинались различия.

- Используя библиотеку DDK gpdk045 (gsclib045) собрать схему D-триггера.

- Создать символ D-триггера.

- Создать тестовую схему для проверки работоспособности D-триггера

- Спроектировать топологию D-триггера

- Провести верификацию DRC

- Провести верификацию LVS

- Провести экстракцию топологии разработанного D-триггера.

- Провести моделирование D-триггера с учётом экстракции

- Спроектировать схему делителя частоты (на 2, 4, 8, 16, 32), используя разработанный D-триггер.

- Создать символ делителя частоты (на 2, 4, 8, 16, 32)

- Создать тестовую схему для проверки работоспособности делителя частоты (на 2, 4, 8, 16, 32)

- Спроектировать топологию делителя частоты (на 2, 4, 8, 16, 32)

- Провести верификацию DRC

- Провести верификацию LVS

- Провести экстракцию топологии разработанных делителей

- Провести моделирование делителя частоты (на 2, 4, 8, 16, 32) с учётом экстракции

| Время задержки, t01 | |

| Время задержки, t10 |

Задание 2

- Используя библиотеку DDK gpdk045 (gsclib045) собрать схему DV-триггера.

- Создать символ DV-триггера.

- Создать тестовую схему для проверки работоспособности DV-триггера

- Спроектировать топологию DV-триггера

- Провести верификацию DRC

- Провести верификацию LVS

- Провести экстракцию топологии разработанного DV-триггера.

- Провести моделирование DV-триггера с учётом экстракции

- Спроектировать схему нецикличного реверсивного счётчика от 0 до 8:, используя разработанный DV-триггер.

- Создать символ разработанного счётчика

- Создать тестовую схему для проверки работоспособности разработанного счётчика

- Спроектировать топологию счётчика

- Провести верификацию DRC

- Провести верификацию LVS

- Провести экстракцию топологии счётчика

- Провести моделирование счётчика с учётом экстракции

| Время задержки, t01 | |

| Время задержки, t10 |

Задание 3

- Используя технологическую библиотеку gpdk045 собрать схему СВЧ ключа (Г-П-Т-образные) для получения наименьших потерь и наибольшей развязки.

- Создать символ ключа

- Создать тестовую схему для проверки работоспособности ключа

- Спроектировать топологию ключа

- Провести верификацию DRC

- Провести верификацию LVS

- Провести экстракцию топологии разработанного ключа.

- Провести моделирование ключа с учётом экстракции

| Частота среза, ГГЦ | |

| Потери, dB | |

| Развязка, dB |

Для части с D-триггером — нужно было спроектировать схему делителя частоты (на 2, 4, 8, 16, 32). Для части с DV-триггером — спроектировать схему нецикличного реверсивного счётчика от 0 до 8. Часть со сборкой схемы СВЧ ключа сюрпризов в себе не таила, но до неё, к сожалению, не добрался никто из участников. Из-за этого жюри пришлось оценивать тех, кто по максимуму справился с первыми двумя частями.

Для создания ячейки деления на два, на четыре и на восемь, участники пытались использовать защёлку (половину master/slave), стремясь уменьшить себе работу, реализовав это на простой схеме. По-хорошему необходимо было использовать схему триггеров master/slave.

Много времени у ребят занял и поиск в сети подходящего решения. Если реализацию делителя на два ещё можно найти, то вот переход к делению на четыре и на восемь — нужно додумывать самому. Особенно во второй части, где нужно было спроектировать схему счётчика. Для неё нужно было написать таблицу истинности и по ней собрать цифровой блок, а студенты решили, что можно загуглить.

Ещё одна причина, почему у участников не получилось решить 3 части — они не работали с этой средой проектирования. Сделать первые две части задания и корректно реализовать топологию им помогли лишь написанные инструкции по проектированию.

Мотаем опыт на ус

Из проблем участников с третьим заданием организаторы извлекли важный урок о предварительном информировании участников о том, с чем им предстоит работать.

Изначально задание создавалось для тех, кто видел САПР Cadence Design System и осведомлен о том, как там проектировать топологии. В МИЭТ есть кафедры проектирования микросхем, на которых обучают работе в этой программе. Студенты-четверокурсники с кафедры проектирования топологии смогли бы, подумав, написать таблицу истинности. Но так уж вышло, что с этой кафедры на хакатон пришёл только один участник и командам пришлось импровизировать, в этом им помог их опыт в проектировании плат, который можно соотнести с проектированием микросхем. Ведь если человек разбирается, как соединяются резисторы или конденсаторы на плате, то он сможет, немного подумав, сделать это и на микросхеме.

Как пофиксить такой дисбаланс участников мы ещё будем думать. Например, можно провести серию вебинаров, на которых подробно раскрывалась бы роль топологии в проектировании микросхем и рассказывалось об инструментах, том же Cadence Design System.

Несмотря на некоторые сложности, участники отмечали, что им понравилось задание и они поучаствовали бы ещё. Остаётся этому только способствовать и заинтересовывать топологией больше молодёжи, тем более что спрос на топологов будет только расти ввиду открытия в России новых дизайн-центров.

Другие статьи о хакатоне

- Обзорный материал: Как мы впервые делали инженерный «хакатон» и что из этого вышло

Комментарии (17)

R9A_019

06.07.2022 12:42+5"На текущем этапе развития машина не может соотнести тот ток, который протекает, с толщиной шины, которую необходимо сделать." Можно по подробней? (Законы Максвелла и дифференциальный закон Ома достаточно просто позволяют промоделировать даже очень сложные распределения плотности тока, и мощностей вроде везде хватает)

sepuka

06.07.2022 13:33Анализ уже сделанного -- без проблем, с красивыми градиентами токов и падения напряжения. Синтез же, когда надо тянуть толстую шину далеко и утоньшать там, где надо заходить в отдельные мелкие элементы, да ещё и оптимально эти элементы располагать -- вероятно, как-то формализовать можно, но пока не особо выходит.

bowwow

06.07.2022 13:15+1На текущем этапе развития машина не может соотнести тот ток, который протекает, с толщиной шины, которую необходимо сделать. Поэтому это рассчитывает человек. С уверенностью можно сказать, что в обозримом будущем топологам «нашествия роботов» можно не опасаться.

нельзя ли на этапе проектирования schematic указать границы возможного тока по шине, а далее уже контролировать правилами DRC в топологии? На мой взгляд не такая сложная задача для машины.

Borkau

06.07.2022 13:15На текущем этапе развития машина не может соотнести тот ток, который протекает, с толщиной шины, которую необходимо сделать.

Не специалист, но ощущение, что это не какая-то непреодолимая задача. По крайней мере, таковой кажется со стороны. В чем сложность, если на пальцах?

saege5b

06.07.2022 16:19+2Конкретный софт не умеет, а его разработчики не хотят.

justPersonage

07.07.2022 09:11а его разработчики не хотят.

Почему?

saege5b

07.07.2022 12:50Там много причин может быть (я не разработчик данного продукта и что там происходит тоже не знаю):

продукт начнёт пересекаться с другой линейкой

нет профильных специалистов

менеджмент не видит необходимости в данном функционале (соотношение цена-функционал-затраты; просто не хотят раздувать функционал; что-то иное)

большие затраты на внедрение (движок не способен обработать, пересечение с хардкодом, иное)

sheblaev

07.07.2022 15:46А еще такая функциональность может существовать в продуктах Cadence года с 2005, но многие не знают как ей пользоваться и предпочитают ее не замечать.

BlamIvan

08.07.2022 18:29Очень большая вариативность возможных решений и с увеличением дизайна критерии оптимальности не столь очевидными становятся

checkpoint

06.07.2022 23:48Поясните, почем для обучения используется проприетарный Cadence, а не свободный Magic ? Что бы обнулить знания и навыки специалистов в эпоху санкций ?

BlamIvan

08.07.2022 09:52Думаю, основной задачей хакатона было познакомить студентов с маршрутом проектирования интегральных схем, а не с работой ПО. И что значит - проприетарным? Какой дизайн-центр не использует инструменты Cadence для проектирования аналоговых схем?

KstnRF

Пытаюсь относиться с пониманием, когда пишут "кремний и металлы". Кто с чем работает, как говориться. Но не стоит забывать, что есть и технологии на других полупроводниках и изоляторах, и не стоит забывать, что есть люди, которые этого не знают.

Фраза "сделали длинный провод" применительно к ИС- полез под заглавие проверить, не перевод ли это какой-то статьи. Нет, не перевод.![]()

Больше похоже на разбор ошибок, причём разбор текстовый. Было бы интересно глянуть картинки, схемы. Например, как реализовать делители на 4, 8 и т.д. А то начинаю сомневаться в собственной компетентности.

Раздел "Мотаем опыт на ус" видимо написан для себя, либо для участников хакатона. Потому что здесь практически ничего не понятно. Инфа для посвящённых, и соотвественно зачем она тут - у меня вопрос.

Не совсем понимаю, как кафедра по проектированию топологий соотносится с составлением таблиц истинности. Таблицы это своя дисциплина: схемотехника или микросхемотехника как называлась у нас, на которой разбираются логические операции. Но никак не топология.

"Открытие новых дизайн-центров в России"... Не заводов, не заводов...

Ringenium

Конечно не заводов, нужно проводить массовый ребрендинг производства в стране, чтобы студент хотел идти работать на это производство