Гугл переводит английское слово embarrassment как "смущение", но для британцев это не просто смущение. Для них это сродне ощущение во сне, в котором вы приходите на экзамен совсем не готовым и при этом голым. Когда британцы проводят семинар с какими-нибуть платами в далекой стране, они панически боятся, что плата не заработает и будет embarrassment. Поэтому они стараются использовать один тип плат в фиксированной конфигурации, если всего этого нельзя избежать вообще и просто показывать плату издалека.

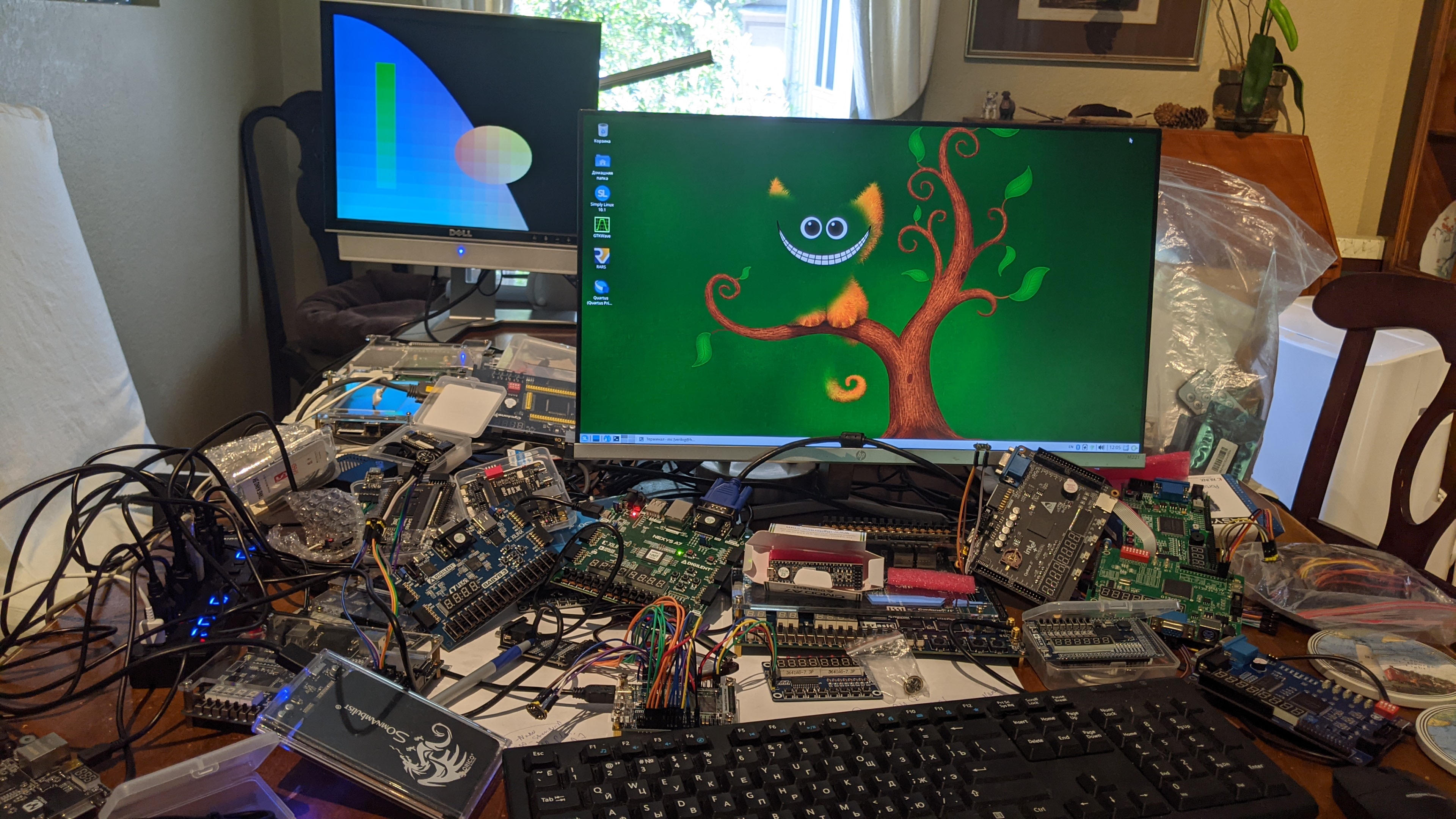

В глубине души британцы завидуют русским, которые "able to cope with difficulties". И вот вам свежий пример: когда выяснилось, что на более чем 300 заявок (UPD: сейчас уже больше 600) на Школу Синтеза Цифровых схем в 15 российских кластерах (UPD: уже 19, из них один белорусский) не хватает FPGA плат, группа волонтеров реализовала возможность легкого портирования учебных примеров на зоопарк из более чем 20 типов плат от Intel FPGA/Altera, Gowin и Xilinx/AMD, с идеей расшириться до 50 типов, с креативным добавлением недорогих внешних устройств.

В прошлых сезонах Школа Синтеза в основном использовала платы Omdazz и очень похожие на них платы RzRd a.k.a. EasyFPGA. Omdazz и RzRd отличаются только порядком внутренних номеров светодиодов - слева направо или справа налево, что скрыто от пользователя файлом .qsf, который привязывает номера ножек FPGA к названиям сигналов в коде на языке описания аппаратуры Verlog.

В новом сезоне решили купить еще 150 плат, но, как и в предыдущих сезонах, платы купили в последний момент и теперь они опоздают на первые два занятия - 23 сентября и 30 сентября. Наученный многолетним опытом, причем не только с россиянами, я знал, что так будет еще два месяца назад. Поэтому предложил набрать из кучи источников зоопарк плат, после чего написать примеры для Школы и скрипты таким образом, чтобы изолировать ученика от платы.

Схема описана в посте В России не любят Линукс, а я не люблю виртуальные машины. Что делать? Ученик клонирует git-репозиторий basics-graphics-music, после чего запускает скрипт для синтеза примера. При первом запуске скрипт спрашивает, какая у ученика FPGA плата, после чего ученик просто работает в независимом от платы модуле top.sv, который в свою очередь инстанциируется в board_specific_wrapper.sv (в который ученику как правило заглядывать не нужно). Скрипт сам выбирает toolchain для синтеза (Quartus, Vivado, Gowin IDE) и программы для прошивки конфигурации FPGA. Причем работает как под Linux, так и под Windows, используя встроенную в пакет Git for Windows командную оболочку Bash.

Платы, которые сейчас идут для школы из Китая, называются Saylinx и выглядят так. Это недорогие ($50) платы того же класса что и Omdazz, но у них пошире семисегментный индикатор (8 цифр, а не 4) и получше графика (5 бит на каждый из цветовых каналов). Cyclone IV FPGA в этих платах можно конфигурировать синтезированными процессорными ядрами микроконтроллерного класса. Для введения в синтез цифровых схем - ровно то, что нужно.

Примеры для этой платы я отлаживал в вагоне поезда Сан-Хосе - Санта-Барбара, куда я поехал со своим отцом. В процессе отладки справа от нас проплывали установки для запуска ракет от SpaceX (а до них выходы из шахт МБР). В SpaceX тоже нанимают людей делать дизайны на FPGA. Мой отец разрабатывал электронику для спутников в 1960-е годы и ездил из Киева в Зеленоград за 40 лет до того, как в Зеленограде побывал я сам. Моя же мама программировала станки с ЧПУ и тоже ездила в Зеленоград. Поэтому вся картина смотрелась гармонично.

Но как я уже сказал, платы Saylinx на Школу Синтеза Цифровых Схем еще не доехали, поэтому я бросил клич в телеграм-сообществе DigitalDesignSchool и несколько джентлеменов выразили желание помочь мне в деле создания коллекции примеров, работающих на любых платах.

Портированием на важную группу плат от компании Terasic занялись Александр Кириченко и Дмитрий Петренко из Екатеринбурга. Terasic - это тайваньская компания, которая плотно сотрудничает с Altera / ныне Intel FPGA. На платах от Terasic более эргономичные переключатели и кнопки, чем на платах с альтеровскими FPGA из Китая (Omdazz, Saylinx, Zeowaa, Piswords-6 и подобные). Кроме этого на Terasic как правило стоит более емкий FPGA, в который можно сконфигурировать например процессор, на котором может работать Линукс (Линукс требует наличия в процессоре TLB MMU - устройства управления страницами виртуальной памяти). При всех достоинствах Terasic они дороже (не $50-$70, а $150-$200-$400 и выше), а для массового обучения желательно иметь дешевые платы .

Вот на этом видео я пою ноты, и терасиковские платы хором их распознают, используя воткнутые в штырьки GPIO микрофоны INMP 441:

Вообще упражнениями со звуком мы занялись на школе с подачи учительницы флейты Марии Беличенко, которая приезжала в Сколково, МИРЭА, Бишкек и Тбилиси поиграть мелодии на концертной флейте Бёма (французской системы) для FPGA плат и поучить инженеров играть на блокфлейте. Вот Мария учит играть на блокфлейте выпускника МФТИ Виталия Павленко на конференции LaLambda эти летом в Грузии. Блокфлейту Виталия слушает плата Zeowaa (еще более дешевый предшественник Omdazz и Saylinx c с Altera Cyclone IV FPGA):

Вы наверное заметили, что на одной из плат много проводов. Это Terasic DE0-Nano, но ней вообще мало переферии, и чтобы обустроить ее для Школы, мы к ней подцепили, помимо микрофона, плату с широким семисегментным индикатором, 8 кнопочками и 8 лампочками. Такая плата делается на основе чипа TM1638 и стоит пару долларов. Эта плата оказалась чрезвычайно полезной не только для DE0-Nano, но и для DE0-Nano-SoC, DE10-Nano и кучи других плат, в том числе от Xilinx (Arty, Zybo) и Gowin:

Плата на основе TM1638 подсоединяется через три провода + питание и земля:

Плат от Терасика в России довольно много. Десяток DE0-Nano + несколько DE0-CV используют на ВМК МГУ, куда их пожертвовала зеленоградская компания НПО Элвис.

В Волгоградском ВолгГТУ есть несколько удобных плат DE2-115. В МЭИ - DE10-Lite (самая имхо оптимальная терасиковская плата для первого года обучения в университетах) и старые но все еще годные платы DE0.

Правда в DE0 (не путать с DE0-Nano, DE0-CV и DE0-Nano-SoC) стоит старый FPGA Cyclone III, поэтому с ней нужно использовать версию Altera Quartus 2013-года. При этом возникают проюлемы совместимости, которые мы сейчас яростно отлаживаем с преподавателем МЭИ Михаилом Графовым.

Коллекция терасиковских плат есть в ВШЭ МИЭМ. Но самые необычные платы этой группы водятся в Нижегородском Политехе. Там есть несколько штук вот таких монстров 2008 года под названием DK-DEV-3C120N, которые в разной комплектации стоили от $1300 до $2200, что для платы с дешевым Циклоном III необычно.

На эту плату я не смог нарыть никаких примеров со списком пинов в интернете. Но я смог найти для нее CD. Как? Она попала мне в руки в 2015 году, когда ее собирался выбросить некий маркетер. После этого я пытался подарить эту плату еще трем людям, но всякий раз она возвращалась мне обратно (она вместе с мезонинами занимает довольно большой ящик). И вот много лет спустя она оказалась полезна. Я ее оживил (см. файлы в репозитории) и теперь на ней можно показывать лабы с кнопочками, лампочками и семисегментными индикаторами, но не смог подсоединить к ней VGA и GPIO для микрофона. Впрочем, я думаю, что это могут сделать сами нижегородцы - я думаю, что если там 15 лет лежали платы на 10 тысяч долларов, то они скорее всего умеют с ними обращаться.

Пока я писал этот пост, мне доставили терасиковскую плату DE1-SoC. Она примечательна тем, что на ней делают лабы в Назарбаевском Университете в Астане. Адаптацию примеров для этой платы сделал Нурсултан Кабылкас, который сейчас пробует раскрутить преподавание компьютерной архитектуры и верификации в Казахстане. Нурсултан - молодой казах, который написал диссертацию в Университете Калифорния Санта-Круз по верификации суперскалярного RISC-V из Беркли. Он также поработал в AMD.

Лет пять назад университеты Казахстана всё искали европейских пофессоров с высоким хиршем, которые бы приехали и возглавили. Но еще тогда было понятно, что гораздо эффективнее привлекать свои кадры, которые пообтесались не только в академии, но и в индустрии.

Короче мне принесли DE1-SoC, которую тут же обнюхала моя собака:

Теперь перейдем к другой группе плат - SiPEED Tang на основе китайских FPGA Gowin (Go-Win - "идти и выиграть"). Лет 10 назад в китайские FPGA чипы никто не верил (китайские платы были на основе Xilinx и Atera), но Gowin меня приятно удивили, прежде всего низкой ценой и быстрым синтезом. Раньше GoWin использовал синтез от Synplicity (это широкоизвестная в 1990-е контора с синтезом, изначально написанным одним человеком; была куплена Synopsys-ом). Сейчас китайцы написали свое. Говорят, что не так хорошо оптимизирует, но для наших целей обучения достаточно. Что касается скорости синтеза - это песня: где Xilinx делает несколько минут, а Altera/Intel пару минут, Gowin делает за десятки секунд.

Gowin-ом в проекте примеров для Школы Синтеза Цифровых Схем занимаются Александр Рябов из Иннополиса и Виктор Вязовцев из Челябинской области.

Хотя на Gowin-ах есть интерфейс к HDMI, но к VGA их приходится подключать с помощью адаптера (1, 2). Также на них нет семисегментника и микрофона, но это все просто подключить и даже с дополнительными компонентами комплект гораздо дешевле плат от Terasic / Altera / Intel FPGA и Digilent / Xilinx / AMD.

Если вы подключаете к VGA и видите вот такие решетки слева, это означает, что вы перепутали биты каналов одного или нескольких цветов:

А теперь - платы от компании, которая изобрела FPGA, еще в середине 1980-х годов. Это Xilinx, сейчас часть AMD. Xilinx выпускает самые высокопроизводительные high-end FPGA, которые используются для плат, которые предназначены для прототипирования ASIC-ов и стоят $100 тысяч долларов и выше. У Xilinx есть и платы для обучения, но они дороже, чем аналогичные по параметрам платы от Altera.

Плата с Xilinx 4000 была моей первой FPGA платой в 1997 году. Затем я пользовался платами Xilinx в 2012-2017 для образовательных программ, но потом перешел на Altera из-за более высокой скорости синтеза, более дешевых плат и менее раздутого софтвера (бесплатная облегченная версия Xilinx Vivado сегодня занимает 80 гигабайт).

Но вот при приготовлении к Школе Синтеза Цифровых Схем я обнаружил, что:

1) МИЭТ и питерский ИТМО используют Digilent Nexys A7 / Nexys4 DDR с Xilinx Artix-7.

2) МИРЭА и Питерский Политех используют Digilent Arty A7 с Xilinx Artix-7.

3) В Минске инспользуют Digilent Nexys4 и Zybo Z7 (гибрид из Xilinx FPGA и ARM CPU).

Ну и я уже знал, что Xilinx много лет использовали в Самарском Университете.

Подержкой Xilinx для наших примеров занялись Ян Штундер из физфака МГУ (Zybo Z7), Илья Сторожев и Вячеслав Вахин из МИРЭА.

Поддержка Xilinx открыла для нас Беларусь и позволила передвинуть альтеровские платы из МИЭТ и ИТМО в другие города (вспомним, что на школе 600 заявок, а 150 плат Saylinx еще идут).

Посему я быстро накупил Nexys A7, Nexys4, Basys3, CMOD A7. Digilent Nexys4 (не путайте с Digilent Nexys4 DDR) - это редкая плата, которую Digilent выпускало недолго и быстро заменила на Digilent Nexys4 DDR. Но в свою недолгую жизнь Nexys4 попал в республику Беларусь, которая еще с советских времен была известна школой проектирования микросхем, которая образовалась вокруг их завода Интеграл. Я смог найти Nexys4 на EBay всего за $90 и вот она справа (обычно платы такого класса строят $350-$500).

Примеры у нас не только с кнопочками, лампочками и цветомузыкой. Во втором комплекте лаб, который пойдет после первого, есть элементы микроархитектуры - конвейеры, очереди FIFO, арбитры, кредитные счетчики и другие штуки, которые не очень хорошо покрываются даже программой Стенфорда, так что тут у российских вузов есть реальный шанс оказать впереди планеты, как советские физики в свое время. Правда этим же занимаются и китайцы, так что надо спешить.

Вот лаба с очередью FIFO на плате Nexys4: заполняем FIFO, опустошаем, а потом одновременно заполняем и опустошаем:

У нас (инициативной группе разработки портабильных примеров) пока нет никого, кто бы взял быка за рога с платами c Lattice FPGA (как с проприетарным маршрутом синтеза, так и с открытым от Yosys). Если есть желающие, кто готов сделать это аккуратно, сообщите:

Ну и пару слов про другие платы. Вот Zeowaa, плата, которую я использовал в семинарах с Иннополисом, в МИЭТ и на семинарах для для московских школьников под эгидой Роснано в 2019 году. Эта плата тогда стоила $17, а сейчас платы такого класса стоят $50-70. Единственный недосаток по сравнению с Omdazz и Saylinx - у нее нет внешней памяти, только внутренная блочная память.

Плату zeowaa сняли с производства, но в этом году я обнаружил у себя в гараже ящик таких плат, который остался у меня с 2019 года. Этот ящик пришел по почте когда я ездил в Москву и по возвращению я о нем забыл. Это оказалось очень кстати, так как я применил этот ящик на семинаре в Грузии. Таких плат еще осталось несколько десятков вокруг Иннополиса, посему их стоит поддерживать.

Другая снятая с производства плата - Piswords-6. Ее закупали для Школы Синтеза на ChipEXPO в 2021 году, но заказы постоянно отменялись. Тем не менее, я оставил несколько таких плат на семинаре в Киргизии, так что ее тоже стоит поддерживать. По классу она между Omdazz и Saylinx.

Среди учеников Школы этого года есть уже два (один - юноша из Башкирии), у кого есть вот такая плата. Она странная, потому что в ней де-факто есть одна кнопочка, одна лампочка, и при этом Ethernet. Зачем это? Тренировать молодежь анализировать сетевой трафик? К этой плате легко подсоединить модуль за $2 с кнопочками, лампочками и семисегментником, но она у меня почему-то не прошилась. Причем не прошились даже ее родные примеры. Кто знает, что с ней такое? Где я ошибся?

Среди альтеровских плат есть крошечные, которые вставляются в макетку (еще не поддерживается, можете попробовать сами сделать порт):

Есть и компактные платы с Gowin под названием Runber.

Такие же платы есть и от Digilent c Xilinx Artix-7 - CMOD A7. Я проводил с ней семинары весной 2017 года в Киеве:

Помимо платы CMOD A7 с Artix-7 есть еще плата с Spartan-7 под названием CMOD S7. Я о ней ничего особого не думал вплоть до сегодняшего дня, когда нашел на EBay платку, которая выглядит точно как CMOD S7, но называется PLTW S7.

Оказывается, есть американская организация, которая продвигает раннее обучение школьников наукоемким инженерным профессиям. Организация называется Project Lead The Way (PLTW). Они очевидно заказали у Digilent плату, похожую на ту, которую я использовал в Киеве в 2017 году и написали (в 2022 году) очень похожую программу занятий для школьников (счетчики, сдвиговые,регистры, конечные автоматы, системы контроля). Это своего рода приквел как к университетским программам (MIT 6.111), так и к Школе Синтеза, которая идет дальше, в микроархитектуру, процессоры, методы верификации итд.

Значимость такого образования очевидна: она дает преимущества для создания в стране сообщества разработчиков любой электроники, от космических ракет до айфонов, и PLTW еще раз подтверждает этот тезис.

Короче, если вы хотите записаться на занятие Школы Синтеза Цифровых Схем в эту субботу 23 сентября, вот регистрация. А если хотите принять участие в портировании примеров на платы и создании примеров - отмечайтесь в комментариях.

Комментарии (24)

Polarisru

21.09.2023 10:50-2Подскажите пожалуйста, а власти США в курсе, что Вы занимаетесь экспортом подсанкционных товаров в Россию?

https://www.bis.doc.gov/index.php/2011-09-14-14-10-06/russia-export-controls

YuriPanchul Автор

21.09.2023 10:50+4Какую строчку приведенного вами документа я, по-вашему, нарушаю? Можете процитировать?

olartamonov

21.09.2023 10:50Юр, я мимоходом чисто на всякий случай: учитывай, что микрофонов INMP441, тобой упомянутых, оригинальных в продаже нет, есть китайские клоны с очень разной степенью паршивости звука и глюками (вплоть до экземпляров, гадящих в I2S не в своём канале, дающих неразборчивый булькающий звук и т.п.). Могут быть неприятные сюрпризы.

Прямо настоятельно советую взять что-нибудь другое, если в Школе микрофоны используются.

YuriPanchul Автор

21.09.2023 10:50Хм, а я-то удивлялся, почему в Грузии были проблемы с микрофоном. Но у них в принципе есть порядка сотни микрофонов от диджилента, PMOD MIC3 с SPI интерфейсом, его можно поддержать как альтернативный. А какой микрофон ты рекомендуешь как альтернативу?

olartamonov

21.09.2023 10:50Я не занимался детальным изучением вопроса, просто сам недавно столкнулся с этими INMP441 и жалобами заказчика, что звук полное дерьмо. SPH0645LM4H, пожалуй, стоит попробовать.

firegurafiku

21.09.2023 10:50+1Несколько лет назад, когда преподавал в университете, покупал для лаб за свои деньги полдюжины плат Lattice MachXO3L StarterKit — стоили они тогда примерно 30 баксов за штуку. Сами платы довольно приятные, но слегка спартанские: есть программатор, тактовый генератор, несколько светодиодов и DIP-свитчей и тонна GPIO — если для лабы нужно что-то ещё (например, семисегментный индикатор или угловой энкодер, до звука и видео просто не успевали дойти за семестр), студенты собирали это что-то рядом на макетках. Это занимало кучу времени, но студенты готовы заниматься чем угодно, лишь бы код не писать.

Поэтому они стараются использовать один тип плат в фиксированной конфигурации, если всего этого нельзя избежать вообще и просто показывать плату издалека.

И правильно делают, в противном случае преподаватель только тем и будет заниматься, что бегать от студента к студенту, разбираясь с их «А почему у меня не работает?!». Я бы ещё и периферию всю использовал максимально одинаковую, чтобы не получить комбинаторный взрыв у себя в голове.

YuriPanchul Автор

21.09.2023 10:50Тем не менее, если это пробить (а мы ставим именно такой эксперимент), все участники получают дополнительный опыт. Особого взрыва после преодоления начальных трудностей быть не должно,так как врапперы и скрипты делают платы одинаковыми для участников, и запуск скрипта одним движением изолирует участника от toolchain. Замечу что в больших электронных компаниях скрипты синтеза и симуляции изолируют пользователя даже от Synopsys versus Cadence, то есть мы следуем принятым индустриальным практикам.

ovn83

21.09.2023 10:50+1Я за Xilinx, он рулит, Alterу как то не перевариваю, первая ПЛИС xc9500, 20 лет назад. С платой от майнера на Zynq, с платой расширения, можно чудеса творить.

https://youtu.be/I7Awfnm8Etk?si=b_RdGnBAy1SfQeFl

YuriPanchul Автор

21.09.2023 10:50Очень интересно, спасибо, надо бы такую приспособить тоже

ovn83

21.09.2023 10:50https://electronix.ru/forum/index.php?/topic/158364-дешёвая-отладка-zynq-7000-c-али/#comments

Вот тема по отладочной плате.

vi_al

21.09.2023 10:50

kosmosmars

21.09.2023 10:50А есть рекомендации платы, которая подошла бы для Школы синтеза, но при этом была бы максимально бюджетной из возможных? Зоопарк разных плат вводит в ступор

Vektor975

21.09.2023 10:50Существуют ли платы с отечественными плисами, приходилось ли вам с ними соприкосаться?

YuriPanchul Автор

21.09.2023 10:50Да, конечно, существует платы из Воронежа с аналогами Altera FLEX10K и более новыми устройствами. На них несомненно можно портировать примеры, но для массового обучения эти платы дорогие (>$1000)

https://rg.ru/2022/11/22/reg-cfo/sokratit-razryv.html

https://abireg.ru/newsitem/94186

Еще какой-то ПЛИС сделали в Миландре, но я про это что-то краем глаза читал.

https://www.milandr.ru/upload/iblock/60c/60cdbff6fae9ad208ada6109a1f3cd9f.pdf

checkpoint

21.09.2023 10:50Юрий, я умею в Yosys для Lattice ECP5 и iCE40 (вот пример проекта), обьясни в чем суть задачи ?

YuriPanchul Автор

21.09.2023 10:50О, это прекрасно. Давай созвонимся и все это обсудим. Вот я записал видео как портировать на платы с Xilinx, тот же подход применим для Lattice. Нужно написать board-specific wrapper (пример), инстанциировать в нем board-independent top (в котором работает ученик), а также скрипты на bash (пример) для поддержки тулчейна под линуксом и (если есть) под Windows. Пришлите мне ваш емейл и телеграм для включения в соотвествующие рассылки, чаты и созвоны. Созвон будет завтра, сразу можно ввести в курс дела.

checkpoint

21.09.2023 10:50Ок, отписался. Тут надо понять для какой платки делать порт. У меня в основном свои платы, но кое-что есть в загашниках с Алиэкспресса.

YuriPanchul Автор

21.09.2023 10:50вы мне в частное сообщение или на емейл присылали? Мне не пришло yuri@panchul.com

Joysi

Altera Max10 10M50 (брал полтора года назад за чуть ) для практике по книге =)