В комментариях к моей статье про управление RGB светодиодами средствами блока UDB микроконтроллеров PSoC фирмы Cypress было высказано мнение, что неплохо бы в начале статьи кратко рассказать, что такое вообще UDB. Как я уже отметил в статье, про UDB кратко не написать, но можно просто перевести фирменную документацию на него, чтобы познакомить отечественного читателя со столь мощным средством для реализации микропрограммных функций.

Но прежде, давайте рассмотрим, что вообще такое PSoC. PSoC — это набор семейств микросхем фирмы Cypress для реализации систем на кристалле. Разные семейства имеют разное процессорное ядро (для PSoC 3 это MCS-51, для PSoC 4 — Cortex M0, для PSoC 5LP — Cortex M3, а для PSoC 6 — сразу два: Cortex M0+ и Cortex M4) и набор программируемой логики. Причём логика эта не чисто цифровая, есть там и аналоговые вещи. Кроме набора различных АЦП, там присутствуют также аналоговые коммутаторы. Можно даже программно связывать ножки через аналоговые цепи, правда, сопротивление у цепи будет измеряться килоомами. Есть внутри PSoC и операционные усилители, которые можно программно коммутировать, а значит — строить на них разные аналоговые блоки.

Кстати, PSoC’и можно питать любым напряжением от 2.7 до 5.5 вольт. То есть не нужно думать о каких-то стабилизаторах ни при батарейном питании, ни при питании от USB.

Но про аналоговые вещи я написал чисто для красного словца. Сейчас мы сосредоточимся на вещах цифровых. В большинстве современных контроллеров имеются мощные периферийные блоки, которые предоставляют огромное множество функций. Но на практике, в каждой конкретной программной разработке эти блоки используются не полностью, а только частично. И в PSoC вместо кучи добра реализована программная логика, похожая на логику классических ПЛИС. Соответственно, на ней можно реализовать именно те блоки, которые нужны, включив их именно в те режимы, которые требуются. А на неиспользуемые режимы ресурсы не тратить, отдав их на реализацию каких-то собственных вещей.

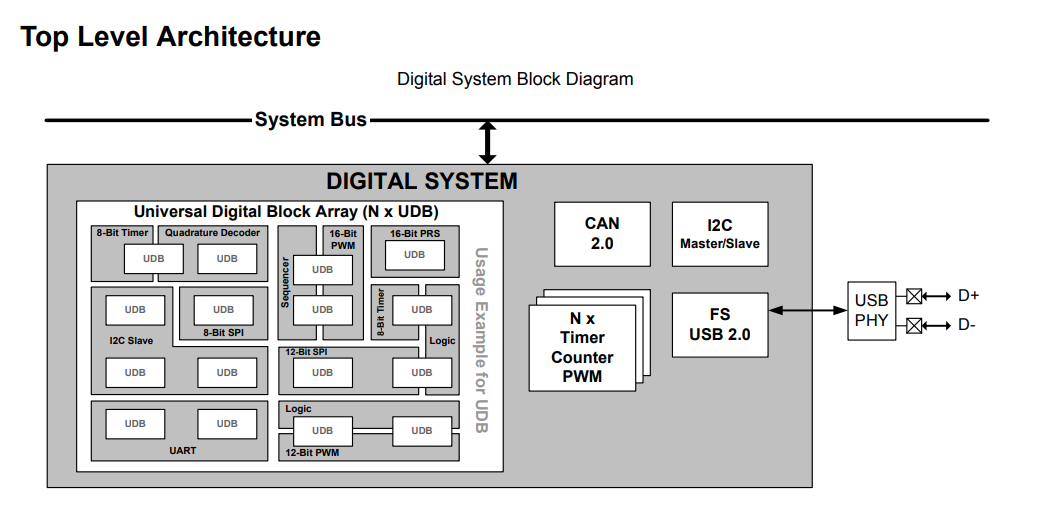

И вот здесь часто возникает некоторое недопонимание. Многие разработчики привыкли к тому, что Программируемые Логические Интегральные Схемы (ПЛИС) бывают двух видов: CPLD и FPGA. Поэтому многие, кто слышал про PSoC, считают, что там кроется некая CPLD-шка, которую можно программировать на языке Veriolg. По факту — и да, и нет. Некоторое количество PLD (без «C», просто PLD) там действительно есть, и на Verilog их программировать действительно можно. Но реально, эти PLD входят в состав блоков UDB. И именно UDB является основным элементом программируемой логики, реализованной в PSoC. Этот блок чрезвычайно самобытен и предоставляет просто широчайшие возможности для разработчика. Рассмотрим рисунок из фирменной документации, поясняющий суть использования блоков UDB.

Так как я изучал всё на примере семейства PSoC 5LP, переводить буду документацию именно на него. Но перед тем, как начать, скажу пару слов про цену этих контроллеров. Если зайти на Ali Express и посмотреть на макетные платы для них, возникает грустное ощущение. Прямо скажем, по сравнению с STM32-DISCOVERY они ещё ничего, а вот на фоне макеток STM32F103C8T6 дороговаты. В первую очередь, это связано с тем, что на фирменных макетках всегда стоит не один, а два таких контроллера. Функции JTAG реализуются на PSoC 5LP, даже если целевой контроллер и PSoC 4 (у последнего обычно нет порта USB).

Но и поделив цену на два, всё равно получаем, что она выше, чем у сходного по процессорному ядру STM32F103. Тем не менее, если мы добавим к тому самому STM32 снаружи ещё и даже самую простенькую CPLD, то суммарная цена уже выйдет в пользу PSoC. А ещё добавим потерянные ножки на связь этих двух корпусов (у PSoC же все связи внутри). А ещё цену квадратных сантиметров платы. Вот и получается, что, если нужно работать только с процессорным ядром, в PSoC действительно нет необходимости. Если же нужно какой-то функционал вынести на микропрограммный или аппаратный уровень — тут нужен именно PSoC. На нём система выйдет дешевле и проще.

На самом деле, у меня есть маниакальная идея попробовать сделать аппаратную поддержку ядра нашей ОСРВ МАКС. Для этого я изучил методику разработки Bare Metal приложений под Altera V SoC (увы, выяснилось, что особенность архитектуры там такая, что ОС можно замедлить, но нельзя ускорить — одиночные запросы к аппаратуре там идут с бешеной латентностью). Для этого же я начал осваивать и PSoC. До разгона ядра ещё не дошёл (есть только общие мысли), но сама идея программирования UDB мне жутко понравилась. Само собой, я теперь заинтересован в том, чтобы донести эту идею до максимального числа отечественных программистов. Поэтому приступаем к переводу соответствующей части фирменной документации Cypress, посвященной UDB. Нумерацию глав и рисунков сохраняем в соответствии с оригинальным документом.

UDB. Что же это такое? Часть 1

21. Универсальные цифровые блоки

В этой главе мы рассмотрим, как универсальные цифровые блоки (англ. Universal Digital Blocks, UDB) позволяют разрабатывать программируемые цифровые периферийные функции. Архитектура UDB обеспечивает баланс между гранулярностью конфигурации и эффективной реализацией. UDB состоят из комбинации нескоммутированной логики, схожей с программируемой логической матрицей (ПЛМ, англ. PLD), структурированной логики (операционные автоматы, далее — Datapath) и гибкой схемы трассировки.

21.1 Особенности

- Для обеспечения оптимальной гибкости каждый UDB содержит следующие компоненты:

• 8-битный Datapath на базе АЛУ (Arithmetic and Logic Unit, ALU) с хранилищем инструкцией на 8 слов, несколькими регистрами и буферами FIFO;

• две PLD, каждая из которых имеет 12 входов, восемь конъюнктивных термов (англ. Product Terms, PT) и четыре выхода макроячеек;

• регистры управления и статуса;

• модули тактирования и сброса. - PSoC 5LP содержит массив размером до 24 UDB.

- Гибкая трассировка между элементами массива UDB.

- Элементы UDB могут разделяться или связываться в цепочки для создания более крупных функций.

- Гибкая реализация ряда цифровых функций, включая таймеры, счетчики, широтно-импульсные модуляторы (в том числе ШИМ с генератором мёртвой зоны), UART, шину I2C, шину SPI и проверку/генерирование CRC.

21.2 Блок Схема

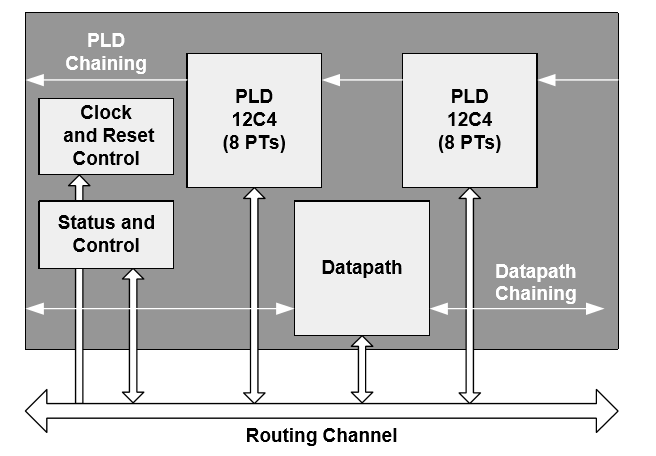

Рисунок 21-1 показывает UDB в виде конструкции, содержащей два базовых логических блока PLD, Datapath и функции управления, статуса, тактирования и сброса.

Рисунок 21-1. Блок схема UDB.

21.3 Как это работает

Основными компонентами UDB являются:

- PLD (2). На входы этих блоков подаются данные из трассировочных ресурсов. В них реализуется комбинаторная логика и защелкивание данных, что позволяет реализовать конечные автоматы, управлять операциями блока Datapath, настраивать входные условия и управлять выходами.

- Datapath. Этот блок содержит динамически программируемое АЛУ, четыре регистра, два буфера FIFO, компараторы и генерацию условий.

- Управление и статус (Status and Control). Эти модули предоставляют механизм взаимодействия микропрограмм центрального процессора (ЦП, англ. CPU) и синхронизации с операциями UDB. Регистры управления воздействуют на внутренние элементы, а регистры статуса считывают состояние внешних элементов.

- Управление тактированием и сбросом (Clock and Reset Control). Эти модули обеспечивают выбор и включение тактирования, а также выбор сброса внутри UDB.

- Объединение сигналов в цепочку (Chaining Signals). PLD и Datapath имеют сигналы, которые позволяют связывать соседние блоки в цепочку для создания функций с более высокой разрядностью.

- Трассировочный канал (Routing Channel). UDB соединены с трассировочным каналом через программируемые коммутационные матрицы для связи между блоками в рамках одного UDB и для связи с другими UDB в массиве.

- Интерфейс системной шины (Sysytem Bus Interface). Все регистры и ОЗУ в каждом UDB проецируются на системное адресное пространство, и доступ к ним можно получить как при помощи центрального процессора, так и через прямой доступ к памяти (англ. Direct Memory Access, DMA) в виде 8-битных и 16-битных данных.

21.3.1. PLD

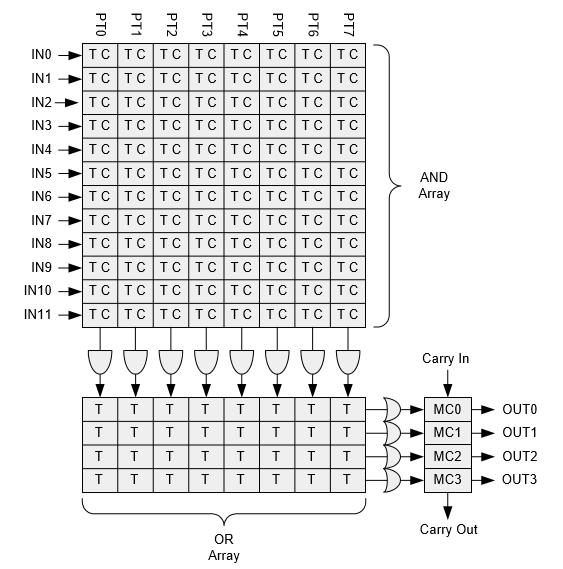

В каждом UDB есть две PLD «12С4». Блоки PLD, показанные на рисунке 21-1, можно использовать для реализации конечных автоматов, обработки данных ввода/вывода и для создания табличной логики (англ. Lookup Table, LUT). Кроме того, PLD можно настроить для выполнения арифметических функций, установки последовательности Datapath и генерации статуса. Общая логика может быть синтезирована и спроецирована на блоки PLD. Этот раздел содержит обзор архитектуры PLD.

PLD имеет 12 входов, которые передают информацию на 8 конъюнктивных термов в массиве AND. В каждом конъюнктивном терме можно выбрать прямой (true, Т) или инверсный (complement, С) вход. Выход конъюнктивных термов идет на вход массива OR. Буква ‘C’ в 12С4 показывает, что термы OR постоянны для всех входов, а каждый вход OR может получить программный доступ к любому конъюнктивному терму. Такая структура обеспечивает максимальную гибкость и гарантирует, что все входы и выходы могут быть перемещены.

Рисунок 21-2. Структура PLD 12С4.

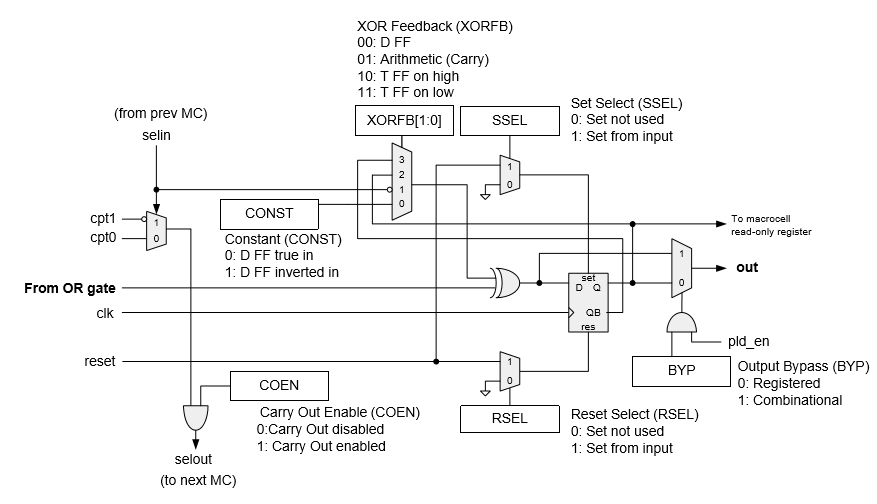

21.3.1.1 Макроячейки PLD

Архитектура макроячеек показана на рисунке 21-3. Выход управляет трассировочным массивом и может быть защелкнут или комбинаторным. Для защелкивания используется D-триггер с прямым или инверсным входом либо T-триггер с высоким или низким входным уровнем. Выходной триггер может быть установлен или сброшен при инициализации или асинхронно при нормальной работе, по внешнему сигналу из трассировочного канала.

Рисунок 21-3. Архитектура макроячейки.

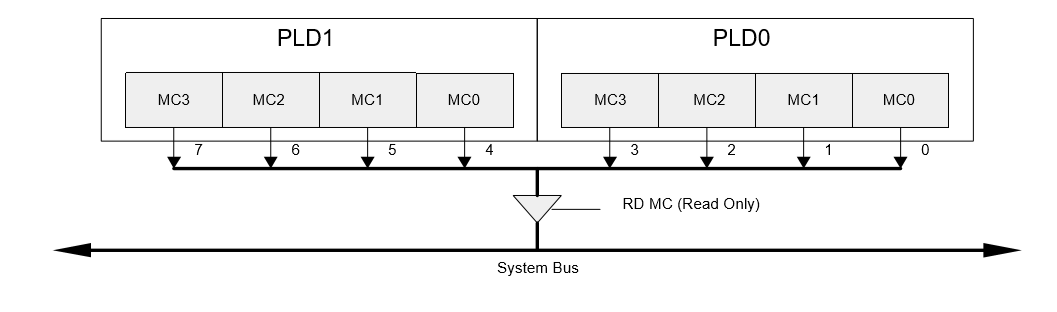

Регистр макроячейки PLD «только для чтения»

Помимо управления трассировочным массивом, выходы макроячеек обеих PLD спроецированы на адресное пространство в виде 8-битного регистра «только для чтения», доступ к которому можно получить при помощи CPU или DMA.

Рисунок 21-4. Регистр макроячейки PLD «только для чтения».

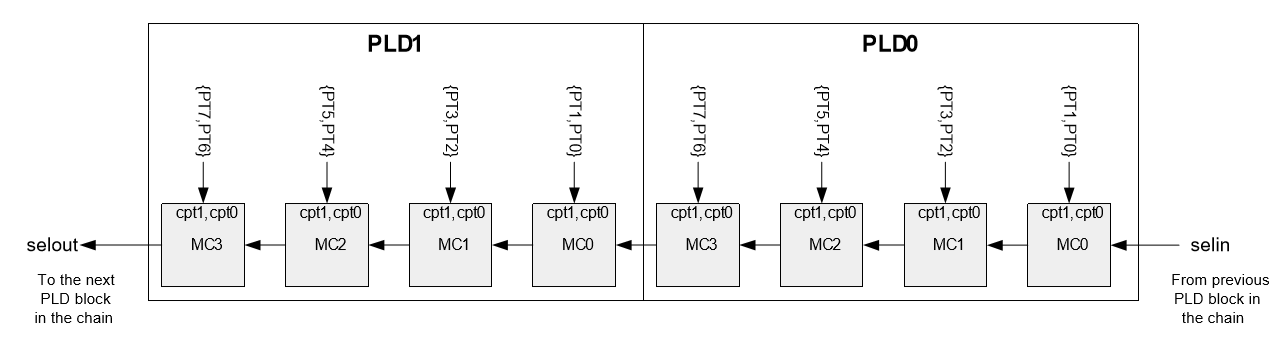

21.3.1.2 Цепь переносов PLD

PLD связаны вместе в адресации UDB. Как показано на рисунке 21-5, вход цепи переносов «selin» пробрасывается из предыдущего UDB в цепи, через каждую макроячейку в обеих PLD, после этого направляется на следующий UDB в виде выхода цепи переносов «selout». Для поддержки эффективного размещения арифметических функций, генерируются специальные конъюнктивные термы (PT), которые используются в макроячейках совместно с цепочкой переносов.

Рисунок 21-5. Цепь переносов PLD и входы специальных конъюнктивных термов.

21.3.1.3 Конфигурация PLD

Каждая PLD предстает перед CPU или DMA в виде ОЗУ с 16-битным доступом. Массив AND имеет 12?8?2 бит или 24 байта для программирования, а массив OR имеет 4?8 бит или 4 байта для программирования. Кроме того, каждая макроячейка имеет один байт конфигурации, итого, 32 байта конфигурации на каждую PLD. Так как каждый UDB имеет 2 PLD, всего конфигурация каждого UDB занимает 64 байта.

В следующий раз мы будем рассматривать Операционные автоматы (Datapaths).

Комментарии (6)

vitmeat

18.12.2018 13:37Прекрасная статья, вообще считаю что за комплексами проц+логика будущее.

Вопросы:

— какова скорость логики (чем ограничено)?

— я так понимаю почти все интерфейсы (uart, i2c) кроме высоко скоростных (usb) отсутствуют и реализуются на этом udb?

— можно ли делать вычислительные инструкции на базе этого udb?

EasyLy Автор

18.12.2018 13:58Когда говорим о скорости, помним, что это живёт в контроллере с ядром Cortex M3. Насколько я помню, у него предельная частота около 80 МГц (у меня сейчас в текущем проекте стоит 72). Выше не может быть в принципе. А так — в упомянутом текущем проекте у одного блока Fmax была чуть выше 60 МГц. Одно неверное движение, и она упала до 16. Изменил режим входной ножки — вернулась обратно. Бывали случаи, когда предельная частота блока была в районе 24 МГц, изменяя логику — удавалось поднять до 33. В общем, порядки значений ясны. Значение Fmax, как и для всей программируемой логики, выдаётся в отчётах о компиляции.

Интерфейсы в PSoC реализуются двояко. Зависит от семейства. Может быть один UART аппаратный, остальные — на UDB. То же касается и других интерфейсов. Всё надо смотреть в документе TRM. На первом рисунке к этой статье (который ещё без номера) видно, что у PSoC5LP имеются аппаратные таймеры-ШИМы, имеется аппаратный CAN, имеются аппаратный I2S и аппаратный USB. остальное — через UDB. У других семейств — иначе.

Про вычислительные инструкции — будет понятнее после следующей порции перевода.

PTM

18.12.2018 16:55дико плюсую, тк инфы про udp маловато… а дома есть штук 15 PSOC4… для разминки самое то)

nerudo

Интересно, но без поддержки в тулчейне пока непонятно как этим эффективно пользоваться. Ждем следующей серии.

EasyLy Автор

Всё как раз началось с практической статьи. Но оказалось, что не все знакомы с самой идеей UDB. В планах — делать сухие переводы документа (в нём практики нет) и перемежать их с практическими авторскими вещами. Если тема не окажется неинтересной, и планы не будут изменены.

nerudo

Спасибо, пропустил.