Продолжаем рассматривать UDB на основе документации Cypress. И в этот раз предметно изучим Datapath, операционный автомат.

Предыдущая статья:

UDB. Что же это такое? Часть 1. Введение. PLD.

21.3.2 Операционный автомат (Datapath)

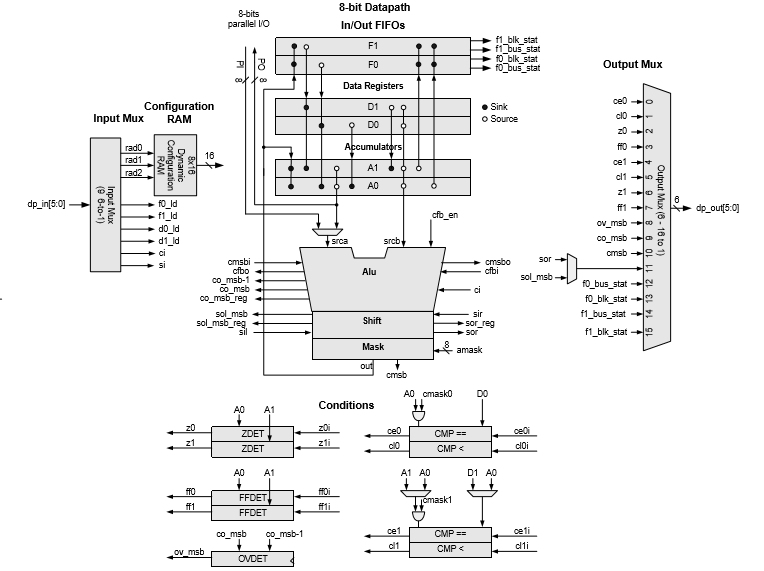

Datapath, показанный на рисунке 21-6, содержит 8-битное однотактное ALU и связанные с ним схемы сравнения и выработки флагов условий. Блоки Datapath соседних UDB могут объединяться в цепочки для повышения разрядности. Datapath включает в себя небольшое ОЗУ динамической конфигурации, которое может динамически выбирать выполняемую операцию в определенном цикле.

Datapath оптимизирован для реализации типичных встраиваемых функций, таких как таймеры, счетчики, ШИМы, PRS, CRC, регистры сдвига и генераторы мертвой зоны. Добавление функций сложения и вычитания обеспечивает поддержку цифровых дельта-сигма операций.

Рисунок 21-6. Верхний уровень Datapath.

21.3.2.1 Обзор

Следующие главы представляют обзор основных особенностей Datapath.

Динамическая конфигурация

Динамическая конфигурация – возможность менять работу и внутренние связи Datapath в каждом цикле под управлением секвенсора. Это реализовано с помощью конфигурационной памяти (конфигурационного ОЗУ), в которой хранится восемь уникальных конфигураций. Входной адрес этой памяти может быть проброшен из любого блока, подключенного к трассировочным ресурсам, обычно из логики PLD, контактов ввода-вывода или из других Datapath.

ALU

ALU может выполнять восемь функций общего назначения: инкрементировать, декрементировать, складывать, вычитать, а также выполнять логические операции AND, OR, XOR и PASS. Выбор функций определяется конфигурационной памятью для каждого цикла. Операции независимого сдвига (влево, вправо, перестановки нибблов), а также операции наложения маски доступны на выходе ALU.

Условные конструкции

Каждый Datapath имеет два компаратора с побитовым маскированием, которые можно сконфигурировать для выбора множества входов регистров Datapath в качестве аргументов. Другими выявляемыми условиями могут быть все нули, все единицы и переполнение. Эти условия формируют основные выходы Datapath и могут быть проброшены на цифровые линии трассировки либо входы других функций.

Встроенные CRC/PRS

Datapath имеет встроенную поддержку однотактовых вычислений CRC и генерации псевдослучайных последовательностей (англ. Pseudo Random Sequence, PRS) с заданными разрядностью и порождающим полиномом. Чтобы достигнуть разрядности более 8 бит, сигналы могут быть связаны в цепочки между Datapath. Эта возможность управляется динамически, а значит может чередоваться с другими функциями.

Настраиваемый номер старшего бита

Номер старшего бита (англ. Most Significant Bit, MSB) арифметической функции и функции сдвига может быть задан программно. Это обеспечивает поддержку функций CRC/PRS переменной длины, и, в совокупности с маскированием выходных данных ALU, позволяет реализовывать таймеры произвольной длины, счетчики и блоки сдвига.

Входные/выходные буферы FIFO

Каждый Datapath имеет два 4-байтовых буфера FIFO, каждый из которых можно настраивать для работы в качестве входного буфера (CPU или DMA записывает данные в FIFO, Datapath считывает FIFO), либо в качестве выходного буфера (Datapath записывает в FIFO, а CPU или DMA читает из него). Эти буферы FIFO генерируют статус, который может быть проброшен для взаимодействия с секвенсорами, прерываниями или запросами DMA.

Связывание в цепочки

Datapath можно настроить для связывания условий и сигналов в цепочку с соседними Datapath. Сдвиг, перенос, захват и другие условные сигналы можно объединять в цепочки для создания арифметических функций большей разрядности, а также функций сдвига и функций CRC/PRS.

Временное мультиплексирование

В приложениях с избыточной дискретизацией или где не нужны высокие тактовые частоты, один блок ALU в Datapath можно эффективно делить между двумя наборами регистров и генераторов условий. Выходы ALU и регистра сдвигов защелкиваются и могут быть использованы в качестве входных данных в последующих циклах. К примерам использования можно отнести поддержку 16-битных функций в одном (8-битном) Datapath или чередование операций генерации CRC с операциями сдвига данных.

Входы Datapath

Datapath имеет четыре вида входов: конфигурационные, управляющие, а также входы данных (последовательных и параллельных). Конфигурационные входы выбирают адрес ОЗУ динамической конфигурации. Управляющие входы загружают регистры данных из FIFO и выгружают выходные данные аккумулятора в FIFO. К последовательным входам данных относятся входы сдвига и переноса. Порт входа параллельных данных позволяет получать до 8 битов данных из трассировочных ресурсов.

Выходы Datapath

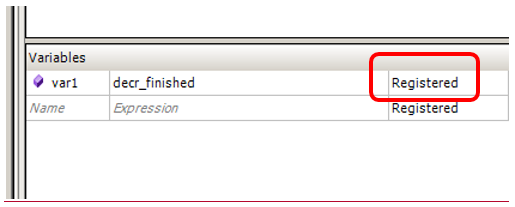

Всего существует 16 сигналов, вырабатываемых в Datapath. Некоторые из них являются условными сигналами (например, сравнения), другие являются сигналами статуса (например, статуса FIFO), а остальные являются сигналами данных (например, выход регистра сдвига). Эти 16 сигналов мультиплексируются в 6 выходов Datapath и направляются на трассировочную матрицу. По умолчанию, выходы синхронизируются с тактовой частотой, что создает конвейеризацию с задержкой на 1 такт. Также их (выходы) можно переключить в асинхронный (комбинаторный) режим (см. примечания переводчика).

Примечание переводчика

Я долго искал, в чём заключается синхронность выходов Datapath. Мой опыт говорил, что всё там асинхронно. Оказалось, что имеется в виду не столько состояние выходов, сколько вот эта настройка редактора для переменных, основанных на них.

Это заставит редактор сгенерировать такой Verilog код:

/* ==================== Assignment of Registered Variables ==================== */

always @ (posedge clock)

begin : register_assignments

var1 <= (decr_finished);

end

Если переключить на комбинаторный режим

код станет таким:

assign var1 = (decr_finished);

Но всё это относится к переменным, сгенерированным на основе выходов Datapath. А сами выходы всегда асинхронны. И их имена (в данном примере decr_finished) можно использовать без ввода дополнительных переменных.

Рабочие регистры Datapath

Каждый модуль Datapath имеет шесть 8-битных рабочих регистров. CPU или DMA имеют доступ на чтение и запись ко всем регистрам.

Таблица 21-1

| Тип | Имя | Описание |

|---|---|---|

| Аккумулятор | А0, А1 | Аккумуляторы могут быть как источником, так и приемником для ALU. Они также могут быть загружены из регистра данных или FIFO. Аккумуляторы обычно содержат текущее значение функции (например, счетчика, CRC или сдвига). Эти регистры теряют свои значения при переходе в спящий режим и при сбросе принимают значение 0х00. |

| Данные | D0, D1 | Регистры данных обычно содержат константы функции, например, значение сравнения ШИМ, период таймера или полином CRC. Эти регистры сохраняют свои значения при нахождении в спящем режиме. |

| FIFO | F0, F1 | Два 4-байтных буфера FIFO предоставляют как источник, так и приемник для буферизированных данных. FIFO могут быть настроены как буферы входа, так и буферы выхода, или как один буфер входа и один буфер выхода. Сигналы статуса показывают статус чтения и записи этих буферов. К примерам использования можно отнести буферизованные данные TX и RX в SPI или UART, а также буферизованные данные ШИМ и буферизованные данные о периоде таймера. Эти регистры не сохраняют свои значения в спящем режиме и при сбросе принимают значение 0х00. |

В следующей статье мы начнем разбираться с FIFO.