Школа синтеза цифровых схем, о которой вы могли читать месяц назад в посте "Проектировщики RISC-V из Yadro покажут школьникам как проектировать процессоры" - прошла на ура. Все 25 мест в офлайне в Сколково были все время заняты. Присутствовали школьники, студенты, преподаватели вузов и кружков. Всего было подано 86 заявок. Все ~70 FPGA плат которые пожертвовали Наносемантика, Максим Маслов и другие, были быстро разобраны, люди охотно проходили роснановский онлайн-курс чтобы получить сертификат и соответственно плату.

Из новых пунктов программы больше всего интереса вызвали опыты по распознаванию мелодий с помощью zero-crossing и конечных автоматов, реализованных в ПЛИС. Это занятие провели преподавательница флейты Мария Беличенко (инстаграм) и молодые инженеры Семён Москоленко (МИРЭА) и Виктор Прутьянов (МФТИ, Сколтех, SberDevices):

Видео от Лилии Антоненко.

Так как школа оказалась популярна, мы решили расширить ее до полноценного семестрового курса по субботам, с объемом материала на уровне университетских лабораторных по FPGA (типа MIT 6.111), к которым мы добавили элементы компьютерной архитектуры, базовый туториал для ASIC и некоторые умения из промышленности.

Новый цикл занятий начнется с 30 октября 2021, закончится 12 февраля 2022, и будет проходить по субботам в Технопарке Сколково в Москве, с трансляцией в казанский Иннополис и другие места. Регистрация уже открыта.

В этом году будет 7 занятий. Фактически 3-х дневный курс школы на ChipEXPO с упражнениями на FPGA будет расширен на 7 дней (суббот).

Затем, под Новый Год в рамках школы пройдет туториал по Cadence Genus & Innovus с синтезом ядра schoolRISCV для ASIC. Продуктами от Cadence пользуются разработчики массовых микросхем в крупных электронных компаниях, которые платят за лицензии на эти программы сотни тысяч и миллионы долларов. Поэтому такой туториал - это редкая возможность для школьника или студента почувствовать себя на месте проектировщика микросхемы для смартфона или игровой приставки.

Студенты запустят скрипты и рассмотрят результаты выполнения шагов:

Логический синтез.

Определение плана начального размещения.

Определение ячеек ввода-вывода.

Определение сети подачи питания.

Синтез дерева тактовых сигналов.

Окончательное размещение.

Трассировка сигналов.

Статический временной анализ с учетом размещения и трассировки.

Окончательная проверка DRC и LVS.

Генерация GDSII файла который отправляется на фабрику, которая выпекает микросхемы.

А после Нового Года, начиная с 15 января - три более продвинутые занятия с комбинацией schoolRISCV и элементов микроархитектуры. Докладчики на ChipEXPO уже рассказывали про очереди FIFO, кредитные счетчики, арбитры, многобанковые памяти и процессорные кэши. Но там это было абстрактно, а на новой школе это будет привязано к конкретным процессорам на FPGA плате, чтобы было понятно зачем это:

Элементы микроархитектуры 1: очереди FIFO и кредитные счетчики.

Разбор примера: процессорное ядро schoolRISCV посылает сообщения другому ядру schoolRISCV через блок шифрования сообщений. Очередь FIFO ставится после конвеера блока шифрования. Запись данных в блок шифрования происходит через запись в определенные адреса в адресном пространстве первого процессорного ядра, чтение данных из FIFO происходит через чтение из определенных адресов в адресном пространстве второго процессорного ядра.

Элементы микроархитектуры 2: арбитры, банки и разделение памяти.

Разбор примера: три процессорных ядра schoolRISCV читают свои потоки инструкций из общей памяти, используя арбитр для доступа к ней. Демонстрация существенного снижения скорости работы всех трех ядер. Введение сначала двух, потом четырех банков памяти. Демонстрация повышения скорости работы в зависимости от того, читают ли процессорные ядра одни и те же адреса или разные.

Элементы микроархитектуры 3: строим процессорный кэш.

Разбор примера: подключаем процессорное ядро schoolRISCV к контроллеру внешней SDRAM памяти на FPGA плате. Наблюдаем потерю производительности по сравнению с использованием внутренней памяти. Подключаем простейший ассоциативный кэш и наблюдаем компенсацию потери производительности.

Домашний проект для особо продвинутых: подключить к schoolRISCV пример контроллера кэша на верилоге из приложения к учебнику Хеннесси-Паттерсона.

Наконец, в феврале на школе будет организована имитация собеседования (в формате олимпиады / письменного экзамена) и его разбор, чтобы учащиеся поняли, что их ждет при поступлении на работу в серьезную электронную компанию и готовы ли они к этому.

Не все мероприятия школы и бизнес-программы на ChipEXPO прошли гладко. Например основатель американского стартапа Redwood EDA Стив Гувер (Steve Hoover) подготовил интересный туториал по изобретенному им языку TL-Verilog, и по использованию этого языка для проектирования конвейерного RISC-V процессора - но туториал в эфир не вышел, так как в Сколково пришлось поменять Zoom линк в то время, когда Стив в Америке спал.

Тем не менее Стив выложил туториал на гитхаб и в ютюб. Я очень рекомендую посмотреть этот туториал тем читателям, у которых есть честолюбивая мечта изобрести новый язык описания аппаратуры. Дело в том, что верилог, при всей моей любви к нему, является очень трудозатратным языком. Когда вы описываете в верилоге конвейер и строите сигналы и логику для остановок (stalls) и байпасов (forwarding bypass), не говоря уже о двойных буферах между стадиями (skid-buffers), FIFO для принятия результатов, кредитных счетчиков и прочих перемычек с изолентой - получается много кода, в котором легко делаются баги. Стив попытался сделать шаг по автоматизации этого процесса и его опыт полезно изучить, чтобы понять куда он пробует копать.

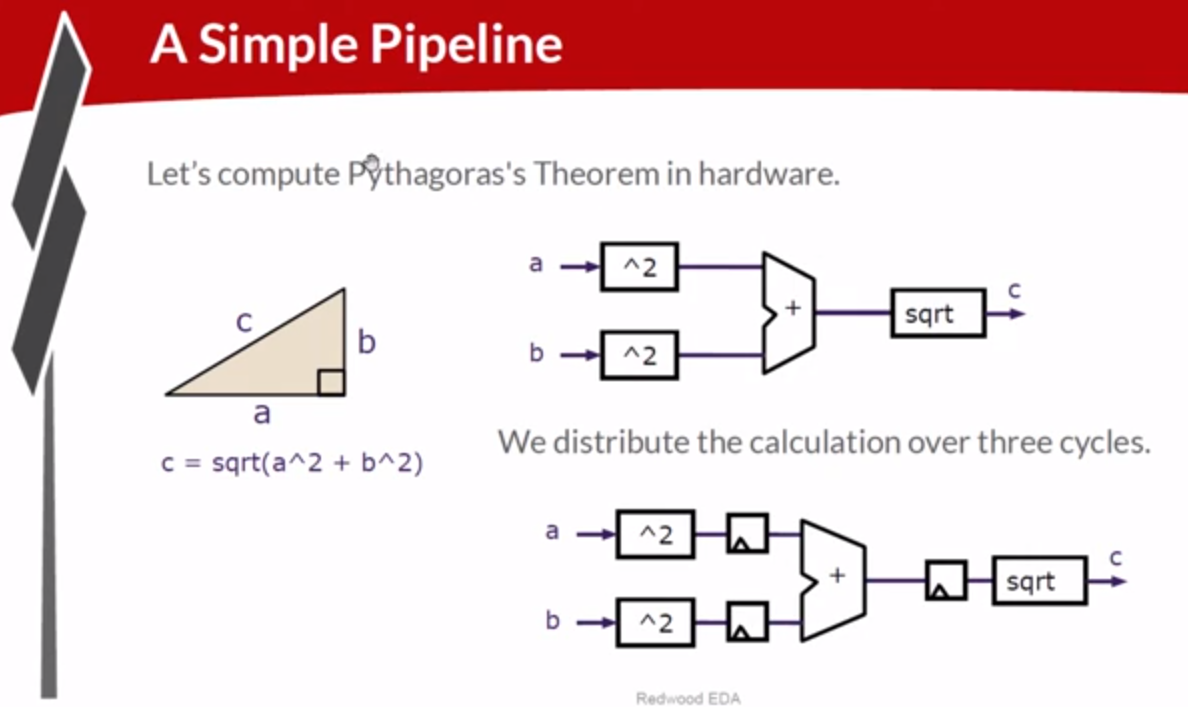

До стартапа Стив работал в Интеле, так что он знает боли разработчика арифметического конвейера на себе лично. При этом Стив излагает все на пальцах. Еще до иллюстрации конвейера в процессоре Стив начинает с более простого конвейера, вычисляющего гипотенузу по теореме Пифагора и показывает, как перемещать вычисления между разными стадиями для максимизации частоты тактового сигнала:

a

Вот еще пятиминутную речь со школе, для записи которой мы выбрали точку в Silicon Valley, которая с одной стороны находится в довольно центральном месте (на северо-запад от нее - Google, Facebook и Стенфорд, на запад - Apple, на северо-восток - Тесла, на юг - Интел), а с другой стороны, находится прямо посреди соленого болота, с его уникальной экосистемой моллюсков и солеустойчивых растений. Болото в Альвизо малоизвестно среди визитеров из России, но популярны для перелетных птиц, летящих из Канады в Мексику и наоборот:

Попробуйте догадаться, зачем здесь эти двери:

Кстати, школа проходила не только в Москве. Руководители кружков и преподаватели из регионов участвовали в школе в Сколково удаленно. Особенно отличился руководитель кружка в Ульяновске Юрий Денисов.

Юрий Денисов пропустил через теоретический курс от Роснано семерых молодых людей, которые соотвественно получили бесплатные платы, на которых Юрий провел упражнения школы. Интересно, что Юрий смог запустить софт для работы с ПЛИС, Intel FPGA Quartus, на российском дистрибутиве Линукса - Astra Linux.

Также была крупная группа участников из Ярославля, участники из Санкт-Петербурга и других мест.

Более подробно программа новой "длинная" Школы Синтеза Цифровых Схем описана на все том же сайте что и раньше.

Комментарии (4)

KeisN13

05.10.2021 18:39+1В этом году у нас прям аншлаг, много желающих, много новых тем. Надеюсь, что будем расти и дальше.

KeisN13

06.10.2021 08:07+1Если можно, я оставлю приглашение на еще одно бесплатное FPGA мероприятие. Слишком уж мало их у нас https://fpga-systems.ru/conference/2021-2/index.html

tirus

Зарегистрировался на субботний курс как преподаватель кружка. Надеюсь, места хватит всем и меня не выгонят )

YuriPanchul Автор

Да, регистрация только началась, так что пока все хорошо. Очень желательно если вы до первого занятия пройдете теоркурс от роснано и установите Quartus на своем ноутбуке. В отличие от школы на ChipEXPO, где 25 компьютеров привез МИРЭА, тут мы хотим чтобы все ставили на своих ноутах, их приносили бы в Сколково, также носили бы с собой платы домой и делали часть проектов и дома, не только в Сколково. Инструкции по установке и предварительному курсу здесь https://habr.com/ru/post/576622/