Вот линк на сообщение о семинаре 13-14 мая возле Лос-Анжелеса, на котором Imagination и Xilinx будет показывать новый продукт под названием MIPSfpga представителям academia — imgtec.com/mipsfpga

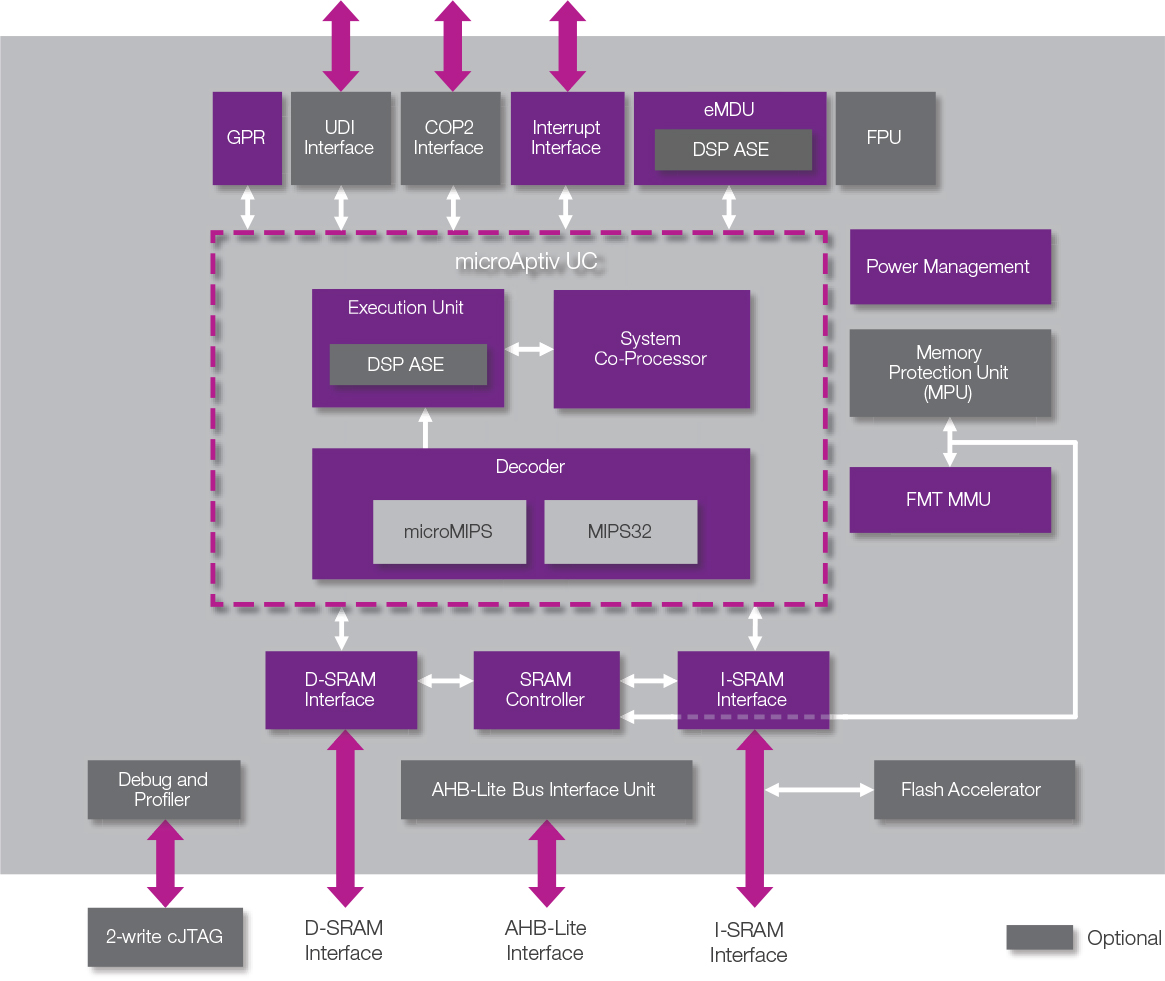

Фактически MIPSfpga — это бесплатная лицензия на базовую конфигурацию экономичного процессорного ядра MIPS microAptiv UP, которое предоставляется в исходных текстах на языке описания аппаратуры Verilog. Это то же самое ядро, которое продается коммерческим клиентам за сотни тысяч долларов. MIPS microAptiv UP — это простой дизайн с пятью стадиями последовательного конвейера (как в учебниках компьютерной архитектуры), но в нем есть кэши и TLB MMU. TLB MMU позволяет даже использовать на нем Линукс.

Описание ядра: www.imgtec.com/mips/aptiv/microaptiv.asp

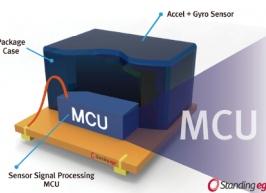

Наиболее широко известным примером использования ядра MIPS microAptiv UP является 32-битный микроконтроллер Microchip PIC32MZ, который начали выпускать в прошлом году. А из самых последних примеров использования: 10 апреля этого года Electronic Engineering Times опубликовала статью про южнокорейский стартап Standing Egg, который лицензировал ядро MIPS M5100 (фактически MIPS microAptiv без кэшей и MMU, но с добавленным расширением для виртуализации) для создания платформы для MEMS сенсоров, с приложениями для Internet of Things:

www.eetimes.com/document.asp?doc_id=1326327

Разработчики микросхем с MIPS microAptiv UP используют стандартную за последние 20 лет методологию электронного дизайна под названием Register Transfer Level (RTL, уровень регистровых передач). Согласно этой методологии, дизайн пишется на языке Verilog, после чего специальная программа (logic synthesis) превращает дизайн в граф из проводов и логических элементов, другая программа (static timing analysis) сообщает разработчику, вписывается ли он в бюджет скорости, а третья программа (place-and-route) раскладывает этот дизайн по площадке микросхемы.

Когда дизайн проходит все этапы: кодирование на верилоге, отладка, верификация, синтез, static timing analysis, floorplanning, place-n-route, parasitics extraction и т.д. – получается файл под названием GDSII, который отправляют на фабрику, где и изготавливаются микросхемы. Самые известные фабрики этого типа принадлежат компании Taiwan Semiconductor Manufacturing Company или TSMC. При этом, ничего не мешает производить микросхемы с ядром MIPS microAptiv UP на российских фабриках Микрон и Ангстрем.

Альтернативой производству микросхемы на фабрике является реализация дизайна на программируемых пользователем матрицах логических элементов (Field Programmable Gate Array — FPGA), что и используется для образовательных целей в новом продукте MIPSfpga.

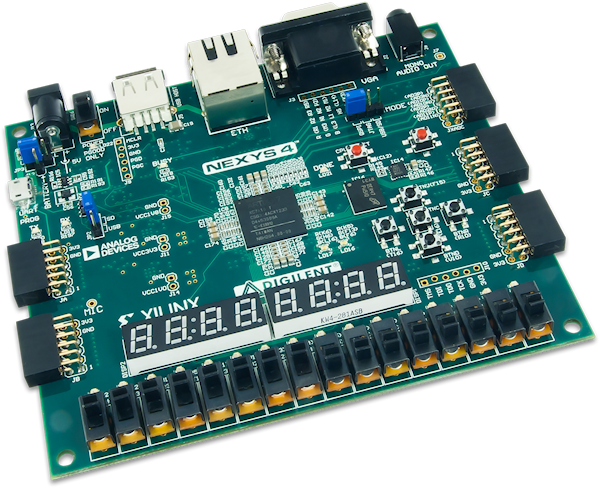

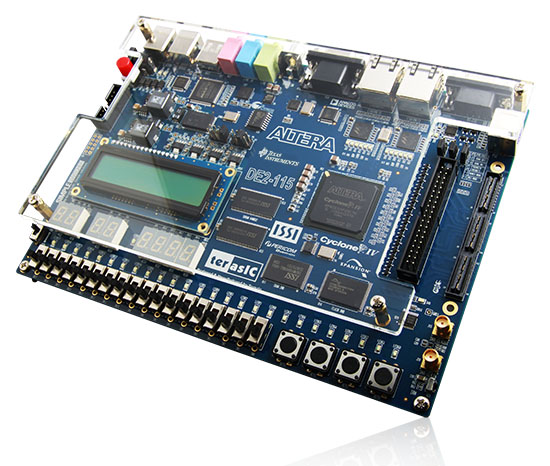

Хотя пакет MIPSfpga и заточен на синтез для FPGA (например в MIPSfpga есть реализация памяти внутри кэшей, используя макро для Xilinx Artix-7 и Altera Cyclone IV), но в основном это те же исходники, которые используются и для синтеза в ASIC. Иными словами, студенты и аспиранты могут экспериментировать с ядром на недорогих FPGA-платах, придумать какое-нибудь интересное решение (скажем многоядерную SoC из малых некогерентных ядер, или комбинацию из ядра MIPS microAptiv UP со специализированным студенческим DSP процессором), не вкладывая при этом денег инвесторов, после чего, когда идея доказана, найти инвесторов, приобрести коммерческую лицензию и сделать микросхему на фабрике — ASIC.

Обращаю внимание, что в случае с MIPSfpga речь идет не об ограниченном образовательном подмножестве MIPS (таких подножеств довольно много из других источников) и не об open-source ядре типа OpenRISC или Leon4, а о коммерчески успешном современном индустриальном ядре, которое за деньги лицензировало несколько десятков компаний.

У конкурирующей компании ARM тоже есть soft core для образовательного экспериментирования на FPGA, но их ядро не в открытом исходном тексте (т.е. студенты не могут подключать провода к внутренним регистрам и модифицировать верилог), у ARM-овского ядра ARM Cortex M0 в конкурирующем продукте нет кэшей, интерфейса к отладчику и TLB MMU. Все это у MIPSfpga есть.

Дополнительные детали:

Сейчас MIPSfpga работает на двух платах Digilent Nexys-4 с Xilinx Artix-7 и Altera DE2-115 с Cyclone IV E. У первой академическая цена $180 / коммерческая $320, у второй академическая $300 / коммерческая $600. Перенести его на другие платы довольно легко (при условии, что вместится) – нужно заменить некоторые макро для памяти и подсоединить top-module к board-specific внешнему verilog wrapper-у. В частности, можно попробовать перенести его на дешевую плату Digilent Basys-3 с Xilinx Artix-7 (академическая $80 / коммерческая $150), а также на платы, которые спроектированы или производятся в России.

В качестве toolchain предлагается Codescape MIPS SDK, который содержит отладчик и GCC toolchain. Связь между отладчиком и платой Nexys-4 делается с помощью EJTAG, BusBlaster probe и OpenOCD. На Altera DE2 115 применяется отладочный интерфейс который стоит прямо на плате, т.е. BusBlaster не нужен. Также прилагается Boot code на ассемблере, который инициализирует кэши и MMU и т.д.

Теперь какое это может иметь отношение к вам:

1. Первый этап апробации MIPSfpga на трех университетах в US и UK успешно завершен. Теперь продукт будет проходить бета-тестирование в бОльшем количестве университетов в США, Европе и Азии. Если вы работаете в университете, и в нем есть достаточная экспертиза в Verilog или VHDL чтобы работать с пакетом, то вы можете принять участие как early adopter и получить преимущество перед другими вузами в его использовании.

2. 13-14 мая в Лос-Анжелесе будет проходить семинар, организованный Imagination Technologies вместе с Xilinx, на котором профессора Harvey Mudd College и application engineers из Imagination будут тренировать профессоров различных вузов использовать MIPSfpga. Если вы или кто-либо из ваших знакомых преподавателей уиверситетов хочет в нем участвовать и может приехать в это время в Лос-Анжелес, просьба связаться либо с менеджером образовательных программ Робертом Оуэном (его координаты в imgtec.com/mipsfpga ), либо со мной (yuri.panchul@imgtec.com).

3. К моменту семинара в Лос-Анжелесе MIPSfpga будет официально объявлен, а после завершения (1) станет общедоступным. Поэтому если вы не имеете возможности принять участие как early adopter, вы тем не менее сможете начать работать с продуктом летом.

Возможность использования индустриальных процессорных ядер на верилоге в образовательных целях и без покупки коммерческой лицензии, позволит большому числу молодых разработчиков в academia заняться прототипированием инноваторских решений в области систем на кристалле и расширений микроархитектуры, с непосредственным путем к коммерциализации — созданию своих микросхем для интернета вещей и других приложений.

Юрий Панчул

Senior Hardware Design Engineer, MIPS processors

Imagination Technologies

Только зарегистрированные пользователи могут участвовать в опросе. Войдите, пожалуйста.

Комментарии (23)

nckma

21.04.2015 13:20+1А сколько занимает места в Cyclone IV?

Возможно ли будет запустить в плате Марсоход2 с Cyclone III?

marsohod.org/index.php/prodmarsohod2

ARM v2a SoC а этой плате запускается…

YuriPanchul Автор

21.04.2015 20:13*** А сколько занимает места в Cyclone IV? ***

На вариант, который в DE2-115 влазит совершенно свободно, оставляя много места для всякой периферии, в вариант который на DE0-Nano — не пробовал.

*** Возможно ли будет запустить в плате Марсоход2 с Cyclone III? ***

Зависит от варианта Cyclone III.

О, давно хотел разобраться, что из себя представляет marsohod. Может быть альтернативным источником плат для российского рынка для образовательных целей. Вы не связаны с marsohod-ом?

*** ARM v2a SoC а этой плате запускается… ***

Это авторизованное ARM-ом ядро, или реализация архитектуры из другого источника?

nckma

21.04.2015 22:13Да, я занимаюсь поддержкой этого проекта marsohod.org и в частности занимался портированием SoC ARM v2a.

ARM v2a — это проект размещенный на opencores, проект, который реализует самое раннее ядро ARM без MMU. Как говорят «is not covered by patents so can be implemented without a license from ARM»

YuriPanchul Автор

21.04.2015 22:27+1Понятно. Вы связаны с каким-нибудь университетом? Если да, то я могу поговорить с менеджером образовательных программ Робертом Оуэном и вы можете попробовать MIPSfpga на вашей плате. Вообще, у меня еще с 2011 года есть необходимость в источнике FPGA плат внутри России, и если вы сможете сделать MIPSfpga на некоем варианте марсоход-а, то я могу договориться с маркетингом обеспечить вам какую-то поддержку (например показывать ваши платы на международных выставках).

nckma

22.04.2015 15:12увы, мы не связаны с университетом и являемся коммерческой организацией. Тем не менее весь наш проект marsohod.org — популяризация технологии ПЛИС и обучение проектированию. Мы сами пишем обучающие статьи по Quartus II и Verilog и готовим проекты (open source) к нашим платам. Было бы интересно, если бы можно было бы запустить MIPS на плате Марсоход2

YuriPanchul Автор

22.04.2015 17:37Я поговорю с Робертом Оуэном, менеджером образовательных программ. Я думаю, что это можно устроить. Если не сейчас (во время early trial) то летом. Я также на днях запущу синтез с FPGA, который на марсоходе и посмотрю, влазит ли он. Если не влазит, то мы обсудим планы, можете ли вы поставить бОльший FPGA. Также на днях выходит учебник на русском языке, который может помочь популярности марсохода как платфоромы для упражнений — см. слайды про учебник — bit.ly/hh2slides

valplo

21.04.2015 15:03-2Хорошо, конечно, но MIPS, даже с конвеерами и прочими штучками, можно накодить и на коленке: архитектура очень простая.

valeriyk

21.04.2015 15:21+3Это да, только он будет в три раза больше по размеру, жрать электроэнергию как крокодил, его CoreMark будет раза в три-четыре меньше, чем у конкурентов, а раз в сто тысяч выполненных команд в нем будут возникать непонятные баги, которые никто никогда не отладит.

YuriPanchul Автор

21.04.2015 20:04+2Вы возможно путаете архитектуру (систему команд и регистры видимые программисту) и микроахитектуру (организацию конвейера, вычислительных блоков). Действительно, архитектура MIPS упрощает создание микроархитектуры для простого случая (короткий последовательный ковейер). Но это не означает, что все процессоры MIPS — архитектурно простые. Существуют высокопроизводительные суперскалярные процессоры MIPS с внеочередным выполнением команд, разнообразными расширениями (векторное расширение, DSP-расширение, расширение для аппаратно-поддерживаемой виртуализации, расширение для аппаратно-поддерживаемой многопоточности), многоядерностью с когерентными кэшами и т.д.

MIPSfpga / MIPS microAptiv UP — это ядро экономичной линейки. А вот ядра средней/эффективной и высокопроизводительной линеек гораздо сложнее. MIPS P5600 (high-end, OoO, 32 bit), MIPS I6400 (mid-range, 64-bit):

MIPS I6400 (mid-range, superscalar, MT, multicore, 64 bit):

ComodoHacker

22.04.2015 08:07Интересно, не попадает ли распространение этой технологии в России под санкции.

YuriPanchul Автор

22.04.2015 17:28+1В текущий момент — нет. У России уже есть как early adopters MIPSfpga, так и лицензиаты коммерческих ядер MIPS, с которыми MIPSfpga имеет общий код.

SerJook

Надеюсь дожить до того времени, когда можно будет скачать процессор с github и распечатать его на 3d принтере :)

amartology

Оптимисты говорят, что уже лет через 10-15. Прямо сейчас можно скачать процессор с Opencores и некоторых других мест и залить в FPGA. Это уже сильно лучше, чем ничего)

beeruser

Качайте =)

github.com/openrisc/mor1kx

Это IP-ядро, но на opencores, как уже было сказано, есть вполне готовые девайсы.

Напечатать пока не получится. Если у вас нет лишнего миллиона зелёных, конечно =)

amartology

Миллион зеленых — совершенно недостаточно для того, чтобы построить себе собственный заводик, и слишком много для того, чтобы отдать заказ на производство на уже имеющуюся фабрику.

demitsuri

Подскажите пожалуйста, где можно посмотреть расценки (хотя бы в первом приближении) на размещение заказа на производстве.

amartology

Обычно после подписания NDA фабрики дают расценки, исходя из нужного вам размера партии, техпроцесса и т.д. и т.п.

Если вам нужен тестовый запуск в несколько десятков чипов на поиграться или проверить работоспособность, то минимальные цены начинаются буквально от единиц тысяч евро, а реалистичные (относительно большой чип и относительно современные проектные нормы) — от нескольких десятков тысяч евро.

Мелкосерийное производство начинается от сумм порядка десяти миллионов рублей за 5-10 пластин.

YuriPanchul Автор

amartology говорит про всякие экономичные варианты, но мейнстримные ASIC сейчас — это действительно миллион долларов сразу + отчисления от продаж. Не считая оплату проектирования и сервисов при фабриках.

Далее, насколько я помню (давно не освежал вопрос в голове), фабрика на 20-28 nm стоит 5-6 миллиардов долларов, а вот на 65-90-130 nm (этого достаточно для дешевых микроконтроллеров) можно купить за 500 миллионов долларов.

beeruser

О каком заводике идёт речь? Один только набор масок для 28нм техпроцесса стоит пару миллионов.

Вообще, как можно создать и произвести свой CPU на помощью шаттл-ране, написано в главе Silicon on a Shoestring Budget:

www.adapteva.com/wp-content/uploads/2011/06/adapteva_mpr.pdf

Понятно, что малобюджетно здесь — это сотни тысяч $.

googol

Вот похоже еще одна попытка создать открытое железо riscv.org

YuriPanchul Автор

RISC-V — это хорошая попытка от уважаемых людей, но пока за ней нет 1) экосистемы 2) поддержки учебниками 3) использования коммерческими компаниями.

А вот за MIPSfpga есть — только в прошлом году в мире было произведено более 700 миллионов устройств с ядрами MIPS, по учебниками Patterson & Hennessy и Harris & Harris учится немерянное количество студентов во всем мире (эти учебники используют MIPS для объяснения микроархитектуры), а в экосистему входит дюжина RTOS-ов, куча компиляторов, Linux и т.д.

googol

Спасибо за ответ. Начинаю разбираться в области digital design и подобная информация мне очень кстати.