SystemC это библиотека для C++ позволяющая моделировать всевозможные аппаратные системы на различном уровне абстракции. Поддерживается как традиционное дискретно-событийное моделирование, привычное программистам на Verilog и VHDL, так и аналоговое моделирование в духе SPICE/Verilog AMS. В комплект также входит библиотека и методология для виртуального прототипирования, библиотеки для написания тестовых окружений и верификации с использованием рандомизированных тестов.

В этой я расскажу о синтезируемом подмножестве SystemC, сравнивая его с синтезируемым SystemVerilog. Сам я пользуюсь SystemC уже где-то 3 года, а до этого несколько лет писал на Verilog/SystemVerilog. Попытаюсь охватить предмет с разных сторон: начиная с философских рассуждений о причинах возникновения SystemC, краткого обзора экосистемы и инструментария и заканчивая практическими примерами синтаксиса и семантики.

Подразумевается, что читатели знакомы с Verilog и C++.

Размышления о причинах возникновения SystemC

За свою длинную историю индустрия разработки электроники нашла применение множеству языков программирования и породила огромное количество DSLей (Domain-specific languages). Если представить себе гипотетического full-stack аппаратчика (по аналогии с full-stack веб-программистом), который в одиночку может спроектировать современную микросхему, от алгоритма до реализации в кремнии, то ему помимо знания матчасти (арихитектура эвм, электроника, алгоритмы из прикладной области и др.) придется владеть целой кучей разнообразных языков: Matlab для разработки алгоритмов, Verilog или VHDL для описания RTL модели, SystemVerilog/E/Vera для написания тестов и тестового окружения, TCL для написания скриптов управляющих САПР пакетами, SPICE/Verilog-AMS для моделирования аналоговых подсистем, SKILL или Python для генерации топологий, Си/Asm для написания всевозможного firmware. При желании список можно продолжать и дальше.

Конечно в природе такие универсальные инженеры практически не встречаются и проект делают несколько команд, каждая из которых хорошо разбирается в своей достаточно узкой области. Однако, очень часто приходится совмещать работу на нескольких этапах разработки. К примеру, легко представить, что человек написавший RTL модель IP блока напишет для него и набор тестов для верификации. Это в свою очередь создает запрос на создание универсальных языков, пригодных для решения смежных задач.

В мире цифровой микроэлектроники таким универсальным языком стал SystemVerilog, который помимо классического Verilog (с небольшими расширениями), содержит в себе объектно-ориентированный язык для написания тестовых окружений, язык утверждений (assertions) для формальной верификации а так же специальные конструкции для рандомизации и анализа тестового покрытия. В каком-то смысле SystemVerilog это не совсем новый язык, а скорее конгломерат языков, склеенный общим синтаксисом.

Но что если мы хотим большего? Язык на котором помимо всего вышеперечисленного можно разрабатывать алгоритмы, писать встроенное ПО, создавать виртуальные прототипы. Не пора ли добавить к SystemVerilog еще пару DSL?

We need to go deeper

Существует однако и другой подход: вместо придумывания всё новых DSLей, можно создавать программные библиотеки, предназначенные для решения специального класса задач. Таким путём пошли создатели SystemC — библиотеки для C++, позволяющей моделировать цифровую аппаратуру. Хотя в каком-то смысле SystemC является DLS’ем, созданным средствами метапрограммирования на C++, сам C++ при этом не расширяется новыми синтаксическими конструкциями. Метапрограммирование широко применяется и в других C++ библиотеках.

У такого подхода существуют свои плюсы и минусы. Основной плюс C++ в его универсальности: сегодня ты можешь писать хардвер на SystemC, а завтра GUI на Qt. (Хотя придется потратить достаточно много времени на изучение каждой из этих библиотек). Основной минус в синтаксисе: код на чистом DSL будет намного красивей, особенно если нужно сделать что-то простое (для простых модулей код на Verilog будет компактней и проще, чем аналогичный код на SystemC).

Помимо недостаточной универсальности у Verilog есть и другая проблема: он очень низкоуровневый. В каком-то смысле синтезируемый Verilog это макроассемблер для аппаратуры ( если ассемблер для аппаратуры это логическая схема). Новые конструкции, появившиеся в синтезируемом SystemVerilog не решают эту проблему низкоуровневости. Очень часто приходится прибегать к использованию всевозможных генераторов кода на Verilog, например скриптов на Python. Среди моих коллег популярной была идея вставлять код на Perl внутрь модулей на Verilog. Полученный таким путём гибрид назвали перлилогом. Думаю многие знакомы с Verilog-mode для emacs, который умеет генерировать Verilog код для соединения модулей.

По сравнению с SystemVerilog, синтезируемый SystemC позволяет гораздо больше. Да, вы можете писать синтезируемый код с классами! При решении сложных задач средства абстракции C++ позволяют писать более элегантный (простой и компактный) код.

Экосистема SystemC

Рассмотрим основные программные инструменты, с которыми приходится иметь дело разработчикам на SystemVerilog и SystemC.

Среда разработки

SystemVerilog:

Большинство программистов на Verilog для написания кода используют текстовый редактор: поддержка Verilog есть в Vim, Emacs, Sublime Text, Notepad++, Slickedit и других популярных редакторах. Прикладным программистам написание кода в тестовом редакторе может показаться архаизмом: большинство из них используют умные IDE с авто-подсказками, автоматизированными рефакторингами, удобной навигацией. Однако в мире синтезируемого Verilog огромной пользы от использования IDE нет: это объясняется тем что вся функциональность разбивается на совершенно независимые друг от друга модули. Весь контекст с которым работает разработчик отдельного модуля обычно умещается в один файл. Совсем другое дело с написанием тестбенчей на SystemVerilog, здесь вполне может пригодится IDE, такая как DVT.

SystemC:

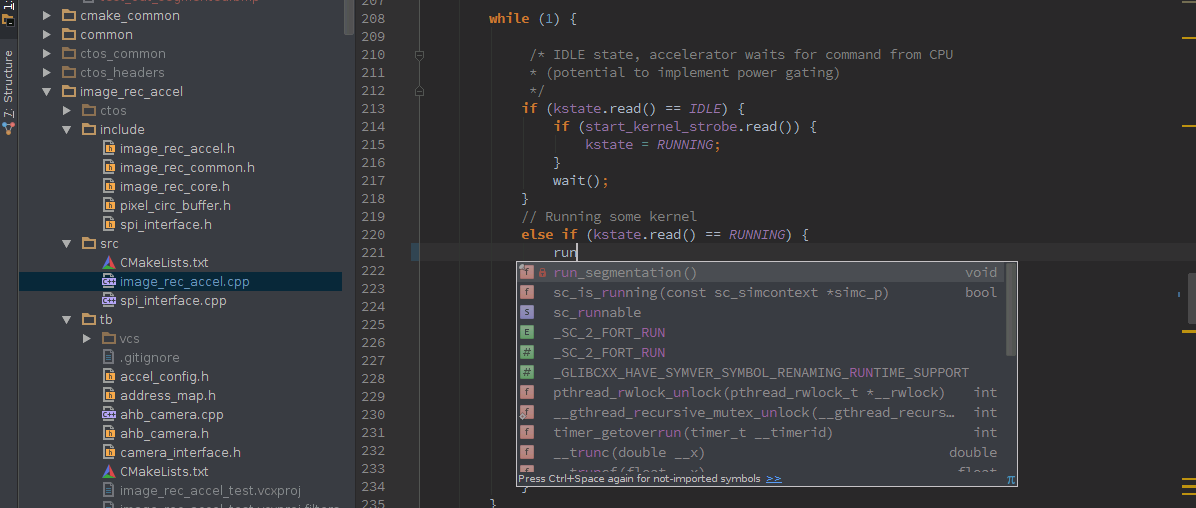

При написании синтезируемого C++/SystemC простым текстовым редактором уже не обойтись. К счастью, существует множество C++ IDE (в том числе и бесплатных), которые в состоянии справиться с кодом на SystemC. Например, можно использовать привычную многим MS Visual Studio. Я долгое время пользовался Eclipse CDT и Netbeans для написания кода на C++/SystemC. Последнее время пробую Clion от Jetbrains.

Написание SystemC кода в Clion

Написание SystemC кода в ClionСимуляция и отладка

SystemVerilog:

Для симуляции и отладки кода на Verilog используется HDL симулятор. Существуют как бесплатные (IcarusVerilog), так и платные симуляторы. По сравнению с бесплатным симулятором коммерческие решения обеспечивают большую скорость симуляции и предоставляют удобные графические среды для отладки.

SystemC:

C SystemC ситуация в целом похожа: можно использовать референсный симулятор и GDB для отладки, но когда нужно отлаживать какой-то более-менее сложный сигнальный протокол приходится пользоваться одним из коммерческих симуляторов.

Отладка SystemC в симуляторе

Синтез

SystemVerilog:

Синтез SystemVerilog поддерживается основными FPGA и ASIC вендорами. В том числе существуют и бесплатные версии пакетов для FPGA, чем пользуются многие российские вузы для обучения студентов азам цифровой схемотехники.

SystemC:

Для синтеза SystemC используются специальные пакеты высокоуровневого синтеза (англ. High-level Synthesis, HLS). Что в них такого высокоуровневого спросите вы? Всё дело в том, что HLS пакеты, помимо традиционного RTL кода написанного на SystemC умеют синтезировать и чисто поведенческий (“untimed”) код, автоматически вставляя регистры, там где это необходимо.

Большинство HLS пакетов могут синтезировать и чистый C/C++, SystemC используется только в тех случаях, когда нужно добавить модульность и сигнальные интерфейсы. В каком-то смысле синтез с C/C++ является технологией для разработки акселераторов, конкурирующей с синтезом с OpenCL. Хотя при использовании SystemC мы не ограничены только разработкой акселераторов, а можем разрабатывать совершенно любые цифровые схемы. Чуть позже я расскажу про HLS немного подробнее.

На выходе HLS пакета мы обычно имеем привычные RTL модули на Verilog, которые затем синтезируются с помощью Verilog синтезатора.

К сожалению, все существующие HLS с поддержкой SystemC исключительно коммерческие и стоят много денег. Бесплатных версий нет, хотя университетам всё продают с большой скидкой.

Лучшими средствами синтеза SystemC на рынке являются Stratus от Cadence и Catapult C от Calypto/Mentor Graphics.

Другие EDA пакеты для SystemC

Помимо написания синтезируемого кода, SystemC достаточно широко используется для виртуального прототипирования. Создание виртуальных прототипов (эмуляторов) на C++/SystemC используется в пакетах Synopsys Virtualizer, Mentor Graphics Vista, Cadence Virtual System Platform. При этом нельзя сказать что SystemC на этом рынке является доминирующим решением: существуют и продукты SystemC не использующие, например WindRiver Simics.

На этом обзорная часть статьи завершается. Пришло время погрузиться в код.

Погружение в код

Синтезируемый SystemC. Базовые строительные блоки

Не буду здесь полностью описывать весь стандарт SystemC, пройдусь только по самому необходимому. Все примеры будут построены на сравнении SystemVerilog и SystemC.

Типы данных

SystemVerilog:

Основным типом используемым в синтезируемом SystemVerilog является тип logic. Переменная типа logic может принимать 4 значения: 1, 0, x, z. x означает неизвестное значение. z означает высокоимпедансное состояние. Можно создавать вектора типа logic различной длины, например:

logic [1:0] data; // 2-х битный вектор

initial begin

data = 7;

$display(data);

end

SystemC:

В SystemC тоже есть типы с 4-мя состояниями. Однако на практике в основном используются типы с 2-мя состояниями 1 и 0. Основная причина — типы с 2-мя состояниями симулируются быстрее.

После синтеза все типы с 2-мя состояниями превращаются в logic. Это может привести к различиям в результатах симуляции SystemC (до синтеза) и Verilog (после синтеза). В SystemC не сброшенный регистр будет иметь значение 0, в Verilog — x. К счастью, синтезатор выдает предупреждение каждый раз когда видит регистр без сброса, поэтому на практике после чтения лога синтезатора проблем с расхождением результатов симуляции можно избежать.

Очень часто в коде на SystemC используются встроенные типы C++, такие как int или char. Если же нам требуется число с заданным количеством бит, можно использовать тип sc_uint:

sc_uint<2> data; // 2-х битная переменная

data = 7;

cout << data;

Как реализован sc_uint? Это просто шаблонный класс в котором перегружены все основные операторы.

Модули

Рассмотрим пример пустого модуля на SystemVerilog и SystemC

SystemVerilog:

module top (

input clk, rstn,

input [7:0] din,

output logic [7:0] dout

)

// тело модуля

endmodule

SystemC:

struct top: public sc_module {

sc_in<bool> clk, rstn;

sc_in<sc_uint<8> > din;

sc_out<sc_uint<8> > dout;

top(const char* name) : sc_module(name) , clk("clk") , rstn("rstn") , din("din"), dout("dout")

{ }

};

struct top: public sc_module {

sc_in<bool> clk, rstn;

sc_in<sc_uint<8> > din;

sc_out<sc_uint<8> > dout;

top(const char* name) : sc_module(name) , clk("clk") , rstn("rstn") , din("din"), dout("dout")

Error: (E109) complete binding failed: port not bound: port 'top.dout' (sc_out)

Ошибка: порт dout модуля top никуда не подключен.

( Возможно, когда в C++ появится нормальная поддержка интроспекции объекты в SystemC смогут узнавать свои имена самостоятельно )

Для удобства создания модулей в SystemC определено несколько макросов. С их использованием аналогичный модуль выглядит следующим образом:

SC_MODULE(top) {

sc_in<bool> clk, rstn;

sc_in<sc_uint<8> > din;

sc_out<sc_uint<8> > dout;

SC_CTOR(top) , clk("clk") , rstn("rstn") , din("din"), dout("dout") {}

};

Переменные и присваивания

SystemVerilog:

Можно утверждать что все переменные в синтезируемом SystemVerilog- статические: они существуют с начала и до конца симуляции. И имеют глобальную область видимости (хотя доступ к сигналам “через крышу” по иерархическому имени не допускается в синтезируемом коде). Еще одной особенностью SystemVerilog является наличие нескольких операторов присваивания: блокирующего и неблокирующего присваивания в процедурных блоках, а так же непрерывного присваивания.

Блокирующее присваивание происходит либо сразу, либо блокирует исполнение текущего процесса до момента когда присваивание совершится.

Пример:

logic a;

initial begin

a = #42 1;

$display($time);

end

т.к. вызов функции $display произойдет лишь в момент времени 42, когда присваивание произойдет.

Неблокирующее присваивание откладывает присваивание на какой-то момент симуляционного времени в будущем и не блокирует исполнение процесса. Если время не указано явно, присваивание происходит на следующем дельта-цикле.

initial begin

a <= #42 1;

$display($time);

end

SystemC:

Переменные в C++ ничего не знают про симуляционное ядро SystemC и поэтому ведут себя привычным для C++ программиста образом. Для того чтобы промоделировать неблокирующее присваивание в SystemC используется специальный тип sc_signal, переменные этого типа далее называются сигналами:

sc_signal< sc_uint<2> > data; // сигнал типа sc_uint<2>

Синтезируемый SystemC требует, чтобы взаимодействие между несколькими процессами происходило через сигналы. Аналогично, в Verilog хорошим стилем является использование исключительно неблокирующих присваиваний в always_ff процедурных блоках. В противном случае рискуем получить неопределенное поведение (состояние гонки), когда результат симуляции будет зависеть от порядка вызова процессов в одном дельта цикле.

Аналога блокирующего присваивания в SystemC нет.

Процессы (Процедурные блоки)

SystemVerilog :

Синтезируемый SystemVerilog поддерживает два основных типа процедурных блоков always_comb и always_ff. Помимо них есть еще always_latch, но использовать регистры-защелки на практике приходится довольно редко.

always_comb используется для описания комбинаторной логики

always_comb

begin

a = b + c;

end

always@(b or c)

begin

a = b + c;

end

assign a = b + c;

always_ff @(posedge clk or negedge arst_n) begin

if(~arst_n) begin

a <= 0;

end

else begin

a <= a + 1;

end

end

SystemC:

Процессы в SystemC создаются в конструкторе модуля. Тело процессов описывается в функциях-членах модуля. Тип процесса похожего на always блок из Verilog в SystemC называется SC_METHOD.Рассмотрим примеры процессов, аналогичные приведенным ранее процедурным блокам на SystemVerilog:

Комбинаторная логика:

SC_CTOR(top) {

SC_METHOD(comb_method); // макрос для создания процесса типа SC_METHOD

sensitive << b << c; // список чуствительности (аналог @(a or b) )

}

void comb_method() { a = b + c; } // тело процесса описывается в функции-члене

SC_CTOR(top) {

SC_METHOD(seq_method); // макрос для создания процесса типа SC_METHOD

sensitive << clk.pos() << arst_n.neg(); // список чуствительности ( @(posedge clk or negedge arst_n) )

}

void seq_method() { // тело процесса описывается в функции-члене

if (!arst_n)

a = 0;

else

a = a + 1;

}

Параметризация

Модули на SystemVerilog можно параметризовать. К примеру, можно написать параметризуемое FIFO, ширина и глубина которого будут указываться при создании экземпляра.

В SystemC для создания параметризуемых модулей используются шаблонные классы. С использованием шаблонов и наследования возможности по параметризации в SystemC становятся почти безграничными.

Промежуточные итоги

SystemC позволяет описывать аппаратуру на уровне RTL в стиле очень близком к простому Verilog. Код на Verilog будет изящней и компактней, но в целом всю функциональность можно повторить. Рассмотрим полноценный пример: реализуем на Verilog и SystemC сдвиговый регистр с последовательным входом и выходом (serial-in/serial-out) и асинхронным сбросом:

Код на Verilog:

module shifreg (

input clk, sin, reset,

output sout

);

reg [7:0] tmp;

always @(posedge clk or posedge reset) begin

if (reset)

tmp <= 0;

else

tmp <= {tmp[6:0], sin};

end

assign sout = tmp[7];

endmodule

// Для сигналов и портов используется инициализация в стиле C++11

SC_MODULE(shift_reg) {

sc_in<bool> clk{"clk"}, sin{"sin"}, reset{"reset"};

sc_out<bool> sout{"sout"};

SC_CTOR(shift_reg) {

SC_METHOD(shift_method);

sensitive << clk.pos() << reset.pos();

// т.к. непрерывного присваивания нет, приходится создавать процесс

SC_METHOD(sout_method);

sensitive << tmp;

}

private:

sc_signal <sc_uint<8> > tmp {"tmp"};

void shift_method() {

// для чтения и записи сигналов используются методы read и write

// метод write - аналог неблокирующего присваивания в verilog

if ( reset.read() ) {

tmp.write(0);

} else {

// перегруженный оператор "," (запятая) используется для конкатенации

tmp.write((tmp.read().range(6,0) , sin.read()));

}

}

void sout_method() {

sout = tmp.read()[7];

}

};

Хороший SystemC. Возможности синтезируемого SystemC, которых нет в SystemVerilog

Пользовательские типы данных

Синтезируемый SystemC полностью поддерживает объектно-ориентированное программирование на C++. Это позволяет создавать удобные типы данных для работы в своей предметной области. Например, если вы занимаетесь 3D графикой, то вам постоянно приходится иметь дело с 3-х мерными вещественными векторами. Для их аппаратной реализации потребуется решить несколько задач.

Во первых, операции с плавающей точкой как правило не поддерживаются синтезатором. Поэтому вам придется реализовать их самостоятельно, или использовать стороннюю библиотеку, например DesignWare floating point. И в том и в другом случае вы можете создать удобный класс для работы с плавающей точкой:

class my_float {

public:

my_float operator+( const my_float &rval) const;

my_float operator-( const my_float &rval ) const;

my_float operator*( const my_float &rval ) const;

// и другие операции ...

private:

sc_uint<32> raw_data; // внутри себя float это простой 32-битный вектор

}

class vector_3d {

public:

vector_3d operator*( const vector_3d &rval ) const; // vector product

vector_3d dot_product (const vector_3d &other) const; // dot product

// и другие операции ...

private:

my_float x, y, z;

};

vector_3d a,b,c;

c = a + b;

package Vector3DPkg;

typedef struct {

logic [31:0] x, y, x;

} vector_3d;

function vector_3d add(vector_3d a, b);

add.x = float_add (a.x, b.x);

add.y = float_add (a.y, b.y);

//...

endfunction

function vector_3dmul(vector_3d a, b);

//....

endpackage : Vector3DPkg

SC_CTHREADS (clocked threads). Процессы с неявным состоянием

Синтезируемые процессы в Verilog не могут использовать выражения для управления временем и ожидания событий. Т.е. запущенный процесс должен исполниться до конца и только потом передать управление другому процессу. К примеру, данный процесс не синтезируется:

always @(posedge clk)

begin

out <= 1;

@(posedge clk); // ожидание события не синтезируется

out <= 2;

@(posedge clk);

out <= 42;

end

logic [1:0] state;

always @(posedge clk or negedge reset_n)

begin

if ( ~ reset_n)

state <= 0;

out <= 1;

else

case (state)

0: begin

state <= 1;

out <= 1;

end

1: begin

state <= 2;

out <= 2;

end

2: begin

state <= 0;

out <= 42;

end

end

SC_CTOR ( top ) {

// процесс создается в конструкторе

// clk.pos() означает тактирование по переднему фронту сигнала clk

SC_CTHREAD(test_cthread, clk.pos() );

async_reset_signal_is(reset_n, 0); // асинхронный сброс по уровню 0

}

void test_cthread () {

// код до первого вызова wait() называется reset-секцией, выполняется при запуске процесса или при активном сигнале сброса.

out <= 1;

wait();

// в отличии от SC_METHOD, SC_CTHREAD не должен завершаться никогда

// поэтому в теле процесса всегда есть бесконечный цикл

while (1) {

out.write(1);

wait (); // ожидание переднего фронта на clk

out.write(2);

wait (); // ожидание переднего фронта на clk

out.write(42);

}

}

Истинная мощь SC_CTHREAD процессов заключается в возможности вызова функций, которые могут заблокировать процесс, т.е. вызывать функцию wait(). Такая функция может исполняться несколько тактов! Аналогом из мира Verilog являются task’и, они однако не синтезируются и используются только в тестах.

Например:

while (1) {

res = calculate_something(); // несколько тактов занимаемся какими-то вычислениями

spi_send(res); // отправляем результат по SPI, тоже за несколько тактов

}

Для примера рассмотрим процесс, который читает данные из FIFO, обрабатывает их, после чего отправляет результат в память по системной шине (например, AMBA AXI). Пускай данными будет 3-х мерный вектор рассмотренный раннее, а обработка будет заключаться в нормализации этого вектора. С использованием SC_CTHREAD и готовых классов для работы с FIFO и AXI написать такой процесс очень просто:

fifo data_fifo; // экземпляр FIFO

amba_axi bus_master; // реализация мастера шины AMBA AXI

void computational_thread() {

wait();

while (1) {

vector_3d vec = data_fifo.pop(); // читаем данные из FIFO

vec.normalize(); // обрабатываем данные

bus_master.write( 0xDEADBEEF, vec); // отправляем результат в память по адресу 0xDEADBEEF

}

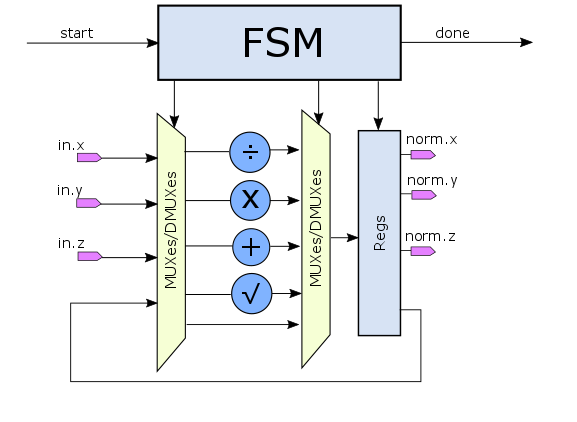

У опытного разработчика наверняка возник вопрос, как мы делаем нормализацию вектора за такт? На какой частоте работает наш модуль? Действительно, цепочка из умножения, двух сложений, квадратного корня и деления это слишком много для одной комбинационной схемы. Тем более что речь идет об операциях с плавающей точкой. В случае синхронной схемотехники эта комбинационная цепочка наверняка станет узким местом, ограничивающем максимальную тактовую частоту работы всей схемы.

В зависимости от требований к пропускной способности нашего нормализатора проблема может быть решена несколькими способами:

- Если мы никуда не торопимся, то можно сэкономить на ресурсах и реализовать нормализацию в виде FSMD с одним умножителем, сумматором, делителем и модулем извлечения квадратного корня. В этом случае мы потратим 6 тактов на вычисление длины вектора и еще 3 такта для вычисления значения каждого из элементов результата, в сумме — 9 тактов на один вектор.

- Если мы сильно торопимся, а ресурсов не жалко, оригинальную комбинационную схему можно превратить в конвейер. В этом случае в пике (когда в FIFO постоянно есть данные) мы получим тот же 1 такт на вектор, но уже на большей тактовой частоте.

- Так же возможны любые промежуточные между первым и вторым варианты. К примеру, если логика дорогая а регистры дешевые, то в первом рассмотренном варианте микроархитектуры можно начинать обработку следующего вектора не дожидаясь завершения выполнения предыдущего, по мере освобождения ресурсов. После вычисления трех квадратов элементов первого вектора, умножитель освобождается и можно начинать обработку следующего вектора. Такая реализация называется конвейером с интервалом инициализации в 3 такта. Т.е. каждые три такта конвейер будет забирать из FIFO новый вектор.

К сожалению, реализация любого из предложенных решений вручную потребует много времени и значительно усложнит наш 3-х строчный исходник. Например, в случае конвейерной реализации придется создать по процессу на каждую из стадий конвейера. К счастью, при использовании SystemC нам ничего не нужно делать руками — ведь можно просто воспользоваться высокоуровневым синтезом!

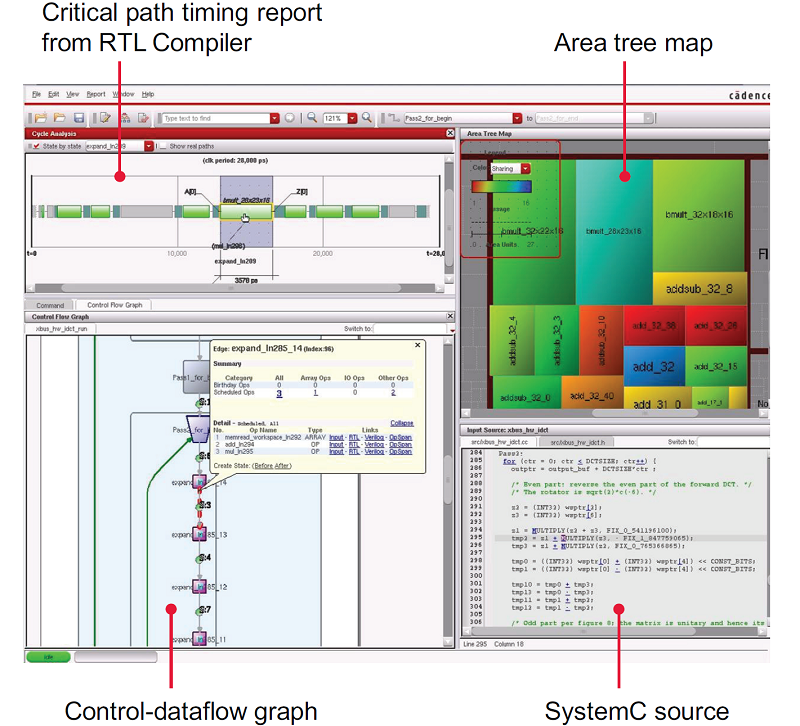

Высокоуровневый синтез.

Высокоуровневый синтез это процесс трансформации алгоритмического кода написанного на высокоуровневом языке программирования в цифровую аппаратуру его реализующую. На вход HLS пакета подаются:

- Исходный код. Иногда его называют untimed code, т.к. он не содержит конструкций для остановки процесса, таких как функция wait

- Timing constraints. Временные ограничения. Задают список тактовых сигналов и их период, а так же задержки на внешних портах

- Спецификация микроархитектуры. В качестве микроархитектуры мы можем выбрать любой из рассмотренных ранее вариантов

void vector_3d::normalize() {

my_float magnitude = sqrt( x*x + y*y + z*z );

x = x / magnitude;

y = y / magnitude;

z = z / magnitude;

}

Анализ проекта в HLS пакете от Cadence

Опытные пользователи средств логического синтеза знают что некоторые из них (например Deisgn Compiler) обладают похожей функцией, которая называется ретайминг (retiming). В сравнении с ретаймингом HLS обладает несколькими преимуществами:

- Не требуется руками специфицировать регистры, логику остановки конвейера.

- HLS позволяет переключаться между несколькими микроархитектурами не меняя исходный код.

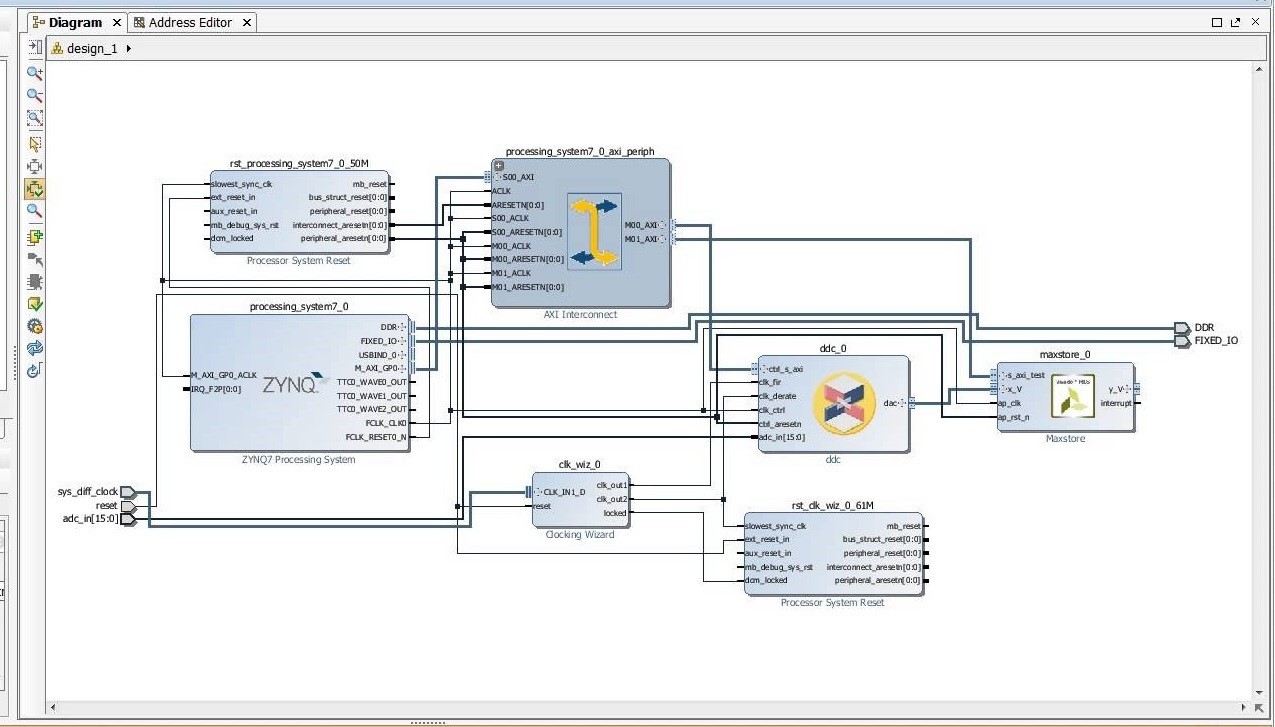

uint32_t write_address; // 32-битный адрес

vector_3d memory[1024]; // память 1024x96 , каждый вектор - 96 бит

....

while (1) {

vector_3d vec = data_fifo.pop(); // читаем данные из FIFO

vec.normalize(); // обрабатываем данные

memory [write_address] = vec; // записываем результат в память

write_address ++;

}

Соединение HLS блока с ARM процессором через AMBA AXI в Vivado IP Integrator

Заключение

В качестве заключения хочу попробовать ответить на вопрос который часто задают RTL разработчики увидев новый тул: А что с качеством результата? Как будут отличаться тайминги, площадь, энергопотребление схем описанных на SystemC и синтезированных с помощью HLS в сравнении с RTL описанным на SystemVerilog?

На самом деле никак. Всё в ваших руках: SystemC и HLS не лишают вас возможности затюнить всё с точностью до гейта там где это требуется. И в то же время HLS не освобождает вас от необходимости понимать основы цифровой схемотехники. HLS это не магическое средство, превращающее C++ программиста в аппаратчика, это средство позволяющее автоматизировать рутинную работу, облегчающее процесс написания и поддержки синтезируемого кода.

В этой статье я никак не коснулся вопроса верификации. Верификация всегда занимает большую часть времени разработки и SystemC есть что предложить на этом поприще. Хорошо написанный SystemC стимулируется быстрее чем RTL, т.к. часть кода написана в “untimed стиле”, а сигнальные интерфейсы можно заменить на вызовы функций (Transaction-level modeling). Библиотека SCV (SystemC Verification Library) позволяет рандомизировать тестовые вектора, так же на подходе SystemC версия UVM. А т.к. SystemC это C++, то части исходного кода можно переиспользовать между синтезируемым кодом, референсной моделью, виртуальным прототипом и драйвером операционной системы. Но рассказ обо всём этом достоин отдельной статьи.

Комментарии (28)

nerudo

28.12.2015 11:06+1Ряд мыслей по поводу сравнения:

- Всю семантику процессов/списков чувствительности/блокирующих-неблокирующих пришлось перенести, переписав другими словами

- Пользовательские типы и операторы — это все есть в VHDL с самого рождения. То, что в веририлоге не осилили — печально

- Последовательные автоматы. Чисто теоретически ничто (и никто) не запрещает синтезировать конструкцию вида

always begin @(posedge clk) out <= 1; @(posedge clk); // ожидание события не синтезируется out <= 2; @(posedge clk); out <= 42; end

Жаль, что нынешние синтезаторы не умеют (а может какие-нибудь продвинутые умеют?), иногда это было бы удобно. Сами же возможности языков что verilog, что VHDL подобную возможность не ограничивают

Daffodil

28.12.2015 17:28+1- Да, весь этот инструментарий используется в SystemC для написания различных signal-level интерфейсов.

- К сожалению я видел своими глазами, как людей заставляли переписывать VHDL в SystemVerilog, чтобы соответсвовать корпоративным стандартам. VHDL сложнее чем Verilog, поэтому Verilog программисты плодятся быстрее и постепенно убивают VHDL. А разработчиков на SystemC можно получать путём тренировки хороших C++ программистов.

- Да, сами языки не ограничивают возможость высокоуровневого синтеза с них. Один из первых HLS — behavioral compiler синтезировал Verilog и VHDL. Но не взлетел. Синтез с C/C++ завоевал себе небольшой рынок прежде всего потому, что алгоритмические модели часто пишутся на C/C++. Поэтому можно к примеру какой-нибудь VP9 кодек переписать из софта в хард не меняя языка разработки. Я читал что Google ровно так и делал, используя Catapult C для синтеза

Pugnator

28.12.2015 11:36А подскажите, какую литературу порекомендуете по SysC. в сети лишь примитивное описание, вроде «создадим вентиль или-не»

Daffodil

28.12.2015 17:34Лучше всего начать с изучения C++ и основ Verilog (Verilog всё равно вам пригодится). А потом просто заказать тренинг от SystemC вендора. После тренинга можно пользоваться стандартом SystemC как референсом.

Pugnator

28.12.2015 20:52Ну, мне как любителю пишущему на плюсах это немного затратно, кмк. Мне систС нужен как конструктор для симуляторов, с удобным интерфейсом на TLE2.0. Через скрипты и прочее. Для того, чтобы не изобретать свои примитивы. А использовать удобную библиотеку.

Daffodil

28.12.2015 21:56+1Понятно, т.е. вас прежде всего интересует вопрос создания виртуальных прототипов как хобби. В таком случае SystemC вам возможно не нужен, можете всё писать на чистом C++.

SystemC+TLM2.0 превращается в конструктор симуляторов только если у вас есть доступ к готовым блокам. А бесплатно эти блоки увы никто не раздает.

Если в ваших проектах вы дойдете до уровня когда вам потребуется моделировать систему с несколькими активными сущностями (Несколько процессоров, процессор и видеокарта, процессор и DMA контроллер) тогда да, есть смысл взглянуть на SystemC. Возможно где-то в сети есть готовая opensource платформа на SystemC, тогда можно было бы разобраться на готовом примере. Не знаю правда есть ли что-то подобное в сети.

В комплекте с коммерческими EDA пакетами такие примеры есть (например в Virtualizer), я разбирался в TLM2.0 на этих примерах.

Про TLM-2.0 есть tutorial в открытом доступе. Его правда достаточно сложно понять. Он скорее подходит для того чтобы освежить всё в памяти, а не для обучения с нуля.

www.doulos.com/knowhow/systemc/tlm2/tutorial__1

Daffodil

28.12.2015 21:58+2Мне тоже всегда хотелось написать свою модель процессора на C++. Но, к сожалению, не хватает на всё времени.

Pugnator

29.12.2015 00:06+2спасибо огромное за столь развернутое объяснение. Я лишь пишу модели для Proteus на Lua, и хотел прикрутить SystemC ради более выразительного описания процессоров, нежели разрозненные модули выдумывая каждый раз что-то новое.

Я обратил внимание на QBox, он имеет уже интерфейс к Qemu, TLM 2.0

И вот даже готовые модули, к примеру, Cortex-M3

У меня всё очень любительское, но эту тема мне очень интересна

Daffodil

29.12.2015 00:58Спасибо за ссылку на GreenSocs/QBox, не знал про них. Посмотрел на исходники Cortex-M3 платформы: там уже не чистый SystemC/TLM, а более хитрая библиотка работающая поверх SystemC.

Наверное разбираться во всём этом как хобби это уже слишком, надо хобби превращать в работу за деньги.

capitanov

28.12.2015 14:19Спасибо, интересная статья! Хотелось бы добавить, что в Vivado HLS от Xilinx большую роль играют директивы, с помощью которых можно получать те или иные результаты по пропускной способности, максимальной задержке и ресурсам. Сначала отлаживается алгоритм в чистом виде, без привязки к железу, а затем путем вставки директив в нужные места, идет борьба за ресурсы и скорость. Насчет handshake/axi вы правы, Xilinx может создать монстрообразную конструкцию с кучей лишних портов, которые потом придется на RTL уровне соединять. Но весь этот процесс можно обуздать. В любом случае, вендоры правильно поступают, привклекая Сишников в разработку на FPGA, особенно с учетом того, что современные кристаллы настолько огромные, что забить его чистым RTL-кодом не так-то и просто :)

Daffodil

28.12.2015 17:38В статье я называл эти директивы «спецификацией микроархитектуры». Они присутсвтуют во всех HLS.

Atakua

28.12.2015 16:39+1Толково написано, спасибо.

При этом нельзя сказать, что SystemC на этом рынке является доминирующим решением: существуют и продукты, SystemC не использующие, например WindRiver Simics.

Как один из разработчиков Simics хочу уточнить это утверждение.

Действительно, функциональные (т.е. не потактовые) модели устройств в Simics пишутся на языке DML (device modeling language), который наиболее хорошо выражает типичные функциональные особенности (банки регистров, порты, карты памяти и т.п.). Однако существующую огромную IP-базу моделей, написанных на SystemC, нельзя игнорировать. Поэтому существует возможность интеграции такого кода в модели Simics. Самое интересное при этом — это сопряжение различий в парадигмах моделирования времени в SystemC и Simics.

Daffodil

28.12.2015 18:25Можно ли запускать Simics как slave в SystemC симуляции? В этом случае мы могли бы например использовать софт бегущий на simics для тестирования RTL. К примеру, использовать драйвер сетевой карты для тестирования RTL модели сетевой карты :)

Atakua

28.12.2015 21:06Я не уверен насчёт деталей master-slave отношений, которые сейчас доступны в Simics. Текущие усилия по интеграции всё-таки были сконцентрированы на переиспользовании существующего кода, чтобы максимально быстро получить модель полной платформы. Хотя нужно понимать, что производительность при этом будет страдать. SystemC модели слишком точные и медленные по сравнению с «родными» функциональными.

> К примеру, использовать драйвер сетевой карты для тестирования RTL модели сетевой карты

Чаще бывает наоборот — драйвер к моменту наличия модели (SystemC/DML — неважно) ещё не готов или совсем ещё плох. Но в принципе, я думаю, и Ваш сценарий на практике кем-то жа был уже опробован.

Daffodil

28.12.2015 22:13По поводу слишком медленных и точных SystemC моделей: всё зависит от того как писать. По хорошему, Untimed модель должна быть на 99% на чистом C++ и минимально использовать фукнции SystemC вызывающие переключение контекста. В идеальном случае переключение контекста нужно только для того чтобы сгенерировать прерывание.

Чаще бывает наоборот — драйвер к моменту наличия модели (SystemC/DML — неважно) ещё не готов или совсем ещё плох. Но в принципе, я думаю, и Ваш сценарий на практике кем-то жа был уже опробован.

Ну идея в том чтобы писать железку и драйвер одновременно. Hardware/Software Codesign, о необходимости которого всё время говорили большевики.

Мы сейчас пытаемся вставить в RTL симуляцию C++ную модель процессора на которой бежит реальное firmware.

Daffodil

28.12.2015 22:14Хотел кстати спросить, многопроцессорные системы в Symics симулируются в одном треде операционной системы, или можно запустить каждый процессор в отдельном треде?

Atakua

30.12.2015 12:10В последней версии Simics 5 некоторые модели архитектур ЦПУ x86, ARM, ppc могут исполняться параллельно даже при работе с общей памятью. Если общей памяти не шарится (например, моделируются несколько плат, соединённых по сети ), то такие части можно запускать в параллель, и это работает уже давно.

tsafin

30.12.2015 12:19Гриша Atakua а зачем в одной конфигурации замешивать x86, arm или powerpc? Был реальный usage-case?

Atakua

30.12.2015 23:15+1Я имел в виду, что если в модели есть несколько ядер x86, то в пятой версии симулятора они могут быть помещены в домен с общей памятью и при этом симулироваться параллельно. Не для всех моделей разных архитектур эта возможность сейчас поддерживается, т.е. скажем, модель процессора от MMIX (гипотетическая многоядерная) в Симиксе из коробки будет работать только в квотированном режиме на одном хозяйском процессоре. Добавление возможности параллельной симуляции для нового процессора — непростая вещь, и, что немаловажно, далеко не все сценарии симуляции получат от этого выигрыш. Например, при работе системного кода (UEFI, firmware, ...) часты доступы к устройствам, код IO-bound, и от параллелизации толку нет.

> зачем в одной конфигурации замешивать x86, arm или powerpc? Был реальный usage-case?

В современных платформах очень часто вместе с центральным процессором от IA-32 идут контроллеры (security, сенсоры, управление питанием) от иных вендоров или не с архитектурой x86.

Kopart

28.12.2015 16:41Так и не нашел для себя ответ на вопрос:

Вы описываете как аналогичные конструкции SV выглядят на SystemC, но при этом этом для синтеза все равно используется HLS-синтезатор.

Это выглядит как прослойка в виде SystemC, чтобы иметь возможность написать SV код в C++ для синтеза.

Почему от этого не отказываются в пользу чистого HLS-синтеза с директивами (или OpenCL), но без специальных классов SystemC, которые опускают программистов на низкий уровень абстракции SV?

Daffodil

28.12.2015 18:06Вы правы, в одном из юзкейсов SystemC можно рассматривать как прослойку, позволяющую написать SV код в C++ для синтеза. Это нужно для того чтобы склеивать HSL блоки с SV модулями. Альтернативный подход — использовать некоторый стандартный набор сигнальных интерфейсов в HLS, а в случае если нужен нестандартный интерфейс, конвертор можно написать в SV. Vivado HLS как раз поддерживает такой подход.

Но у синтезируемого SystemC есть еще одна важная область использования: спецификация параллелизма на уровне процессов. SystemC это как pthreads для моделирования аппаратуры.

Проще всего объяснить на примере: представьте что вам нужно написать out-of-order процессор. Тогда у вас есть процесс который накачивает данные, есть процесс-плнировщик, набор процессов для исполнения (integer и floating point), процесс с reorder buffer'ом и сохранением результатов. Исполняться они будут параллельно. SystemC позволяет явно специфицировать каждый процесс и соединить их с помощью каналов. Причем с нулевыми накладными расходами (всё как в SV).

YuriPanchul

29.12.2015 00:47+4Напишу свой пост 2012 года с критикой SystemC. Глядя назад, пост слишком энтузиастичен по поводу UVM, но мое мнение про SystemC сейчас то же, что и в 2012 году:

panchul.livejournal.com/203346.html

Вот позавчера мне пришло письмо от джентлемена из одного российского университета, который занимается верификацией дизайнов на VHDL с помощью тестов, написанных на SystemC. Джентлемен спрашивает, имеет ли смысл транслировать тесты из SystemC в VHDL с помощью какого-нибудь third-party тула, наподобие тула от британской компании Celoxica, который использовали его коллеги. В качестве симулятора они, насколько я понял, используют ModelSim, который входит в состав Altera Quartus.

Мой ответ:

1. Disclaimer

Я обычно пишу такие ответы довольно уверенным тоном, но мой тон не означает, что я пытаюсь навязать свое мнение как истину в последней инстанции. Вашему научному руководителю может быть виднее, а для студентов полезно экспериментировать с разнообразными технологиями, даже если подобные эксперименты были не очень удачны в прошлом. Тем не менее, мое мнение может быть для вас полезным, так как я в свое время заседал на заседаниях, на которых присутствовали и маркетеры SystemC, которые потом перестали со мной здороваться. Кроме этого, я должен предупредить, что так как я пишу блогпост в Живом Журнале, а не статью для СМИ, я не буду перепроверять все свои утверждения, а также не буду делать расследование текущего состояния тех технологий, за которыми я перестал следить. Учитывая, что речь пойдет о развитии языковых средств за последние 15 лет, я могу запросто сказать что-нибудь не то.

2. Кратко

С моей точки зрения, SystemC всегда был и остается неудачной технологией, подерживаемой на плаву маркетингом различной степени недобросовестности. Несмотря на то, что некоторые группы в Европе в начале 2000-х годов стали использовать SystemC для системного моделирования, сейчас многие индустриальные команды стараются избавиться от кода, написанного на SystemC и перевести всю верификацию на SystemVerilog. Это связано с тем, что SystemC не ликвидировал неудобства, связанном с его использованием (см. ниже), а также не смог накопить критическую массу средств для functional-coverage based constraint random verification methodology — методологии, которая появилась в языках для верификации e/Specman, OpenVera и SystemVerilog, и которая стала в последние годы мейнстримом. Кроме этого, сейчас в индустрии приобретает все большую популярность Universal Verification Methodology (UVM), основанная на SystemVerilog. Так как эта методология еще год назад считалась нестабильной, существует множество мелких возможностей для создания разнообразных стредств автоматической верификации и тулов для верификационных инженеров на платформе UVM. Несмотря на то, что UVM критикуют за излишнюю сложность, эта все еще открытая ниша может эксплуатироваться как университетскими группами, так и небольшими компаниями.

<lj-cut text=«Дальше»>

3. История и проблемы с SystemC

3.1 Начало

В начале 1990-х годов произошло распостранение С++. После этого в середине 1990-х годов одновременно у нескольких людей возник зуд имплементировать HDL в виде библиотеки С++ классов, используя переопределение операций (overloading), чтобы обыкновенное присваивание вызывало скрытое обращение к event-driven simulation engine. Этот зуд возник у партнера (забыл имя) Джона Сангвинетти, двух немецких студентов, джентльменов из бельгийского исследовательского центра IMEC и лично меня.

Лично у меня идею идти этим путем обломал некий маркетер в Mentor Graphics, где я в то время работал, и я написал впоследствие свой тул для трансляции из С в Verilog, используя другую идею, а также сделал технологию CycleC, которая строилась на cycle-driven simulation, а не на event-driven simulation, как у SystemC (см. http://en.wikipedia.org/wiki/C_Level_Design).

Джон Сангвинетти и компания создали компанию C2DA / CynApps, которая впоследствие слилась с Forte. Сначала C2DA сделали библиотеку классов, которая напоминала SystemC, но была более элегантной. Впоследствие им пришлось под давлением от индустриальной политики отказаться от своей библиотеки и использовать SystemC в качестве входного языка.

Джентлемены из IMEC создали странную технологию, при виде которой у хардверных инженеров соловели клаза и они погружались в кому. Классы в C++ вообще вызывали у хардверных инженеров отторжение, но в случае с IMEC-ом они еще и как-то хитро генерировали HDL код во время симуляции, или что-то в таком духе, забыл идею.

Двое немецких студентов решили реализовать VHDL в C++. У маркетинга Синопсиса сработал условный рефлекс на слово «Си» и SystemC был рожден.

Кроме вышеперечисленных, в период 1996-1999 в мире появилось еще пара компаний, которые разными способами транслировали (или делали вид, что транслировали) С в хардвер — Handel-C/Embedded Solutions/Celoxica и Frontier Design. У всех претендентов были похожие слайды и похожий объем венчурного финансирования, хотя продавали все компании разное. Ни у одной из компаний не было уверенного успеха. У C Level лицензии приобрели Hitachi и Fujitsu, у CynApps и Frontier — еще кто-то, ESL/будущая Celoxica выпустила прес-релизы, что они «разослали свой С-подобный продукт в 50 университетов». Мнение индустрии (точнее, слухи, распускаемые Синопсисом) были «это все фигня, вот сейчас выйдет Синопсис и всех уроет».

3.2 Выход в свет и первые реакции

И вот в начале 1999 года Synopsys выкатил на обозрение то, чем они собирались всех урыть — первой версией библиотеки классов SystemC, которая реализовала классы, имплементирующие модули, порты и сигналы. Несмотря на то, что перед презентацией был огромный ажиотаж, показанное вызвало разочарование у многих инженеров.

Дело в том, что большинство хардвер-инженеров в 1999 году под словом «C» имело в виду тот ANSI C, который им когда-то преподали в коледже для писания простых алгоритмов, а не C++ с классами, темплейтами, виртуальными функциями и overloading. Все эти красоты хардверные инженеры видали в гробу, посколько это не входило в сферу их проблем — как организовать конвейер, оптимизировать тайминг и т.д. До презентации многие хардверные инженеры думали, что Synopsys покажет им тул, который магически траслирует untimed алгоритмы, написанные на бедненьком простеньком С в отпимизированных хардвер. В Synopsys верили — ведь за 10 лет до этих событий они организовали революцию в области логического синтеза.

«Прохладная встреча — ну и ладно», — подумали синопсоиды. «Мы сейчас как рррразвернем нашу маррркетинг-мышцу и заставим инженеров принять наш тул через их головы, впаривая его их менеджерам».

Это план не прошел. Инженеры реагировали так, как будто их пробует изнасиловать представитель несовместимой с ними сексуальной ориентации. «Ни за какие деньги!!!»

Причин у такой реакции было несколько:

1. Без хорошего понимания C++ пользователи SystemC постоянно налетали на ошибки компиляции, связанные с overloading в сложноустроенных templated классах для сигналов и портов разной ширины. Эти ошибки были так же далеки от их жизни, как general protection fault от феминистических статей Натальи Радуловой. Хардверные инженеры не собирались ради этой хрени учить нюансы C++ и тем более разбираться с кишками библиотеки SystemC. Чтобы бороться с таким явлением, всевозможные SystemC консультанты стали предлагать писать конструкции с аксессорами типа вместо «a = b + c» писать «a.write (b.read () + c.read ())». Это выглядело неубедительно, особенно для пользователей Verilog-а, хотя пользователи VHDL уже были в прошлом

Daffodil

29.12.2015 02:11+3Спасибо за ответ, было интересно узнать про историю SystemC подробнее. Ведь я во время описываемых событий ещё учился в школе!

Попытаюсь выступить в роли адвоката SystemC и ответить на критику:)

1. Про сложность SystemC для среднестатического хардверщика: полностью согласен. С точно такой же критикой C++ выступают программисты на Си. C++ это наверное один из самых сложных языков программирования. Поэтому большинство инженеров использующих SystemC, которых я знаю, имеют C++ный бэкграунд (неторые даже не знают Verilog/VHDL).

2. Про время компиляции: какое оно имеет значение если время симуляции на порядок больше? Если говорить про простейшие модули, то на моём десктопе и SystemC и Verilog компилируются меньше секунды, без precompiled headers.

3. SystemC симулируется медленнее чем Verilog в компилирующем симуляторе.

Простой ответ: это проблема компилятора, а не SystemC. Технически, ничто не мешает сделать компилирующий симулятор для SystemC.

Правильный ответ: не нужно писать RTL на SystemC. На SystemC нужно стараться использовать untimed код и TLM интерфейсы.

Пример из жизни: занимаюсь сейчас обработкой видео: Синтезируемый SystemC обрабатывает один кадр примерно за 30 секунд, полученный из него RTL на Verilog — около 10 минут.

4. Про медленное смешанное исполнение SystemC и HDL. Не знаю, может и так. Но мы верифицируем SystemC без HDL примесей. А Full-chip симуляцию проводим на SystemVerilog, без SystemC.

5. TLM 2.0 — странная технология. Может быть. Но сама идея обмена данными через function-call'ы очень правильная. Никто вас не заставляет использовать TLM2.0, можно придумать свой велосипед с похожим функционалом.

Как мне кажется история с TLM2.0 ровно такая же как c UVM: они облегчают торговлю IP. В случае TLM-2.0 это IP для виртуальных прототипов. В случае UVM — это IP для верификации.

6. Альтернатива SystemC — SystemVerilog и UVM. Это мне кажется вопрос привычки: на SystemC вполне можно написать testbench в UVM стиле. Европейцы уже даже запилили UVM на SystemC. Рандомизировать пакеты тоже можно, и функциональный coverage мерить, и code-coverage тулы для C++ тоже есть.

Но на деле часто получается что пока ты пишешь свой суперрандомизированный тест, парни в соседней комнате уже подняли FPGA эмулятор и ОС запускают. А дальше приходится уже трейсы с железа снимать и писать директед тесты, чтобы понять почему оно повисло.

Но это конечно зависит от проекта. Не знаю как у вас всё устроено. Наверное в MIPS вы одно ядро можете десяток лет продавать и поддерживать, поэтому можете даже формальную модель написать, чтобы она вам без симуляции всё доказала.

potan

29.12.2015 16:03А BlueSpec Вы не видели? Интересно с ним сравнить.

Daffodil

29.12.2015 20:26+3Видел, но не пробовал. Хотя знаю людей которые его использовали для быстрого прототипирования архитектуры на FPGA. Отзывались положительно.

Насколько я понимаю язык BlueSpec либо умер, либо умирает. Сейчас просто невозможно заставить кого-то изучать язык не выкладывая при этом тулы в опенсорс.

Я читал спеку на язык. BSV это описание аппаратуры в стиле функционального программирования c системой типов из Haskell. Как мне кажется, идея в целом правильная. Функциональное программирвоание хорошо ложится на вычислительную среду в виде массива триггеров/вентилей.

CodeRush

Хабр снова торт! Спасибо большое за статью.

Сталкивался с SystemC во время учебы, и тогда он показался достаточно интересным, но проблемы с открытыми (или хотя бы дешевыми) утилитами для синтеза останавливали. Видно, что с тех пор прогресс ушел далеко вперед, но утилит таких по прежнему нет — печально.