Последнее время в своей работе постоянно сталкиваюсь с задачами по снижению потребления разрабатываемых микросхем. Наиболее популярными на текущей момент решениями являются динамическое управление тактированием и напряжением питания. Т.е. если для решения текущей задачи не требуется тот или иной блок микросхемы, то для него отключается тактирование, снижается или вовсе отключается напряжение питания. Такие гранды как Texas Instruments и Renesas пока меряются

Потребляемая микросхемой энергия обусловлена двумя причинами:

— статический ток утечки в транзисторах даже в том случае если они не переключаются.

— динамический ток, требующийся для перезарядки емкости цепей когда происходят переключения.

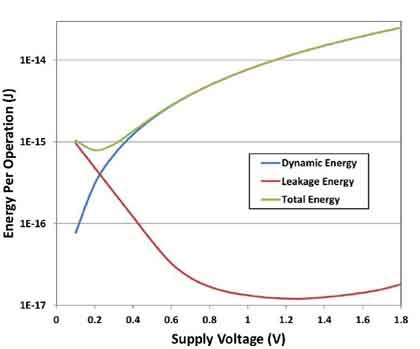

Для обычных схем при работе динамический ток преобладает, особенно для высоких уровней питающего напряжения, которые сейчас используются. Зависимость токов потребления от напряжения питания показаны на следующем рисунке.

Так как динамический ток потребления пропорционален квадрату напряжения питания, то именно снижение напряжения питания является основным ключом к снижению общего потребления микросхемы (при этом мы имеет обратный, но не такой драматический эффект роста статического тока потребления). Например, если сравнить обычную схему с 1,8В питанием и схему работающую в около пороговой области на 0,5В, то динамическое потребление снижается в 13 раз. А для схемы работающей на под пороговом напряжении 0,3В потребление может быть снижено в 36 раз.

Традиционный дизайн цифровых микросхем предполагает два состояния транзистора – «открыт» и «закрыт» — и это основа концепции реализации цифровой логики. Аналоговые разработчики могут оперировать с транзисторами в режиме усиления, т.е. на уроне порогов. Использование подпороговых напряжений означает, что транзистор никогда не будет «открыт». И таким образом «логической единице» будет соответствовать практически не отличимое от «закрытого» состояние транзистора. А это означает, что для реализации микросхем по такой схеме требуются новые подходы и решения.

Подпороговые решения известны уже несколько десятилетий.

Разработка схем с подпороговыми напряжениями питания не являются чем то сверхновым. Еще в 70-х года швейцарские часовщики заметили потенциал использования транзисторов в подпороговом режиме. Эта идея используется для кардиостимуляторов и RFID меток, но пока кроме этого более нигде активно не применялась. После затишья, которое длилось несколько десятилетий, данная тема снова обрела академический интерес в конце 90-х начала 2000-х годов. К этому времени стало очевидным значение тока потребления в коммерческой электронике и начались исследования различных методов в области снижения токов потребления. Учредители Ambiq были частью данных академических исследований, когда работали в Университете штата Мичиган. Основным направлением их исследований была коммерциализация данной технологии.

Возникает вопрос, почему если возможность работать с подпороговыми напряжениями питания были известна с 70-х годов, то она до сих пор не применяется. Возможно, что недостатки этого подхода не позволяют применить его в обычных условиях. Проще говоря: «Если это так просто, то почему все не делают так ?» Ответ прост: «Потому что это очень не просто». В этой технологии нет фатальных недостатков, но переход к методам работы с подпороговыми напряжениями питания не тривиален. Можно так же спросить, что изменилось с 70-х годов, когда появились первые подпороговые коммерческие устройства. В первую очередь изменились масштабы. Старые разработки использовали максимум несколько десятков транзисторов работающих в подпороговом режиме и такая схема могла быть рассчитана и оптимизирована вручную. Сейчас микросхемы содержат миллионов транзисторов. Рассчитать такую схему вручную невозможно и для их разработки приходится использовать стандартные программные инструменты, которые ориентированы в первую очередь на работу со стандартной надпороговой логикой. И адаптация стандартных инструментов и подходов для работы с подпороговым напряжением питания позволили компании Ambiq коммерциализировать эту технологию.

Проблемы подпорогового режима

Адаптация стандартных надпороговых подходов для разработки схем с подпороговым напряжением питания имеют несколько ключевых проблем.

Плохие модели транзисторов

Модель транзистора эта основа основ всего в разработке современной микроэлектронике. Все симуляторы, все абстракции и автоматизации всего процесса разработки завязаны на точность модели транзистора.

Большинство современных моделей транзисторов сфокусированы на его работу при высоких напряжениях питания, т.е. они достаточно точно описывают его поведение при питании значительно выше порога. Но при питании от 0В до порога эти модели не работают вовсе или выдают неадекватные данные.

Логические переключения и шумы

В подпороговом режиме для обнаружения изменение тока через транзистор при переходе из «открытого» в «закрытое» состоянии и обратно требуется большая чувствительность. И хотя токи изменяются в геометрической прогрессии от изменения напряжения, но они все равно остаются чрезвычайно малыми. В подпороговом режиме ток через «открытый» транзистор всего в 1000 раз больше тока «закрытого» транзистора, в то время как для обычного режиме это соотношение превышает несколько миллионов. Таким образом, внешним шумам значительно легче исказить работу схемы.

Чувствительность к условиям эксплуатации

Подпороговый режим работы транзистора также гораздо более чувствителен к отклонениям процесса изготовления и условий окружающий среды. Например, при отклонении процесса изготовления кристаллов в медленную сторону ток через транзистор будет в 10-100 раз меньше чем при типовом процессе. С учетом того что и так соотношение токов «открытого» и «закрытого» составляют порядка тысячи такое изменение не может быть проигнорировано.

Перепады температуры так же оказывают огромное влияние на токи транзисторов. При этом изменения токов в подпороговом режиме на порядки превосходят изменения токов в обычном режиме. Таким образом, при разработке схемы с использованием подпороговых напряжений питания разработчикам требуется дополнительные усилия, что бы схема была работоспособна в различных условиях эксплуатации.

Инфраструктурные проблемы

Современное процесс производства микросхем основан на использовании надпороговых напряжений питания, и перестают работать при применение под пороговой технологии. Это связано с различными проблемами, например, тестовые установки и измерительные приборы с помощью которых контролируются процессы изготовления не обладают достаточной точностью, требуемой для работы с под пороговыми напряжениями питания. Эти измерительные приборы позволяют измерять микроамперы, а нужно нано- и даже пикоамперные диапазоны.

Даже набор характеристик схем на подпороговом напряжении питания должен быть переосмыслен по отношению к традиционным схемам. Типичный набор свойств не может быть достаточным, что бы доказать, что схема с подпороговом напряжением питания будет работать полностью правильно во всех режимах эксплуатации.

Решение от Ambiq

Разработанная Ambiq SPOT технология позволяет лучше понять поведение транзистора в этих условиях. Ambiq охарактеризовала некоторый выбранный набор транзисторов из обычной технологии изготовления для работы в подпороговом режиме. При этой характеризации были обмерены большое число однотипных транзисторов для получения качественных статистических данных разброса параметров, это необходимо для того что бы обнаружить и понять различные эффекты, вызванные отклонением процесса изготовления, влиянием окружающей среды.

После того как были получены качественные модели транзисторов на их основе была разработана библиотека стандартных цифровых ячеек, которые смогут работать в подпороговом режиме. Данная библиотека так же тщательно исследована и охарактеризована. При разработке библиотеки стандартных ячеек приходилось решать две взаимоисключающие задачи — приходилось делать схемы с крайне высокой чувствительностью, и при этом минимизировать собственное потребление ячейки.

Разработка аналоговых схемы требуют дополнительных усилий. В то время как разработка цифровых ячеек для подпорогового режима была во многом построена по переработке уже существующих решений, то для разработки аналоговых блоков требуется другие схемотехнические решения, которые принципиально отличаются для тех, которые обычно применяются. При разработке схем с подпороговым уровнем питания нет общих подходов, подходящих для всех случаев. В некоторых случаях реализовать схему на подпороговом режиме транзисторов не удавалось, и приходилось использовать транзисторы в обычном режиме с обычным питанием, и применение таких схем в малых количествах не сильно сказывается на общем потреблении. Хорошим примером этого служит энергонезависимая память, в которой хранятся настройки и калибровочные коэффициенты пока устройство выключено. При включении питания схема начинает работать в режиме с питанием выше порога. После того как настройка завершена и калибровочные коэффициенты переписаны в настоечные регистры питание снижается до подпорогового уровня, а энергонезависимая память больше не используется. В случаях когда требуется повышенная производительность и подпорогового напряжения уже не хватает для обеспечения требуемой скорости, напряжение может быть поднято до порогового уровня или даже выше. Очевидно, что в этом случае растет и потребление. Так же для стабильной работы схемы приходится динамически отслеживать внешние факторы, например, такие как температура, и в зависимости от них перестраивать режимы работы подпороговых схем, для обеспечения их качественной работы.

Много усилий было потрачено на то, что бы технология работы в подпороговых режимах обеспечивала работоспособность в рамках стандартных процессов изготовления кристаллов. Специальные процессы изготовления кристаллов могли бы облегчить жизнь, но они значительно удорожили изготовление. Технология Ambiq работает в тех процессах, которые уже хорошо известны и проверены и широко применяются.

Процесс разработки основан на специальной библиотеке охарактеризованной для специальных условий работы в подпороговых режимах. Этот процесс во многом повторяет те задачи которые стоят при разработке схемы для 28-нм процесса. Ambiq просто сделала тоже самое для более простых и доступных технологий, что позволило значительно снизить потребление.

Очень большое внимание было уделено задачам тестирования схем. Так как обычное измерительное оборудование не может с достаточной точностью измерить потребление микросхемы. Так же отбраковочное тестирование микросхем требует большей тщательности, нежели это принято для обычных микросхем, так как требуется измерить микросхему в большем числе комбинаций внешних условий.

В целом все этапы разработки микросхем были переосмыслены и изменены для обеспечения работоспособности схемы в подпороговом режиме и снижения тока потребления. Разработка схем по новой технологии требует, что бы они были проверены, что они работают в течении длительного времени жизни. Для разработчиков аппаратуры надежность микросхем является не менее важным параметром на ряду с потреблением. По этому микросхемы от Ambiq были подвержены целой серии испытаний на надежность, в том числе в условиях экстремальных воздействий внешних факторов. В том числе были проведены другие стандартные испытания, например на устойчивость к статическому электричеству. Все испытания доказали, что микросхемы обладают необходимой надежностью.

Заключение

В настоящее время компания Ambiq уже выпустила серию микросхем часов реального времени с потреблением не более 55 нА. И планирует начать выпуск микроконтроллеров серии Apollo c предельно низким уровнем потребления 30 мкА/МГц.

Основные характеристики микроконтроллеров Apollo:

- Сверх малое потребление в активном режиме 30 мкА/МГц

- Сверх малое потребление в спящем режиме 100 нА (RTC включен)

- Высокопроизводительное ядро ARM Cortex-M4F

- Тактовая частота до 24 МГц

- Память программ до 512 Кбайт Flash

- Память данных до 64 Кбайт

- АЦП 10 бит, 13 каналов со скоростью до 1 Мвыб/с

- Стандартный набор периферии I2C, SPI, UART

- Напряжение питания от 1,8В до 3,8В

- Компактные корпуса 64 выводной BGA и 42 выводной CSP

Сравнение микроконтроллера Apollo с другими микроконтроллерами:

Сравнение проводилось на тесте Coremark.

По материалам:

Комментарии (13)

Ivan_83

30.04.2015 21:18+4Только вот защищённость устройств от всякого рода помех всё падает и падает, вместе с тех процессом и потреблением.

kosmos89

01.05.2015 02:27>Так как динамический ток потребления пропорционален квадрату напряжения питания

Не ток, а мощность.

amartology

01.05.2015 08:40+1Пожалуйста, вычитайте статью как следует. Количество опечаток просто зашкаливает.

А за сам перевод/обзор спасибо, забавно почитать, как люди из хорошо известных и проверенных решений создают у окружающих ощущение офигенного ноу-хау.

barabanus

01.05.2015 14:07+2Похоже, что статья очень переработана маркетологами, детали по сути отсутствуют. А еще если Ambiq сравнивает свой еще не вышедший чип с Atmel, то тогда бы сравнила его с Smart SAM L21 с заявленным потреблением 35 мкА/МГц.

Sergei2405 Автор

02.05.2015 15:18Статья основана на их инвестор зазывалке. И перевел ее потому что в ней описаны основные проблемы так, что бы даже бухгалтер понял.

По поводу сравнения с SAM L21 от Атмеля. Мопед не мой, как говорится, но все равно почитал их спецификацию.

Рабочее напряжение питания ядра VDDCORE не ниже 0,9В. (скорее всего что то стандартное 90 нм с малым потреблением). А весь фокус (все честно, не спорю) в их встроенном регуляторе который и вырабатывает VDDCORE. И когда он работает в LDO режиме имеем стандартное потребление 75-100 мкА/МГц. А когда он в импульсном режиме, то ток потребления снижается до 35 мкА/МГц, но по питанию 3,3В. А это значить что ядра с питанием 0,9В все равно потребляет ~100 мкА. Если такой же фокус сделать с Ambig то потребление по первичному питанию у них получится 30 мкА*0,5В/3,3В = 5 мкА/МГц. Тут кончено тоже много подводных камней, так как на малых частотах собственное потребление регулятора будет преобладать.

amartology

02.05.2015 18:10Импульсник-то встроенный можно с очень хорошим КПД даже на малых токах сделать.

FYR

05.05.2015 14:48Пороговое напряжение это для полевых транзисторов только? Просто к биполярным оно вроде как отношение не имеет. Там уже токи насыщения и т.д.

Номер два — если правильно помню курс то ВАХ униполярных/канальных транзисторов на допороговых напряжениях это вообще очень сложная тема и ее не просто сложно смоделировать, ее смоделированную потом очень сложно повторить в «железе».

И номер три — боюсь даже представить как выглядит обычный триггер на допороговых напряжениях. А как расчитывать это все?

amartology

05.05.2015 16:25Биполярные схемы давно уже не являются мэйнстримом. Все, что можно сделать на КМОП, делается на КМОП.

По номеру два и три — современные САПР творят чудеса, как те, которые моделируют, так и те, которые снимают параметры моделей. Вопрос исключительно в том, сколько времени и сил вы готовы положить на то, чтобы оно заработало.

Halt

Интересная информация, спасибо!

Если эту технологию совместить с самосинхронными схемами то получится вообще что-то фантастическое. Устройства питающиеся от теплового или электромагнитного фона станут реальностью.

grossws

Уже сейчас потребление стало таким, что многие устройства могут работать за счёт energy harvester'ов (вибрационных, фотоэлектрических). Последние несколько лет — довольно активный тренд в этом направлении.

Halt

Я понимаю. Тем не менее, порядок величин еще такой, что массовым это сделать пока не получается. Эта же технология может открыть путь к широкому применению где можно и где нельзя.

amartology

Профильные журналы по электронике уже который год полны статьями о разработках преобразователей напряжения от уровней, получаемых energy harvester'ами, до разумных напряжений питания — это значит, что коммерческие продукты будут уже вот-вот. И, что характерно, без всяких фантазий типа самосинхронной схемотехники.