Сразу к делу — вот о чём написано в этой статье:

- Материалы для производства печатных плат

- Учет изменения толщины препрега в процессе изготовления PCB

- Учет Etch Factor

- Особенности расчета толщины металлизации

- Учет паяльной маски

Все описанное ниже — это не Know How, а по сути, собранные воедино и систематизированные данные из разных источников. На абсолютное знание мы также не претендуем.

Итак, поехали.

Материалы для производства печатных плат

Преамбула (как обычно это происходит).

Обычно инженер примерно оценивает стек платы, передает его производителю PCB. В ответ ему приходит много китайских бланков с предложениями — на которые он обычно соглашается. Сводятся они к изменению толщин ядер/препрегов, а также проводников и зазоров в CAM редакторе.

Обычно оно и нормально. Но тут есть три минуса:

- Итоговое изделие отличается от того, что описано в вашей КД (иногда чуть более, чем полностью).

- Повторяемости результата при переходе к другому производителю — нет. Например у нас есть борд, который запускался на двух разных фабах с совершенно разными стеками (при этом исходные данные в обоих случая были одни и те же).

- Если толщины проводников на печатной плате находятся в зоне 4 mil — то любое изменение их ширины в сторону уменьшения весьма серьезно влияет на потери. Если между проводником 6 mil и 5 mil разница незначительна, то между 5 mil и 4 mil — весьма существенна, а 4 mil и 3 mil — это с точки зрения потерь разные вселенные. (Вообще на наш взгляд идеальные топологии дифференциальной пары — 6-6-6 или 7-7-7).

Поэтому мы предпочитаем сформировать стек так, чтобы его зависимость от особенностей конкретного производителя PCB сводилась к минимуму. Если вы работаете с одним и тем же вендором, то вполне реально сформировать стек так, чтобы его модификация производителем не требовалась совсем. Это экономия 1—2 недель при подготовке к производству.

Кстати оффтоп.

Наверняка кто-то нибудь захочет спросить — что лучше, сильносвязанные или слабосвязанные дифференциальные пары. Наше мнение: лучше слабосвязанные — их проще выровнять по длине. Можно позволить себе более серьезные бампы. Никаких особенных преимуществ сильносвязанных пар перед слабосвязанными (если не рассматривать странные топологии типа 5-14-5) c точки зрения SI на наш взгляд — нет. Для любителей формальных правил: одна-две ширины между проводниками в паре — нормально. Больше — уже не очень. Меньше — трудно выравнивать. Несмотря на то, что ЭМС показатели сильносвязанных пар сильно лучше, в абсолютном выражении это «сильно» — несущественно.

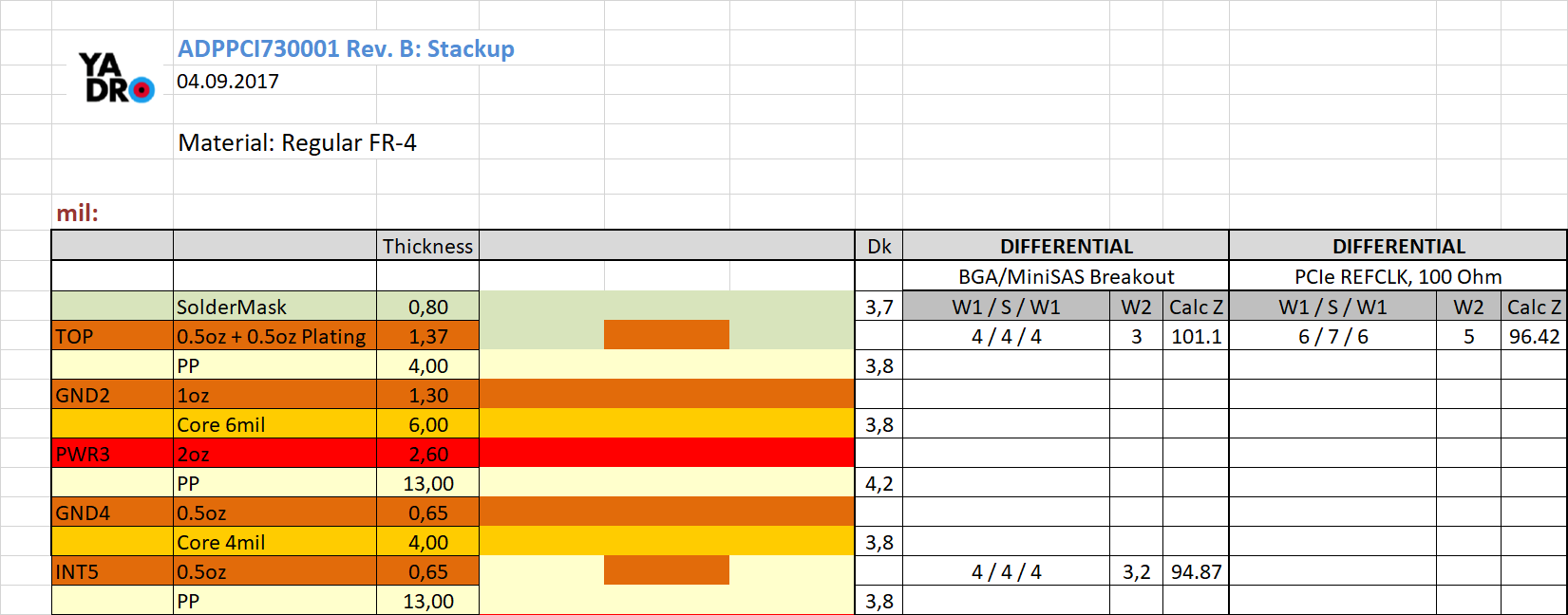

Для того, чтобы более-менее точно сформировать стек печатной платы — нужно знать параметры конкретных ядер и препрегов применяемого материала. В даташитах приводятся усредненные параметры для всей группы и для точного расчета эти данные не годятся. Данную информацию можно запросить как у производителя материала, так и у производителя PCB. Это таблица, которая выглядит это примерно так (у каждого производителя материала она своя):

Толщины разных типов препрегов — как правило, одни и те же у разных производителей. Поэтому информация на приведенной картинке — актуальна и юзабельна безотносительно к производителю материала (Dk/Df, понятно, у всех разные).

При проектировании стека печатной платы необходимо учитывать, что производители PCB, как правило, делают поправку на ламинацию, снижая значения диэлектрической постоянной (Dk) как препрегов, так и «ядер» примерно на 0.2 по отношению к значениям, приведенным в документации производителя материалов.

Если значения Dk/Df приведены для разных частот, то рекомендуется использовать значения данных параметров для частоты, наиболее близкой к частоте Найквиста наиболее быстрого интерфейса на PCB. Например, если в PCB присутствует PCI Express Gen3, то следует использовать значения Dk/Df для частоты, наиболее близкой к 4 ГГц.

Кто-то возразит: как же, ведь полоса того же Gen3 простирается аж до 18 ГГц. Это правда — но спецификация PCIe регламентирует RL и IL до Найквиста, да и не пройдут все эти адовые гигагерцы через коннекторы, переходные отверстия и печатную плату — затухнут по дороге. А если пройдут — это большой вопрос, понравится ли вам результат.

В ситуации, когда на PCB присутствует несколько разных высокоскоростных интерфейсов — не стоит в рамках стека одной платы использовать значения Dk/Df для разных частот. Несмотря на то, что такой подход является более верным с точки зрения расчета импеданса — он вызовет большие трудности при согласовании стека с производителем PCB (их тестовое оборудование настраивается на одну конкретную частоту).

В случае, если значения Dk/Df значительно варьируются с частотой, а контроль импеданса критичен — имеет смысл, получив значения импеданса для реальной частоты интерфейса, пересчитать его, взяв Dk для некоторой единой частоты (самого критичного интерфейса). «Отнормированное» таким образом значение импеданса — указать в качестве целевого для контроля производителем PCB.

Например вы делаете расчет 100 Омной трассы для частоты 4 ГГц, используете значение Dk для 4 ГГц, и в соответствии с полученными данными осуществляете трассировку. Далее, если у вас например есть интерфейсы, требующие расчета для 10 ГГц — подставьте значение Dk для более высокой частоты в исходный расчет. Допустим, при этом вы получите значение импеданса 105 Ом. Наш совет: вот 105 Ом и укажите производителю PCB для контроля. Не стоить морочить ему голову разными Dk для разных частот на одном и том же слое.

Также не повредит на берегу поинтересоваться с каким стеклом работает фаб, чтобы не было потом проблем со сроками поставки. Потому что есть популярные препреги и не очень. Обычно на складе у него всегда в достатке 3-4 типа, из которых и стоит выстраивать стек PCB. Материалов с низкими потерями обычно на складе не бывает, в силу ограниченного срока хранения — поэтому применение чего-то особенного это всегда вопрос не столько цены, сколько сроков изготовления.

Учет изменения толщины препрега в процессе изготовления PCB

В таблице ниже приведены абсолютные значения изменения толщины одного слоя препрега для разных условий применения. Допуск на все значения составляет 10%.

| Условия | Изменение толщины препрега при начальном значении | |

|---|---|---|

| Не более 2.3 mil | Более 2.3 mil | |

| Прилегание к меди 0.5 oz с 30% заполнением | 0.4 mil | 0.4 mil |

| Прилегание к меди 0.5 oz с 70% заполнением | 0.1 mil | 0.2 mil |

| Прилегание к меди 1 oz с 30% заполнением | 0.8 mil | 0.9 mil |

| Прилегание к меди 1 oz с 70% заполнением | 0.3 mil | 0.4 mil |

| Прилегание к меди 2 oz с 30% заполнением | 1.8 mil | 1.9 mil |

| Прилегание к меди 2 oz с 70% заполнением | 0.8 mil | 0.8 mil |

| Расположен между двумя слоями препрега | 9% | 10% |

| Прилегание к внешнему слою | не изменяется | не изменяется |

Для более точного расчета изменения толщины препрега можно использовать следующее выражение:

В случае, когда между слоями металлизации расположен один слой препрега — значения изменений толщины для соответствующих условий должны суммироваться, так как изменение толщины препрега на самом деле представляет собой вдавливание в него проводящего рисунка.

При формировании послойного описания PCB следует указывать финишное значение препрега. При этом порция препрега, вдавленная в рисунок металлизации, не должна включаться в значение финишной толщины в документации, передаваемой производителю PCB.

Пример

Необходимо рассчитать финишную толщину стека, приведенного на рисунке. На всех слоях металлизации используется медь 1 oz. Исходная толщина препрега 2116 равна 5.1 mil.

Результирующий стек будет иметь вид:

| Тип слоя | Начальная толщина | Изменение толщины | Финишная толщина |

|---|---|---|---|

| Внешний | 1.35 mil | — | 1.35 mil |

| Слой 2116 | 5.1 mil | — | 5.1 mil |

| Слой 2116 | 5.1 mill | 0.9 mil | 4.2 mil |

| Внутренний сигнальный | 1.35 mil | — | 1.35 mil |

| Core | 39 mil | — | 39 mil |

| Внутренний Plane | 1.35 mil | — | 1.35 mil |

| Слой 2116 | 5.1 mil | 0.4 mil | 4.7 mil |

| Слой 2116 | 5.1 mil | — | 5.1 mil |

| Внешний | 1.35 mil | — | 1.35 mil |

| Итого: | 63.5 mil ± 10% |

Учет Etch Factor

Выражение для расчета Etch Factor для процесса электрического осаждения меди представлено на рисунке:

В таблице приведены значения Etch Factor для разных типов металлизации для различных производителей. Как видите, они сильно разнятся. Поэтому значение EF — это первое, что вы должны уточнить у вашего PCB-партнера.

| Тип слоя | Фабрика 1 | Фабрика 2 | Фабрика 3 | Фабрика 4 | ||||

|---|---|---|---|---|---|---|---|---|

| EF | W2-W1 | EF | W2-W1 | EF | W2-W1 | EF | W2-W1 | |

| Внешний 0.5 oz | 3.4 — 4 | 1 mil | 3.4 — 4 | 1 mi | 3.4 — 2 | 1.5 mil | 2.6 | — |

| Внешний 1 oz | — | — | — | — | 1.66 | 2.4 mil | 2.6 | — |

| Внутренний 0.5 oz | 1.75 | 0.8 mil | 4.33 | 0.3 mil | 1.73 | 1.75 mil | 3 | — |

| Внутренний 1 oz | 2.4 | 1 mil | 4.33 | 0.6 mil | 2.6 | 1 mil | 3 | — |

| Внутренний 2 oz | — | 1.5 — 2 mil | 4.33 | 1.2 mil | 2.6 | 2 mil | 3 | — |

| Внутренний 3 oz | — | — | — | — | 2.6 | 3 mil | 3 | — |

| Внутренний 4 oz | — | — | — | — | 2.3 | 4.5 mil | 3 | — |

Для случаев, когда информация о значении EF от конкретного производства отсутствует – можно считать, что EF принимает следующие значения:

- внешние слои — 2.6

- внутренние слои — 3.7

Особенности расчета толщины металлизации

Металлизация внешних слоев

При расчете металлизации внешних слоев значение толщины меди весом 1 oz, как правило, принимается равным 1.37 mil. Рекомендуется отдельно задавать вес базовой меди и вес осаждаемой меди. Итоговое значение получается в результате суммирования этих двух параметров. Типовые значения приведены в таблице:

| Base copper | Plating copper | ||

|---|---|---|---|

| 0.7oz | 1oz | 2oz | |

| 0.5oz | 1.644 mil | 2.055 mil | 3.425 mil |

| 1oz | 2.329 mil | 2.74 mil | 4.11 mil |

| 2oz | 3.699 mil | 4.11 mil | 5.48 mil |

| 3oz | 5.069 mil | 5.48 mil | 6.85 mil |

Металлизация внутренних слоев

Для внутренних слоев значение толщины меди весом 1 oz, как правило, принимается равным 1.3 mil.

Учет паяльной маски

При учёте паяльной маски опираемся на следующую схему:

В случаях, когда явно не указано иное, можно считать, что паяльная маска имеет следующие параметры:

- Dk — 3.7

- Df — 0.025

- Толщина — 0.8 mil

Большинство производителей при учете влияния паяльной маски считает значения C1, C2 и C3 равными друг другу.

Некоторые фабрики считают значения C1 и C3 равными толщине металлизации (T1), а C2 – 0.8 mil. Правильность данного подхода приблизительно подтверждается реальными данными, полученными после производства PCB.

Один из наших PCB-партнеров считает толщину паяльной маски на сплошных участках меди 0.79 — 1.18 mil, на краях проводников 0.2 mil. Также данный производитель при расчете стека рекомендует не включать паяльную маску в расчет, так как при травлении внешних слоев происходит малейший перетрав (то есть увеличение значения импеданса), который маской компенсируется в номинал теоретического измерения импеданса внешних слоев без маски.

Это, кстати, хороший пример того, что при работе с данным производством — толщина трасс на вашей PCB будет меньше, чем заложено в рисунке печатной платы.

Итоги

Вот такие у нас внутренние рекомендации и правила, с которыми в обязательном порядке знакомим всех инженеров, проектирующих печатные платы. Надеюсь что данная статья будет полезна тем, кто рыщет по просторам интернета в поисках разрозненных рекомендаций и пытается угадать, как там получится в его конкретном изделии. Приглашаю делиться опытом в комментариях — будем рады дополнить свой. Если будет интерес, выложу ещё несколько подобных внутренних инструкций.

Комментарии (23)

dernuss

21.09.2017 16:35Жаль что все размеры в mills. Думаю многим сложно ориентироваться.

Я использую дифпары такие:

Скрытый текст

asmolenskiy Автор

21.09.2017 18:14Мы производим PCB на Тайване — они работают в mil.

Поэтому мы соответственно тоже.

Ну и в милах цифры ровные ).

Касательно Ваших пар:

Ваш калькулятор не учитывает EF — а оно порядка 5 Ом дельту дает. Ну и 3mil пары годятся для небольших трасс. Например от чипа до QSFP. Далеко их таскать я бы не рекоммендовал.

dernuss

22.09.2017 10:49Калькулятор для наглядности.

Далеко не таскаю, у меня просто плотность трассировки высокая.

asmolenskiy Автор

22.09.2017 11:22Не ну я же Вас ни в чем не обвиняю =)

Просто увидел у Вас 3mil — и предупредил на всякий случай.

Вдруг Вы захотите их через бакплэйн на пару метров протащить.

Мы тоже используем 3-4-3 иногда.

Но лично я люблю ровные 4-4-4 5-5-5 6-6-6 =).

Кстати к вопросу о мил/мм — видите какие числа ровные. В микронах это будет не так гламурно.

dernuss

22.09.2017 14:29Числа да, ровные. Но и у меня тоже нормальные, 75 мкм, 150 мкм. PCIe gen2 и SRIO работают. PCIe gen3 пока не было в проектах.

Просто почему то я не могу привыкнуть к английской системе. И наверное не я один.

asmolenskiy Автор

22.09.2017 14:39Да это вопрос практики. Кто с чем работает — то к тому и привык.

Начинаешь читать когда по взрослому про все вот это вот — там одни милы.

Главное не миксовать — типа делать дизайн в микронах, а производителю отдавать исходные данные в милах.

maxbrsw

21.09.2017 19:50И снова отличная статья! Правда сложилось мнение что это не просто систематизированные знания, а скорее результат не совсем приятного и удачного опыта работы с рядом азиатских производителей: сильно бросается в глаза то, насколько сильно вам приходится контролировать китайцев. Могу конечно ошибаться, но впечатление именно такое- нарабатывался иммунитет:)

Сразу к делу — вот о чём написано в этой статье

Имхо имело смысл также упомянуть про weave effect(weave pitch), CTE(z) из-за которого легко не попасть в IPC Class даже при качественных материалах(особенно если речь идет о Class 3 и выше), шероховатая vs гладкая фольга- да и все же тут специфика именно ваших борд: больших, жестких(т.е. не flex и/или комбо), со стандартными отверстиями(не HDI), без встроенных компонентов, без BGA/WCLSP с малым шагом и пр. Что разумеется нисколько не умаляет ценность статьи.

Наш совет: вот 105 Ом и укажите производителю PCB для контроля. Не стоить морочить ему голову разными Dk для разных частот на одном и том же слое.

Здесь по правде говоря сложно согласиться- те же 105 Ом при «обычном» разбросе в 10% легко могут стать головной болью в ряде дизайнов, и тут как раз стоит напрягать производителя: явно чисто китайская халтура, если такие моменты приходится столь пристально контролировать. Как пример (сугубо в рамках контекста) можно привести EU фабы типа AT&S, где сразу выделяют инженера который может все сделать при вас(расчеты/проверки) и его самого еще контролируют пару людей, или US фабы вроде TTM где для соответствующих борд может быть от 3 до 12+ человек. Соответственно подход совершенно другой и все сильно проще как в плане составления стека, так и процесса в целом, включая логистику: у хороших фабов есть все, даже экзотика- проблемы может быть только если внезапно нужно сделать очень большой выпуск, но это для серий уровня мажорных вендоров.

Наше мнение: лучше слабосвязанные — их проще выровнять по длине.

Правда не всегда есть место для них при определенной плотности соединений- специфично для конкретного дизайна.

Если будет интерес, выложу ещё несколько подобных внутренних инструкций.

Было бы очень интересно почитать.

asmolenskiy Автор

21.09.2017 19:55Здесь по правде говоря сложно согласиться- те же 105 Ом при «обычном» разбросе в 10% легко могут стать головной болью в ряде дизайнов

Я думаю те не верно уловил посыл.

Смысл такой — для себя родных мы считаем как надо — на 100 Ом в требуемой частоте.

Но если вендору написать — ты вот мне на этом слое (одном и том же) эти трассы так измерь, а эти эдак — будет боль и страдания.

Я пробовал: через стену «как это так у Вас разный Dk в одном и том же слое?» пройти очень тяжело. Хоть заобъясняйся что 100МГц клок и 7.5 ГГц дифпары в контексте Dk — это две большие разницы.

maxbrsw

21.09.2017 21:11Мне все же кажется что ляосяо халтурит- я когда делал борды с MMIC и обработкой/связью на быстрой цифре, такие моменты тоже всплывали- но производитель именно законтролил все моменты связанные с материалами. Долго моделировали в HFSS и Sigrity и по результатам было видно, что очень много можно получить проблем если упомянутые числа выйдут из под контроля, однако фаб(на тот момент это был TTM) не то что вошел в положение, а вроде еще своих SI инженеров выделил дополнительно, которые уже консультировали их коллег по заводу со стороны CAM подготовки и производства.

Насколько мне не изменяет память, в мире IC packaging на уровне субстрата под бга и всяких SiP(хайспидные конструкции) тоже «считают все числа», именно в контексте того уже уплыва Dk в рабочей полосе частот- это при том что там расстояния в порядки меньше чем на целевой борде.

asmolenskiy Автор

22.09.2017 13:00Ну учитывая что запуск одного шаттла IC — это мульен долларов минимум — тут совсем другие правила игры. Там стадия верификации дизайна порядка 1 года занимает.

maxbrsw

22.09.2017 13:19Ну да, долго и дорого- особенно если делается MCP. Наверняка люди еще какой-то внутренний софт юзают: взять хотя бы тепловое моделирование- thermal degradation/thermal derating не только же к конденсаторам относится. Когда смотрел на борды с 4мя зионами соединенных в crossbar, с «довесками» из стратиксов 10, в первую очередь удивлялся тому, как люди смогли везде учесть тепло, начиная с субстрата заканчивая самой бордой. Как там контролируют Dk и пр, во всех режимах эксплуатации, даже не знаю- небось в лоб перебирают все варианты.

mwambanatanga

22.09.2017 09:10Очень интересная статья, но я ничего не понял. Автор может возразить, что статья для специалистов и кому надо, те поймут. Но все же хотелось бы в общих чертах сперва понять, а потом решать, надо оно мне или нет.

asmolenskiy Автор

22.09.2017 09:19+1Ну Вы можете задать вопрос. Я разъясню.

Просто вот например в статье есть два словца — IL и RL. Это Insertion Loss и Return Loss — нормально рассказать что это — это по одной статье на слово.

К сожалению нельзя на пальцах объяснить то, чему люди учатся по несколько лет.

Статья действительно для специалистов — если бы мне кто-то принес такую методичку год назад — я бы сказал ему спасибо ). Поэтому мы решили что кому-то пригодится.

LampTester

22.09.2017 14:35Просто вот например в статье есть два словца — IL и RL. Это Insertion Loss и Return Loss — нормально рассказать что это — это по одной статье на слово.

К сожалению нельзя на пальцах объяснить то, чему люди учатся по несколько лет.

Я попробую для примера. Вот намеренно упрощенные определения. Ужмем несколько лет в две фразы. :)

Insertion Loss — параметр, показывающий, сколько энергии теряется на чем-то, включенном в линию передачи сигнала.

Return Loss — параметр, показывающий качество согласования линии с чем-то, включенным в нее.

asmolenskiy Автор

22.09.2017 14:37Ну если говорить строго — это S-параметры:

IL — это S21 — отношение мощности на выходе, к мощности на входе — то есть потери.

RL — это S11 — отношение отраженной мощности на входе к входной.

И сразу же надо дальше рассказывать что это такое.

LampTester

22.09.2017 15:04+1Да-да, дальше надо расписать на четыре доски уравнения для однородной линии передачи без потерь, после чего добить вычислениями с этой самой матрицей рассеяния. :) Так любят делать в наших институтах. Я, правда, этих выкладок уже не вспомню, хотя, вроде бы, сдавал.

Я просто к тому, что большинство понятий можно объяснить простыми словами. Не всегда это, конечно, даст возможность сразу применять их в полном объеме, но представление у слушателя создаст.

К слову, я не вижу смысла «дальше рассказывать, что это такое». Ну, разве только если читающий не заком с понятием электрической мощности и совсем не в курсе того, что энергия может отражаться, но это уже другая история. Как по мне, скажем, фраза «отношение мощности на выходе к мощности на входе» уже исчерпывающе объясняет смысл параметра. Тем не менее, в своей версии определений (см. выше) я сознательно отказался от терминов типа «мощность» — что такое энергия каждый понимает хотя бы интуитивно, потому так проще.

asmolenskiy Автор

22.09.2017 15:47Ну… сойдемся на том что цель иная.

Здесь много статьей в формате методички, которые непонятны простым интересующимся, но мне например помогают достаточно часто.

Вот — считайте что эта статья такая же. Не познавательно-кругозоро расширяющая — а для добавления в закладки тем, кто занимается печатными платами =). Для топологов/схемотехников тут общем-то ничего непонятного нет.

asmolenskiy Автор

22.09.2017 09:24Ну вообще в целом — ответить на коммент точечно проще тем писать статью. Требует меньше времени )

Спрашивайте.

schetilin

Эээ… А это для людей написано?

Дело в том, что подобные статьи могут читать люди весьма далекие от данной предметной области, так сказать в целях самообразования (ну интересно просто, а как это готовят). Но тут в одном предложении пришлось 1 раз серьезно напрячь мозг, и два раза слазить в Гугл. И так весь текст :(

Если возможно, поменьше используйте профессиональный сленг.

SemenovNV

Постараемся сбалансировать лексику в будущих публикациях. Посчитали, что даже если слова незнакомы, то из контекста должно быть понятно.

Но раз действительно у таких очень специализированных статей есть читатели из других предметных областей, то этот образовательный аспект будем тоже учитывать. Спасибо за замечание.

asmolenskiy Автор

Ну как сказать.

Людей весьма далеких темы должен отпугнуть сам заголовок.

Софтверные статьи например наполнены слэнгом, который я вообще не понимаю чуть более чем полностью.

Касательно слэнга.

Борд = board = печатная плата.

Фаб — это фабрика.

Мне показалось — что в общем-то эти слова и так понятны даже людям далеким от тематики.

Наверное я ошибся — прошу прощения.

schetilin

Могу дать хороший совет: Напишите статью (можно даже целую серию), с описанием вашей работы. Простым языком, с фото, забавными инцидентами, с какими трудностями сталкиваетесь и как их решаете. Не только техника, но и люди.

От желающих почитать отбою не будет.

SemenovNV

У нас есть один сотрудник, который как раз хочет написать статью про свою практику работы «переводчиком» между программистами и железячниками. Жду с нетерпением.