Предварительная подготовка

— Everyone please observe the fasten seat belt and no smoking signs have been turned on. Sit back and enjoy your ride.

Итак, по порядку.

Тестирование осуществляется на всех стадиях жизни аппаратуры. Тестирование бывает первоначальное (bringup), компонентное, функциональное, нагрузочное, производственное, и даже тестирование на заказчиках.

Еще на стадии разработки аппаратуры инженер думает о том, как он будет оживлять свое детище. Платы обсыпаются контрольными точками, отладочными коннекторами, перемычками, посадочными местами для запасных компонентов и прочим подобным. Совокупность возможностей для тестирования, заложенных в аппаратуру, называется DFT (Design for Testability). Плата, выпущенная в DFT фазе, может содержать в два раза больше компонентов, чем плата, вышедшая в тираж. Естественно, следуя принципу «работает – не трогай», потом ее никто не переделывает, и конечный потребитель недоуменно рассматривает пустующие посадочные места на материнской плате из магазина, придумывая различные конспирологические теории по поводу их предназначения.

Итак, забрали с фабрики наш борд – что делать дальше? Ну конечно же – воткнуть в розетку и выпустить из него весь белый дым.

— Everybody falls the first time.

Фотка из интернета, у нас жжёных плат не нашлось, но каюсь – иногда так и делается. На моей памяти есть давняя история, когда любопытный системный архитектор сидел и подбирал наугад, в какие разъёмы нужно воткнуть фазу, нейтраль и землю (ну вот не было у него времени заглянуть в схему), а рядом сидел разработчик и ловил бледного.

Но обычно всё происходит по-другому. Первая фаза тестирования – bringup (в народе «оживляш»).

Оживление Рождение

— Wake up, Neo...

Для bringup обычно изготавливается 3—5 образцов (в расчете на то, что как минимум два будут уничтожены в бреду дебага). Если в составе устройства есть дорогие чипы — на один из образцов они не устанавливаются. Фаб может предложить вам сэкономить на золоте — НИ В КОЕМ СЛУЧАЕ НЕ СОГЛАШАЙТЕСЬ (ну просто паять придется много и часто).

Плата без чипа — это первый кандидат на убой. На ней проверяются последовательность включения питания, сбросы, номиналы напряжений и прочее подобное. Потом такая плата является донором органов и/или полигоном для проверки всяческих гипотез. Также перед тем, как что-то включать, нужно обязательно:

- прозвонить землю-питание, там частенько есть КЗ;

- визуально осмотреть плату – там запросто бывает перепутана полярность конденсаторов, чипы стоят вверх ногами, присутствует стружка, с лёгкостью можно найти пассивные компоненты, которые оторвали;

- отдельно изучить – а не поставили ли вам на плату компоненты, которые вы просили не ставить (лайфхак: не делайте черную маску на первых сэмплах – на ней не видно установлены или нет чип-резисторы).

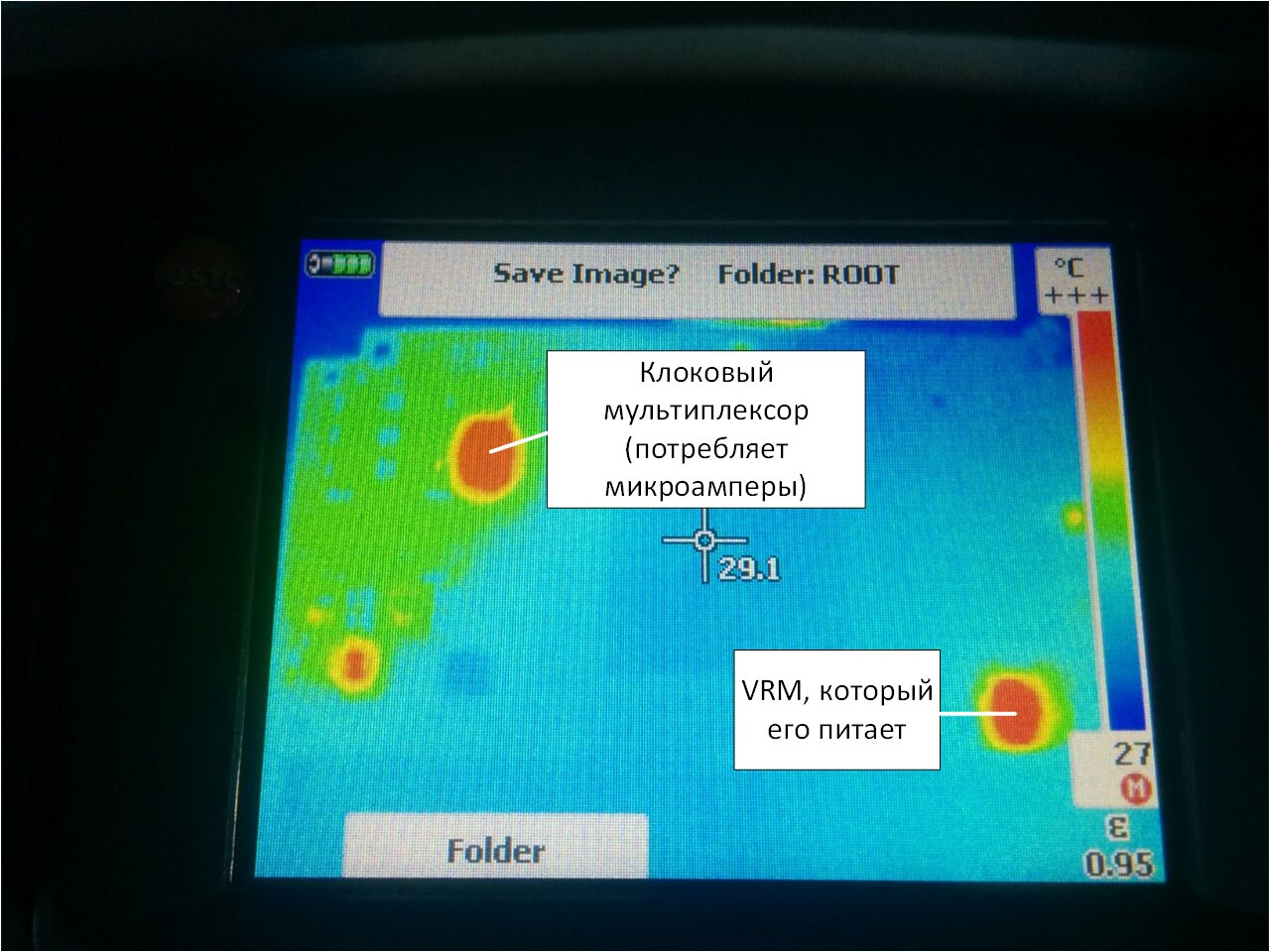

Наигрались с первой жертвой – идем пускать дым из боевой платы. При этом необходимо запастись пилотом с кнопкой отрубания питания и тепловизором. Пилот надо поставить под ногу, на случай если по рукам будет бить 220 В (ну или просто руки будут заняты), а в тепловизор можно увидеть КЗ.

Но вообще при самом первом включении обычно можно не бояться — оно скорее всего не включится, так как вы наверняка забыли перепаять компоненты, у которых в дизайне перепутаны ноги:

И еще припаять немножко проводов:

Термоклей — наше все, лучший друг разработчика, почти как скотч в обычной жизни.

Сразу после Дремеля:

И молотка, которым приходится забивать бонки в плату, — не всегда выходит аккуратно.

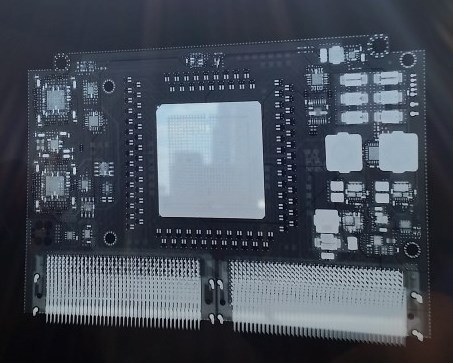

Иногда приходится делать пациенту рентген или томографию. Выглядит это так:

Отсканировать плёнку, оказывается, не очень просто. Сняли телефоном на просвет напротив окна.

Конкретно на этом снимке не видно ничего — не вглядывайтесь. Но вообще на рентгене можно увидеть непропай, трещины и прочее подобное.

Отдельно стоит сказать про bringup материнских плат, потому что делается он по-другому. DFT сэмплов матерей обычно заказывается много – порядка 20 штук. Стоит это дорого, поэтому тут своя стратегия.

Берутся разработчики и отправляются на фабрику. Собирается порядка 5 плат и конвейер останавливается. Далее у разработчиков есть порядка 30 минут, чтобы плату включить (для x86-систем критерий успеха — загрузить BIOS). Если всем повезло — собираются остальные образцы. Если нет — производство отменяется, а разработчики едут домой думать. Деньги затраченные на PCB — потеряны, зато компоненты ждут на складе следующей попытки.

Хорошо — мы запустили нашу плату, и даже запустили другие, которые должны работать вместе с ней. Что дальше? Собираем стенд.

И тут вы, наверное, ожидаете увидеть такое?

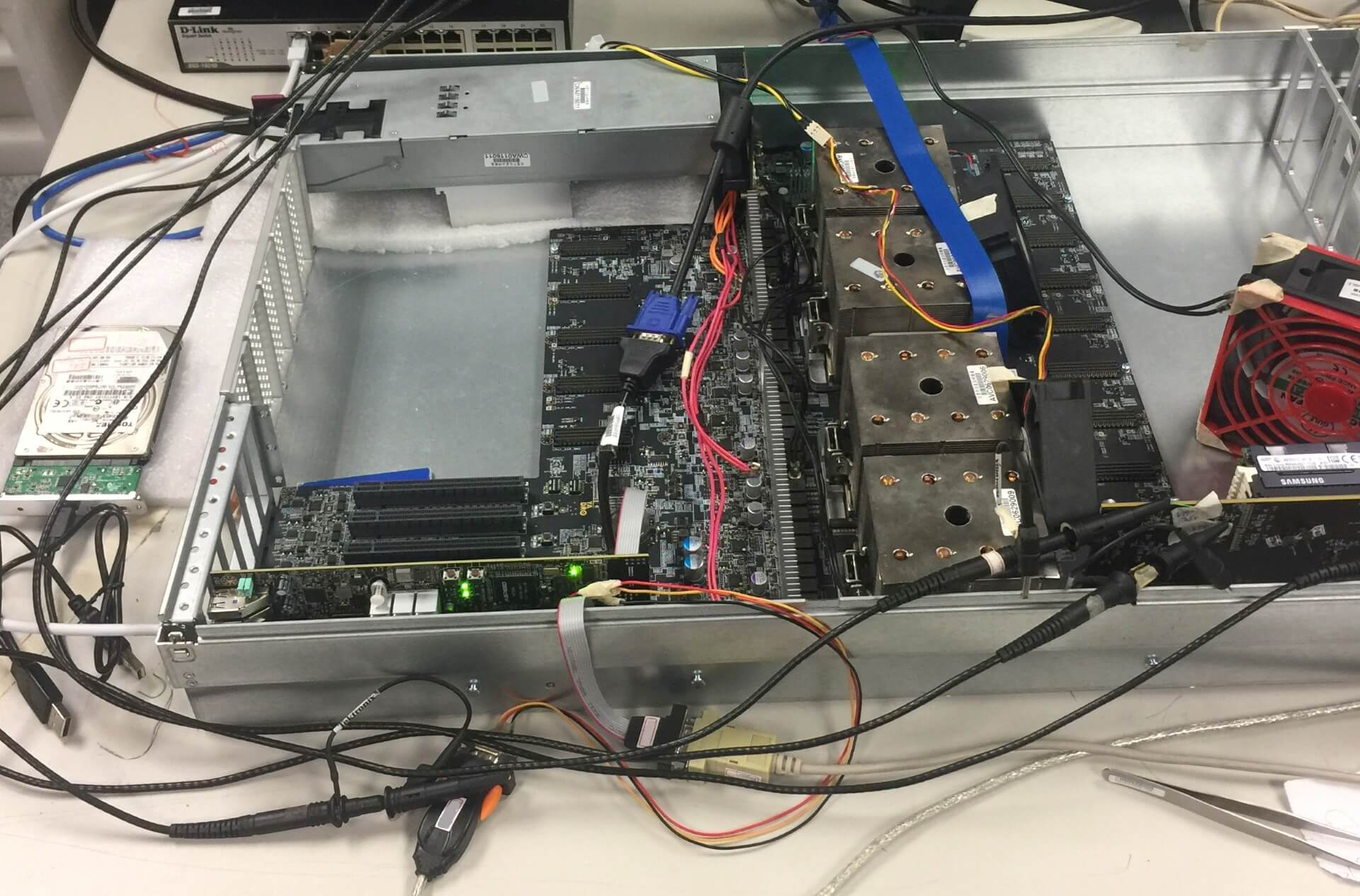

Это все показуха для замминистров. Настоящий стенд должен быть собран из палок и желудей, и выглядит так:

— I didn't say it would be easy, Neo. I just said it would be the truth.

(стакан для противовеса, фломастер — чтоб радиатор внатяг сидел — оно там проводом примотано)

Или так:

В лабораторию набивается вот такая орда:

И все начинают наперегонки зашивать свои прошивки, программки, и тыкать везде осциллографом.

Иногда в процессе то и дело раздается вежливая просьба «Дорогой коллега, пожалуйста, уберите паяльник от моей руки — уж очень горячо» или «Будьте так добры — больше не включайте источник питания, когда я привинчиваю плату к шасси».

Как гласит наш веб-сайт:

В нашем конкретном случае основная цель проверки совместной работы нескольких устройств — узнать, работает ли PCI Express, соответствует ли он стандарту. Просто без всего остального в принципе можно жить. Обычно функционал, закладываемый в железку, избыточен. Тонны GPIO выводов, I2C/SPI шин, термодатчиков, ледов и прочего, как правило, остаются невостребованными, так как их отладку откладывают на последний момент, который никогда не наступает.

Естественно, у нас нет на каждый случай жизни измерительной аппаратуры за несколько миллионов рублей — это для слабаков. Нам на помощь спешит тестовое ПО от производителей компонентов. Практически все современные чипы с высокоскоростными интерфейсами имеют внутри цифровой осциллограф. К нему полагается специализированное ПО, позволяющее считать его показания. Запускаем и смотрим глазковые диаграммы. Видим такое:

Иногда видим опасный прищур:

А иногда ловим кальмаров:

Кальмары — самые опасные. Это нелинейные искажения, и встроенные эквалайзеры с таким бороться особо не умеют. Кальмары означают, что где-то в канале связи есть что-то очень плохое — слишком длинное переходное отверстие, существенный перепад импеданса, попадание какой-то неравномерности в 1/4 или 1/2 длины волны каких-то гармоник в полезной полосе и прочее подобное.

Кто-то, возможно, заметит, что кальмар немного похож на то, что делает с принятым сигналом DFE в эквалайзере приемника PCIe. Но в данном случае это таки кальмар, а не результат работы DFE (просто результат работы DFE используемое нами ПО отображать не умеет).

Отдельно надо сказать про тестовый софт, который тоже бывает крайне коварным. Например для снимания глазковых диаграмм мы используем две версии одной и той же программы — одна версия рисует картинки, но не пишет значения раскрыва глаза, вторая — наоборот.

Ну и да — если вы планируете снимать глаза по интерфейсу I2C — забудьте, это будет очень очень очень медленно. Только in-band. Проблема в том, что для съема in-band у вашего устройства должен быть рабочий PCIe линк с компьютером, где работает тестовое ПО, что весьма проблематично, когда ваша железка не устанавливается в стандартный PCIe слот. И что самое забавное — у вас уже должен быть хоть как-то работающий линк на том канале, который вы отлаживаете, причем именно в том режиме (gen2/3) в котором вам нужно (ибо в разных режимах разные глаза и по разному работают эквалайзеры). Нет

Про то, как выкручиваться с PCIe — я ранее написал отдельную статью.

Вообще, при разработке сервера, конечно, очень важна поддержка со стороны производителей используемых компонентов, поскольку сегодня сложность даже относительно простых чипов такова, что без использования встроенных в них тестовых вещей полноценно проверить и отладить систему вряд ли получится. Тактовые генераторы, регуляторы напряжений, сетевые контроллеры, коммутаторы PCI Express, редрайверы – все это имеет встроенные средства для настройки, диагностики, и нуждается в определенном наборе программ и кабелей для подключения для полноценной настройки и тестирования, без использования которых разработка становится просто невозможной.

В процессе проведения проверок иногда выясняется, что где-то что-то идет не так. И тогда начинается увлекательный процесс локализации ошибки, чтобы ее можно было исправить в следующей ревизии. И хорошо если это «не так» стабильно повторяется – тогда выяснить, что именно является причиной ошибки, как правило, не составляет труда. Но иногда все гораздо хуже. Например, на некоторых экземплярах плат при длительном прогоне тестов возникают одиночные некорректируемые ошибки на шине (которых быть не должно совсем). И вот здесь зачастую уже приходится применять метод «пристального взгляда» — то есть просто сидеть, гипотетически глядя на схему предполагать, что именно может быть причиной, пробовать эту гипотетическую причину устранить в схеме, и тестами уже проверить – угадали мы или нет.

Мы с подобным сталкивались несколько лет назад, когда тесты NVIDIA (да, многие производители предоставляют специфические наборы тестов, которые позволяют проверить вещи, недоступные программным путем при использовании стандартных утилит) давали редкие одиночные ошибки при длительных (сутки и более) прогонах на некоторых экземплярах плат. Тогда все дело оказалось в неудачной трассировке референсного клока (100 MHz) — хотя прежде чем мы к этому пришли, проверено было много всего, начиная от качества питания и заканчивая глазковыми диаграммами по всем линиям.

И кстати, это хорошо. Самый большой кошмар разработчика — когда все работает сразу. Это значит только одно — где-то закопана мина, которая сработает после отгрузки 100500 единиц оборудования заказчику. Дело в том, что в процессе поиска причины какой-то глобальной проблемы осуществляется проверка нескольких гипотез и как правило выявляется множество мелких неисправностей, никак с возникшей проблемой не связанных. Нет большой проблемы — не найдёте маленьких. Их за вас найдут ваши заказчики.

Проверка по списку

— All I do is what he tells me to do.

После завершения компонентных тестов начинается функциональное тестирование – проверка работоспособности комплекса в целом и корректной работы всех заложенных функций. Обычно этим занимается QA. Простор для творчества здесь, конечно, весьма обширный, но в целом основной упор делается на корректную работу системы при проигрывании стандартных сценариев использования. Здесь обнаруженные ошибки могут уже иметь как аппаратную, так и программную природу, поэтому в первую очередь важно выяснить, что именно вызвало ошибку. Зачастую первые предположения могут быть обманчивыми, то есть явно аппаратная на первый взгляд проблема может быть вызвана некорректной работой встроенного ПО. Значительную часть в функциональном тестировании занимает проверка того, как система отрабатывает разнообразные ошибки, которые могут возникать в процессе работы. Современные отладочные средства позволяют осуществлять искусственную инжекцию ошибок в стандартные интерфейсы процессоров, потому что на уровне железа многие из них создать специально достаточно проблематично (ну не отрывать же на лету чипы памяти или замыкать линии шины PCI Express).

А… я же не сказал, что функциональное тестирование не означает собранную готовую к бою систему. Тут тоже бывает не все гладко. В какой-то момент оказалось что у нас нет в запасе OcuLink кабелей нужной длины, и у сервера появились кишки.

И почему-то вот в такой вот конфигурации при нагрузочном тесте все начало перегреваться. До сих гадаем — почему. Кабели грелись, наверное.

А два арбуза в каждой руке унести сможешь?

— You're faster than this. Don't think you are, know you are…

В какой-то момент параллельно с функциональным тестированием начинается тестирование нагрузочное — важно убедиться, что сервер продолжает корректно функционировать в предельных режимах работы. Причем нагрузочные тесты проводятся как применительно к отдельным подсистемам (диски, память, процессоры, ввод-вывод), так и на всей системе в целом. Как правило локализованные тесты позволяют сильнее нагрузить один конкретный модуль, чем это можно сделать при максимальной нагрузке на всю систему.

Кроме того, здесь помогают отладочные средства от производителя аппаратной платформы (например, Hardware Tests Executive от IBM). Таким образом можно загнать процессор в совсем предельные режимы, принципиально недостижимые при работе реальных приложений. Основные проблемы, выявляемые при нагрузочном тестировании – перегрев, нестабильность питания или перегрузка по максимальному току, ошибки при активной работе с интерфейсами ввода-вывода.

Также на помощь приходят бенчмарки. Потому что когда реальные значение бенчмарков сильно отличаются от прогнозируемых — значит что-то пошло не так. Хороший повод пойти потыкать плату палочкой.

На стадии тестирования мы используем в основном микробенчмарки:

Для процессоров это обычно однопоточные нагрузки, типа spec2006 (сейчас уже speccpu2017), parsec, но вообще их огромное количество от сборки ядра linux и компрессии (lzma, gzip), до перемножения матриц и вычисления быстрого преобразования Фурье (fftw).

Для памяти много лет ничего не меняется: STREAM, RAMspeed SMP, lmbench.

Для дисков: fio, iozone.

При успешном прохождении всех функциональных и нагрузочных тестов остаются еще ряд вещей, требующих проверки – стабильность работы во всем диапазоне температур, стойкость к вибрации, проверка совместимости с определенным набором стандартных компонентов (память, диски, PCI Express контроллеры).

P.S.: После того как мы на функциональных тестах первой ревизии сервера все проверили и обрадовались, у нас в лаборатории внезапно обвалилось три сервера. Мы начали проверять питание и на линии 1.2В (питание шины PCIe процессоров) увидели вот такое:

Акцентирую ваше внимание — одна клетка 500mV. Номинал 1.2 В. Резистором ошиблись в цепи компенсации одного из VRM. Вот с таким вот питанием были успешно пройдены все нагрузочные тесты, бенчмарки, прожарки и прочее подобное, и дизайн радостно поехал на вторую ревизию.

Так что, когда на Вашем уютном домашнем компьютере именитого бренда внезапно появляется экран смерти — не стоит думать, что это непременно «глючит винда».

Комментарии (46)

maxbrsw

10.08.2017 17:09+3Совершенно восхитительная статья, а конкретно вот этот текст:

Самый большой кошмар разработчика — когда все работает сразу. Это значит только одно — где-то закопана мина, которая сработает после отгрузки 100500 единиц оборудования заказчику. Дело в том, что в процессе поиска причины какой-то глобальной проблемы осуществляется проверка нескольких гипотез и как правило выявляется множество мелких неисправностей, никак с возникшей проблемой не связанных. Нет большой проблемы — не найдёте маленьких. Их за вас найдут ваши заказчики.

нужно сразу в золотую рамку. Вообще, вызывает неподдельное уважение тот факт что у Вас происходит именно серьезный технический анализ проблемы, а не бессмысленные и беспощадные гадания(с периодическим заходом в антинаучные гипотезы)- как это часто происходит в хардварных командах.

По Dfx позвольте спросить:

— часто вообще сталкиваетесь с неправильной ориентацией компонента и отчего идет ошибка(схема или завод)?

— часто сталкиваетесь с проблемами на уровне футпринта?

Ну и вопрос из области чистого любопытства- много смотрел серверных дизайнов на OCP, очень интересно было сравнить разводку памяти между Xeon и POWER, в том смысле что у последнего все выведено на отдельный контроллер Centaur: правильно ли я понимаю, что в случае POWER разводка более трудоемкая как из-за организации включения так и пинаута камня? У тех же Xeon очень оптимизированный пинаут, и чтобы развести много планок не требуется запредельного числа слоев- так ли это?

asmolenskiy Автор

10.08.2017 17:17+3Привет, Максим.

По DFX:

— Ну как часто… бывает. Я не скажу что прям всегда — но первое что мы проверяем когда что-то не запустилось — это первые пины. Вот не далее как месяц назад пришла партия плат на одной из которых квадратный микроконтроллер был повернут на 90 градусов. В чистом виде ошибка фаба.

— Касательно ошибок в схеме и футпринтов — у нас максимальный re-use. Мы стараемся брать не то что компоненты, которые уже применены нами — а целые куски схем из девайса в девайс таскаем. Иногда даже в ущерб оптимизации. У нас пожалуй разнообразия в платах больше, чем в схемах которые на них реализованы. Так что со временем количество таких ошибок минимизируется. Косячки в футпринтах бывают часто — но благо наши PCBA партнеры очень глазастые и внимательно отсматривают наши гербер и ассембли файлы.

Касательно твоего второго вопроса.

Сказать что при проектировании Кентавра IBM вообще не думал о разводке его на плате — это вообще ничего не сказать. У Intel с этим делом все гораздо лучше. Это правда.

maxbrsw

10.08.2017 18:24Привет, Антон- и большое спасибо за развернутый ответ. Ну, в случае серверных борд re-use наверное более чем оправдан: даже чисто по-человечески страшновато каждый раз делать все from-sсratch, тем более для дизайнов такого уровня, к тому же жалко не использовать хорошие куски. С футпринтами интересно весьма- я в своих задачах получал в основном негативные фидбеки при использовании manufacturer recommended footprint для нестандартных корпусов как на картинке, пока не начал делать все с нуля включая 3д модели:

В серверах много используются всякие powerstage, drmos и т.п. для организации многофазных POL DC/DC, типа SiC645- у вас бывали проблемы с такими корпусами?

С кентавром стало яснее, пинаут у него конечно страшный но мне кажется, что по-настоящему этот момент заиграл бы если сразу распаивались микросхемы на плату, а не сокеты под модули: с зионом(и заодно 10 стратиксами) судя по всему особых проблем быть не должно- смотрю на примерно такие платы

А с кентавром наверное будет пот, даже не могу представить разводку. С ним вообще бывают memory-down дизайны? Почему привел эти картинки: интересно узнать субъективное мнение- в своих платах я воюю за каждый мм, кладу меандры и проводники без «пустых островов»(~99% использование пространства) и когда вижу разводку зиона, и тем более с модулями памяти, то сразу заведую белой завистью. Сложилось впечатление что в случае кентавра, особенно когда он не один на плате, разводка может и не супер сложная, но очень и очень трудоемкая из-за неудачного пинаута- это так?

maxbrsw

10.08.2017 19:39И вдогонку вопрос- в твоем посте посте упомянуто что:

наши PCBA партнеры очень глазастые и внимательно отсматривают наши гербер и ассембли файлы.

Неужели такие платы в герберах отправляете? В смысле, почему не ODB++ и/или другие(новые) форматы?

asmolenskiy Автор

10.08.2017 19:44+1Ну я не знаю как твои китайцы, а наши китайцы всякие такие новомодные штуки — не понимают =)

maxbrsw

10.08.2017 19:55:) Наверное какие-то привередливые китайцы- в Азии часто встречал проблемы с принятием тех же Gerber X2(которые крайне удобны для HDI плат в сравнении с обычными герберами), а ODB++ никогда не вызывал вопросов, формат весьма зрелый же. Но вполне допускаю что скорее всего здесь многого не знаю, т.к. по больше части дизайню под EU/US заводы- полагаю в то же самое время, борды как у вас наверное делает кто-то уровня фокскона с пегатроном со своими правилами и хотелками.

asmolenskiy Автор

10.08.2017 20:03Да нет. С точки зрения технологичности у нас достаточно обыденные борды.

Мы ж не айфоны делаем.

Я думаю их почти все можно в России сделать с технической точки зрения.

У нас есть одна мрачная, но ее мрачность заключается исключительно и только в длине 700мм — мало у кого помещается такая заготовка и проблемы с пайкой (ее коробит) и со сверлением — на длине точность уезжает.

maxbrsw

10.08.2017 20:24Понятно- ну с длинными бордами ситуация ожидаема вполне, да и наверное логично при таких вводных предполагать проблемы также с backdrill на слабых фабах. По поводу пайки, вы когда-нибудь делали LGA(сокетные) to BGA conversion? Понятно что на особо теплых компонентах в этом, пожалуй, смысла нет, но просто интересно: видел как зионы те же так переделывают под rugged серверы.

asmolenskiy Автор

10.08.2017 19:49Насчет memory-down.

Без поддержки IBM — memory-down тебе гарантирован.

А если с точки зрения работоспособности в целом — Кентавр не умеет делать Degrade скорости ни по своей последовательной шине 9.6 GT, ни по собственно DDR4 1600. То есть если на данных скоростях оно не поднимется — то опустить частоту чтобы хоть как-то что-то заработало — не получится. Пан или пропал.

Касательно сложности разводки при распаянных чипах — не могу сказать, мы ж его так не разводили.

maxbrsw

10.08.2017 20:01Сложно представить POWER-based дизайн без поддержки IBM, разве что есть какое-то ограничение на «элитность» в духе разделение Tier 1/2/3, но в целом ситуация понятна- даже странно что у отдельного контроллера есть такие ограничения. Даташита на кентавр у меня разумеется нет, но предполагал что он невероятно интеллектуальный- м.б. может даже перекидывать адреса как удобно(в духе Nvidia Tegra K1 например или круче). Но наверное проще таки заручиться поддержкой чем потеть с memory-down в случае с кентавром.

asmolenskiy Автор

10.08.2017 19:51В серверах много используются всякие powerstage, drmos и т.п. для организации многофазных POL DC/DC, типа SiC645- у вас бывали проблемы с такими корпусами?

Пока нет — но я боюсь их как огня если честно.

maxbrsw

10.08.2017 19:56А почему если не секрет? Классные приборы вроде и удобно.

asmolenskiy Автор

10.08.2017 20:00А ты пойди его реворкни, если ошибешься.

Или руками перепаяй.

maxbrsw

10.08.2017 20:14Насчет реворка 100% соглашусь- тут проводками не наиграешься особенно, но именно в части перепайки коллеги сообщали о проблемах только в случае конкретно больших и мощных SIP, вроде ISL8272 или EM2130L01QI

Вообще, как например в случае с RF фронтендами, часто делаю отдельную тестовую плату с целевой разводкой под POL DC/DC- ее прогоняли, а потом ставили в целевую борду: и то, по большей части чтобы проверить футпринт- производители довольно часто допускают ошибки в чертежах на корпус. Но разумеется и в плане чисто электрических тестов это очень сподручно.

ukt

10.08.2017 20:55Расскажите, пожалуйста, про глазковую диаграмму.

Как определить хорошую от плохой.

Я задним умом понимаю, что смотрятся передние и задние фронты, поэтому получается «глаз».

Но вдруг, есть что то новое.

asmolenskiy Автор

10.08.2017 21:01+1Ну если совсем на пальцах — то существует так называемая Compliance Mask. Это ромбик который врисосывается в центр глаза. Точнее даже не в центр глаза — а в точку захвата приемником. Если глаз наползает на ромб — fail, не наползает — pass.

А сам глаз получается посредством прогона в канале PRBS последовательности которая нарезается по три бита и все эти кучки по 3 бита друг на друга накладываются. PRBS формируется таким образом что в ней происходит перебор все-возможных переходов от 000 до 111 в разных комбинациях.

asmolenskiy Автор

10.08.2017 22:53+2Кстати на иллюстрациях в статье это на самом деле не глазковая диаграмма в классическом понимании. Потому что внутри чипа конечно нет никакого осциллографа в традиционном понимании. Это графическое отображение интенсивности ошибок при сдвиге точки захвата приемника в системе координат напряжение/время. Фигурально выражаясь — он двигает прицелом и смотрит есть ошибки приема или нет. Темно синяя зона — это 0 ошибок. То есть это некий допуск приемника в пределах которого он может гулять.

Но по сути — та же глазковая диаграмма.

maxbrsw

10.08.2017 21:28Я наверное уже основательно достал своими вопросами :), но осмелюсь спросить еще- как на таких платах дезигнаторы на шелкографии ставите? Руки, скрипты, CAM редактор, другое?

asmolenskiy Автор

10.08.2017 22:35Спрашивай — не жалко.

Автосилк + руки.

Ну то есть это я так думаю что наши топологи в основном именно так и делают.

Но так как я сам в нашей компании платы не развожу и в процесс расстановки шелкографии особо не лезу — то вполне допускаю, что они делают не совсем так.

maxbrsw

10.08.2017 23:54Спрашивай — не жалко.

Спасибо=) Ну, раз добро получено, хочу поинтересоваться(именно с оглядкой на серверную тематику)- пользуетесь ли и как часто следующими вещами:

— выравнивание паттерном trombone и особенно его разновидностью под названием switchback

— разводка под произвольным углом(не зигзаги), в т.ч. с дугами

— snake routing для бга с выводами в шахматном порядке

— торцевая металлизация плат (особенно жирных, бэкплейны не в счет)

— broadside coupled пары

— differential coplanar пары(связь с окружающей землей на том же слое)

— active/passive line conditioner для отдельных хайспидов

— индуктивности с дополнительным экранированием в питании

— конденсаторы с реверсированным корпусом(электрод по длинной стороне) и 3х выводные

Заодно интересно, какие задачи решаете с помощью Tag-Connect- понятно что дебаг, но что именно отлаживается?

asmolenskiy Автор

11.08.2017 01:50— тромбон/аккордион — используем конечно, про switchback впервые слышу

— 11 градусов — да, арки нет. В одном проекте только были, c 12.5 GHz сердесами. Арки слайдить муторно.

— snake routing — да

— торцевую металлизацию не делаем. Мы не отводим тепло в торцы платы. А про чудодейственное улучшение ЭМС металлизацией торцев — ИМХО миф.

Все остальное по списку — нет.

Tag-Connect мы цепляем к Aadvark. А с этим девайсом добрая половина I2C дебажного софта работает.

maxbrsw

11.08.2017 02:27тромбон/аккордион — используем конечно, про switchback впервые слышу

С аккордеоном понятно- его все используют. Switchback, это как бы «однократный тромбон»- с ним очень легко накрутить много длины если большой разбег в матчгруппе, в то же время с ним проще всего облажаться при тюнинге в плотном дизайне.

11 градусов — да, арки нет. В одном проекте только были, c 12.5 GHz сердесами. Арки слайдить муторно.

Арки слайдить конечно сложнее чем прямые- я сам чаще обычно скругляю уже разведенное: это гораздо проще. Примечательно что почти все платы которые смотрел с ОСР были именно с разводкой под произвольным углом- поэтому стало любопытно.

торцевую металлизацию не делаем. Мы не отводим тепло в торцы платы. А про чудодейственное улучшение ЭМС металлизацией торцев — ИМХО миф.

Склоняюсь к мнению что эта технология несколько переоцененная в ряде случаев, но она точно небесполезна, в т.ч. с точки зрения того же ЭМС. Скорее ее «сила» не такая большая как некоторые ожидают(чудо-таблетка).

А используют ли в POWER-based серверах HMC?

asmolenskiy Автор

11.08.2017 02:44+1Switchback, это как бы «однократный тромбон»- с ним очень легко накрутить много длины если большой разбег в матчгруппе, в то же время с ним проще всего облажаться при тюнинге в плотном дизайне.

Вот эту хрень, которая Switchback — мы используем постоянно. Но я не знал что она так называется.

Тромбон и тромбон…

Арки слайдить конечно сложнее чем прямые- я сам чаще обычно скругляю уже разведенное: это гораздо проще.

Скругление углов… — ну вообще сам же понимаешь что это марафет. В полосе до 10GHz — ничего не дает. Только лишнюю головную боль.

Про произвольный угол — ну вообще мы хотели просить PCB Shop просто поворачивать заготовку на 11 градусов. Но потом поняли что проконтролировать мы его не сможем. Он отрежет прямо, а денег возьмет как будто повернул и пол-заготовки выкинул. Поэтому — иногда да, упарываемся зигзагом под 11 градусов когда тянуть далеко надо. Там Fiberwave эффект уже по настоящему начинает влиять. Причем не только на Skew Match но и на Lane-Lane match.

Склоняюсь к мнение что эта технология несколько переоцененная в ряде случаев, но она точно небесполезна, в т.ч. с точки зрения того же ЭМС. Скорее ее «сила» не такая большая как некоторые ожидают(чудо-таблетка).

Хочешь тихие торцы — сделай питание уже опорной земли диэлектриков на 7-10. Этого достаточно.

А используют ли в POWER-based серверах HMC?

По перспективным технологиям у нас Алексей эксперт — может ответит позже.

maxbrsw

11.08.2017 03:11Вот эту хрень, которая Switchback — мы используем постоянно. Но я не знал что она так называется.

Тромбон и тромбон…

Тут видимо я ввел тебя в заблуждение формулировкой- просто привык что классический тромбон, это просто «перевернутый» аккордеон, а свичбэк всегда в 1 «виток» и может уже следовать по траектории проводника с изломами.

Скругление углов… — ну вообще сам же понимаешь что это марафет. В полосе до 10GHz — ничего не дает. Только лишнюю головную боль.

Да, разумеется- хотя часто использую там где не получается сохранить минимальную длину 45гр сегментов(т.е. где выходит сильно меньше скажем 1.5х ширины трассы).

Про произвольный угол — ну вообще мы хотели просить PCB Shop просто поворачивать заготовку на 11 градусов. Но потом поняли что проконтролировать мы его не сможем. Он отрежет прямо, а денег возьмет как будто повернул и пол-заготовки выкинул. Поэтому — иногда да, упарываемся зигзагом под 11 градусов когда тянуть далеко надо. Там Fiberwave эффект уже по настоящему начинает влиять. Причем не только на Skew Match но и на Lane-Lane match.

Ну тут я не понимаю немного- а откуда именно это значение, 11гр? Про борьбу с влиянием струтуры диэлектрика разумеется знаю из первых рук :), но история именно про полностью произвольные углы, например:

— Xeon to Xeon

— POWER to POWER

Хочешь тихие торцы — сделай питание уже опорной земли диэлектриков на 7-10. Этого достаточно.

Всегда бы места столько было:) Но тут больше интересно улучшение земли, особенно в RF бордах(почти всегда в них использовал), да и в HDI с BGA/WLCSP на краях тоже часто нет возможности убирать края плейнов питания внутрь.

По перспективным технологиям у нас Алексей эксперт — может ответит позже.

Весьма интересно было бы послушать.

asmolenskiy Автор

11.08.2017 09:17+1Ну тут я не понимаю немного- а откуда именно это значение, 11гр?

Я думаю кто-то, детально знающий параметры стеклотекстолита сел и посчитал какой угол будет наиболее оптимальным чтобы трасса статистически поровну находилась и в стекле и в смоле.

Это ИМХО.

Paging

11.08.2017 03:24HMC пока удел сильно специфического железа, то есть там, где реально это нужно — дорого же очень…

maxbrsw

11.08.2017 03:51Спасибо за пояснение- а если не секрет, HMC подсоединяется напрямую или через какой-то контроллер, вроде того же кентавра? У HMC весьма удобный пинаут и вывод сигналов, но наверное это будет нивелироваться пинаутом POWER/контроллера?

Paging

11.08.2017 03:53У HMC же вообще свой интерфейс, ничего общего с DDR4 не имеющий, а значит требуется его поддержка со стороны хоста. Из популярных вычислительных платформ ее нет, насколько я знаю, ни у кого. Под FPGA — да, есть IP-ядра, но это логично. Вроде как она поддерживается еще в каких-то чипах быстрых сетевых свичей, но тут я точно не скажу — не занимался этим.

maxbrsw

11.08.2017 04:04Ну да, там диффпары одни(правда очень много)- с фпга его соединить конечно не проблема, связь через GTX если не изменяет память. Но в случае POWER я не знаю почти ничего, но может есть какие-то платы расширения с HMC специально под серверы или отдельные дизайны.

robert_ayrapetyan

11.08.2017 00:00А можно для совсем непосвященных — кто является клиентами и откуда вообще берется все это железо?

asmolenskiy Автор

11.08.2017 01:54+1Про клиентов я говорить не буду — у меня нет на это полномочий. Да я и не знаю особо, если честно.

А вопрос про происхождение железа — я не понял.

robert_ayrapetyan

11.08.2017 02:12Ну в моем мирке все должно тестироваться производителем. Но судя по рассказу, вы не производите железо, вам его привозят (разное, от обычных материнских плат до каких-то кастомных железяк), причем какие-то опытные образцы… Вы в России? Кто-то производит материснские платы и собирает кастомные сервера? Расскажите об этом.

asmolenskiy Автор

11.08.2017 02:25+1А, понятно.

Вам просто надо было прочитать все рассказы ))).

Железо мы разрабатываем по большей части — сами.

Я сначала хотел написать и расписать что мы делаем, но потом решил, что возможно завтра кто-нибудь из маркетинг-людей скажет это более правильными словами.

Сходите к нам на сайт www.yadro.com — там в принципе уже есть достаточно информации (его таки запустили).

SemenovNV

11.08.2017 09:25+1Мы в России. Разрабатываем сами архитектуру, печатные платы, корпуса, встроенное ПО для своих продуктов. Микросхемы и стандартные базовые компоненты (вентиляторы, блоки питания, диски, планки памяти) не делаем. По собственным изделиям, можно сказать, делаем всё, кроме непосредственно изготовления. Распространённая fabless-модель, по которой работает большинство производителей вычислительных систем.

Сборочное производство у нас тоже есть своё, в России. Кстати, одно из единичных в мире, сертифицированных по стандартам IBM — в новостях есть об этом упоминания.

Имена заказчиков я пока не могу называть — стандартной практикой раскрытия информации о поставках является публикация пресс-релиза совместно с заказчиком. В своё время сообщим.

Про некоторые разработки мы писали в этом блоге — можно почитать про архитектуру сервера в целом, технологию вывода PCIe наружу через кабели и отладку её технической реализации, плату управления сервером. Писали также про OpenBMC применительно к OpenPOWER, и вот совсем недавно — про первые тесты дисковой подсистемы сервера.

Что касается тестов железа, то часть проверок делается сразу на фабрике, детальное тестирование проходит у нас в лаборатории. Тут надо ещё на всякий случай сказать, если вдруг не вполне очевидно, что в этой статье Антон описал процесс тестирования изделий, ещё не вышедших в серийное производство. Опытных образцов, как правило первой ревизии, когда надо не только проверить соответствие произведённого изделия проекту, — но и выявить на практике, что в проекте надо улучшить или исправить до выпуска изделия в серию.

Контроль качества изготовления серийной продукции — отдельная большая тема.

D_EL

11.08.2017 01:37

В том году разрабатывал одноплатник на IMX6DL. Видео на борту не требовалось, поэтому я не подключал модуль LVDS к питанию. Потом оказалось что от этой ноги питается контроллер DDR.

Вытянул проволоку с советского реле РЭС49 и припаял паяльником.

В итоге все заработало.

P.S. Паял в самопальной печи)

asmolenskiy Автор

11.08.2017 01:59+1Это пример одной из двух крайностей.

Первая — это когда на каждый вывод питания вешают 100500 разномастных декапов и фильтров.

Второй — когда контроллер DDR запитывают проволокой.

Нормально =).

Мы сейчас пытаем борд (на рентгене который нарисован) — у него на Backplane коннекторе куда-то пропали контакты. Заводской брак. Причем на разных платах разные. Где-то клока нет, где-то неизвестно чего пока нет.

Так и живем.

D_EL

13.08.2017 20:24Я запитал только логику, там потребление тока — единицы микроампер.

Драйвера физического уровня нормально подключены.

EFG

11.08.2017 09:18Вопрос не совсем в тему конкретно этой статьи, но тем не менее интересно используются ли глухие переходные отверстия на вашей материнской плате? Если можно поподробнее о глубине/диаметре, допустимых токах и других нюансах глухих отверстий.

asmolenskiy Автор

11.08.2017 09:23+1Мы делали вариант дизайна с глухими отверстиями, но по-моему в производство мы его так и не отправили, потому что железка заработала и так. Там были проблемы с хвостами переходных отверстий, а бакдрилл не влезал из-за того, что к нему полагаются серьезные антипады.

Но в общем и целом — нет не используем, почему-то так получается, что там где у нас обычно проблемы с разводкой — они не спасают. Так что мне Вам особо и рассказать тут нечего.

murz165

Отличная статья с хорошим юмором! У вас тестовые точки используются только для припайки проводов и для щупов осциллографов или вы используете игольчатые поля?

asmolenskiy Автор

Спасибо, мы старались чтоб было не скучно.

Это контрольные точки для разработчиков, а не для игольчатых полей. В основном мы их ставим на все цепи Power Sequence, на все напряжения питания, на сбросы и на клоки.