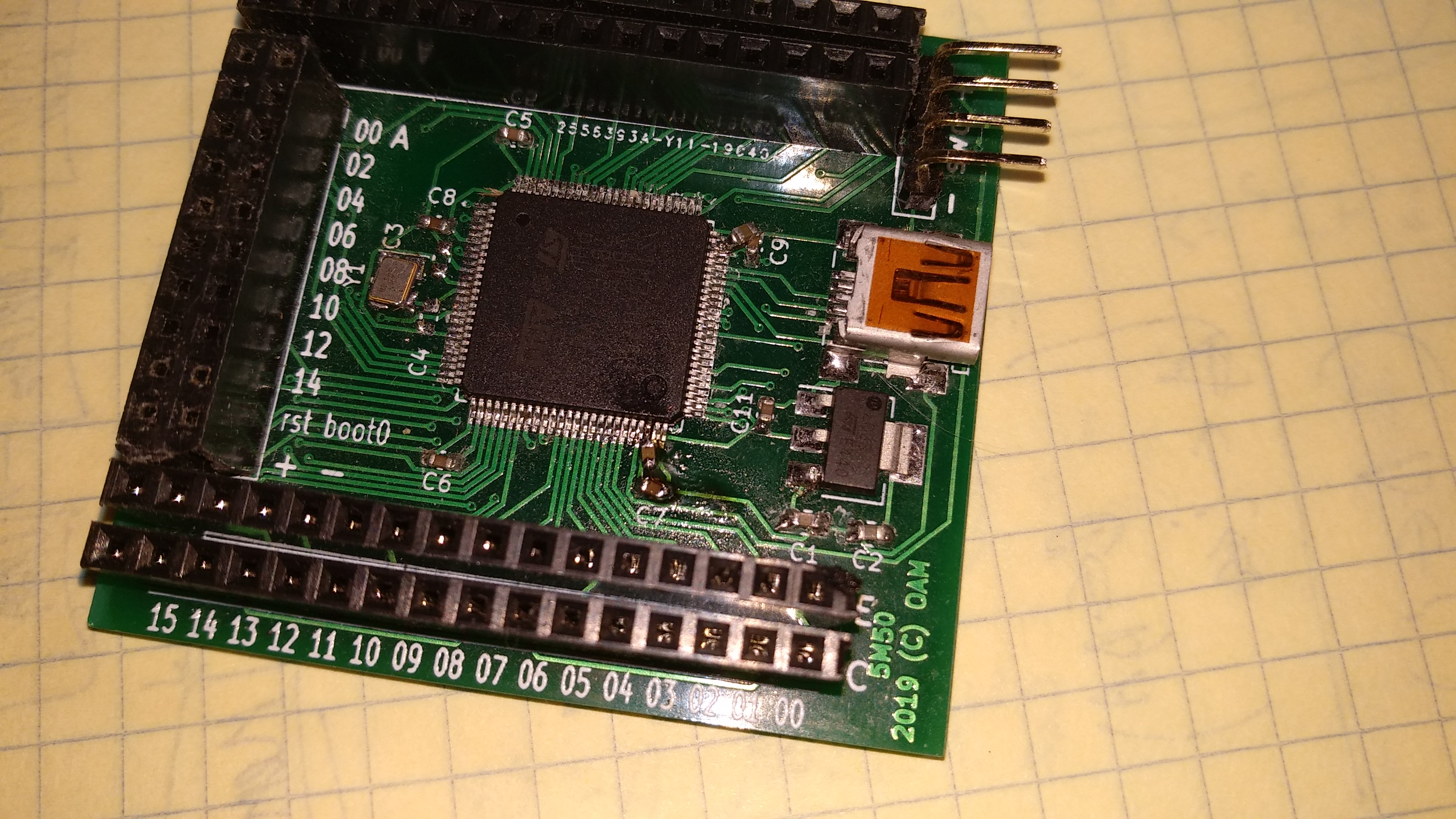

На КДПВ — герой нашего романа — он смог читать данные на такой скорости!

Итак, мой очередной проект потребовал читать поток данных вида 32-бита на скорости 50 МГц (это и будет, кстати, тот самый 1.6 Gbps) в количестве заранее известном — пусть будет 10000. Было бы просто отлично читать сразу с помощью DMA из одного порта — но вот, к сожалению, подходящих процессоров не нашлось (надеюсь, в комментариях это дело кто-нибудь поправит), у всех подходящих по скорости порты почему-то 16-битные.

Но такая мелочь нас не остановит — будем читать из двух портов сразу! Правда, это в общем случае не всегда удастся делать с нужной степенью контроля и синхронности, но в нашем случае все не так печально — есть сигнал, после которого 20 ns данные будут на порту держаться.

А так как процессор у нас — stm32h750 на 400 Мгц, а шина и таймеры на 200 Мгц, то все должно получиться.

Казалось бы простой случай — по сигналу запускать одну пересылку DMA. Но вот только у DMA нет такой возможности — порт может выдать прерывание, но не может управлять DMA. Но зато у нашего процессора есть хорошая штука — DMAMUX, в котором есть генератор событий для канала DMA, а вот в этом генераторе есть две подходящие возможности — или использовать прерывание EXTIT0 или сигнал от таймера TIM12 (такая вот странная фантазия была у разработчиков чипа).

По прерыванию мы не успеем по времени — на даже пустую отработку нужно порядка 47 тактов, а такт у нас — 2.5 ns…

Зато успеем по таймеру. Осталось только затактировать таймер от внешнего сигнала в 100 МГц, причем длину таймера ставим в 1 и по его выходу TRGO будет срабатывать генератор DMAMUX, а уж он-то задаст команду на пересылку DMA и тот прочитает порт и перешлет данные в память.

Но стоп! Порт-то 16-бит, а у нас 32… Что же, можно попробовать читать еще второй порт… Только вот для этого нужен второй канал DMA, и еще это займет ту же шину — то есть прочитать-то мы успеем, но вот можем не успеть записать данные в память. Что-же, теоретически, у этого процессора есть разные типы памяти, и на большом рисунке структуры процессора можно видеть, что и DMA и память RAM_D1 сидят на одной и той-же шине с частотой 200 МГц. Осталось проверить практически.

DMA1->LIFCR |= ~0;

DMA1_Stream0->CR = (0b11 << DMA_SxCR_PL_Pos) | (0b01 << DMA_SxCR_MSIZE_Pos)

| (0b01 << DMA_SxCR_PSIZE_Pos) | DMA_SxCR_MINC;

DMA1_Stream0->M0AR = (uint32_t) data;

DMA1_Stream0->PAR = (uint32_t) &(GPIOE->IDR);

DMA1_Stream0->NDTR = 10000;

DMA1_Stream1->CR = (0b11 << DMA_SxCR_PL_Pos) | (0b01 << DMA_SxCR_MSIZE_Pos)

| (0b01 << DMA_SxCR_PSIZE_Pos) | DMA_SxCR_MINC;

DMA1_Stream1->M0AR = (uint32_t) data2;

DMA1_Stream1->PAR = (uint32_t) &(GPIOD->IDR);

DMA1_Stream1->NDTR = 10000;

DMAMUX1_Channel0->CCR = DMAMUX_CxCR_EGE | (1);

DMAMUX1_Channel1->CCR = DMAMUX_CxCR_EGE | (2);

DMAMUX1_RequestGenerator0->RGCR = DMAMUX_RGxCR_GE

| (0b01 << DMAMUX_RGxCR_GPOL_Pos) | (7);

DMAMUX1_RequestGenerator1->RGCR = DMAMUX_RGxCR_GE

| (0b01 << DMAMUX_RGxCR_GPOL_Pos) | (7);

DMA1_Stream0->CR |= DMA_SxCR_EN;

DMA1_Stream1->CR |= DMA_SxCR_EN;

TIM12->CNT = 0;

TIM12->CCMR1 |= TIM_CCMR1_CC2S_0;

TIM12->CR2 = (0b010 << TIM_CR2_MMS_Pos);

TIM12->CR1 |= TIM_CR1_CEN;

while (DMA1_Stream0->NDTR)

i++;

TIM12->CR1 &= ~TIM_CR1_CEN;

Ну и конечно, надо разместить массивы data и data2 в нужном сегменте памяти, это делается так:

__attribute__((section(".dma_buffer"))) uint16_t data[10240],data2[10240];

а в файле для линковщика указываем:

.dma_buffer : {

*(.dma_buffer)

} >RAM_D1

Для проверки, ну и как первый вариант, был реализован просто тупое копирование с помощью

центрального процессора (все же 400 МГц):

uint16_t * ptr = cpudata;

volatile uint16_t * src = &(GPIOE->IDR);

volatile uint16_t * src2 = &(GPIOD->IDR);

for (register int i = 0; i < 10000; i++) {

*ptr++ = *src;

*ptr++ = *src2;

}

Для проверки данные cpudata размещались в разной памяти, быстрее всего подошла (ну она, правда, всего 64К) сверхбыстрая память (тоже 400 МГц) DTCMRAM.

Результаты

В процессе испытаний выяснилось, что с помощью CPU можно читать на скорости 12.5 МГц из двух портов. И 25 МГц из одного. Так что вариант не работает…

С помощью DMA и

Так что в моем (немного вырожденном) случае, удалось достигнуть скорости передачи информации в процессор stm32h750 на скорости 32x50 = 1600 Mbps.

Комментарии (116)

IgorPie

14.09.2019 19:20+1Получилось и отлично, но сразу возникает вопрос о синхронизации таймера на 100МГц с входящим сигналом (да, занудничаю). А если его нет, то рано или поздно данные разъедутся как в детстве показывали по телевизору другой телевизо и плыла полоса кадра, пол кадра были старыми и пол кадра — новыми.

И оффтоп, куда столько данных, у H750 мегабайт ОЗУ, если по сусекам поскрести?

oam2oam Автор

14.09.2019 19:26+1я, наверно, не очень подробно описал окружение — дело тут в том, что сигнал 100 МГц и тактирование самого процессора — синхронные. Да, есть, конечно, вероятность сбоя, но, во-первых, сам характер данных таков, что можно (иногда) и пропустить что-то, а, во-вторых, я тут посчитал — сама вероятность где-то 1 сбой на 100000 пересылок. А у меня блок из 10000… и между блоками промежуток времени большой и применяются дополнительные меры по синхронизации.

Ну вот и ответ — куда — данных не очень много всего 40К. А памяти-то меньше можно использовать — только RAM_D1 а это 512К

IgorPie

14.09.2019 19:29+1По идее, можно же дать клок с FPGA?

oam2oam Автор

14.09.2019 19:30+2так и делаю.

IgorPie

14.09.2019 19:42тогда все шикарно, тем более, H750, про которого толком нет инфы, а RM на 1200 страниц, попробуй освой разом.

oam2oam Автор

14.09.2019 19:45+2да, есть такое — но очень понятный, кроме двух вещей :) — есть там DMA BDMA DMAMUX, а еще MDMA — вот с ним мне ничего не понятно пока. И еще есть странный раздел про DLYB — ну то есть что это, понятно, как работает — тоже, но к нему нет доступа!!! И вот зачем описывать то, до чего нет доступа — непонятно…

Fox_exe

14.09.2019 19:44А можно всеже узнать, что это такое вы читаете на таких скоростях? (Сетевые пакеты, чтоли, обрабатываете?)

Да и одно дело только прочитать и совсем другое — ещё и обработать, да вернуть результат. Хватает?

(Пока писал, ответили выше...)

oam2oam Автор

14.09.2019 19:47+1все же отвечу — вот так вот оказалось, что использовать stm32h750 — самый дешевый способ обработки потока (он там не очень-то обрабатывается, скорее накапливается и перемешивается)…

romanetz_omsk

14.09.2019 20:11+1Логично поставить два чипа SRAM и работать с ними по очереди (ping-pong buffers). Дело в том, что H750 обработать эти данные все равно не успеет на такой скорости.

oam2oam Автор

14.09.2019 20:19Тут такая тактика — читаем 10К данных, потом их спокойно перерабатываем (ну точнее подготавливаем и дальше передаем). А вот два чипа памяти ставить — наверно, можно организовать управление от fpga, но даже не знаю — а они успеют? И потом — все равно надо потом с них читать, время тратить… ну и это все равно дороже выходит — нет же дешевых SRAM? Вот и выходит, что как-бы процессор проще и дешевле.

jaiprakash

14.09.2019 21:14Зато SRAM можно взять широкую и быструю, и кинуть данные на 6,4 Гбит/с.

oam2oam Автор

14.09.2019 21:26вы удивитесь, но даже SRAM на 50 МГц стоит от $30 и это с организацией 8-бит (ну может и можно найти 32-бит..). А DRAM и все ее разновидности тут не проходят, хотя и дешево… А процессор — $3.50

jaiprakash

14.09.2019 22:16Удивлюсь, т. к. можно найти SRAM с 32-битной шиной на 200 МГц дешевле $10 (или около того).

И удивлюсь, что stm32h750 стоит $3.50, или это не о нём?

oam2oam Автор

14.09.2019 22:23с такими надо работать по специальному протоколу обычно. Тут надо SRAM типа flow-througthput с двумя портами, а они как раз и стоят от 30.

А $3.50 — это о нем, так вот получилось, повезло…

xFFFF

16.09.2019 10:08CY7C1338G 4-Mbit (128K ? 32) 100-MHz, покупал дешевле 500р в Мск. в баксах будет 7-8 баксов.

AVI-crak

15.09.2019 00:56У чипов stm32h7хх и stm32f7xx -есть интерфейс qspi, сразу на два чипа памяти.

AD9288 при использовании внешней логики — легко формирует DDR режим. Трамбуя один канал в 4 бита на скорости в 100МГц(а каналов два). Железо уже оптимизировано на такую скорость захвата, ничего изобретать не нужно.

Есть минус: пока идёт захват — к быстрой памяти лучше не обращаться.

oam2oam Автор

15.09.2019 06:27наверно, так тоже можно… но сами видите — QSPI только (!) на два чипа, а у AD9288 — четыре потока по 4 бита — и что делать?

AVI-crak

15.09.2019 09:24У вас 2 чипа AD9288???

А если всё-же один — то все данные прекрасно трамбуются в DDR режиме.

oam2oam Автор

15.09.2019 09:29нет, тут вот что — один чип ad9288 — это по-сути два ADC в одном корпусе, потому у него 2х8 бит на выходе. А так как там еще и интерлив, то данные все равно надо прогонять через fpga. Но как полученный поток трамбовать в DDR? В QSPI я понимаю как — пропускаем установки адреса и команды и гоним подряд данные — будто бы читаем последовательно байты. Но, как я писал — QSPI не справится…

AVI-crak

15.09.2019 12:23Ну во первых, пропустить команду в qspi не получится, адрес тоже — на них завязаны внутренние триггеры приёмо/передачи для dma. Но нет требования эти команды обрабатывать, так что можно смело использовать RC задержку на включение передачи логики.

Во вторых, DDR режим получается ну очень просто — два регистра на 8 бит с Z состоянием на выхлопе. Уровнем тактового сигнала коммутируем на выхлоп первый или второй. На первый регистр заводим старшие 4 бита с первого и второго ацп, на второй — младшие. +Мелкая логика в корпусе sot23-6…

И да, эта пакасть qspi передаёт и принимает сначала старший бит байта — наследие древнего стандарта spi и uart. Мне пришлось несколько раз плату переделывать…

Sun-ami

15.09.2019 02:02Не понял, зачем использовать таймер, почему не завести на запрос DMA EXTI0 через DMAMUX? Ведь разрешать и обрабатывать это прерывание при этом не нужно, схема EXTI0 используется лишь для генерации импульса запроса по нужному фронту с нужного порта.

oam2oam Автор

15.09.2019 06:22я тоже так хотел вначале — не работает! Только при включенном прерывании — там у них в даташите написано extit0 а не exti0 — такая вот тонкая, понимаешь, разница… :(

А было бы очень хорошо… Кстати, на BDMA — работает, но BDMA только с медленной памятью domain3 работает, так что тоже только 25 МГц может.

Wesha

15.09.2019 03:04+2микроконтроллер может читать данные на скорости 1.6 Gbps

Напомнило анекдот про блондинку — "Я печатаю со скоростью 600 слов в минуту… правда, какая-то фигня получается".

kabuto

15.09.2019 05:24-1И сколько стоило напечатать такой текстолит?

«В процессе испытаний выяснилось, что с помощью CPU можно читать на скорости 12.5 МГц из двух портов. И 25 МГц из одного. Так что вариант не работает» — это бешеная скорость для подсчета с обоих, особенно разрядив шину по периметру текстолита.

Тот кого ты подставил, печатая данную статью отрубит тебе руки.

oam2oam Автор

15.09.2019 06:25Это конечно, хорошо, что вы обратили внимание на КПДВ — тут я сам частично удивлен, эту платку я делал по приколу — вывел все порты в ряд — но самое тут удивительное, что все это именно работает замечательно, даже и на 100 МГц, а не то что на 50…

Мне кажется, вы недооцениваете черную магию :)

Dima_Sharihin

15.09.2019 08:32+2Стойкое ощущение героического превозмогания вместо решения проблем. Ну впихнули вы эти данные МК, а дальше-то что? По одному-два такта процессора на выборку? И зачем тогда вам вообще МК? Возьмите любой гетерогенный процессор (NXP i.MX7, TI AM335x, TI AM57x, STM32MP1) и вам не нужно будет решать еще одну задачу по выбросу данных уже из МК.

oam2oam Автор

15.09.2019 08:47Проблема, которую я решал — получить достаточно дешевое и устойчивое решение для чтения потока данных 1600 Mbps размером в 40К.

Ваш вопрос — что дальше — это уже именно что дальше. Хорошо, что вы заглядываете за горизонт проблемы, но задача, частью которой является эта, уже, конечно, решена — и решения эти очень дорогие (раз так в 20-40). А я хочу сделать дешевое, но хорошее решение — вот и декомпозиция у меня на подзадачи получается странная.

Если вы не заметили, но перечисленные вами варианты не лучше, но дороже и сложнее. Собственно, я использую процессор как этакую асинхронную память. Как не удивительно, но это получилось дешевле всего и проще в реализации.

Получается, что не-героическое должно быть так — че парится, берем суперкомпьютер подходящий и…

Но вы забываете, что здесь пишут статьи, не как надо что-то сделать, а как получилось. И это да, немного героическое — но я не вижу ничего плохого в этом.

ser-mk

15.09.2019 13:01Было бы гораздо интереснее если бы написали предварительно вводную статью, какую глобальную задачу решаете и как разбили на подзадачи.

Так работа конечно выглядит интересно, но очень сложно дать её практическую оценку.

oam2oam Автор

15.09.2019 13:14ну тогда подождите немного, в следующей статье замысел автора будет раскрыт более полно :) все как в детективе…

robomakerr

15.09.2019 10:49Это не 1.6 Gbps, это 200 MBps.

oam2oam Автор

15.09.2019 11:21чтобы не было разночтения — у меня Gbps Гига бит в секунду, у вас видимо MBps мега байт в секунду. А так да.

robomakerr

15.09.2019 12:23Ну просто бит/с ассоциируется с последовательной шиной, а байт/с — с параллельной. Т.е. я ожидал увидеть частоту тактирования 1.6 ГГц )

genseq

15.09.2019 11:04Восхищён глубиной проработки вопроса. И у автора, и в обсуждении. Может быть, здесь найдётся человек, которого заинтересует моя проблема? Речь идёт о разработку отечественного секвенатора:

habr.com/ru/post/455156

Проблема в том, что нужно снимать информацию с сенсорных чипов (измерять пикоамперные токи), оцифровывать её посредством многоканального АЦП (желательно 16-разрядного), передавать на FPGA, а дальше — по USB 3.0 на компьютер. Это всё уже сделано, но в Великобритании. А нужно сделать что-то подобное у нас. Можно на их родных чипах, ориентированных на секвенирование. Но можно и на неродных — на сборке чипов, усиливающих пикоамперные токи. С неродными (MAX9923FEUB и т.п.) проще, зато с родными (от MinION) может получиться лучше. Но их ещё нужно отреверсить.

Буду признателен за соучастие и содействие. Если не в работе, то в поисках специалистов, с которыми можно обсуждать подобные проблемы.

Dima_Sharihin

15.09.2019 11:44Вы не указали ключевых моментов задачи: частота дискретизации, требование к одновременности семплирования и так далее. Так я не понял из вашей задачи, зачем вам USB3 и FPGA, ведь обычно многоразрядные АЦП как правило не бывают быстрыми

genseq

15.09.2019 12:05Ключевые моменты знают только разработчики нанопоровой технологии секвенирования. А они стараются не делиться информацией. Судить о некоторых параметрах электронной части их приборов можно только по косвенным признакам. И ориентироваться на лучшие показатели. Например, известно, что частота работы чипов AXBIO (1 миллион сенсоров) достигает 110 гигагерц в секунду. И каждый сенсор из этого миллиона работает с частотой 20 опросов в секунду. У оксфордцев сенсоров меньше (512 или 3000), но считываются они быстреее (5...10 тыс. опросов в секунду).

Dima_Sharihin

15.09.2019 12:15110 гигагерц в секунду

110ГГц полосы — это самый крутой осциллоскоп от Keysight. И даже там всего лишь 256Gsps идет на АЦП. Никаких 16 бит там и рядом нет.

Полагаю что-то совсем не так, как вы описываете. Сигнал на такой частоте вовсе не означает измерений на этой частоте.

Ключевые моменты знают только разработчики нанопоровой технологии секвенирования.

Ох эта разработка по-русски. "Мы не знаем, как оно работает, но должны еще вчера сделать не хуже". Без теоретического обоснования того что, как и, самое главное, зачем мы что-то измеряем любое принятое техническое решение сводится к киданию дротика в доску с развешенными партнамберами. Может быть вам повезет и оно действительно решит задачу, в остальном же — пустая трата времени, сил и средств.

amartology

15.09.2019 16:30Ох эта разработка по-русски. «Мы не знаем, как оно работает, но должны еще вчера сделать не хуже».

И так вот бродит отечественный нанопоровый секвенатор в комментариях в каждой второй статье про электронику на хабре. И с разработчиками потом надо говорить с такими, которые или сделают все бесплатно, или сами найдут финансирование решения этой красивой научной задачи. И бизнес-план напишут тоже сами.

oam2oam Автор

15.09.2019 12:25а вот давайте прикинем простейший вариант. Пусть на входе стоит что-то типа opa4333 а дальше мы читаем в микроконтроллер и данные со всего массива микроконтроллеров объединяем (другой вариант ставим аналоговый мультиплексор после ОУ). У мк 16-разрядных входов обычно до 36 (а 12-разрядных до 42), так что без мультиплексирования на 512 сенсоров уйдет 128 ОУ и 15 мк (это примерно на 20-30 кв.см плата будет), ну и результирующий поток при пусть 1К опросов в секунду (1К*512*16 = 8Mbsp) не выглядит очень уж угрожающим. Такое вполне можно сделать… Будет слегка оригинальная такая плата на кв. дециметр…

oam2oam Автор

15.09.2019 12:28и еще — 110 ГГц — это видимо в сумме такая частота, ну например, миллион микроконтроллеров по 110 кГц :)

это как со звуком — на колонках пишут 100W, так это значит, оказывается, что при данной мощности их разрывает :)

genseq

15.09.2019 12:35Немного информации к размышлению:

sci-hub.se/10.1016/j.aca.2019.01.034

sci-hub.se/10.3390/bios6030042

www.ncbi.nlm.nih.gov/pmc/articles/PMC4883400

habr.com/ru/post/455156

1drv.ms/p/s!Aj-K-u-yGV92mDjxBBlbD7siqlsU?e=taUQ4b

HorrorInfinity

15.09.2019 13:57Если данные формируются в fpga, то почему бы в ней же не сформировать fifo-буфер (скажем на 1000 строк) с выдачей однократного прерывания на МК по заполнению и читать по такту из МК?

Таким образом можно пропустить 400 МБ даже при тактировании GPIO в 100 МГц (32 бита/4 байта х 100 МГц) или 3200 Мбит

oam2oam Автор

15.09.2019 13:59пока не находил решение, удовлетворяющее по цене, но вот выше предложили ICE40UP5K — надо пробовать…

HiTechSpoon

16.09.2019 07:20Качество распайки платы на КДПВ выглядит печально, особенно грустно от почти замкнутых ножек МК.

oam2oam Автор

16.09.2019 17:24да, вот так уж пришлось… но эта плата — инженерный вариант, паяна вручную и потом несколько ножек пришлось отогнуть и на них конденсаторы висят… Но следующий вариант был уже нормальным, жаль никуда не пошел пока…

сначала я думал, вообще не заведется — но нет, даже 100 МГц работает на такой плате, а процессор на 480 МГц вообще без проблем пошел… бывает же…

GarryC

16.09.2019 09:40Может быть, я чего то не понял, но я бы прицепил на FPGA память и складывал туда данные, а потом спокойно перекачивал их в контроллер.

amartology

16.09.2019 10:27Насколько я понял автора, его в первую очередь интересует дешевизна решения, а подходящие ПЛИС — дороги.

oam2oam Автор

16.09.2019 17:23все верно. Но под влиянием обсуждения буду пробовать Cyclon-IV вместе с DDR на 400 МГц — может и смогу :) там меня выше в комментах подбадривают :) а то я не очень в fpga (всего одну систему сделал...). Вроде как бы дешево выходит…

OloloFine

16.09.2019 17:20Хм, если тактирование синхронное, чтоб не мучиться с разрядностью шины, не думали просто 2 или 4 микроконтроллера в параллель, пусть каждый свою часть шины в свою память кладет, эдакий гоблин-RAID?

oam2oam Автор

16.09.2019 17:21так и делал, но у меня там еще четыре таких потока… уже слишком процессоров :)

a_freeman

Расскажите, откуда такая широкая шина данных приходит, что то не очень современное?

oam2oam Автор

хм, мне правда, казалось, что как раз это весьма современно — большие потоки данных :) Странное тут — использование микроконтроллера… А вот откуда — это, вообще-то, тема следующей статьи… но так, по секрету — данные идут из fpga, а туда — из быстрого ацп, я их замедляю в fpga.

iliasam

Делаете DDC SDR приемник?

oam2oam Автор

что вы :) — гораздо круче! Ждите, где-то через месяц напишу, что получилось — но там речь пойдет уже об 6.4 Gbps (если все получится, конечно)…

sinc

Возьмите уже USB 3.0, не мучайтесь

oam2oam Автор

It implements an architecture that enables 375-MBps data transfer from GPIF II — так вот они пишут. Так что — 375 не играет против 1600! Но за наводку — спасибо.

sinc

Максимум у usb 3.0 5 гигабит/с. 100 мегабайт в секунду делал лично, для 2-х 16-ти разрядных АЦП.

oam2oam Автор

если не секрет — что за АЦП? Они на 100 МГц данные могут давать?

sinc

они на 25 МГц были. какие точно, уже не помню. вы лучше скажите зачем 100 МГц. Просто, AD9288, судя по даташиту, не шибко-то хорошие.

oam2oam Автор

жаль, что 25… AD9288 они конечно 8-битные, но довольно бодрые. Хотя и jitter великоват. Но главное — они дешевые…

Rullix

Даже на 400 мгц.

oam2oam Автор

Это какие?

Rullix

Я работал с этой. ADS5401, 12-Bit Resolution, Maximum Clock Rate: 800 Msps, Input Bandwidth (3 dB): > 1.2 GHz.

oam2oam Автор

Да уж, я посмотрел — ее и в продаже не очень-то найдешь… а сейчас, видимо, из-за санкций совсем исчезла.

sfclubh

Я конечно извиняюсь но мне кажется что вы мегобиты(Mbps) путаете с мегабайтами в секунду(MBps)

VelocidadAbsurda

375 — это в мегабайтах/с! Там сам порт вообще до 100МГц*32бит, но где-то дальше накладные расходы на сборку пакетов снижают до тех самых 375МБ/с.

oam2oam Автор

ну тогда да — интересный вариант получается.

S-trace

А сжатие (хотя бы какое-нибудь простенькое) использовать не пытались? Может, удастся снизить поток данных при помощи него?

Если, конечно, приём такого потока не является для вас самоцелью)

xFFFF

А нельзя сильнее нагрузить fpga?

oam2oam Автор

а в каком смысле? Поток-то изначально 1.6 Gbps — просто я его на fpga из 16-битного делаю 32-битным, при этом частота падает с 100 до 50 МГц. Но сам-то поток никуда не девается. Я пробовал вообще 100 МГц пихать в MCU — не лезет! Ну нечем просто читать и писать на такой скорости… И fpga у меня простенькое — MAX-II (в прошлой статье как раз с ним разбирался...), это самое простое и дешевое оказалось решение.

Но я бы с удовольствием узнал, как это можно сделать.

AigizK

может просто fpga взять xilinx какой нибудь у которых ЦП на борту. и там считать?

oam2oam Автор

Это очень дорого и непонятно для чего — там тоже ведь шина не резиновая. Те же яйца, только в профиль — поток не понятно, как вводить…

Drottarutarnum

У латтис есть плисы как раз для превращения последовательного потока в параллельный

Как на счет того, чтобы сделать не 32 бита, а больше? Раза в 4. Тогда скорость ещё упадет и станет легче

oam2oam Автор

так свободных портов мало — максимум еще один можно выделить. И на каждый порт — еще канал DMA, а это еще нагрузка не внутреннюю шину процессора — тут похоже вообще предел для нее 1.6 Gbps

ukt

а если использовать встроенный процессор на фпга(ну вроде ниос или зайлинковский аналог)?

oam2oam Автор

вот думал в эту сторону — но сложно и дорого это не мой путь в данном случае…

drWhy

Извините за профанский вопрос, почему бы не использовать для высокоскоростной передачи данных интерфейс SATA? Реализация SATA в виде IP core доступна для fpga, есть бесплатные реализации. Интерфейс отработанный, быстрый, симметричный, с низкими задержками, простой в аппаратной реализации, без сложной синхронизации, с простыми разъёмами и массой качественных кабелей длиной до 1м.

oam2oam Автор

Эм-м, как бы объяснить — вот есть такая штука, ацп и у нее просто 16-битный выход, на котором с частотой 100 МГц появляются данные, никакого интерфейса другого нет (SATA уж тем более). И вот надо эти данные как-то читать без задержки даже на 1 ns и так 10000 раз подряд. Кстати, у SATA — это 1-битный поток, на что намекает первая S и скорость у него 300 Mbps (у SDATA — 3 конечно 6 Mbps). Ну и там, в этом SATA свой сложный протокол. К нему и надо подготовить данным, может быть… Но лучше их потом в USB или ETH запихать — легче будет…

И вот чтобы эти наши данные превратить в SATA — довольно сложное fpga надо, а я сложное и дорогое тут не хотел бы…

drWhy

Про требования к отсутствию задержек понял. А АЦП с последовательным выходом, соответственно, дадут ещё 16-кратное увеличение частоты.

Но ведь вычислительно SATA должен быть легче USB, и нужно реализовать лишь часть функциональности. Соединение точка-точка, никаких очередей, настроить один раз передачу данных в одну сторону (как делают контроллеры в режиме DMA) и потом просто подавать данные.

Про выбор привычного и неизбыточного решения тоже, конечно, понятно.

oam2oam Автор

заметьте — про USB я ничего не говорил. Это уже следующая задача будет, куда снятые данные отдавать. Тут именно что надо их взять как-то…

pvvv

ft601q до 100МГц х 32 бита, правда фифо 16кБ всего. но 1.6Gbps должен через неё непрерывно пролазить.

у блэкфинов параллельный порт до 66МГц х 16бит, и у некоторых из них портов больше чем один да и разрядности до 24 бит встречаются,

но можно и распараллелить на два самых дешевых bf592 (по 1.99$ за 1k штук у производителя, получится конечно дороже чем stm32f750 за 3.5$, но не намного)

хотя может просто взять плисину немного пожирнее,

ICE40UP5K-SG48I qfn48, 6$ за штуку и мигабит памяти?

а вообще как АЦП 4 штуки lpc4370 будут не особо дороже чем два ad9288, и АЦП 12битный, правда 80МГц, а не 100, зато сразу с памятью и хоть с USB, хоть c ethernetом, хоть с последовательным портом.

oam2oam Автор

Как-то не очень понял про lpc4370 — почему вы думаете, что 80 МГц это частота сэмплирования, а не частота ADC? Так-то у них не больше 6 Msps…

Но список вариантов у вам получился большой. Я вот никак не смог придумать, что делать с плисом полезного — большой плис со встроенной памятью дорог, а маленький бесполезен…

pvvv

встроенный АЦП у lpc4370 — 80Msps, в даташите так написано. откуда вы взяли цифру 6Msps? была какая-то поделка, labtool вроде — просто плата с усилителями и разъёмами для LPCLink2, там полоса была ограничена в несколько МГц просто предусилителями перед АЦП.

а полоса пропускания самого АЦП под 250МГц

вам данные всё равно в результате надо в ПК перегнать, если средний поток данных не сильно большой, и эти 40кБайт данных прилетают, грубо говоря, раз в секунду, то хоть по последовательному порту можно из плис их достать. или через какой-нибудь usb мост от ftdi, например ft232h. ethernet со стороны плис тоже не особо сложно делается.

вышеуказанный ICE40UP5K c мегабитом памяти стоит дешевле stm32f750

а 5к ячеек и на soft процессор хватит чтобы протокол общения с ПК на С/C++ писать, а не на верилоге.

oam2oam Автор

действительно, для ADCHS — 80 Msps, правда пишут, что no matter how you juggle with the FIFO, DMA, and interrupt, it will all boil down to the relation that the core has only slightly greater than 5 clock cycles per ADC sample — то есть в реальности без обработки можно только 40 Msps.

Но это не главное — АЦП тут должны быть внешние из-за точного тактирования (речь идет о долях такта).

А вот fpga с памятью может оказаться удачной идеей. Но я пока не нашел таких же дешевых решений. Ту что вы указали — мало пинов (у меня меньше 42 не выходит), мало памяти — 1 кбит (а надо 16 кбит), мала частота — у меня MAX-II 5 грейда еле справляется с его задержками распространения по LUT менее 1 ns, а тут совсем не то.

bugdesigner

MAX 10 по цене не дороже микроконтроллера + MAX II выйдет. 10M04xxx — 189kbit памяти 4K LE. Если будете покупать много, можно цену в районе 5-6$ выпросить.

pvvv

то что пишут про 5 clock cycles per sample, там человек пытается на ходу ещё и обрабатывать данные и двойная пересылка через два буфера, если же надо просто сложить N отсчётов из АЦП в память, DMA со всеми 80Мsps справляться должно, процессор вообще при этом спать может.

с синхронизацией смотреть надо, думаю есть какая-нибудь возможность аккуратно затактировать ФАПЧ АЦП от внешнего источника с нужной фазой. но если клок не равномерный, а надо по внешнему клоку, со случайной фазой, сэмплировать данные, то не получится.

памяти у ICE40UP5K мегабит, а не килобит, максимум 70МГц х 64 бита = 4.5Гбит/c (4 блока 16 битных по 256кбит)

а количество ног у АЦП: 16бит данных и два клока, это 18, оставшихся 20 ног вполне хватит для любого разумного интерфейса с ПК.

oam2oam Автор

да, пожалуй надо рассмотреть решение на ICE40UP5K — очень даже заманчиво! И по цене вполне нормально.

pvvv

я бы всё-таки с ft600q для начала попробовал, напрямую без плис/МК, там возможно лишь пара логических элементов/инверторов понадобится, чтобы АЦП с синхронным fifo склеить, а если требований к 100МГц клокам особых нет, их можно прям с ft600q взять, и потом задержать/инвертировать для interleaving АЦП.

oam2oam Автор

так ведь получится только в поток USB 3.0 превратить, а его же потом надо куда-то читать?

pvvv

ну может, воткнуть этот USB провод в ПК?

или вы делаете портативный прибор и данные в этом же stm32 и будут обрабатываться?

oam2oam Автор

в ПК обязательно воткнем! Но не сразу — в задумке таких блоков аж 4 штуки (как минимум) — все не воткнешь, да и ПК захлебнется и от одного…

pvvv

от одного не захлебнётся, но от четырех пожалуй да, только если дополнительные USB3 порты на PCIe воткнуть, но тогда действительно проще всё-таки какое-нибудь достаточно большое fifo и любой медленный интерфейс.

oam2oam Автор

посмотрел характеристики — слишком медленная… по памяти 70 МГц, задержки LUT 9 ns. Но идея, может, и стоящая…

pvvv

70МГц * 64бит = 4.5 Gbps

oam2oam Автор

откуда же 64 бит — всего (!) пинов-то 39, из них на вход 16, да клоки, да… в общем — 16 бит и всё…

pvvv

завести внутрь надо 100МГц х 16бит, а вот уже внутри их можно превратить в 25МГц х 64 бит и спокойно засунуть в 70МГц память. Она там организована так, 4 отдельных блока с 16бит шинами.

oam2oam Автор

видимо, так можно, но очень смущает время LUT 9 ns — это же почти на пределе для 100 МГц — как-то не очень я представляю какую-нибудь асинхронную схему… А с синхронной можно и пролететь по таймингам…

У меня вообще пределы по времени не более 1.4 ns выходят для нормальной работы.

xFFFF

MAX-II — дикое старье. Предлагаю заказать на Алиэкспрессе отладочную плату с FPGA Cyclone II EP2C5T144. Я покупал рублей за 800. Cyclone II имеет встроенные блоки памяти. Т.к. количество данных вполне определенное, то можно сконфигурировать память как двухпортовую. В один порт писать с большой скоростью, а читать и отдавать наружу через второй порт. Это можно сделать с более низкой частотой, не кратной частоте записи. Можно даже сжатие данных реализовать. Часть семплов передавать полностью, а часть как разницу между сэмплами. Аналогично сжатию видео.

oam2oam Автор

я смотрел, подходит разве только начиная с cyclon-iv E (40) — не сказать, чтобы очень дорого. Конечно, сейчас я использую max-II за 89 рублей чип. Если только использовать один циклон на все каналы (их 8), то наверно, будет лучше… Только вот это для меня вызов своего рода — я первую свою программу для fpga написал в этом году только… что-то нет уверенности…

xFFFF

Надо верить в свои силы) Когда я впервые столкнулся с плис, мне пришлось писать обработку видео в реальном времени, и все получилось, хотя я видел плис первый раз в жизни. Но там не сложная обработка была, типа автоконтраста, и автояркости и тд). Сейчас сменил работу, с плис года 4 не работал.

AigizK

а что за ацп используете?

oam2oam Автор

простое AD9288 — там на борту два ацп, клок 100 МГц