IBM объявила о разработке техпроцесса 2 нм.

О чём было объявлено:

- 2 нм.

- 50 млрд транзисторов на площадке размером с «ноготь». Позднее уточнили – на площади в 150 кв.мм – то есть, 333 млн транзисторов на миллиметр квадратный (MTx/мм2).

- Шаг затвора транзистора (Contacted Poly Pitch, CPP) в 44 нм, длина затвора 12 нм.

- Транзистор с кольцевым затвором (Gate All Around, GAA). Такие затворы можно сделать несколькими способами – судя по разрезам, IBM использует горизонтальные нанопластины (horizontal nanosheets, HNS).

- Стек HNS находится на оксидном слое.

- На 45% быстрее или на 75% экономичнее по сравнению с передовыми чипами на 7 нм.

- Фотолитография в глубоком ультрафиолете (EUV) используется на лицевой стороне и позволяет варьировать ширину HNS от 15 до 70 нм. Очень полезно для подстройки различных областей схемы под низкое энергопотребление или высокую производительность, а также для ячеек SRAM.

- Пластины имеют толщину 5 нм и располагаются друг на друге по три штуки.

Действительно ли это 2 нм техпроцесс? Сегодня в производстве чипов лидирует TSMC. Мы построили график связи между названиями техпроцессов TSMC и плотностью транзисторов, аппроксимировав кривую с коэффициентом детерминации 0,99.

От 28 нм до 5 нм используются реальные цифры по данным IC Knowledge и TechInsights. Цифры по 3 нм основаны на пресс-релизах TSMC. 2 нм и 1,5 нм – наша экстраполяция.

Используя график, можно преобразовать плотность транзисторов в эквивалентный TSMC техпроцесс (TSMC Equivalent Node, или TEN). Получаем 2,9 нм для 333 MTx/мм2. С нашей точки зрения, получается, что это техпроцесс на 3 нм, а не на 2 нм.

Чтобы детальнее сравнить анонс от IBM с предыдущими анонсами техпроцессов на 3 нм и предполагаемыми процессами на 2 нм, нужно сделать несколько предположений.

- Из анонса известно, что CPP – 44 нм.

- Предположим, что для производства используется самая плотная технология размещения транзисторов, Single Diffusion Break (SDB).

- Судя по фото в разрезе из анонса, технология Buried Power Rails (BPR) не используется. BPR нужно, чтобы уменьшить размер дорожкни HNS до 5,0 – поэтому предположим, что в данном процессе это значение равняется 6,0.

- Чтобы получить плотность в 333 MTx/мм2, минимальный шаг Minimum Metal Pitch должен равняться 18 нм – это весьма агрессивное значение, которое, вероятно, потребует EUV-фотолитографии с мультиматрицами.

2 нм IBM против существующих техпроцессов на 3 нм

В следующей таблице дано сравнение разработок IBM и наших прикидок для 3 нм техпроцессов от Samsung и TSMC. Мы знаем, что Samsung тоже работает с HNS, а TSMC остановилась на 3 нм FinFET. Samsung и TSMC тоже объявили об увеличении плотности размещения транзисторов для своих техпроцессов на 3 нм по сравнению с 5 нм. Поэтому плотность транзисторов всех трёх компаний нам известна, и мы можем подсчитать TEN для всех. TEN от IBM равна 2,9; видно, что у Samsung это 4,7, а у TSMC – 3,0. Опять-таки получается, что 2 нм от IBM больше похож на 3 нм от TSMC, при отставании Samsung.

Красным выделены ориентировочные параметры, необходимые для достижения объявленных плотностей, в предположении, что все компании используют технологию SDB. Высота дорожек меньше всего у TSMC, поскольку без BPR у FinFET этот параметр может достигать 5,0, однако для того, чтобы такая же высота была у HNS, необходимо использовать BPR.

2 нм IBM против существующих техпроцессов на 2 нм

В следующей табличке мы оценили значения параметров для техпроцесса на 2 нм от Samsung и TSMC. В нашей экстраполяции мы предполагаем, что компании используют BPR (технология BPR ещё не отработана, но, вероятно, вступит в строй, когда они анонсируют техпроцесс на 2 нм в 2023-2024 годах). Также предположим, что компании примут на вооружение архитектуру forksheet NHS (HNS FS), чтобы добиться высоты дорожки в 4,33. Оценки CPP и MPP сделаны на основе текущих тенденций по миниатюризации технологий.

Энергопотребление и быстродействие

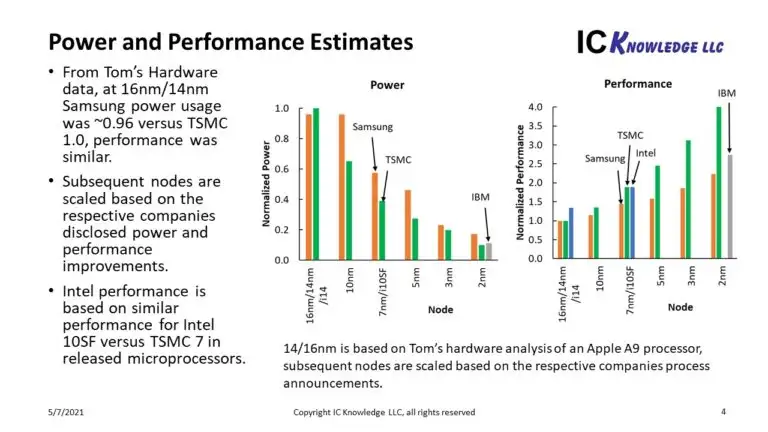

В этом году я уже делал предположения касательно энергопотребления и быстродействия устройств от Samsung и TSMC с использованием дополнительных данных по быстродействию от Intel. Экстраполяция основана на заверениях компаний и на сравнении реальных цифр у техпроцессов на 14 и 16 нм.

Поскольку IBM сравнила улучшения в энергопотреблении и быстродействии с передовыми техпроцессами на 7 нм, я могу разместить их данные на тех же самых графиках.

Благодаря использования HNS, у IBM наблюдается значительное уменьшение энергопотребления, что делает их 2 нм техпроцесс более эффективным, чем техпроцесс на 3 нм от Samsung и TSMC. Хотя, по нашему мнению, когда TSMC перейдёт на HNS на 2 нм, их энергопотребление не будет уступать таковому от IBM. В вопросах быстродействия мы предполагаем, что техпроцесс на 3 нм от TSMC опередит техпроцесс на 2 нм от IBM.

Конечно, всё это лишь прикидки, основанные на большом количестве предположений.

Заключение

Проанализировав анонс IBM, мы приходим к выводу, что их техпроцесс на 2 нм больше похож на техпроцесс на 3 нм от TSMC с точки зрения плотности размещения транзисторов, обладая при этом лучшими показателями энергопотребления, но уступая в быстродействии. Заявление от IBM производит впечатление – однако это всего лишь лабораторный образец, явно превосходящий 3 нм от TSMC только по энергопотреблению. При этом первые рисковые партии устройств от TSMC на 3 нм появятся уже в этом году, а коммерческие – в следующем.

По нашему мнению, TSMC будет удерживать преимущество по плотности, энергопотреблению и быстродействию устройств на техпроцессе в 2 нм, когда те пойдут в производство в 2023-2024 годах.

mSnus

Если верить вот этой статье на Хабре, то скорее нет, чем да.

А если вот этой -- то скорее да, чем нет.

А почему вы спрашиваете?

novoselov

TLDR

Real vs Marketing

4.7 nm = 3 nm Samsung

3.0 nm = 3 nm TSMC

2.9 nm = 2 nm Samsung

2.9 nm = 2 nm IBM

2.1 nm = 2 nm TSMC