У меня был в свое время практикант из Стенфорда, от которого я получил инсайдерскую информацию, чему их там учат. Потом я интервьировал много студентов, и понял, что если человек не делает самостоятельных проектов в вузе, а просто плывет по течению программы как медуза, то будучи выброшенным на берег индустрии, он становится совершенно беспомощным.

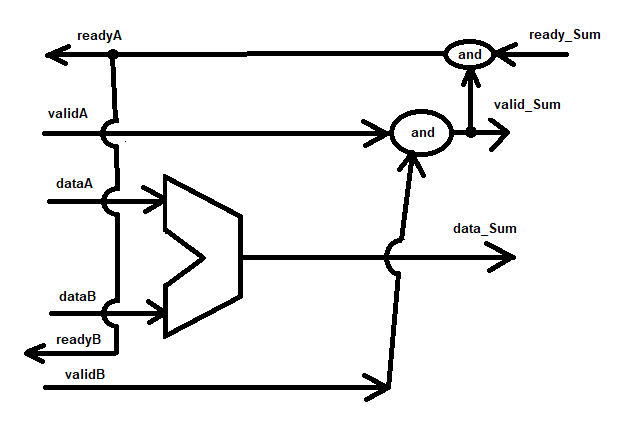

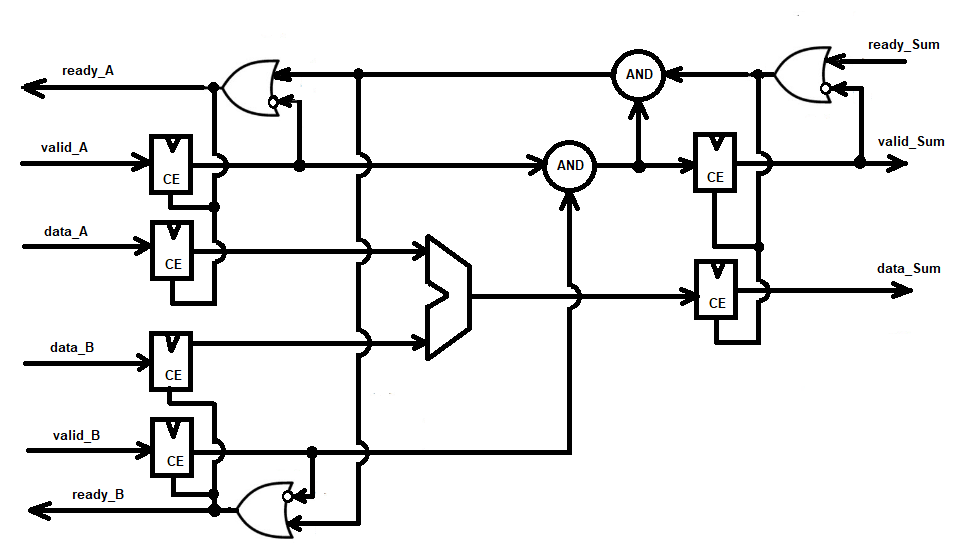

Когда я вижу у недавнего выпускника в резюме какой-то из протоколов в котором используется valid/ready, например AXI или AHB, я прошу его спроектировать блок, у которого на входе два числа A и B, а на выходе их сумма. Разумеется не просто написать SUM=A+B, а еще и поставить valid/ready сигналы на каждый из A, B, SUM, чтобы A и B могли приходить в разное время, а также чтобы блок ждал, если SUM не может быть передана другому блоку сразу.

Некоторые не справляются. Грустно смотреть на человека, который потратил 6 лет своей жизни (4 года в бакалавриате и 2 года в магистратуре) и океан денег на образование - и не может сложить два числа и бьется как угорь на сковородке. То блок не работает когда числа приходят в разное время, то создатель забывает снять valid, и блок на 2+2 выдает не 4, а 4-4-4-4-4-4-4... То числа складываются не попарно, а просто записываются в регистры и на выход идет их текущая сумма, хотя количество аргументов A и B не совпадает. То не отрабатывается backpressure и результаты теряются, то (после того как кандидат написал страницу кода на верилоге) блок работает на половинной производительности, то есть не может принимать поток чисел подряд, а ожидает между ними пропуски (gaps). Короче ведет себя как ChatGPT.

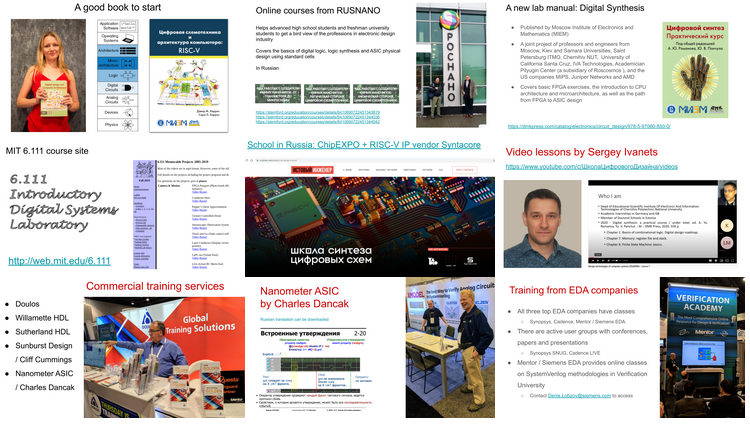

Конечно, если студент сам во время учебы делает скажем правильные open-source проекты, то он вписывается в индустрию легче. Но все равно компании тратят много усилий на переподготовку недавних студентов. Некоторые электронные компании нанимают профессиональных тренеров типа Клифа Каммингса, которые берут три тысячи долларов за неделю трейнинга за_каждого_студента.

Я в свое время пытался привезти Клиффа в Россию, но в первую попытку звезды не сошлись (хотя все топ российские электроные компании согласились прислать по одному-два инженера). А во второй раз настала международная напряженность и все накрылось - Клифф продал свою компанию бОльшей трейнинг-компании и там менеджер не захотел.

Я это все к чему - я на днях прочитал на Хабре что Ядро/Syntacore решили сделать целый внутренний курс для тренировки ASIC проектировщиков из бывших FPGA проектировщиков:

Это в принципе крутая идея, так как отличие front-end ASIC от FPGA инженеров не такие уж большие:

1. FPGA инженер с опытом мою задачку про A+B решит.

2. В FPGA как правило менее навороченные микроархитектуры, чем в ASIC, но это дело количественное, а не качественное в смысле опыта.

3. В ASIC есть больше всякого self-теста, scan chains, энергопотребления - но это в основном забота physical design teams, а не front-end designers.

Замечу что Элон Маск в свой SpaceX сейчас интервьирует на смешанную ASIC/FPGA позицию:

Но что делать тем, кто еще не готов идти в Ядро/Syntacore и хочет натренировать себя в FPGA? Предположим, что у вас есть некий начальный опыт, например почерпнутый из источников, которые я перечислил в презентации для проектов в Средней Азии, или скажем по ссылкам из телеграм-каналов fpgasystems , tinyurl.com/yy79xfer, DigitalDesignSchool , сайта ранних энтузиастов FPGA в России marsohod.org итд:

Следующий шаг - набрать опыта на открытых проектах, и у меня как раз есть такой проект, для которого я собираю команду. Это проект YRV-Plus, см. поддерево Plus в репозитории github.com/yuri-panchul/yrv-plus . Суть проекта - накрутить опций вокруг RISC-V ядра микроконтроллерного класса под названием YRV. В том числе:

Запустить ядро YRV на дюжине FPGA плат от Altera / IntelFPGA, Gowin, Xilinx, Lattice.

Сделать скрипты для работы YRV на различных симуляторах: Synopsys VCS, Cadence Xcelium, Siemens EDA / Mentor Questa, Icarus Verilog, Verilator.

Сделать пару десятков интересных софтверных примеров на ассемблере, в частности с обработкой прерываний.

Сделать различные варианты linker script для компиляции софтверных примеров на Си.

Сделать пример разделения общей памяти между тремя такими ядрами. Сделать разделяемую память многобанковой и показать, как количество банков влияет на производительность.

Сделать пример обмена сообщениями между несколькими ядрами с помощью так называемого gated storage. Одно ядро пишет, а другое читает из адреса, который отображается не на обычную память, а на очередь FIFO. Когда FIFO наполнено, записывающее ядро останавливается на следущей записи. Когда FIFO пустое, читающее ядро останавливается на следующем чтении.

Показать изменение производительности в зависимости от глубины FIFO и поведения программ.Сделать контроллер SDRAM памяти для разных плат и интегрировать его с YRV.

Присоединить к ядру различные кэши: полностью ассоциативные, прямого отображения, многосекционные, с различными стратегиями замещения. Показать изменение производительности с различными сценариями доступа к данным.

Спортировать на YRV какой-нибудь бесплатный RTOS, например FreeRTOS.

Реализовать в ядре FPU и сравнить его производительность по сравнению с библиотечно-целочисленной реализацией плавающей арифметики (начать со сложения или умножения). Сравнить размер и максимальную тактовую частоту получившихся ядер.

Реализовать в ядре векторые расширения и продемонстрировать, какое они дают увеличение производительности.

Присоединить к ядру сопроцессор для работы с графикой, чтобы с ним можно было сделать учебную игровую приставку.

Измерить производительность ядра YRV на бенчмарках Dhrystone и CoreMark, сравнить с другими открытыми ядрами, в частности: Syntacore SCR1, ядро mirisc от Московского института электронной техники и SweRV EH1 от Western Digital.

Верифицировать ядро с различными наборами тестов.

Синтезировать YRV для ASIC с помощью открытого маршрута Open Lane и System-on-Chip (SoC) платформы Caravel. Вот тут-то вы можете начать переучиваться на ASIC.

В частности нужно спортировать YRV на плату Tang Primer 20K c китайским GoWwin FPGA, с которой на фотографии слева работает мой приятель Александр Белиц, инженер из компании Marwell. Эта плата недорогая и вместительная, использует систему разработки от GoWin, которая является альтернативой Intel FPGA Quartus и Xilinx Vivado.

Также в частности стоит спортировать YRV на плату Digilent Nexys4 DDR, которую держит в руках девушка Ирина из Новосибирского Академгородка. Эту плату с системой разработки Xilinx Vivado используют большое количество вузов.

Почему именно процессорное ядро YRV, хотя вокруг этих RISC-V ядер немерянное количество? По комбинации факторов:

YRV одновременно является полнофункциональным RISC-V ядром (не учебным подможеством), и при этом имеет очень компактный размер, то есть влазит в недорогие FPGA платы.

YRV написал проектировщик Монте Далримпл, который занимается процессорами с 1970-х годов в компании Zilog, использует Verilog с начала 1990-х годов, спроектировал кучу чипов, в том числе для космоса. То есть это в чистом виде "старый конь борозды не испортит" - Монте чувствует тайминг, пишет все аккуратно и читабельно, понимает какая нужна периферия и контроллер прерываний для микроконтроллера.

Монте все задокументировал в собственной книжке, которая также описывает весь материал по архитектуре RISC-V необходимый для работы с его процессорным ядром:

К нашей open-source команде, помимо Монте, меня и Белица, присоединился Дмитрий Петренко. Дмитрий одолжил несколько альтеровских плат от программы одалживания FPGA плат Михаила Коробкова и перенес на них YRV. Также Дмитрий написал линкер-скрипт и смог построить маршрут писания программ для YRV на Си (hello world). Вот платы Дмитрия в работе:

Мы недавно с Александром Белицем обедали с Монте Делримплом в Ливерморе, городе, который был недавно в новостях по поводу термояда. Монте там живет. В центре города стоит скульптура - вращающийся шар с фонтаном и надписями про российcко-американское сотрудничество в физике. Кстати по странам происхождения четыре участника проекта являются выходцами из четырех стран - России, Украины, Белоруссии и США - угадайте кто откуда.

Так что присоединяйтесь пятым и более. Репозиторию можете форкнуть у меня или у Дмитрия (ссылка выше). Мы проводим еженедельные созвоны в 9 утра в воскресенье по Калифорнии (это 20.00 вечера воскресенье по Москве).

Но если вы уже изучили простые процессоры и основы FPGA, присоединяйтесь сразу к Ядру/Syntacore . Если нет - можете еще пройти курс лабораторных от МИЭТ по проектированию однотактного процессора с прерываниями и периферией (видео их лекций). И потом присоединиться к новому проекту MIRISC в МИЭТ с более сложным конвейером. Это ситуация "пусть цветут все цветы, заимствуют и меряются друг с другом"

Комментарии (173)

MUTbKA98

20.12.2022 12:18+16Это просто издержки советской системы в принципе - студента грузят знаниями (а спортсмена - тренировками под край и даже за край), и если ВУЗ топовый - то грузят в 20 раз мощнее, что даже весьма умному парню не дает возможности продохнуть и подумать самому хоть о чем-нибудь. И ведь тот, кто все это выдержал и сохранил ресурсы на что-то своё - тот становится крут. Только сколько таких выживших и не потухших?

Но все же процесс этот обратим, поэтому не все так страшно, хотя потеря времени и растрата усилий имеется.

YuriPanchul Автор

20.12.2022 12:26Это издержки не только советской ситемы. Вообще если в России поставят эти курсы по человечески, то российские инженеры могут получить преимущество.

Myclass

20.12.2022 13:42+18Опять эти 'если'. А можно про проблемы обучения в той или иной стране без прикрутки, а вот если бы в России... везде есть косяки и везде есть потенциал стать лучше. Но нужны и условия. И не только в вузе, но и вокруг вуза.

Начали про косяки как-бы в Стенфорде (а скорее какой-то единичныйслучай), а закончили мечтами о курсах в России - не вижу логики.

Slon48

21.12.2022 23:17+5Ну оно из сытой бездуховной Америки как-то всегда сподручнее Расеюшку то любить, типа такого ))

DvoiNic

20.12.2022 13:56+4студента грузят знаниями

в советской системе не хватало практики (за исключением «физтеховской системы»).

а знаний (в «нетоповых», но и не из последних) ВУЗах давали достаточно, но не столько, чтоб «не продохнуть».

anka007

20.12.2022 15:54А вы знаете, очень зависит от студента. Случаи, когда студенты прошли вступительные испытания и потом ночами сидят пытаясь вытянуть уровень даваемых знаний единицы и заканчивается это обычно сильно раньше диплома плачевно проблемами со здоровьем. Все же большинство студентов вполне себе находят время не только вздохнуть, но и на хобби, и на развлечься. Это я сужу по личному опыту и знакомым с топовых технических вузов.

А как так получается, что одни идут развлекаться и все сделано, а другие ночами сидят я кажется уже представляю на примере собственных детей. Старшая еще только в начальной школе, но иногда на нее находит просидеть час над упражнением на 10 минут.

F123456

20.12.2022 12:21Очень сомневаюсь что это был практикант из Стенфорда ?

YuriPanchul Автор

20.12.2022 12:25Агонизировали на этом вопросе другие, но тоже из топ-вузов.

При этом мой давний практикант из Стенфорда тоже не знал работы valid/ready на AXI шине, но он по крайней мере не утверждал, что знал. Вообще он был смышленый парень, но на его примере были видны дыры в программе даже вузов с сильной репутацией в архитектуре и микроархитектуре. Например в стенфордском учебнике есть про skid buffers, но нет про credit-based flow control итд (это не такая суровая но тоже проблема)

sergeyns

20.12.2022 13:04+1я чисто мимокродил... но жутко интересно какие могут быть зарплатные ожидания у инженера, который

" FPGA инженер с опытом мою задачку про A+B решит. "

Кстати, 3000$ за неделю -> 600$ в день - в общем это такая "средняя" ставка практически любого учебного курса того же IBM. У российских учебных центров ставки поменьше, но западные расценки примерно такие, от Business Intelegence до Enterprise bus

YourgenAP

20.12.2022 14:58+9Не мимокрокодил, а реальный студент из топовой московской школы в Техническом Университетете Берлина (для справки, топ-140 мира по рейтингам Times и QS, Топ-2 или Топ-3 Германии среди технических университетов после Мюнхенского и Аахенского, Топ-1 DAAD среди ВУЗов Германии по предпочтению иностранцев). С описанным в самом начале статьи знаком не понаслышке.

Отучился бакалавриат (3 года) по направлению Информатика в машиностроении (дословный перевод старого названия). За 3 года обучения, хоть и информатика, была только база: компьютернориентированная математика (название предмета на 2 семестра, объединяющего алгоритмы на массивах, дискретную математику, хеширование и функциональные языки) и системное программирование (базовые навыки работы с ЯП С). Ни одного проекта. За трехмесячную практику и следующие за ней уже более года работы в реальной компании, занимающей написанием системного софта для жд-транспорта я получил гораздо больше реальных знаний и навыков. Плюс, к дипломной работе изучил ROS-2 и работу с ним. Ни о каких реальных знаниях современных технологий речи просто не идет. База и только база. Все остальное на саморазвитии. Поэтому в той же Германии студенты учатся на бакалавриате 6 лет вместо трех, параллельно работая и получая знания и навыки, связанные с современными технологиями и протоколами.

В университетах студентам просто не дают возможность работать с какими-либо технологиями или протоколами - обучение этому возлагают на юудущего работадателя. В результате, за семестр 14 недель по 11 пар в неделю в сумме в немецком вузе против 17 недель по 16 пар в российском. Результат сравнивать не стоит - есть вероятность сильно разочароваться. Но на выходе из немецких ВУЗов получаем хоть и отчасти хреновых, но специалистов, которых можно чему-то научить со здоровой психикой и готовых к дальнейшему саморазвитию, а из российских ВУЗов получаем специалистов с вроде бы хорошим багажом знаний и навыков, которые насильное впихнуты через "не могу" в мозги, что там творится каша, с подорванным психическим здоровьем (не всегда и не везде, но имеет место быть) и отторжением идей дальнейшего саморазвития, так как они просто устали морально учиться. И в результате дилемма: а кто вам, как работадателю, больше подойдет в долгосрочной перспективе (если у вас, конечно, вакансия не "здесь и сейчас", а на многие проекты вперед)?

DvoiNic

20.12.2022 15:33+2В университетах студентам просто не дают возможность работать с какими-либо технологиями или протоколами

не дают возможность — это запрещают, отгоняют, палками бьют?17 недель по 16 пар в российском

16 пар — это на пятидневке 4.8 часа в день. Неужели это так сильно ломает нынешнюю студенческую психику?из российских ВУЗов получаем специалистов с вроде бы хорошим багажом знаний и навыков, которые насильное впихнуты через «не могу» в мозги, что там творится каша

насчет каши — согласен. четкой структуры всего обучения (взаимосвязей предметов, учебных курсов. структуры.) у отечественных ВУЗов или нет, или она до студентов просто не доводится: «учи что сказали», «так положено»

YourgenAP

20.12.2022 16:07+4не дают возможность — это запрещают, отгоняют, палками бьют?

В данном контексте "не дают" в смысле "не предоставляют". Через те же курсовые или проектные работы (есть с чем сравнивать в ВШЭ и Бауманке).

16 пар — это на пятидневке 4.8 часа в день. Неужели это так сильно ломает нынешнюю студенческую психику?

16 пар - усредненное. Где-то 16, где-то 17, где-то и все 19. Помимо этого еще лабораторные и домашние работы, которые надо сдать вовремя, а для этого поймать препода (из того, что слышал от одноклассников и друзей, кто учится в российских вузах). Так что к 16 парам добавляем еще работу дома. По всем предметам, которые есть в семестре (а это 6-8 по учебным планам). Ну и получается завал, в котором можно начать тонуть и сломаться.

у отечественных ВУЗов или нет, или она до студентов просто не доводится: «учи что сказали», «так положено»

Скорее второе, чем первое. По крайней мере в сравнении Бауманки и ВШЭ с техническим университетом Берлина, где про структуру обучения и взаимосвязь предметов если и слышали, то явно не вслушивались. Хотя те же функциональные языки нам дали за 4 недели, у моего знакомого в Бауманке на это целый семестр.

DvoiNic

20.12.2022 16:24+2В данном контексте «не дают» в смысле «не предоставляют». Через те же курсовые или проектные работы (есть с чем сравнивать в ВШЭ и Бауманке).

В каком-то там ЧПИ во второй половине 80-х мы вполне могли подойти к преподу и сказать — а давайте мы сделаем вот это. Не помню такого, чтоб нас не поддержали. Т.е. мы просто проявляли инициативу.16 пар — усредненное. Где-то 16, где-то 17, где-то и все 19.

если 16 усредненное, а «где-то 19» — то где-то и 13… лабы входят в учебное время, в эти «13-19». домашки — да, есть. еще часа три. т.е. и получаем стандартный обычный привычный для всех трудящихся 8-часовой рабочий день.По всем предметам, которые есть в семестре (а это 6-8 по учебным планам)

у нас в воспитательных целях на первом курсе сделали так: дали курсач (или аналогичное задание) со сроком сдачи 6 недель. через неделю дают по другому предмету задание со сроком сдачи 5 недель. еще через неделю — по третьему, со сроком 4 недели… в общем, в срок сдачи надо было сдать штук 5-6 заданий за пару дней. смогли либо те, кто работал планомерно и размеренно, либо «сумасшедшие гении»(которые смогли сделать это все, как водится, «в последнюю ночь перед»). Это хорошо научило всех работать более-менее планомерно. называли это почему-то «метод бульдозера».Скорее второе, чем первое.

у некоторых первое, у некоторых второе. причем даже на разных факультетах одного ВУЗа.

Samedi_Da_Kapa

20.12.2022 16:52+2Не буду говорить за всю Одессу, но по тому как у меня было расписание - далеко не всегда это было 4,5 - 6 часов одним куском.

У меня были окна, у меня были выходные дни. Соответственно бывало, что один день это выходной или лайтово 3 пары, а другой день 6 пар одна за одной. Или допустим 4 пары, но с окном посередине. Или с переходом в другой корпус за несколько кварталов на большом перерыве в 20 минут. Иногда это были занятия неделя через неделю и я мог одну неделю учится 3 дня, а вторую 5.

А еще были домашние задания, курсовые и материал для самостоятельной проработки. В результате выходило, что нагрузка была на 6 - 7 часов в день при пятидневке.

Теперь вспомним, что уже были исследования про продуктивные часы в интеллектуальном труде и сопоставим 4-5 часов из них с 6 -7 часами, которые выходили у меня. И поймем причину таких проблем с психикой.

DvoiNic

20.12.2022 17:05+2ну я как бы тоже учился...А после учебы еще работал на кафедре, да еще по хозтемам в ОНИЛ. ну и позже — еще и программы писали для Корветов, которые продавали. (что давало вкупе с повышенной стипендией денег больше, чем у инженера-выпускника)

Это всё не мешало общаться с противоположным полом, заниматься чем-то вроде спорта, дежурить в ОКОДе, читать худлит и даже изредка, хм, пьянствовать на днях рожденья и т.п…

Психика в порядке...

Samedi_Da_Kapa

20.12.2022 18:12+10В нашем с вами диалоге мы теряем много контекста - где именно учились мы с вами, насколько глубоко погружались в рабочие темы, насколько глубоко прорабатывали темы и многие другие аспекты.

В моей группе был товарищ, который действительно впахивал на каждой паре, работал с научником очень глубоко по каждой из работ, не следил за балансом, не занимался спортом и не уделял внимание противоположному полу. В результате был инсульт перед дипломом. По профессии он работать не пошел.

Я не говорю, что что инсульты был только и исключительно из-за образа жизни - я не врач. Но на мой взгляд это было взаимосвязанно.

Мой комментарий был оставлен с целью показать, что если в вашем субъективно опыте у людей не было проблем, то это не значит что у других это не так.

DragonWerewolf

22.12.2022 18:10+2Когда я учился, у нас было по 5-6 пар в день. в субботу 7 (две последние практика по группам раз в две недели). После 4 курса стало полегче, там было уже по 4-5 пар, но к тому моменту я уже успел подустать от того, что за 4 года мои практические навыки программиста никуда не двигались и ушел работу работать.

По поводу каши, на первом курсе по физике что-то втирали про дивергенцию по ротору и так далее, в общих чертах понятно, но вот все эти значки и как их применять сразу после школы - было совершенно не ясно. Хорошо хоть на третьем курсе на математике объяснили, стало интересно перечитывать конспекты двухлетней давности и даже понятно что из чего выходит.

Огромный объем времени сжирали работы по социологии, психологии и педагогике, культурологии, культуре речи, русскому языку и еще десяток предметов, назначение которых для получения навыков по программированию на популярных языках казалось весьма сомнительным. Хотя сопромат и термех были интересные, но вот инжинерная графика с вечными чертежами от руки казались кошмаром. Спустя два года на встрече с преподавателями было очень интересно узнать, что можно было сдавать работы в CAD а не от руки, но к тому времени уже даже эмоций не осталось, только вечное желание поспать.

Ну и вишенкой на торте, а на что жить-то, если все доступное время жрет учеба. Хобби только по праздникам, прогулки только от универа и домой. из выходных только воскресенье, когда надо делать рефераты, писать РГР-ки, делать чертежи и прочее

DvoiNic

22.12.2022 19:51+1странный у вас был ВУЗ1.у нас такую нагрузку считали чрезмерной (я даже не помню более 5 пар, которые были крайне редко), обычно не более 4, в субботу 2 или 3. Советские времена. (я уже в теме писал, что нам не разрешили включить в индивидуальный учебный план пару предметов, потому что мы превышали разрешенное учебное время)

2. страннен разрыв программы, когда на одном предмете применяют понятие, а учат понятие на два курса позже. у нас, кстати, дивергенции и роторы были в 3 семестре (как и у сына), что там тянуть до 3 курса- непонятно.

3. набор лженаук™ у нас был более ограничен марксизмом-ленинизмом (зато преподы были ядренее.). У сына тоже не наблюдал такого зоопарка

4. сопромат и термех на ИТшных специальностях? у нас на инженерной этого не было. (читал учебники по ним совершенно добровольно, из интереса, для общего развития, ну и иногда для помощи в компьютеризированных расчетах товарищам со специфических специальностей)

5. инграф была у всех инженерных, а КАДов тогда не было. сейчас у околоИТшных специальностей (судя по сыну и его друзьям) ее нет.на что жить-то, если все доступное время жрет учеба

да, это сейчас основной вопрос. у нас теоретически можно было прожить на стипендию (она была 55, ну и обычно еще +15%, такая зарплата была у малоквалифицированых. Плюс столько же зарплата лаборанта, плюс еще — у меня получалось вообще неплохо, но это скорее исключение, у большинства 55) — но мы были, наверное, последними, кто мог прожить на стипендию. уже под наше окончание СССР издох, инфляция и всё такое. Но вот сын работает со 2 курса, порой со скрипом, но успевает — ну нет у них описываемой вами учебной нагрузки. И у племяшей нет (1 и 4 курс совсем другого вуза совсем других специальностей, далеких от инженерных).

странный ВУЗ.

YuriPanchul Автор

20.12.2022 19:16+1Во-первых, навык, который требуется для решения моих задачек, в учебниках в Стенфорде и MIT есть, в частности начиная с 464 страницы в учебнике ниже (он стоит в стенфордском книжном магазине как требуемый учебник).

Во-вторых, не все студенты учатся 6 лет быть только "хорошими людьми" (это не професия). Есть и те, которые делают качественные open-source проекты, например открытый GPU из многих RISC-V ядер в Georgia Tech ( https://vortex.cc.gatech.edu/ ) и открытая система разработки микросхем OpenROAD в University of California San Diego ( https://github.com/The-OpenROAD-Project - см. вклад MS students https://theopenroadproject.org/our-team/ )

Tim_L

21.12.2022 09:01+7Бакалавриат 3 года??? Кудаааа???? Я в 2014 закончил техникум, где учился 4 (!) года и выпустился техником (!). Когда пошёл бакалавриат за 4 года, я уже был очень удивлен. А тут 3. И да, учился я, в основном, по 3 пары в день 6 дней в неделю. Зачастую было 4 пары, редко 5. Времени хватало и на учёбу, и на спорт, и на какие-то свои проекты, типа цифрового термометра на pic16f84a с ds18b20. И диплом у меня красный со средним баллом 4.99. Потом специалитет 5 лет по 3-4 пары 6 дней в неделю. И так же, хватило времени на диплом со средним баллом 4.7, патент и пару свидетельств на ПО. О чем вы вообще речь ведёте, я не сильно, если честно, понимаю. По мне, если специальность и сфера интересны, то находится время на всё. А если мама с папой запихнули или поступил "хоть куда-нибудь, лишь бы корочка была", то и ожидать нужно соответствующего.

YourgenAP

21.12.2022 14:54+1В Западной системе образования (и тут дело не в том, Болонская она или нет - это лишь унифицирование ученых степеней) бакалавриат длится три года, магистратура - два. Выведенный в Германии из использования, но который хотят вернуть, Диплом (аналог специалитета) длился 4 года. Меньше времени за счет того, что нет иностранного языка, права, философии, экологии, экономики и родного (в случае Германии немецкого) языка, как это есть в тех же российских ВУЗах. Но по факту мало кто учится 3 года на бакалавриате - в среднем 4-4,5 по статистике моего университета. Причины две: 1) студенты заведомо берут меньше предметов в семестр, чтобы оставалось время на себя любимых и чтобы не перетрудиться (без шуток и сарказма - все серьезно) и 2) студенты не могут просто-напросто за 3 года взять все те предметы, которые хотят и которые им интересны, потому что происходит наложение пар (читай ниже почему).

У меня на магистратуре 11 пар в неделю (столько же было на бакалавриате, к слову). Но одним из важных аспектов является то, что расписание в Европе сами себе составляют студенты на основании того, когда преподаватели поставили пары по своим предметам в расписание (а из этого вытекает наложение предметов - никакого согласования расписания между кафедрами и факультетами просто нет: когда преподу удобно, тогда и будет поставлена пара и пофиг, что у студентов может возникнуть наложение, в следующем году возьмут второй предмет тогда). В результате, в моем случае, в текущем семестре у меня в понедельник 1-2 и 5 пары, во вторник 2 и 4-5 пары, в среду 3-5 пары, в четверг 2 и 4 пары, а пятница свободна. И за счет этих перерывов студенты в Германии действительно экономят свое свободное время вечером, делая домашки на больших перерывах, а вечером могут пойти в зал позаниматься спортом или на пробежку, ну или потусить где-то с друзьями.

Для сравнения в России, из того что я знаю по топовым ВУЗам (МГУ, ВШЭ, Бауманка), у студентов пары идут одна за другой, потому что так составлено специально расписание умными специально обученными для этого людьми. И это 5 дней в неделю 3-4 пары. И прибывание в универе с 8:45 до 14:45 или 16:30 (три или четыре пары соответственно), а потом доехать до дома (а это от 15 минут до полутора-двух часов, как повезет) и еще доделывать лабы/дооформлять чертежи/доделывать работы с семинаров/делать домашки, на что тоже уходит время. У кого-то больше, у кого-то меньше. Ну и результат получается у кого-то лучшего, у кого-то хуже.

Ну и важен вопрос отношения к учебе в целом и качества преподавания в самом ВУЗе. Где-то могут раслабленно, спокойно, не напрягаясь относиться к образовательному процессу, а где-то это все превращается в ад. Ну и исходя из этого формируется отношение к учебе и желание заниматься еще чем-либо у студентов. Даже на примере своих одноклассников и знакомых прекрасно это наблюдаю: кто-то игровой сервер успевает пилить, кто-то со Сколково и ЦЕРНом работать, а кто-то просто выживает.

DvoiNic

21.12.2022 15:01А чем в германских учебных заведениях определяется набор предметов, из которого студент выбирает? Как там определяется полученная «специальность»? (или ее как таковой — нет?)

amartology

21.12.2022 15:07А чем в германсих учебных заведениях определяется набор предметов, из которого студент выбирает?

В основном желанием студента.Как там определяется полученная «специальность»?

Набором, из которого студенту дан выбор.

YourgenAP

21.12.2022 15:44+1Зависит от направления очень сильно. В общем и целом, есть набор обязательных предметов (для "информатики в машиностроении" это матан до интегралов по объему, линал+ангеом, диффуры, ЧМы, статика+сопромат, кинематика+динамика, компьютерно-ориентированная математика (алгоритмы на массивах, дискретка, хеширование, функицональные языки и машина Тьюринга), системное программирование, основы электротехники и термодинамика; для обычной "информатики" - матан, линал, диффуры, ЧМы, устройство полупроводников, три или четыре предмета вокруг программирования софта и систем). Далее идет набор обязательных на выбор (в "информатике для машиностроения" это вариации предмета "Измерительная техника и сенсоры" от разных кафедр под разным названием и вариация предмета "Теория автоматического управления" от разных кафедр под разными названиями. Затем добровольно-обязательных: список из примерно 150 предметов по разным направлениям, релевантным для специальность (от систем автоматизации до конструирования и аэродинамики для "информатики в машиностроении"). И еще два предмета на свободный выбор.

По факту специальность определяется как базовая, исходя из базовых предметов и названия направления подготовки, и как специфическая, исходя из предметов, указанных в дипломе. Иными словами, с информатики в машиностроении тебя всегда возьмут программировать любой софт для общих систем, но никогда не возьмут программировать специфический софт, который требует определенных знаний (к примеру, писать логику автопилота и автомата тяги летательного аппарата, так как для полной картины нужно знать еще кучу всего сверху о механике полета и автоматическом управлении управляющими поверхностями ЛА)

А на вопрос о наборе предметов, то обязательная база + минимум 6 предметов из 150 добровольно-обязательных + минимум 2 на свободный выбор.

DvoiNic

21.12.2022 17:00+1Понял, спасибо. Примерно то же видел в системе MIT'а.

Если студент идет не «за дипломом», а «реально учиться» — на мой взгляд, это весьма неплохая система.

Буду очень признателен, если дадите ссылку на список «150 добровольно обязательных», и «для свободного выбора».

YourgenAP

21.12.2022 18:24+3Ссылка на регламент "Информатики в машиностроении" Технического Университета Берлина. С 5ой страницы - полный перечень всех предметов, с пункта 5 - добровольно-обязательные (насчет 150 перегнул, конечно, но выбор все равно большой). "Свободный выбор" - любой предмет любого факультета любой кафедры. Хоть "Микроэкономика", хоть "Управление персоналом", хоть "Психология на производстве". Можно также брать предметы и в других университетах - знаю людей, которые посещали предметы в Свободном Университете или Университете имени Гумбольдтов.

Tim_L

21.12.2022 15:45+1Ну в целом согласен, я как раз и вел к тому, что способность обучаться, как и качество специалиста после выпуска, зависит в главной степени от самого студента, чем от учебного заведения. Если гореть своей темой, можно и без учебного заведения освоить необходимое.

YourgenAP

21.12.2022 18:31+2Ой не скажите. Абсолютно уверен, что студент с машиностроения в Бауманке знает больше чем студент с машиностроения ТУ Берлин при равных приложенных усилиях. Просто по объему знаний в том же сопромате (ровно в два раза меньше - я сверял экзаменационные вопросы и свой уровень знаний).

Насчет IT ручаться не буду - там сравнивать сложнее из-за разных предметов.

edo1h

21.12.2022 21:01+5а почему тогда мы покупаем (покупали?) у сименса турбины и ласточки, а не наоборот?

YourgenAP

21.12.2022 21:25+3Потому что потом Сименс уже сам "дообучает" молодых специалистов через их прикрепление к проектам, где опытные сотрудники уже делятся опытом. Это часть карьерного роста. Серьезно.

amartology

21.12.2022 21:37+2Потому что компетенции в инжиинринге и компетенции в бизнесе — это не одно и то же. Да и инвестклимат немного различается.

edo1h

21.12.2022 21:59+4честно говоря, не понял что вы пытаетесь сказать.

конструкторам сименса надо ездить учиться у конструкторов отечественного чуда?я сам далёк от темы, но на мой непрофессиональный взгляд в механике отечественные конструкции тяготеют к «кондовым» решениям, а западные более изящны.

amartology

21.12.2022 22:30честно говоря, не понял что вы пытаетесь сказать.

Что коммерческая успешность компании «Сименс» определяется далеко не только талантами ее инженеров, и что по тому, кто у кого что закупает, нельзя впрямую судить о качестве подготоки инженеров.

khajiit

22.12.2022 10:27+4Вероятно то, что если даже самых способных и подготовленных в мире инженеров использовать исключительно для шевеления говна, то опыт у них будет только в в этой сомнительной специализации.

И какое-либо сравнение быстро станет совершенно бессмысленным.

Как сравнение поездов Siemens, пачками колесящих далеко за пределами родной Германии, с очередным фейслифтингом для Аллы Пугачевой.

YourgenAP

21.12.2022 22:48+3Я работаю в компании Codewerk, которая работает в партнерстве с Сименсом, Алстомом, Штадлером и Талесом (в разных проектах). Все технические решения (хард) - это развитие уже имеющихся. Даже новый ICE 3 neo (простите, только на немецком нашел) - это развитие старого доброго ICE 3, он же Siemens Velaro, он же Сапсан. Из глобально новых решений - это системы управления. И ведущим разработчикам 40+. А помогают им молодые "специалисты", которые одновременно с этим учатся тому, что не дал университет. Так и получается, что через передачу знаний от старших разработчиков к младшим возникает преемственность знаний и поддержание высокого качества разработки

Refridgerator

22.12.2022 05:59+5а почему тогда мы покупаем (покупали?) у сименса турбины и ласточки, а не наоборот?

Потому что грамотные инженеры улетают из России в Сименс, а не наоборот. Я таких двоих лично знаю, и подозреваю, что это правило, а не исключение.

Tim_L

21.12.2022 15:57А вот теперь возникает, как мне кажется, закономерный вопрос: а всем ли поступившим нужно высшее образование? Смысл его получать, тратить деньги, нервы, а главное, время, чтобы потом идти работать не по специальности? Может было бы проще закончить колледж с какой-то более приземленной специальностью? Если понравилось, как, например, получилось у меня, пойти дальше в вуз, магистратуру, аспирантуру и т.д. Я вот выпускался вообще сисадмином по специальности 23.01.01. Потом пошёл дальше в безопасность, правда вопрос "нравится или не нравится" не стоял, я сразу знал, что это моё.

DvoiNic

21.12.2022 17:09+1Вообще, высшее образование дает (ну да, сейчас в меня опять полетят

струикопья) «общий культурный уровень», «кругозор» и все такое. Т.е. «общество, где у всех такое образование» должно быть более развитым.

Работать по специальности — тут сложнее: кто-то разочаровывается (в специальности, или вообще «в работе головой»), кто-то работает по смежной, кто-то дообразовывается (самостоятельно, курсы, вторая вышка) до другой. Даже в советские времена, где [по идее] каждому выпускнику было уготовано обязательное место работы на 3 года — и то по специальности работали далеко не все.

Ну и большинству действительно не нужно по тем или иным причинам (от «узкоспециального интереса» до «неспособности») высшее, и вполне будет достаточно среднего профессионального или среднего специального.

YourgenAP

21.12.2022 18:39+2высшее образование дает «общий культурный уровень», «кругозор» и все такое

Очень спорный вопрос насчет культурного уровня. Кругозор расширяет. В условиях российских ВУЗов.

Т.е. «общество, где у всех такое образование» должно быть более развитым

Немецкое общество, где каждый занимается своим делом (и, кстати, чаще всего по специальности), очень неплохо себе поживает, хотя и есть свои маразмы, но тут вопрос к Бундестагу.

Ну и большинству действительно не нужно по тем или иным причинам (от «узкоспециального интереса» до «неспособности») высшее

В результате по внутренней статистике ТУ Берлин процент незаконченного обучения (нем.: Studienabbruch - дословно "Отмена учебы") на бакалавриате составляет примерно 60%, варьируясь от направления к направлению - на машиностроении доходит до 75%, на производственном менеджменте не доходит и до 15%. А для того, чтобы поступить в университет, нужно закончить гимназию, сдать итоговые экзамены и на многие направления еще иметь средний балл выше минимального (Информатика, например, держится на 2.3, а Машиностроение на 2.5 последние несколько семестров - в немецкой системе 1.0 - это идеально, 5.0 - неуд).

mbobka

20.12.2022 15:43+15После Стенфорда я пожалуй поищу место получше, чем ваша шарага. И унизительное 2+2 не надо будет реализовывать.

punzik

20.12.2022 16:36Про какую шарагу речь?

mbobka

20.12.2022 16:43+5Посмотрите в профиле автора. Какой-то очередной стартап.

punzik

20.12.2022 17:06+16Нуу, в узком кругу разработчиков RTL не знать кто такой Юрий Панчул как-то уже неприлично, по-моему. Вы точно имеете отношения к плисам и пр?

mbobka

20.12.2022 20:42+9Я не имею никакого отношения к плисам и пр.

Однако я понимаю что такое Стенфорд. И даже мобильное отделение Samsung, и работа с самим Ю. Панчулом -- это шарага по сравнению со Стенфордом. Мне кажется что он даёт более интересные перспективы. А вот если вылететь из Стенфорда, то да, можно и к Ю. Панчулу пойти, но тогда не могу понять почему он удивляется качеству.

punzik

20.12.2022 20:51+5Вы так говорите, как будто Стэнфорд выпускает готовых Клиффордов Каммингсов, не меньше.

amartology

20.12.2022 21:05+9И даже мобильное отделение Samsung — это шарага

Простите, а вы много знаете более передовых и сложных с технической точки зрения чипов, чем изготавливаемые по нормам 5 нм процессоры мобильных телефонов?

Balling

21.12.2022 21:484 нм. Причем у Samsung 137 MTр/мм2 против 146.5 у TSMC и шаг затвора 57 нм против 51. Так что Samsung продувает везде.

amartology

21.12.2022 22:34Один пример нашли, отлично. А хотя бы десять найдете? Даже без учета того, что ваш пример некорректен, потому что с точки зрения инженера-разработчика среднего звена разница между процессами 4 нм и 5 нм минимальна.

AlexanderS

21.12.2022 01:15+5Мне кажется что он даёт более интересные перспективы.

А как тогда получается такое противоречие, что выпускник Стенфорда не может реализовать банальщину? То есть вы берёте крутой математический университет, который математиков выпускает, даёте выпускнику задачу про 2+2*2, а у него получается 8. У будущего математика…

Причём я не спорю, что диплом Стенфорда реально даёт перспективы. Но вам-то привели яркий пример общемировой деградации системы обучения, о котором уже только ленивый не писал. По вашему в Стенфорде от этого явления что ли стены защищают?

И пожалуйста, больше не пишите, что Samsung — это шаражкина контора в научно-инженерном плане. Вы тем самым выдаёте свою просто чудовищную некомпетентность в сфере разработки электроники в целом и в науке в частности.

mbobka

21.12.2022 06:37-2Самсунг огромная корпорация, которая начала с торговли рисом, а теперь производит всё что угодно начиная от электробритв и заканчивая огромными кораблями, а ещё у них есть собственный парк развлечений.

Так вот у г-на Панчула в Самсунг есть шарашкина конторка, укромный уголок под лестницей на огромном предприятии, и не более того. И говорить о каких-то перспективах работая с ним нельзя, ни в научном плане, ни в плане собственного развития.

AlexanderS

21.12.2022 13:57+5А ещё у самсунга несколько десятков центров R&D раскиданных по всему миру. И он является одним из четырёх крупнейших мировых вендоров памяти NAND, проводя полные научно-исследовательские циклы по её развитию — не думаете же вы что технологию TLC самсунг освоил просто почитав об этом в периодике, походу отмахнувшись от всех полупроводниковых и квантовых эффектов, возникающих при уменьшении всех этих нанометров. Рисом торговали и парк развлечений есть, ага…

Хотите заниматься реально наукой — идите в MIT или Стэнфорд, поступайте в магистратуру и оставайтесь на кафедрах. Чего вы с чистой наукой лезете в прикладную сферу? Хотите уметь писать энергоэффективный высокоскоростной и валидный код описания работы логической схемы — как видно, не факт что Стэнфорд в этом поможет, в отличии от того же Панчина или работы в Самсунге. У вас слишком высокомерное и даже спесивое отношение к окружающему миру. При таком подходе, конечно, никаких перспектив нигде видно не будет, кроме тех где есть узнаваемый А-бренд. А делать далекоидущие выводы о «собственном развитии», при этом активно хейтя, признанного спеца в сфере только лишь за то, что он поломал вашу картинку мира идеальных брендов… «Мы вас услышали, ваше мнение очень ценно для нас».

edo1h

21.12.2022 21:42Мне кажется неверной дихтомия «чистая наука или прикладная сфера». Они тесно переплетены друг с другом, одно без другого не может развиваться.

Balling

21.12.2022 21:44А ещё у меня Galaxy S22 Ultra на чипе Snapdragon Gen 1, созданный в фабрике Samsung. Греется сильнее, чем бы грелся от TSMC (как раз 8+ Gen 1).

amartology

21.12.2022 22:35+2греется сильнее, чем бы грелся от TSMC

но слабее, чем если бы был произведен на заводе «Микрон». И вообще мы говорили об инженерах-разработчиках, а не об инженерах-технологах.

Balling

21.12.2022 22:40Не уверен, что 4 нм можно перенести свободно на 22 или сколько там у микрона. Его надо переверефицировать...

И Arm вряд ли даже даст им 4 нм верефицированный дизайн.

amartology

21.12.2022 22:49У Микрона 90 нм.

А процессору не обязательно быть ARM. Юрий вон проприетарные GPU ядра разрабатывает.

И Arm вряд ли даже даст им 4 нм верефицированный дизайн.

Байкалу и Элвису вполне себе давали подходящие для 5-7 нм дизайны.

ViacheslavNk

21.12.2022 13:31+1Но вам-то привели яркий пример общемировой деградации системы обучения, о котором уже только ленивый не писал. По вашему в Стенфорде от этого явления что ли стены защищают?

А может это быть “ошибкой выжившего”? Можно учиться в Стэнфорде и по выпуску быть менее квалифицированным (в контексте разработки FPGA) чем выпускник какого ни будь регионального вуза, много (да фактически все) зависит от студента, его желания и мотивации. Кто-то отслушал лекции, выполнил минимальную практику, получил зачет и пошёл дальше, а кто-то сделал все тоже самое, но еще закопался в книги и теорию поглубже, сделал более сложный курсовой проект.

AlexanderS

21.12.2022 14:11Естественно может. Тем более мозги у всех по-разному работают. Один быстрее сообразит, другой — медленнее. При использовании моделирования поведения схемы вышеприведённая задача решаема в принципе)

Но тот факт, что уровень «соображаемости» падает это «может» всё равно не оспаривает. И если 10 лет назад подобную задачу решило бы сразу условно 85% испытуемых, то сейчас — не более 60% (цифры взял с потолка, просто для демонстрации условного разрыва). Это очень хорошо описывает статья К вопросу о математических способностях студентов или как учить переполненный мозг. И Стэнфорд это или всеми забытый ВУЗ в какой-нибудь провинции — роли не играет. В независимости от того, что у некоторых на название Стэнфорд сразу какая-то реакция агрессивного отрицания проявляется.

YuriPanchul Автор

21.12.2022 02:33-3Приведите примеры интересных перспектив. Даша Навальная?

mbobka

21.12.2022 05:36+10Неожиданно. Оказывается Вы эксперт по политике, а не по ПЛИС.

Nahrenako

21.12.2022 05:58+17Вполне ожидаемо. В тексте преступная война глумливо названа наступившей «международной напряженностью».

YuriPanchul Автор

21.12.2022 06:56+1Просто пришло в голову. Но вы опишите примеры интересных перспектив (я без подколок). Мне интересен взгляд на процесс и цель обучения с разных сторон, я вобще тусовался с самыми разными стенфордцами: как техническими (отцом ИИ Джоном Маккарти, столпами микроархитектуры и автоматизации проектирования Джоном Хеннесси и Джиованни де Мичелли), так и с Макфолом его подопечными которые писали статьи про социологию и счастье. То есть я признаю разные вгляды на вопрос.

mbobka

21.12.2022 07:43+17После упоминания Даши Навальной с Вами обсуждать больше нечего. На это есть ряд причин:

1. Она не политик, не публичное лицо и ни какой-либо общественный деятель. Она всего лишь дочь своего отца. И упоминать тех или иных лиц только за то что у них есть какие-то известные родители -- отвратительно.

2. Это упоминание содержит скрытый намёк, что женщинам инженерные, либо научные дисциплины недоступны, и что это исключительно мужская отрасль, что так же отвратительно.

YuriPanchul Автор

21.12.2022 08:09+2(2) вам показалось. Например конструкции из коммента https://habr.com/ru/post/706484/comments/#comment_25030966 меня обучила женщина

ViacheslavNk

21.12.2022 13:35+1Ну а к слову о ее перспективах, если она способна и самое главное трудолюбива, то перспективы весьма неплохие, преимущество Стэнфорда (а также вузов Лиги Плюща), то что там преподают лучшие преподаватели (специалисты в своих отраслях) в мире, второе там учатся дети очень влиятельных людей в мире, так же там учатся просто очень талантливые и умные люди, это реально очень перспективная среда.

mbobka

22.12.2022 08:53Теперь я знаю кто такой @YuriPanchul, и после беседы с ним его авторитет скатился до 0.

eugenk

22.12.2022 18:51+4Такой потери авторитета Юрий просто не переживёт. Особенно у личности с отрицательной кармой и нулём публикаций.

amartology

20.12.2022 17:25+10акой-то очередной стартап.

С каких пор мобильное подразделение Samsung стало «каким-то стартапом»? )

punzik

20.12.2022 21:29+7Почему, кстати, унизительное? Задание не такое простое, как может показаться, там масса нюансов.

edo1h

20.12.2022 23:23+5потому что показывает некомпетентность кандидата?

mbobka

21.12.2022 08:45+4Не показывает, а тычет. Оно призвано доказать кандидату его "некомпетентность", принизить все достоинства кандидата, и при этом показать собственное превосходство интервьюера, потешив его собственное ЧСВ, что собственно в статье и изложено.

punzik

21.12.2022 09:03+7По-вашему нужно задавать вопросы, на которые кандидат заведомо знает ответ? Зачем такое собеседование?

Brak0del

21.12.2022 09:46+2Задание всего лишь проверяет понимание определённого популярного паттерна проектирования. Если перевести на программистский, то это по сложности как если на собесе С# программиста попросили бы реализовать паттерн singleton например. Вроде всё просто, но вписаться всегда есть где.

edo1h

21.12.2022 21:06как если на собесе С# программиста попросили бы реализовать паттерн singleton например

ну так было бы странно, если свежий выпускник приличного вуза уже забыл (или хуже того — никогда не знал) что такое этот самый singleton.

ну или вроде бы как зная не смог реализовать, ещё лучше.

eugenk

22.12.2022 03:10+1Прошу прощения, немного не понял, почему "тычет", "принижает" и т.п. ??? Я вот не знаю что такое AXI и AHB. Но задание счел реально вполне практичным и интересным. Из двух источников, не синхронно, приходят данные. Между ними попарно делается какая-то операция, и результат так же не синхронно забирает приёмник. Тут например сразу виден подсчёт входных/выходных данных, выходной FIFO-буфер и согласующие сигналы готовности. Типичная задача на буферное устройство между двумя шинами. Мне кажется такие задачи надо уметь решать в обязательном порядке, ВНЕ ЗАВИСИМОСТИ от того знаешь ты или нет соответствующие шины и протоколы. Я бы не взял на работу кандидата, не сумевшего с этим справиться.

Если хотите, можете попытаться решить мою задачу. Она более проста технически, но требует одной немного нетривиальной догадки.

Есть блочная синхронная RAM (в том же чипе от Xilinx хотя бы). Требуется на её основе спроектировать стек. Стек должен выполнять три операции:

PUSH - поместить в стек

POP - вытолкнуть из стека

NOP - пустая команда.

В начальное состояние стек устанавливается сигналом сброса. Сигналы опустошения и переполнения стека можно не реализовывать и эти ситуации не отслеживать. НО. Все три операции в любых сочетаниях должны выполняться ЗА ОДИН ТАКТ.

Если попытаетесь делать в лоб, ничего за один такт работать не будет. Нужно догадаться как небольшим усложнением схемотехники эти грабли обойти.

mpa4b

22.12.2022 15:05+1TOS на регистрах, память всегда светит следующим значением в TOS или пишет TOS когда надо. Одновременно пуш и поп -- только смена содержимого TOS :)

eugenk

22.12.2022 18:12Безусловно и это тоже. Но я не это имел в виду. Если после PUSH сразу же, в следующем такте приходит POP, наивная схема на блочной памяти и регистрах даст сбой. Вот мне и интересно, что придумает человек, чтобы обойти эти грабли. Это несложно, но надо все-таки немного подумать.

P.S. Одновременно туда команды не приходят. Каждая команда выполняется за отдельный такт. Либо поместить в стек, либо вытолкнуть из стека, либо ничего не делать.

P.P.S. Реальный стек из реального проекта выполняет значительно больше команд. Причем две из них за два такта (генерируя такт ожидания для остальной схемы). Но тонкое место, требующее сообразительности только это.

mayorovp

22.12.2022 18:18Безусловно и это тоже. Но я не это имел в виду. Если после PUSH сразу же, в следующем такте приходит POP, наивная схема на блочной памяти и регистрах даст сбой.

Э-э-э, а почему?

eugenk

22.12.2022 18:25-1Не знаю... Наверно такова объективная реальность :))))

Напишите наивную реализацию. Запустите на симуляторе. И убедитесь сами. Ваша задача ПОНЯТЬ почему, и как с этим бороться.

И торопитесь. В ближайшее время я опубликую здесь проект, где эти грабли выплыли. Ну а после публикации разобраться с этим будет уже немного не спортивно :)))

mpa4b

22.12.2022 18:48Это вроде стандартно в памятях -- байпасс.

eugenk

22.12.2022 18:59-1Не так всё просто. Советую то же что предыдущему оратору. Напишите наивную реализацию с tos на регистре. Вы описали её совершенно правильно, так что для Вас это будет нетрудно. Запустите на симуляторе. Командами PUSH затолкните в стек несколько чисел. Потом сразу, без перерыва(NOP), дайте команду POP. И увидите что произойдёт.

vikarti

21.12.2022 06:59+1А где сказано что автор только к себе вербует?

А насчет унизительного, я вот эту задачу в поставленных условиях решить прям сходу сейчас не смогу (но понимаю что если человек не может ее решить — более сложные задачи по дизайну чипов видимо тоже не сможет)

edo1h

21.12.2022 20:58+2А насчет унизительного, я вот эту задачу в поставленных условиях решить прям сходу сейчас не смогу

так почитайте соседние комментарии, именно это и считается унизительным: задаются вопросы, на которые можно не знать ответы. дискриминация кандидатов по уровню подготовленности.

eugenk

22.12.2022 05:20Тут дело не в знании ответов на вопросы, а в базовом умении работать с шинами и потоками. Это абсолютно необходимый навык для любого разработчика железа. Если брать пример из более известной области, примерно то же самое, что для программиста на джаваскрипте иметь представление о dom.

edo1h

22.12.2022 07:33Не знаю, как вам это удалось, но вы не распознали сарказм в моём ответе )

eugenk

22.12.2022 08:02Ну с одной стороны я всё-таки не сетка AlphaGo :))))

А с другой и правда считаю, что не стоит человеку задавать вопросы, на которые он может не знать ответов. Типа что делает конструкция А в дальнем пыльном углу языка B, которым я согласно резюме профессионально владею. Откуда мне знать, что она делает если я никогда ей не пользовался ! Я вот например не употребляю на С конструкцию ? a : b. Мне if кажется нагляднее и понятнее. А на верилоге аналогичную конструкцию применяю повсеместно, там она полезна для присваивания на шину. Задавать вопросы надо надо на знание базовых принципов и умение ими пользоваться. И вообще по-моему одна тестовая задачка от дня до недели, лучше тысячи вопросов на собеседовании.

edo1h

23.12.2022 04:43А с другой и правда считаю, что не стоит человеку задавать вопросы, на которые он может не знать ответов

Задавать вопросы надо на знание базовых принципов и умение ими пользоватьсяэ-э-э… мне видится явное противоречие между этими двумя утверждениями.

SkyHunter

20.12.2022 19:11+7Грустно смотреть на статью человека с завышенными претензиями к окружающим, и не удосужившегося прогнать текст статьи через спеллчекер перед публикацией.

Имя Маска по-русски пишется как "Илон".

Слово "репозиторий" - мужского рода.

mpa4b

20.12.2022 20:32+18Задачка, которой@YuriPanchul мучает студентов на собеседованиях, выглядит странно. Постоянно оказывается, что студенты (из тех, что формально верно её решили) не учли какие-то подразумеваемые требования и поэтому их решение плохое. Не знаю, как обстояли дела на реальных собеседованиях, но исходя из написанного выглядит так, что надо было предлагающего такую задачу заваливать дополнительными вопросами.

punzik

20.12.2022 20:54+1Если условие неполное, не зазорно уточнить подробности у интервьюера.

olartamonov

20.12.2022 21:37+2Либо уточняешь, либо делаешь под worst case scenario из разумно допустимых.

«Тут нам в условиях не сказали» прокатывает в школе, не в выпуске крупного вуза.

Arranje

20.12.2022 21:45+8Вы точно внимательно читали статью? Там написано: "Когда я вижу у недавнего выпускника в резюме какой-то из протоколов в котором используется valid/ready, например AXI или AHB "

Опыт работы с протоколами AXI и AHB ПОДРАЗУМЕВАЕТ, что человек решит эту задачу без ошибок часа за 2-3. Если не может, потенциальный сотрудник наверняка соврал в CV.

mayorovp

21.12.2022 09:45+3А вы работу давно искали? Я вот недавно искал, и у меня такой вот диалог состоялся:

HR> скажите, есть ли у вас опыт коммерческой разработки на .NET 6 и EF Core 6?

Я> именно с указанными платформой и библиотекой у меня опыта работы нет, но я работал с .NET Core 3.1 и EF…

HR> вы нам не подходитеЭто я к тому, что из-за таких вот работодателей врать в CV давно стало нормой.

И да, какой вообще опыт работы с протоколами ожидается от выпускника?

Arranje

22.12.2022 23:03Да, наверное вы правы. На практики бывают случаи из-за которых стало нормальным врать в резюме. Но конкретно в данном случае, человека попросили сложить два числа "по нормальному".

Если перекладывать на близкую Вам область программирования, то тут человек заявил, что знает паттерны ООП. Его попросили спроектировать простую архитектуру на основе паттернов, он не смог (например более абстрактные сущности зависят от конкретных и прочие ошибки плохой архитектуры с точки зрения "канонов").

Врать не хорошо. Иногда это приходится делать. Но уж базовые-то вещи, если написали что знаете -- надо отвечать.

YuriPanchul Автор

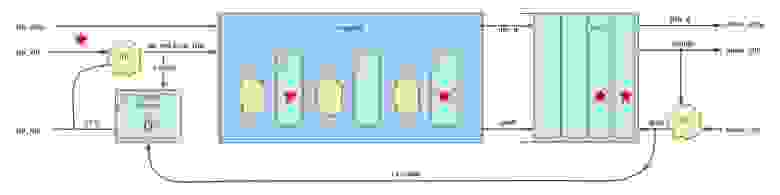

21.12.2022 08:07+6Знаете, если бы я хотел завалить, я бы попросил сделать то же самое, но не для операции комбинационного сложения, а для абстрактного конвейерного арифметического блока с латентностью N. Но это было бы нечестно по отношению к недавним студентам, ибо для хорошей реализации тогда нужно было бы использовать вот такую конструкцию ниже с credit-based flow control, а у них в учебнике (в стенфордском книжном лежит Digital Design: A Systems Approach by William James Dally и R. Curtis Harting) ее нет. (Хотя упоминание credit-based control flow есть в курсе по процессорам в Принстоне от David Wentzlaff).

Но эту конструкцию знают все кто работал в компаниях типа Apple и NVidia, поэтому именно это стоит спрашивать у людей с опытом > 5 лет.

Brak0del

21.12.2022 23:59+3Но эту конструкцию знают все кто работал в компаниях типа Apple и NVidia, поэтому именно это стоит спрашивать у людей с опытом > 5 лет.

К слову, некий канадский FPGA-шник, Charles Eric LaForest, создал справочник, собрав в одном месте много подобных конструкций.

eugenk

22.12.2022 03:53О ! Ценно ! Забил в закладки, чтобы каждый раз не изобретать велосипеды. Спасибо !

Жаль пустых тем ещё много. Ладно, надеюсь мужик не бросит эту деятельность и постепенно будет наполнять ресурс.

eugenk

22.12.2022 03:41Юрий, видя какой тут поднялся срач, мне кажется Вам стоило бы дать точную формулировку задачи. Я её сейчас понимаю так:

module adder ( input clk, //клок input rst, //сброс input[31:0] din, //слагаемые, поступающие парами друг за другом input wr, //запись слагаемого от передатчика output[32:0] dout, //выходные данные output rdy, //выход готовности суммы input rd //сигнал чтения суммы приемником );Нужно принимать данные по сигналу wr, попарно складывать их, буферизовать, и выдавать приемнику сигнал что сумма готова. Я прав ??? Если нет, поправьте пожалуйста.

YuriPanchul Автор

22.12.2022 06:57+1У вас тоже неплохая задача, но я давал другое. Вот:

module stream_adder # ( parameter w = 4 ) ( input clk, input rst, input a_vld, output a_rdy, input [w - 1:0] a, input b_vld, output b_rdy, input [w - 1:0] b, output sum_vld, input sum_rdy, output [w - 1:0] sum, output sum_signed_overflow );

eugenk

22.12.2022 07:32Ну как бы разница не особо большая, в основном сводящаяся к тому, что данные поступают по двум шинам. Ну и шина у Вас более симметричная и "двунаправленная".

Как я понял, передатчики A и B выставляют сигналы a_vld и b_vld, когда их данные валидны. Это аналоги моего сигнала wr. Сумматор сигналами a_rdy и b_rdy говорит передатчикам что готов принять их данные. Этого у меня нет, почему и говорю что Ваша шина более симметрична и "двунаправленна". На выход устройства поступает сумма плюс сигнал переполнения. Устройство говорит приёмнику что сумма готова сигналом sum_vld (мой аналог rdy). Приемник говорит о готовности принять сумму сигналом sum_rdy (у меня аналога нет), и о том что принял данные переходом sum_rdy из активного состояния в пассивное (мой аналог rd).

Да, это наверно лучшее решение чем у меня, хотя чисто эстетически не очень нравятся названия сигналов. Что такое AXI и AHB я не знаю. Точнее слыхал, но было не особо надо разбираться. Надо будет глянуть. Но вообще-то сильно удивительно, что есть выпускники соответствующей специализации, которые на этом сыпятся. Это база...

YuriPanchul Автор

22.12.2022 07:41Все, что необходимо и достаточно знать о valid/ready (это более общая концепция чем AXI) я описал в посте на сходную тему https://habr.com/ru/post/693568/

Но еще более общая концепция - это send/credit_return то бишь credit-based интерфейсы - они у меня тоже разобраны в одном из предыдущих постов в комментах.

eugenk

22.12.2022 08:13Спасибо ! Надо будет погуглить, чтобы не изобретать велосипеды.

Глянул ссылку. Спасибо, ценная статья ! Блин, как я её умудрился зевнуть - ума не приложу... Хабр он такой... Его либо читать от корки до корки, и тогда ни на что другое времени не останется. Либо потом с досадой обнаруживаешь, что пропустил что-то важное и интересное...

YuriPanchul Автор

22.12.2022 09:25+1И вот ветка в другом посте про credit-based flow control - это более гибкая замена valid/ready интерфейсам, которую многие компании применяют как универсальный молоток https://habr.com/ru/post/673916/#comment_24490696

eugenk

22.12.2022 18:39+1Да, прочитал внимательно. Похоже этот велосипед я уже изобретал. Только известен он мне как подсчёт входных и выходных данных. Вообще чувствуется по верилогу давно уже нужно выпускать какую-то книгу про паттерны проектирования. А то такие самостийники как я, каждый раз будут удивляться узнавая, что изобрели велосипед.

YuriPanchul Автор

22.12.2022 19:00+1Да, такая нужда совсем созрела. Меня только вчера спрашивал "не издать ли такую книгу" преподаватель МГУ, а до этого - ВШЭ МИЭМ.

khajiit

22.12.2022 10:35+1Как ни странно, но оба решения и разница между ними оказались понятны даже каджиту, который 20 лет назад читал устаревшие уже тогда справочники по рассыпной логике и что-то издательства "Питер" о до-пентиумных процессорах…

etherblade

22.12.2022 23:38+1В AXI ready может ждать valid (то есть ready может как бы подтвердить valid-ные данные). А вот valid от ready зависить не должен. Тогда и Ваша задачка "по идее" должна решаться достаточно просто:

YuriPanchul Автор

23.12.2022 03:01+1Ну вот, разрушили интригу до того, как просмотры перевалили за 100,000 :-)

Хотя раз так, то дополнительный вопрос: а что если сумматор стоит на критическом пути и мы всё-таки хотим облегчить тайминг?

etherblade

23.12.2022 04:39+2Если без FIFO, то как вариант самодвижушийся конвейер с critical path по ready. Эта схема должна работать:

YuriPanchul Автор

23.12.2022 06:24А то же самое, но с разрывом critical path на ready_sum -> ready_a/b ? :-) Типа чтобы работало если таких блоков сто друг за другом поставить ?

Ну ладно, про skid buffer вы как-нибудь догадаетесь. Годен! :-)

eugenk

22.12.2022 03:50Но эту конструкцию знают все кто работал в компаниях типа Apple и NVidia, поэтому именно это стоит спрашивать у людей с опытом > 5 лет.

Простите, а что в ней такого что > 5 лет ??? Какая разница, сложение у нас или блок с латентностью N ! Все равно есть подсчёт входных данных, подсчет выходных данных и управляющие сигналы записи в блок, чтения из блока приемником, и готовности данных для приёмника. Совершенно справедливо на выходе изображен FIFO-буфер. Обыкновенная задача шинного сопряжения. Я что, могу претендовать на сеньора ???

YuriPanchul Автор

22.12.2022 07:07*** Какая разница, сложение у нас или блок с латентностью N ! ***

(Тут есть одна подсказка о разнице, которую я пока не буду приводить)

*** Совершенно справедливо на выходе изображен FIFO-буфер. ***

Не только. Тут есть еще и конвейер, данные в полете в котором нужно подсчитывать, и всегда посылать не более, чем может в конечном итоге принять FIFO на выходе, если вдруг произойдет останов. Но и не застревать, пока (количество данных в конвейере + количество данных в FIFO) не станет равным размеру FIFO .

*** Простите, а что в ней такого что > 5 лет ??? ***

Ну скажем там: если за 5 лет инженер не сможет это так или иначе понять, то ему дорога только в маркетинг:

eugenk

22.12.2022 07:53+1Ну конвейер это совсем просто. Особенно если он постоянной длинны. Если переменной, зависимой от входных данных, то немного (а возможно много !) труднее, но тоже не бином Ньютона. Впрочем Вы правы конечно. Чтобы в этих вопросах не плавать, надо делать что-то своё. Либо присоединяться к команде, которая что-то делает. Сейчас собираюсь через некоторое время опубликовать здесь на хабре один свой проект. В исходном виде делать это не имею права по NDA c бывшим работодателем. К тому же кое-чем там сейчас сильно недоволен. Так что приходится довольно серьезно переделывать. Это будет упрощенная и сильно улучшенная версия процессора, который уже вполне реально работает во вполне коммерческом проекте. С аппаратным отладчиком и средой разработки на ассемблере (может сделаю ещё компилятор С). Цель проекта - получить очень высокую плотность кода, при достаточно развитой системе команд. Чтобы серьёзные программы можно было запускать чисто на внутренних ресурсах FPGA, без подключения внешней памяти. Все эти игры с Risc-V на FPGA, извините, но кажутся мне немножечко учебными. А это штука совершенно практичная и утилитарная. Тоже хотелось бы чтобы кто-то заинтересовался...

YuriPanchul Автор

22.12.2022 07:57Ну это круто, киньте ссылку потом

eugenk

22.12.2022 08:11Разумеется ! Всегда о Вас тут помню :))))

Писать буду в этом же хабе про FPGA. Так что надеюсь достаточно скоро сможем пообщаться на эту тему.

Myclass

22.12.2022 10:16Я никак не FPGA инженер, но мне интересно. В картинках из книги вижу элементы, каждых из которых выглядит так как ожидаю - по стандартам. Смотрю на ваши картинки, там то мочалки где-то, то and gater тоже в виде какой-то другой формы, но тоже на мочалку похожей показан но не как в стандарте описано. У меня вопрос - это так нормально, не использовать стандартные схемы и формы для описания, а рисовать, как захочется?

amartology

22.12.2022 10:48Облачко для блока логики неясного содержания вполне себе стандарт в индустрии.

Myclass

22.12.2022 17:51Те. AND gater- это логика неясного содержания? А что тогда - ясного?

YuriPanchul Автор

22.12.2022 17:58+1Я просто рисовал картинку в Lucidspark, там значков для гейтов нет, пришлось мочалкой, как combinational cloud. Но вы правы, например для публикуемых учебных материалов это нужно будет перерисовать.

etherblade

23.12.2022 00:30+1Юрий, если бы еще документация была человеческая. Непонятно где этому учиться.

Приведу пример: есть один большой FPGA вендор с синим логотипом, (не буду называть имя вслух) который выпускает очень продвинутые FPGA с технологией "регистры повсюду" - это множество "простых" флопов на фабрике FPGA для оптимизации тайминга. Эти флопы в отличие от регистров в ALM не имеют сигналов reset и clock enable. Казалось бы - идеальное место для предлагаемых Вами конвейеров с кредитными счетчиками.

Тем не менее в официальном гайде для разработчиков приводится вот такая картинка увидев которую сразу становится "очень понятно" как дезайнить конвейеры без backpressure что бы в них использовались флопы с фабрики без clock enable. Вот картинка:

Мало того что решение мягко говоря уступает по удобности использования конвейерам с кредитами так еще и документация подразумевает что каждый прохожий сразу догадается что "Please try to slow down soon" это almost full от FIFO что в инверсии даст ready который можно "притянуть" на вход конвейера. Вот это как пример того что для людей не работающих в Apple и NVidia и не обсуждающих данные детали с коллегами на кофе брейках а просто читающих открытые источники тонкости и трюки хардварного дезайна можно сказать недоступны.

YuriPanchul Автор

23.12.2022 02:16+1Да, это решение с "almost full" которое уступает кредитным счётчикам, так как не учитывает текущее количество транзакций в полете в конвейере.

etherblade

23.12.2022 03:10+1Видимо подразумевается что разница между almost full и full это количество стадий в конвейере. То есть при изменении длины конвейера предлагается переделывать FIFO - издевательство одним словом. С кредитами о таком вообще думать не нужно.

Кстати можно еще на собеседовании просить спроектировать простой AXI stream broadcast с одним входом и несколькими выходами. Вроде на первый взгляд элементарная задача но без кредитов такое реализовать ой как не просто - особенно если приемники находятся далеко от передатчика. Так что да, кредиты о которых Вы так много говорите координально улучшают качество жизни хардварного разработчика.

YuriPanchul Автор

23.12.2022 03:24+1Да, в решении с almost_full - FIFO прийдется делать глубже чем надо, иначе конвейер будет часто простаивать. То есть если в нем 10 стадий и FIFO глубиной 11, то в конвейер нельзя будет запускать даже одну транзакцию, если FIFO не пустое. Так как решение не знает, сколько транзакций сейчас летит в конвейере - там уже может быть 10.

А вот с кредитными счётчиками - никаких проблем, можно минимизировать размер FIFO под пропускную способность и даже если ошибиться с размером, то конструкция будет в худшем случае тормозить, но не переполняться.

YuriPanchul Автор

23.12.2022 03:26+1Да, пример с броадкастом стоит внести и в интервью, и в семинары, спасибо

eugenk

22.12.2022 03:27Если чего-то не понимаешь в условии, никогда не бывает зазорно задать уточняющие вопросы. В статье как я понял речь совсем о другом.

aml

20.12.2022 22:05+23Я могу точно такую же статью написать и про математиков, и про программистов. Все то же самое. Чтобы получить максимум от университета, студенту надо сначала поиграться со всеми технологиями самому (хочешь понять линейную алгебру - сделай 3d-игру, для статистики - поанализируй хотя бы a/b тесты, а лучше ML-модель сделай и поковыряйся с tensordash, хочешь понять сетевые технологии - придумай свой протокол, хочешь понять теорию вычислений - напиши свой компилятор и т.д.). А вот потом на "подготовленную поверхность", на выработанные интуиции теория ляжет, как родная. Тогда получится настоящий учёный или инженер.

kazimir17

20.12.2022 22:45+8Поддерживаю. Мне всегда казалось, что нашим учебным заведениям катастрофически не хватает практики, зато теории хоть завались.

edo1h

20.12.2022 23:33+6мне кажется это усиливается особенностью мышления некоторых людей, которая идёт ещё со школы: целью обучения воспринимается не обучение, а получение оценки.

в результате даже такие сугубо практические предметы, как иностранный язык воспринимаются как никак не связанные с реальной жизнью и получается парадоксальная ситуация: и курс вроде бы не такой плохой, и оценка хорошая; но человек как-то не может прокинуть мостик между предметом «иностранный язык» и общением на иностранном языке.

Ivan22

21.12.2022 15:03+2ты еще скажи что целью работы является не улучшение мира, а получение зарплаты.

DvoiNic

21.12.2022 08:10+2Присоединяюсь.

И добавлю, что (на мой взгляд) значительная причина отсутствия практики в том, что в ВУЗах мало исследовательских работ для промышленности (уж какая есть).

даже в советские достаточно «жирные» времена НИР от промышленности и военных были, но их все равно было мало по сравнению с численностью студентов. Т.е. профессора-доценты работали, а вот для студентов (а вспомогательной работы все равно бывает достатчно) «мест» было мало. А сейчас практически нет. Я, конечно, беру основную часть ВУЗов, без учета топовых — там кафедры яндекса/параллелса/и т.п. дают работу.

victor_1212

20.12.2022 23:55+1> хочешь понять сетевые технологии - придумай свой протокол

серьезно? а чтобы научиться брать интегралы, что требуется?

:)

Samedi_Da_Kapa

21.12.2022 00:40+1Так интеграл это площадь фигуры ограниченной снизу координатной осью, справа и слева пределами(если они есть) и функцией сверху. Разве нет?

victor_1212

21.12.2022 01:29предполагается что все это знают, но не все умеют вычислять (аналитически), а те кто умеют, знают как это делать далеко не во всех случаях

Balling

21.12.2022 21:38А если у вас разрыв посредине? А если интеграл на комплексах? И их сотни типов. От Дарбу до Римана.

victor_1212

21.12.2022 23:13> И их сотни типов

чуть меньше таки, хотя достаточно, но не в этом дело, ув. Александр вероятно кое-что смыслит в математике, поэтому типа предлагалось ему немного подумать какая польза бывает от " придумай свой протокол", imho примерно такая как от "придумай свой интеграл", потому как протокол не более чем инструмент, акцент на функциональности, а не на изобретении еще одного велосипеда

AlexanderS

21.12.2022 00:58+5FPGA инженер с опытом мою задачку про A+B решит.

Ой не факт… Исходя из сложности, чувствуя подвох, будет задаваться вопросами типа: «а в какие ресурсы нужно уместиться», «а на какой частоте схема работать должна», «а какой дизайн в кристалле должен быть». Инженер с опытом в первую очередь будет ТЗ требовать ))) А в конечном счёте, на всякий случай, напишет код, в котором добавление in/out регистров будет параметрическим ибо для облегчения разводки они всяко желательнее, но при условии здоровенных разрядностей выходных/выходных шин, ресурсов это скушает.

eugenk

22.12.2022 05:27Как я понял, должно работать на icarus verilog + gtkwave. Это задача не на проектирование чего-то там, а на понимание базовых принципов.

checkpoint

21.12.2022 01:45+9То числа складываются не попарно, а просто записываются в регистры и на

выход идет их текущая сумма, хотя количество аргументов A и B не

совпадает. То не отрабатывается backpressure и результаты теряются, то

(после того как кандидат написал страницу кода на верилоге) блок

работает на половинной производительности, то есть не может принимать

поток чисел подряд, а ожидает между ними пропуски (gaps). Короче ведет

себя как ChatGPT.Юрий, Вы если причитаете, то не плохо бы сразу показать как делать надо, и как не надо. Короче, не вижу от Вас разжеванных примеров на Verilog-е в данной статье. За одно прошу раскрыть тему сумматоров на примере префиксного. Спасибо.

YuriPanchul Автор

21.12.2022 08:26+4На самом деле это задачка не на тип сумматора (prefix, carry-lookahead итд) а на flow control (см. вариант для не-джунов https://habr.com/ru/post/706484/comments/#comment_25030966 ). Я собираюсь ее разжевать на каком-нибудь будущем семинаре вероятно весной.

byman

21.12.2022 17:37+1Измерить производительность ядра YRV на бенчмарках Dhrystone и CoreMark,

Я запустил Ваше ядро на симуляторе. Оно очень простенькое. Вроде даже умножения нет - у меня вылетает умножение по неизвестной команде. При выборе RV32I и оптимизации О2

Coremark на одной итерации использовал 1 486 325 тактов. Как-то маловато будет :) Может я чего не включил?

YuriPanchul Автор

21.12.2022 18:58+1О, это хорошо. Ядро это не мое, оно от Монте и я его производительность не мерял пока. Multiplication обрабатывается программно, да. Добавление multiplication планировалось как упражнение для студентов. А как у вас тогда весь CoreMark проходит - там же есть умножение? С какими числами у каких других ядер вы сравнивали? Вы можете внести все эти измерения вместе с testbench в fork-нутую репозиторию и выложить ссылку здесь или прислать мне на yuri@panchul.com ? Это важное исследование. Если ядро слишком низкопроизводительное из-за stalls или недоимплементированного forwarding-а, то для учебных семинаров можно рассмотреть другое.

YuriPanchul Автор

21.12.2022 19:10То бишь 0.7 CoreMark / MHz? Да, это слишком мало, надо исследовать что там так тормозит.

byman

22.12.2022 09:09У этого ядра конвейер вроде 6 стадий. Например, какой-то примитивный vscale имеет 3 стадии. На этом же коде у него 1.04 cm/mhz против 0.67. Еще одно ядро (9 стадий конвейер) Если отключить. предсказатель, fusion, суперскалярные фичи, то на этом же коде 0.69 (если включить - 3.3). Так что база вроде нормальна :)

YuriPanchul Автор

22.12.2022 09:39Прекрасно, спасибо. Ну с 3-стадийным понятно - у 6-стадийного бОльшая проблема с ветвлением в отсутствие предсказателя перехода. Вообще по хорошему стоит сделать общий сравнительный фреймворк с несколькими открытыми ядрами и демонстрировать студентам что на каждом из них происходит при переходах, зависимостях итд. И дать студентам задание повысить производительность.

YuriPanchul Автор

22.12.2022 18:06Кстати (делаю себе заметку на потом) надо будет померять максимальную тактовую частоту у YRS и vscalе на Open Lane. Если у YRS будет выше, можно использовать как иллюстрацию "3 станции с низкой частотой - против 6 стадий с высокой частотой". Если нет, обсудить с Монте что в дизайне не так.

YuriPanchul Автор

22.12.2022 19:06Поправка к комменту выше - вместо YRS читать YRV (я иногда называю YRV-Plus - YRS)

YuryVl

21.12.2022 18:50+2Ha-ha, hold my beer (c). Выпускник росс.топ.тех вуза, впервые узнал, что в excel "сзади за картинкой" есть "Формулы". Никогда бы не поверил, если бы не присутствовал при сцене сам. Оказалось, что чел.просто никогда не видел офтсных программ типа эл.таблиц.

Balling

21.12.2022 21:35Сравнивать Excel и то на чем пишут процессоры (в том числе Intel) это как сравнить микроскоп и атомный коллайдер.

mpa4b

22.12.2022 16:38Плохая аналогия, т.к. и в микроскопе и в коллайдере применяется то, что называют 'оптикой' -- в микроскопе для света из стекла сделанная, в коллайдере для заряженных частиц и 'сделанная' из магнитных и электрических полей.

p07a1330

21.12.2022 21:44+2А если он не пользовал эксель - что в этом удивительного?

Эксель мощный инструмент, но во-первых, у него действительно не самый удачный и перегруженный интерфейс, а во-вторых, сейчас зачастую запихнуть CSV в питон, чем искать по экселю, как делается та или иная задача в Экселе

YuryVl

22.12.2022 01:03+2Тут в другом дело - excel и электронные таблицы, это своего рода "стандарт". Так же как "ворд". Можно без них обойтись - конечно! Не знать, как они работаю - странно (особенно, для вчерашнего студента).

K0styan

22.12.2022 17:09+1Слышал похожую историю. Нам в своё время на первых курсах (2000-2002) явно запрещали пользоваться Excel-ем - мол, сначала научитесь руками всё просчитывать, а до Excel всегда успеете добраться. Ну, как-то так оно и вышло: добрались, пользовались вовсю.

Через некоторое время услышал обратную историю. Студентов заставляют пользоваться Excel-ем. Чтобы они хоть как-то получили навык обработки даже не большого - средненького объёма данных.

Balling

21.12.2022 21:31Качаешь arm открытое ядро для Vivado и всё.

smoluks4096

21.12.2022 23:57+3>> нужно спортировать YRV на плату Tang Primer 20K c китайским GoWwin FPGA

Vivado кончилось, говин брать будете?

volchenkodmitriy

Спасибо за статью! Вузы бывают разные)

Alexrook

Студенты тоже. Среди выпускников Стенфорда можно встретить достаточно известных личностей. Сам когда-то находил некоторые лекции Стенфорда в свободном доступе, чтобы иметь представление об уровне преподавания в Штатах. Что сказать, я бы мечтал обучаться там, если бы у меня была в жизни такая возможность.

Даже самый лучший ВУЗ не заставит человека учиться, если его туда силой запихнули родители, заплатили денег, а спросить ребенка, интересно ли ему вообще это направление, забыли.