Очень удобно все свои разработки делать на одном и том же семействе микроконтроллеров. А ещё удобнее их делать на одном и том же встраиваемом модуле с микроконтроллером. Но тогда модуль должен быть максимально универсальным. Здесь вариант такого модуля.

Модуль можно использовать в самых разных устройствах, от программируемых логических контроллеров, роботов, станков, охранных систем, логгеров, домофонов до ёлочных гирлянд со спецэффектами и брелков ДУ.

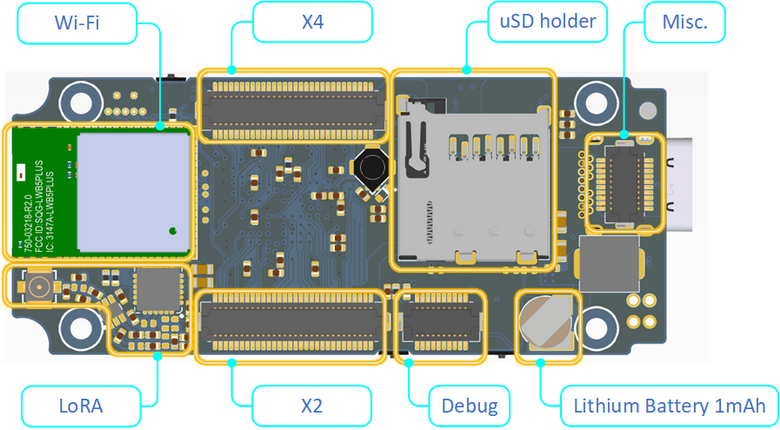

Отличительные особенности — большое количество конфигурируемых входов‑выходов в том числе аналоговых, сравнительно небольшие размеры (63×26×6 мм) и автономное питание со встроенным зарядником и дополнительным элементом питания для часов реального времени.

Модуль является продолжением линии разработки начавшейся с открытого проекта K66BLEZ

Новый модуль теперь имеет ещё больше интерфейсов, больший объем памяти и большую производительность.

Функции и интерфейсы на внешних выводах модуля:

Всего 83 входа-выхода. Из низ 81 могут конфигурироваться и как вход, и как выход.

В том числе 21 вход с 12-битным аналоговым преобразованием

В том числе 6 входов с синхронным аналогово-цифровым преобразованием ( используется для прецизионного управления моторами или для анализаторов 3-фазных электросетей).

В том числе 6 специализированных выходов для управления BLDC и BLAC моторами

Интерфейс RS-485 или RS-232

Интерфейс CAN до 1 Мбит

Интерфейс I2C

Интерфейс SPI до 30 Мбит

Интерфейс USB HS

Интерфейс USB FS

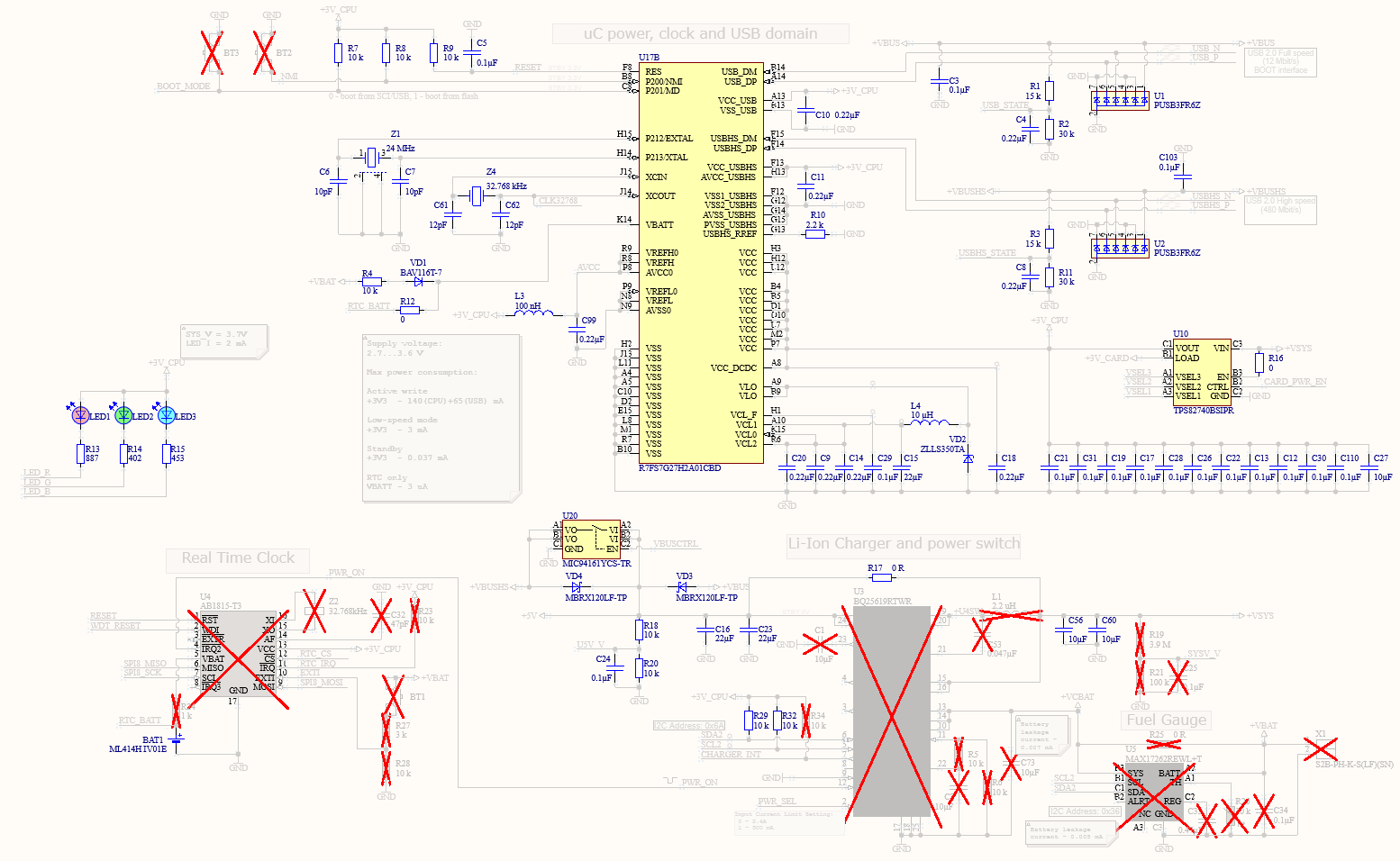

Принципиальная схема

Самое интересное - это внешние разъёмы. Поэтому здесь о них подробней.

Большинство выводов имеют альтернативные функции. Но названия цепей на разъёмах имеют имена созвучные конкретной одной функциональности. Это сделано потому что модули изначально создавались как замена предыдущему поколению модулей с уже устоявшимися функциями. Однако это не означает что выводы нельзя применить по другому назначению. Остаётся на усмотрение разработчика сколько различных интерфейсов и функций он получит в конкретной конфигурации. Но назовём некоторые абсолютные значения достигаемые при разных конфигурациях:

Количество независимых интерфейсов I2C - 4

Количество независимых интерфейсов SPI - 3

Количество независимых интерфейсов UART- 3

Количество независимых интерфейсов CAN -1

Количество каналов для сенсорных ёмкостных кнопок - 6

Количество независимых ШИМ каналов - 17

Количество независимых АЦП - 4 (каналов 21)

Количество независимых ЦАП - 2

В списке выше не учитываются интерфейсы занятые периферией на самом модуле.

Иногда производители модулей выводят на внешние разъёмы сигналы уже занятые периферией их модулей, например сигналы SDRAM или SDIO. Видимо рассчитывая на некое мультиплексирование организуемое на материнской плате. В нашем случае не так. На внешний разъем выведены только те сигналы, которые не используются на самом модуле. Исключение лишь составляет интерфейс SPI8, который подключается на модуле к чипу часов реального времени и внешнему АЦП.

Чтобы было удобнее находить функции выводов и конфигурировать была создана интерактивная таблица в Excel. Таблица позволяет по номеру вывода на разъёме идентифицировать вывод на микроконтроллере и обратно, а также узнать весь перечень возможных функций вывода.

Могут возникнуть вопросы о странных резисторах на схеме R12, R17, R25. В полном варианте комплектации платы они не паяются, но они нужны когда изготавливается бюджетный вариант платы. Схема при этом выглядит вот так:

Конструкция модуля

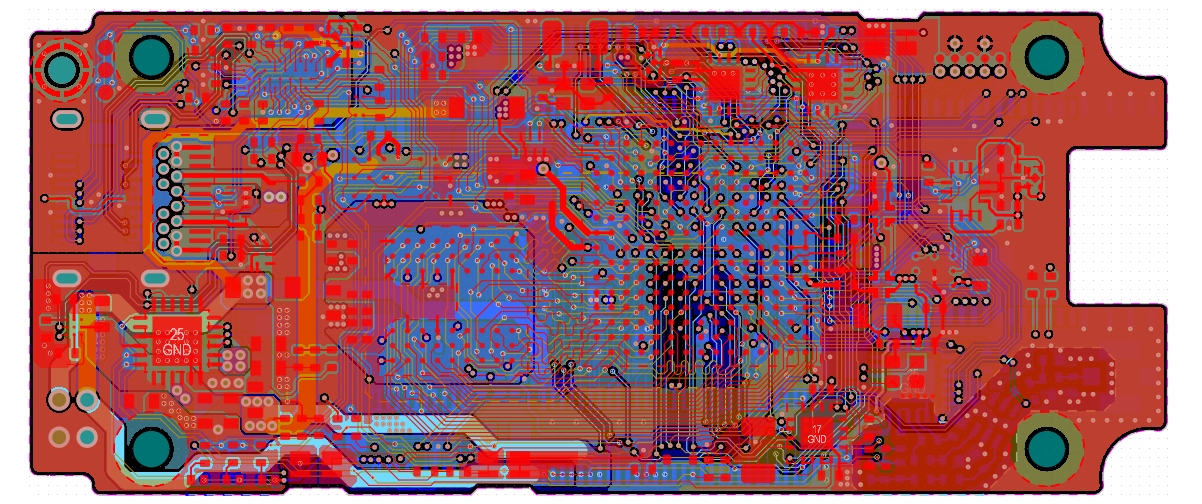

Плата 6-слойная с минимальным зазором 0.1 мм и шириной дорожки 0.1 мм в верхних слоях и 0.075 мм во внутренних слоях.

Плата может размещаться в стандартном корпусе 1551CTSK, поэтому имеет такую несколько не типичную форму

Программирование модуля

Есть два способа начальной загрузки прошивки во Flash микроконтроллера.

Первый способ заключается в использовании штатного начального загрузчика находящегося в ROM микроконтроллера. Начальный загрузчик способен работать через интерфейсы UART9 (X6.13 - RX, X40.50 - TX) и через интерфейс USB FS (X4.58 - USB N, X4.59 - USB P). Для программирования используются утилиты предоставляемые на сайте Renesas.

Второй способ заключается в программировании через SWD/JTAG интерфейс организованный на разъёме X6

В обоих случаях применяются специальные адаптерные платы. Адаптерные платы хороши тем что позволяют одни модули заменять на другие без потери функциональности. Например показанная ниже адаптерная плата S7V30_K66BLEZ вместе с модулем S7V30 полностью функционально заменяет модуль K66BLEZ и ещё добавляет функциональности. На адаптерной плате находится стандартный разъем SWD/JTAG к которому уже можно подключать стандартные кабеля JTAG адаптеров типа JLink.

Проект адаптерной платы также находится в репозитарии.

Создание первой программы

Для микроконтроллеров семейств Synergy производителем чипов предоставляется пакет софта под названием Synergy Software Package (SSP). Там будет IDE под названием e2studio на базе Eclipse. В этой IDE делается полная настройка периферии, пинов и промежуточного программного обеспечения типа файловой системы, RTOS, TCP стека, USB стека и проч. SSP с частотой приблизительно пару раз в год обновляется, поэтому надо следить за текущей версией.

Начинается работа с конфигурирования системы тактирования на чипе:

Конфигурация тактирования в чипах Synergy на удивление простая в отличие например от серии STM32H.

Затем конфигурируем пины

Следующим этапом конфигурируем драйвера HAL и рабочую задачу

Тут почти все готово. Надо знать, что задачи в SSP создаются с использованием Azure RTOS. Сразу это может не стать понятным, поскольку в сгенерированных исходниках сама RTOS будет скрываться в библиотеке libtx.a. Но можно сгенерировать проект и с исходниками RTOS. Правда это будет немного не та версия, которая представлена репозитарии Azure RTOS.

Остаётся заполнить тело задачи. Как обычно, будем моргать светодиодами. На плате их три: синий, красный. зелёный. Текст нашей задачи будет выглядеть вот так:

* @brief Blinky example application

*

* Blinks all leds at a rate of 1 second using the the threadx sleep function.

* Only references two other modules including the BSP, IOPORT.

*

**********************************************************************************************************************/

void blinky_thread_entry(void)

{

/* Define the units to be used with the threadx sleep function */

const uint32_t threadx_tick_rate_Hz = 100; // @suppress("Type cannot be resolved")

/* Set the blink frequency (must be <= threadx_tick_rate_Hz */

const uint32_t freq_in_hz = 2; // @suppress("Type cannot be resolved")

/* Calculate the delay in terms of the threadx tick rate */

const uint32_t delay = threadx_tick_rate_Hz/freq_in_hz; // @suppress("Type cannot be resolved")

/* LED type structure */

bsp_leds_t leds;

/* LED state variable */

ioport_level_t level = IOPORT_LEVEL_HIGH;

/* Get LED information for this board */

R_BSP_LedsGet(&leds);

/* If this board has no leds then trap here */

if (0 == leds.led_count)

{

while(1); // There are no leds on this board

}

while (1)

{

/* Determine the next state of the LEDs */

if(IOPORT_LEVEL_LOW == level)

{

level = IOPORT_LEVEL_HIGH;

}

else

{

level = IOPORT_LEVEL_LOW;

}

/* Update all board LEDs */

for(uint32_t i = 0; i < leds.led_count; i++) // @suppress("Type cannot be resolved")

{

g_ioport.p_api->pinWrite(leds.p_leds[i], level);

}

/* Delay */

tx_thread_sleep (delay);

}

}

Этот текст, за исключением нескольких строк, сгенерирован средой SSP автоматически по шаблону Blink. Поэтому в нем так непривычно много комментариев.

А результат работы будет такой:

Весь проект железа и софта находится в репозитарии. Надо сказать что после генерации проекта в e2studio с использованием Azure RTOS создаётся порядка 4 тысяч файлов, поэтому проект в репозитарии лежит зазипованный. В последующем будет продемонстрировано как упростить проект и избавиться от HAL.

Комментарии (36)

voidptr0

00.00.0000 00:00+2"Очень удобно все свои разработки делать на одном и том же семействе

микроконтроллеров. А ещё удобнее их делать на одном и том же

встраиваемом модуле с микроконтроллером. Но тогда модуль должен быть

максимально универсальным. Здесь вариант такого модуля."А в чем именно преимущество именно Вашей платформы/конфигурации?

Indemsys Автор

00.00.0000 00:00-1Я еще только только начинаю это соревнование за преимущества. Знаете как в гонке?

Преимущества в основном таятся в софте.

olartamonov

00.00.0000 00:00+8Абсолютно не понял смысла этой штуки, пардон. Какое-то «я надену всё лучшее сразу». В каком проекте может потребоваться LoRa, BLE и Wi-Fi одновременно? Если ни в каком, а в реальной жизни и реальных проектах LoRa у нас оказывается на STM32L0, BLE на BlueNRG, а Wi-Fi на ESP32, то в чём польза этой платы?

olartamonov

00.00.0000 00:00+1P.S. Помимо варианта «я демонстрирую инвесторам, как мы поднимем все протоколы IoT, про которые они читали у Гартнера, на одной плате», но этот вариант неактуален год-два как.

Indemsys Автор

00.00.0000 00:00+1Не, ну вы же взялись нам объяснять разницу между протоколами и интерфейсами. Жду ваших перлов про IoT. Там поспорим.

Насчет год два возможно соглашусь. Этот модуль не на века, время жизни пару лет. Потом просто такие чипы перестают делать и начинаются новые.

olartamonov

00.00.0000 00:00+1Ну то есть вместо ответа по сути — переход на личности. Ок.

Indemsys Автор

00.00.0000 00:00+1Но вы хотите чтобы я вам рассказал бизнес идеи? Но делаете это путём такого лёгкого троллинга и неясной формулировки вопроса. Как тут отвечать?

olartamonov

00.00.0000 00:00+1Я хочу увидеть ответ на вопрос «зачем такая плата вообще нужна?», заданный мной очень прямо, ясно и без всякого троллинга. Будет этот ответ содержать ваши бизнес-идеи, регилиозные воззрения или что-то ещё — я понятия не имею, потому что этого ответа не знаю.

Для вас, повторюсь, этот ответ вполне может быть «в 2021 мы получили под эту плату и рассказ, как она заменит все остальные платы, лям баксов от венчура, так что всё окупилось».

Indemsys Автор

00.00.0000 00:00+1Ответ в статье же есть! Чтобы заменить K66BLEZ, потому что (раскрою вам секрет) Kinetis K66 перестали делать.

Зачем нужен был K66BLEZ? Для нашего оборудования. Оно работает по всему миру. А ещё применялось в гимбалах для киностудий, в прототипах продвинутых вибраторов, в электроприводах для автоматических дверей, в охранных устройствах и системах контроля доступа, в многококанальных измерителях. Да тут на Хабре есть несколько проектов с ним.

olartamonov

00.00.0000 00:00+2С лорой, бле, вайфаем, SD-картой и USB-C на каждом устройстве одновременно?

Для меня это выглядит как бессмысленное удорожание и усложнение модуля. Примерно ни в одном реальном проекте не используется больше трети от напиханного на модуль, при этом а) материнская плата нужна всё равно и б) вкинуть на неё нужную периферию не представляет никакой существенной сложности в силу простоты всей этой периферии (а результат ещё и чаще будет лучше, потому что аналоговые цепи, антенны и разъёмы оказываются где надо, а не где получилось, etc).

Поэтому, собственно, примерно все успешно продаваемые вычислительные модули, начиная хотя бы с всем известного RPi Compute Module, несут на себе минимум периферии — как правило, только то, что встроено в процессор, плюс его необходимую обвязку, плюс иногда вещи, которые сложно спроектировать и произвести (т.е. они заметно усложнят материнскую плату).

Indemsys Автор

00.00.0000 00:00+1Половину деталей можно не припаивать. В статье упомянут бюджетный вариант сборки. В нем нет ни LoRa, ни Wi-Fi. Т.е. думаю претензии к избыточности не обоснованы.

Далее про удобность периферии на материнке. Это не всегда верно.

Например АЦП лучше работают когда они на качественной плате с плэйнами. Материнки же могут быть двухслойными, заказываться на PCBway и созданы начинающими дизайнерами. Т.е. наличие АЦП сразу в модуле большой плюс, а стоит это удовольствие недорого. С USB HS или SDIO таже история.

При минимизации модулей уже нельзя поставить разъёмы где надо (а где надо? ), приходится делать компромиссы.И наконец я не планировал конкурировать с RPi.

У моего модуля совершенно другой спектр применений. Так что сравнение неуместное.

olartamonov

00.00.0000 00:00Этот модуль не имеет большого смысла заказывать поштучно — банально будет очень дорого. Соответственно, мы говорим о производстве партиями в десятки, а лучше в сотни штук.

Что подразумевает либо что модуль производится со всем фаршем сразу (не вручную же его потом допаивать по потребности?), либо у нас проекты как минимум мелкосерийные, чтобы под каждый проект имело смысл заказывать свою версию модуля.

Но в мелкосерийном проекте трудозатраты на разработку материнской платы с периферией легко могут оказаться уже ниже, чем затраты на производство чрезмерно сложного вычислительного модуля.

Что касается АЦП — лучше всего они работают, когда их параметры соответствуют задаче. ADS7028 — хороший АЦП, но — это АЦП общего назначения. В конкретной задаче запросто могут быть просто другие требования, в том числе более низкие — удовлетворяемые АЦП по $1 штука, а не по $5 (умножить на два, умножить на минимальный разумный размер партии).

Что касается спектра применений, то его бы и хотелось понять. Пока что для меня это выглядит как натягивание совы на глобус и «потому что можем».

Indemsys Автор

00.00.0000 00:00+1Я уже было клюнул на эту манипуляцию и написал целый список. Но нет, мои планы это мои планы.

olartamonov

00.00.0000 00:00Манипуляция — это, вообще говоря, ваши заголовки «открытый проект», под которыми вы выкладываете на Хабр какую-то очередную разработанную вами чисто для ваших внутренних нужд железку, совершенно не собираясь вести это как открытый проект.

Indemsys Автор

00.00.0000 00:00+1В смысле?

Я сделал проект модуля K66BLEZ. Потом сделал на нем пару совершенно рабочих утилитарных проектов и выложил их, описал их. Чего ещё не хватает? Что ещё не открыто?

Для текущего модуля тож будут проекты, только не всё сразу. Имейте терпение. Это ж работа по вдохновению.

olartamonov

00.00.0000 00:00+1Вы выкладываете схемотехнику модуля, который скорее всего никто не будет повторять — и уж точно никто не будет производить на продажу. Примерно все ваши дискуссии заканчиваются на тезисе «я исходники выложил, больше я ничем вам не обязан». Потом выложите «утилитарные проекты» с таким же уровнем поддержки и востребованности.

Это не «открытый проект». Это «файлы от закрытого проекта, который я делал для себя».

Indemsys Автор

00.00.0000 00:00+1Я вот смотрю много апнотов у TI, у ST. И не один мне там не подходит. Ну чувствую нутром что их кто-то делал под себя и не сказал, а как там все в целом. Как деньги на этом заработать. Зачем это все делалось.

Ну у вас что-то похожее.

rukhi7

00.00.0000 00:00+1а хотя бы порядок (хотя бы) цены этой красавицы можно озвучить 10, 50, 100, 200? Сколько штук за раз можно купить?

Среда разработки скачивается после регистрации или платить надо?

Indemsys Автор

00.00.0000 00:00Среда бесплатная. Раньше была очень дорогая. Но уж как год за неё перестали брать деньги.

Порядок цены в районе 100 евро если покупать детали у розничных продавцов.

Такая уж получилась.

aumi13

00.00.0000 00:00control card в виде готовых модулей для мк с минимальной обвязкой полно у каждого производителя. мне видеца более удобными с краевыми разъемами или стандартными 2.54

https://eu.mouser.com/images/texasinstruments/images/ITP_595-TMDSCNCD28335_t.JPG

Indemsys Автор

00.00.0000 00:00Краевые разъемы я рассматривал. Они сами по себе занимают много места.У меня была цель поместить в минимальные размеры. К тому же с краевыми разъемами я бы не смог обеспечить заменяемость предыдущего модуля K66BLEZ. Краевые разъемы я рассматривал. Они сами по себе занимают много места.У меня была цель поместить в минимальные размеры. К тому же с краевыми разъемами я бы не смог обеспечить заменяемость предыдущего модуля K66BLEZ.

Koyanisqatsi

00.00.0000 00:00+2Видов микроконтроллеров, периферии, подключаемых устройств, протоколов и интерфейсов настолько огромное количество, что создать что-то универсальное просто невозможно, но качество разработки у вас на высоте, могу заметить.

VladimirFarshatov

00.00.0000 00:00Что будет делать автор, после того как поставки этих микроконтроллеров закроют от слова совсем? Это первое. Второе: сколько заводов в РФ способно производить плату массово? И третье: Кто из производителей IoT в РФ сможет применять плату с учетом "импортозамещающих" ограничений при госзакупках, к примеру?

Как решение задачи впихнуть невпихуемое, тем не менее поставил плюсик. Т.к. впихнуть всё это в такой типоразмер - автор(ы) явно превзошли сами себя. Но, в целом - кмк, проект "мертворожденный" о чем тут уже отписалось несколько авторов.

Как пример такого же мертворожденного решения: https://vk.com/id484853030?z=photo484853030_456239018%2Fphotos484853030 - Atmel Mega 2560 во всем своем великолепии в типоразмере 56х88мм, со всеми ножками и сдвоенными контактами для стекирования и прямого использования. С БП до 5ампер на борту. С возможностью домашнего изготовления методом ЛУТ (шаг 0.25мм, 2 слоя) И? А кому сейчас нужна эта "мега"? :)

Indemsys Автор

00.00.0000 00:00+2Я сожалею что многие воспринимают открытые проекты как исключительно возможность своего личного стартапа.

Gromin

00.00.0000 00:00+3Очень удобно все свои разработки делать на одном и том же семействе микроконтроллеров. А ещё удобнее их делать на одном и том же встраиваемом модуле с микроконтроллером. Но тогда модуль должен быть максимально универсальным. Здесь вариант такого модуля.

Модуль можно использовать в самых разных устройствах, от программируемых логических контроллеров, роботов, станков, охранных систем, логгеров, домофонов до ёлочных гирлянд со спецэффектами и брелков ДУ.

Вам, вероятно, виднее что к чему, но хотел бы ответить со стороны своего опыта.

Да, действительно весьма удобно разрабатывать используя одно семейство микроконтроллеров и, тем более, на одном модуле. Для этого те же ST выпускают десятки модификаций контроллеров в каждом семействе. Разные размеры корпуса, разный объем памяти, разная периферия и разная цена.В серийном изделии платить 20-40-60$ за плату или чип, если все прекрасно влазит в чип стоимостью 2$ - нонсенс.

На этапе разработки наличие всякой разной периферии, большого объема памяти и кучи выводов, безусловно, полезно. Но не надо в готовое устройство вставлять плату с SD разъемом если он там не используется.

Та же BluePill тем и хороша, что на ней ничего, по сути, нет: только чип и нужные разъемы. И она дешевая.Внешние разъёмы не плохи (за исключением цены), но лучше бы тогда поставили один, а не 4: паять легче, перекос не страшен (а у вас - только автомонтаж, без вариантов), а развести вы их всяко смогли бы, столько слоев на плате!

В общем вы, конечно, молодцы, но штука очень нишевая. Прям сильно.

Indemsys Автор

00.00.0000 00:00Ниша такого проекта даже не маркетинговая и не технологическая, а я бы сказал организационно-техническая.

Есть места где за всю электронику и софт в больших проектах отвечает всего один человек. Таких мест на самом деле немало. Их больше чем заводских КБ. Я сам поработал в десятке таких мест. Так работают фрилансеры от электроники. Это проект в помощь фрилансерам.Тут не важно сколько копеек разработчик сэкономил на комплектации. Важно только как быстро разработчик переориентируется на новый продукт. Даже применять другие чипы одного семейства обременительно. Легче поставить всюду чип жирнее, но не возиться с коррекцией драйверов. Потому что софт здесь главный и самый сложный элемент.

С другой стороны я не раздеваю заказчика. Не нужен SD разъем, так не паяйте его. Altium даёт широкие возможности для версионирования продукта. У меня, как написано в статье, есть два варианта комплектации платы. Урезанный вариант в два раза дешевле полного варианта.

Насчёт двух разъёмов я бы поспорил. Опыт говорит, что с несколькими разнесёнными разъёмами материнские платы трассировать проще, а занимаемая площадь расходуется эффективней. Я уже три материнские платы разработал для этого модуля и очень доволен что сделал несколько разъёмов. И да, с позиционированием даже при ручной пайке особых сложностей не возникает, вы сами наверно можете догадаться как паять не сместив такие разъёмы.

Karlson_rwa

И сколько при этом себестоимость производства? Странное решение, неужели нельзя было сделать эту плату с нормальными тех. нормами? 0.075 не каждый завод возьмется делать.

Также видится несколько странным расположение DF12 с трех сторон. Это сразу подразумевает автоматическую расстановку ответок на материнке, куда втыкается такой модуль. Руками не криво запаять эти разъемы, чтобы всё хорошо сажалось будет несколько проблематично.

Чем обосновано расположение U.FL на нижней стороне? Ведь чтобы застегнуть туда антенну, придется демонтировать модуль, что тоже видится несколько неудобным.

Karlson_rwa

Отвечу пока сам себе на свой же первый вопрос. Технологичностью в плате не пахнет от слова совсем, увы. После просмотра создалось впечатление, что делало плату несколько людей или же она делалась в несколько заходов с сильными перерывами. Никакого зазора в 0.075 на внутренних слоях я не увидел. Везде 0,1 и больше. Можно даже на нормальные 0,15 перейти, если немного поработать руками. Но это всё равно не поможет снизить стоимость производства, потому что вы умолчали про слепые переходные, которые используете.

Indemsys Автор

Каждый раз убеждаюсь что много писать не нужно.

Вот вы даже не удосужились увидеть слепые переходные на рисунке.

Karlson_rwa

Ну рисунок, да. В тексте-то ничего не сказано, только про какие-то 0.075. Неправильный, кстати. Не будет у вас внутри 18мкм меди, а снаружи 47мкм. Откуда такие цифры? Китайцы, которые её вам делали, прислали?

По остальным вопросам что-нибудь напишете? :)

Не воспринимайте, пожалуйста, мои вопросы как наезды. Мне всего лишь любопытно.

Indemsys Автор

Кто изготавливал платы я не знаю. Я отдаю контрактному сборщику и получаю уже готовые собранные платы. 0.075 - это технологическое ограничение, а не обязательно величина зазора который я обязан делать. В конце трассировки я всегда увеличиваю все зазоры до максимально возможных. И так вышло что 0.075 зазоров не осталось. В стекапе может быть изменен только тип диэлектрика, на остальное я с производителем не подписывался.

Karlson_rwa

Тогда вот так писать совершенно некорректно:

Не находите? А то я тоже для своих плат вообще всех могу указать минимальные тех. нормы того же Резонита, например. Но это не будет корректное описание платы.

Это как? А разный эпсилон у разных диэлектриков?

Вот, кстати, еще вопрос. В чем ваш умысел по удалению меди под РЧ-частью?

Indemsys Автор

Медь удалена на inner4, а на inner3 она есть. Это чтобы дорожки при приемлемой ширине имели 50 Ом. Иначе будут слишком узкие.

Кроме эпсилона у диэлектрика есть ещё кучка параметров как Tg, Df и вот производитель начинает там торговаться что ему применить. Для дешёвого FR-4 кстати эпсилон указывают плюс-минус сапог.

Насчёт 0.075 не стоит обсуждений думаю. Ну может в следующий раз такие сделаю. Это же не показатель качества.

Все же в правилах в проекте записано 0.075 для ширины дорожек во внутренних слоях. С этим не поспорите.

Karlson_rwa

Как-то это на 50 Ом не похоже. Мог, конечно, ошибиться, но что в калькулятор не вбивай, а 50 Ом ну никак. Это если ориентироваться на тот стэк, который в проекте задан и на панасониковский даташит с плюс-минус лаптем.

Indemsys Автор

Да походу вы правы.

Нашли ошибку в трассировке. Должен сказать вам спасибо.

Накосячил в Altium с выбором референтного слоя.

К счастью там частота 868 МГц и такое отклонение почти не имеет значения для данного модуля.